Módulo de detección de codificador incremental de canal doble invt FK1100

Instrucciones de uso del producto

- El módulo de detección de codificador incremental de doble canal FL6112 admite entrada de señal de cuadratura A/B con un volumen de entradatagy de 24V.

- También admite modos de multiplicación de frecuencia x1/x2/x4. Cada canal tiene una entrada y salida de señal digital con un volumentagy de 24V.

- Asegúrese de realizar un cableado adecuado siguiendo las especificaciones de cable proporcionadas.

- Conecte la fuente de alimentación externa de 24 V y 0.5 A para alimentar el módulo y el codificador conectado.

- Asegúrese de tener un aislamiento adecuado y protección contra conexión inversa y sobrecorriente.

- El módulo admite la medición de velocidad y frecuencia utilizando las señales del codificador conectados.

- Asegúrese de la detección adecuada de las señales del codificador A/B/Z, las señales de entrada digital y las señales de salida digital para un procesamiento de datos preciso.

- Consulte el manual para conocer la configuración de parámetros comunes, como ajustes preestablecidos del contador, modos de pulso y niveles eléctricos de detección de DI.

- Solucione fallas comunes como problemas de conexión de energía o configuraciones de parámetros incorrectas utilizando las luces indicadoras.

Preguntas frecuentes

- Q: ¿Cuál es la frecuencia máxima de entrada del codificador admitida por el módulo FL6112?

- A: El módulo admite una frecuencia de entrada de codificador máxima de 200 kHz.

- Q: ¿Qué tipo de señales de codificador admite cada canal?

- A: Cada canal admite la entrada de señal de cuadratura A/B con un volumen de entradatagy de 24V.

Prefacio

Encimaview

Gracias por elegir el módulo de detección de codificador incremental de dos canales FL6112 de INVT. El módulo de detección de codificador incremental de dos canales FL6112 es compatible con los módulos de interfaz de comunicación de la serie INVT FLEX (como FK1100, FK1200 y FK1300), el controlador programable de la serie TS600 y el controlador programable de la serie TM700. El módulo de detección de codificador incremental de dos canales FL6112 tiene las siguientes características:

- El módulo admite la entrada de codificador incremental de dos canales.

- Cada canal de codificador admite una entrada de codificador incremental A/B o de codificador de dirección de pulso.

- Cada canal del codificador admite la entrada de señal de cuadratura A/B con un volumen de entradatage de 24 V, y admite los tipos de fuente y sumidero.

- El modo de codificador incremental admite los modos de multiplicación de frecuencia x1/x2/x4.

- Cada canal del codificador admite 1 entrada de señal digital con un volumen de entradatagy de 24V.

- Cada canal del codificador admite 1 salida de señal digital con un volumen de salidatagy de 24V.

- El módulo proporciona una salida de alimentación de 24 V para que el codificador alimente el codificador conectado.

- El módulo admite una frecuencia de entrada de codificador máxima de 200 kHz.

- El módulo admite la medición de velocidad y frecuencia.

Esta guía describe brevemente la interfaz, el cableado y la interfaz.amples, especificaciones del cable, uso examparchivos, parámetros comunes y fallas comunes y soluciones del módulo de detección de codificador incremental de doble canal INVT FL6112.

Audiencia

- Personal con conocimientos profesionales en electricidad (como ingenieros eléctricos cualificados o personal con conocimientos equivalentes).

Historial de cambios

- El manual está sujeto a cambios irregulares sin previo aviso debido a actualizaciones de la versión del producto u otras razones.

| No. | Cambiar descripción | Versión | Fecha de lanzamiento |

| 1 | Primer lanzamiento. | V1.0 | Julio de 2024 |

Presupuesto

| Artículo | Presupuesto | |||

|

Fuente de alimentación |

Volumen nominal de entrada externatage | 24 V CC (-15 % – +20 %) | ||

| Corriente nominal de entrada externa | 0.5A | |||

| Bus de placa base

Volumen de salida nominaltage |

5 V CC (4.75 V CC–5.25 V CC) |

|||

| Corriente del bus de placa posterior

consumo |

140 mA (valor típico) |

|||

| Aislamiento | Aislamiento | |||

| Protección de la fuente de alimentación | Protección contra conexión inversa y sobrecorriente | |||

|

Indicador |

Nombre | Color | Seda

pantalla |

Definición |

|

Indicador de ejecución |

Verde |

R |

Encendido: el módulo está en funcionamiento. Parpadeo lento (una vez cada 0.5 s): el módulo está estableciendo comunicación.

Apagado: El módulo no está encendido encendido o es anormal. |

|

|

Indicador de error |

Rojo |

E |

Apagado: No se encontraron anomalías durante el funcionamiento del módulo.

Parpadeo rápido (una vez cada 0.1 s): el módulo está fuera de línea. Parpadeo lento (una vez cada 0.5 s): No hay alimentación conectada externamente o Configuración de parámetros incorrecta. |

|

| Indicador de canal | Verde | 0 | Habilitar el codificador del canal 0 | |

| 1 | Habilitar el codificador del canal 1 | |||

|

Detección de señal del codificador A/B/Z |

Verde |

A0 |

Encendido: la señal de entrada es válida. Apagado: la señal de entrada no es válida. |

|

| B0 | ||||

| Z0 | ||||

| A1 | ||||

| B1 | ||||

| Z1 | ||||

| Artículo | Presupuesto | |||

| Entrada digital

detección de señal |

Verde | X0 | Encendido: La señal de entrada es válida.

Apagado: La señal de entrada no es válida. |

|

| X1 | ||||

| Salida digital

indicación de señal |

Verde | Y0 | Activado: Habilitar salida.

Desactivado: Desactivar salida. |

|

| Y1 | ||||

| Conectado

tipo de codificador |

Codificador incremental | |||

| Número de

canales |

2 | |||

| Volumen del codificadortage | 24 VCC ± 15% | |||

| Rango de conteo | -2147483648 – 2147483647 | |||

| Modo pulso | Entrada de pulso de diferencia de fase/pulso+dirección (admite

señales sin dirección) |

|||

| Frecuencia de pulso | 200 kHz | |||

| Multiplicación de frecuencia

modo |

x1/x2/x4 |

|||

| Resolución | 1–65535PPR (pulsos por revolución) | |||

| Contador preestablecido | El valor predeterminado es 0, lo que significa que el ajuste preestablecido está deshabilitado. | |||

| Pulso Z

calibración |

Compatible de forma predeterminada con la señal Z | |||

| Filtro de contador | (0–65535)*0.1 μs por canal | |||

| Número de DI | 2 | |||

| Detección DI

nivel eléctrico |

24 V CC | |||

| Borde DI

selección |

Borde ascendente/Borde descendente/Borde ascendente o descendente | |||

| Tipo de cableado DI | Cableado tipo fuente (PNP)/tipo sumidero (NPN) | |||

| Tiempo de filtro DI

configuración |

(0–65535)*0.1 μs por canal | |||

| Valor bloqueado | Valores totales bloqueados y banderas de finalización del bloqueo | |||

| ENCENDIDO/APAGADO

Tiempo de respuesta |

A nivel de μs | |||

| Canal DO | 2 | |||

| Nivel de salida DO | 24 V | |||

| Formulario de salida DO | Cableado tipo fuente, corriente máxima 0.16 A | |||

| Función DO | Resultado de comparación | |||

| Hacer vol.tage | 24 V CC | |||

| Medición | Frecuencia/Velocidad | |||

| Artículo | Presupuesto | |

| variable | ||

| El tiempo de actualización de la medición.

función |

Cuatro niveles: 20 ms, 100 ms, 500 ms, 1000 ms |

|

| Función de compuerta | Puerta de software | |

| Proceso de dar un título | CE, RoHS | |

|

Ambiente |

Protección de entrada (IP)

clasificación |

IP20 |

| Laboral

temperatura |

-20 ° C– + 55 ° C | |

| Humedad de trabajo | 10%–95% (sin condensación) | |

| Aire | Sin gas corrosivo | |

| Almacenamiento

temperatura |

-40 ° C– + 70 ° C | |

| Humedad de almacenamiento | HR < 90%, sin condensación | |

| Altitud | Menos de 2000 m (80 kPa) | |

| Grado de contaminación | ≤2, conforme con IEC61131-2 | |

| Anti-interferencia | Cable de alimentación de 2 kV, conforme a IEC61000-4-4 | |

| Clase ESD | 6 kVCD o 8 kVAD | |

| Compatibilidad electromagnética

nivel antiinterferencia |

Zona B, IEC61131-2 |

|

|

Resistente a las vibraciones |

IEC60068-2-6

5 Hz–8.4 Hz, vibración ampLongitud de 3.5 mm, 8.4 Hz–150 Hz, ACC de 9.8 m/s2, 100 minutos en cada dirección de X, Y y Z (10 veces y 10 minutos cada vez, para un total de 100 minutos) |

|

| Resistencia al impacto |

Resistencia al impacto |

IEC60068-2-27

50 m/s2, 11 ms, 3 veces para cada uno de los 3 ejes en cada dirección de X, Y y Z |

| Instalación

método |

Instalación en riel: riel DIN estándar de 35 mm | |

| Estructura | 12.5 × 95 × 105 (An. × Pr. × Al., unidad: mm) | |

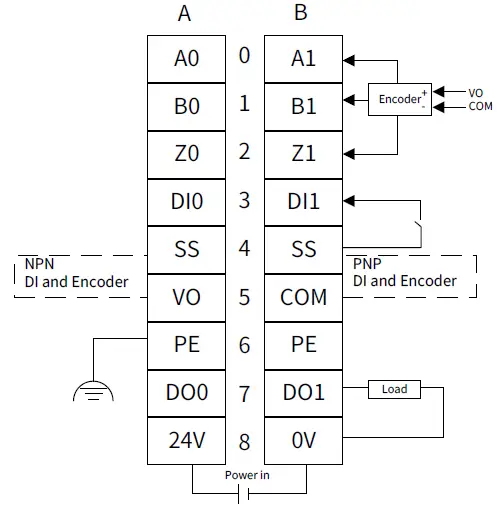

Descripción de la interfaz

| Diagrama esquemático | Señal izquierda | Izquierda Terminal | borne derecho | Señal correcta |

|

A0 | A0 | B0 | A1 |

| B0 | A1 | B1 | B1 | |

| Z0 | A2 | B2 | Z1 | |

| DI0 | A3 | B3 | DI1 | |

| SS | A4 | B4 | SS | |

| VO | A5 | B5 | COM | |

| PE | A6 | B6 | PE | |

| DO0 | A7 | B7 | DO1 | |

| 24 V | A8 | B8 | 0V |

| Alfiler | Nombre | Descripción | Presupuesto |

| A0 | A0 | Entrada de fase A del codificador del canal 0 | 1. Impedancia interna: 3.3 kΩ

2. 12–30 V de volumentagLa entrada es aceptable. 3. Admite entrada de sumidero 4. Máx. frecuencia de entrada: 200kHz |

| B0 | A1 | Entrada de fase A del codificador del canal 1 | |

| A1 | B0 | Entrada de fase B del codificador del canal 0 | |

| B1 | B1 | Entrada de fase B del codificador del canal 1 | |

| A2 | Z0 | Entrada de fase Z del codificador del canal 0 | |

| B2 | Z1 | Entrada de fase Z del codificador del canal 1 | |

| A3 | DI0 | Entrada digital del canal 0 | 1. Impedancia interna: 5.4 kΩ

2. 12–30 V de volumentagLa entrada es aceptable. 3. Admite entrada de sumidero 4. Frecuencia de entrada máxima: 200 Hz |

| B3 | DI1 | Entrada digital del canal 1 | |

| A4 | SS | Puerto común de entrada digital/codificador | |

| B4 | SS | ||

| A5 | VO | Fuente de alimentación externa positiva de 24 V |

Potencia de salida: 24 V ± 15 % |

| B5 | COM | Fuente de alimentación externa de 24 V negativa | |

| A6 | PE | Tierra de bajo ruido | Puntos de conexión a tierra de bajo ruido para el módulo |

| B6 | PE | Tierra de bajo ruido | |

| A7 | DO0 | Salida digital del canal 0 | 1. Admite salida de fuente

2. Frecuencia máxima de salida: 500 Hz 3. Corriente máxima soportada de un solo canal: < 0.16 A |

|

B7 |

DO1 |

Salida digital del canal 1 |

|

| A8 | +24 V | Módulo de entrada de alimentación de 24 V positivo | Entrada de alimentación del módulo: 24 V ± 10 % |

| B8 | 0V | Módulo de entrada de alimentación de 24 V negativo |

Cableado exampLos

Nota

- Se debe utilizar un cable blindado como cable del codificador.

- El terminal PE debe estar bien conectado a tierra a través de un cable.

- No ate el cable del codificador con el cable de alimentación.

- La entrada del codificador y la entrada digital comparten un terminal común SS.

- Al utilizar módulos para alimentar el codificador, para la interfaz de entrada del codificador NPN, cortocircuite SS y VO; para la interfaz de entrada del codificador PNP, cortocircuite SS a COM.

- Cuando se utiliza una fuente de alimentación externa para alimentar el codificador, para la interfaz de entrada del codificador NPN, cortocircuite SS y el polo positivo de la fuente de alimentación externa; para la interfaz de entrada del codificador PNP, cortocircuite SS al polo negativo de la fuente de alimentación externa.

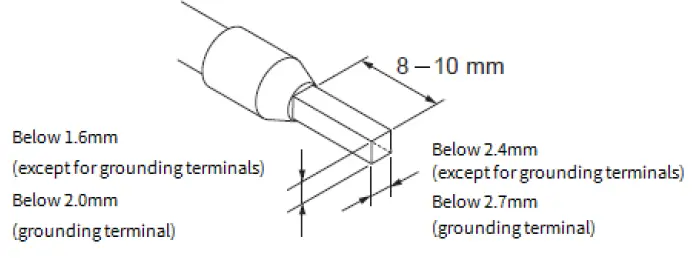

Especificaciones de cable

| Material del cable | Diámetro del cable | Herramienta de crimpado | |

| mm2 | AWG | ||

|

Terminal de cable tubular |

0.3 | 22 |

Utilice un alicate de crimpado adecuado. |

| 0.5 | 20 | ||

| 0.75 | 18 | ||

| 1.0 | 18 | ||

| 1.5 | 16 | ||

Nota: Los diámetros de los cables de los terminales de cable tubulares de la tabla anterior son solo de referencia y se pueden ajustar en función de las situaciones reales.

Al utilizar otros terminales de cable tubulares, se engarzan varios hilos de cable y los requisitos de tamaño de procesamiento son los siguientes:

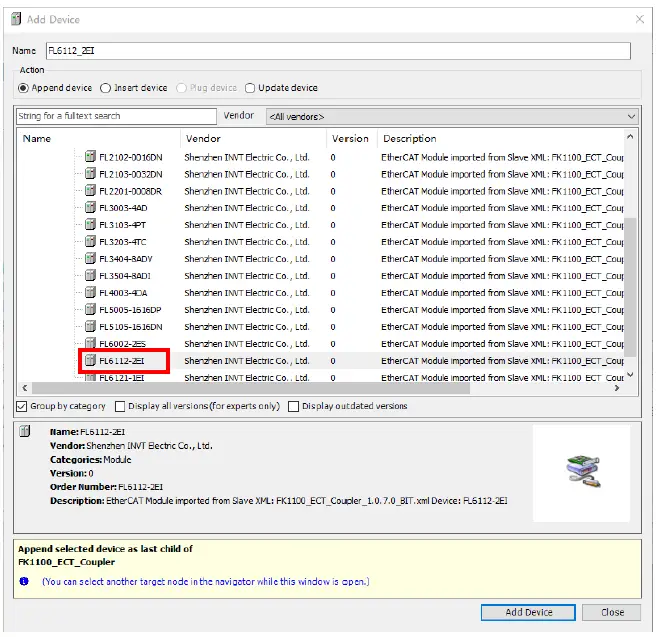

Aplicación example

- Este capítulo toma a CODESYS como ejemploampLe presentamos el uso del producto. Paso 1 Agregue el dispositivo FL6112_2EI.

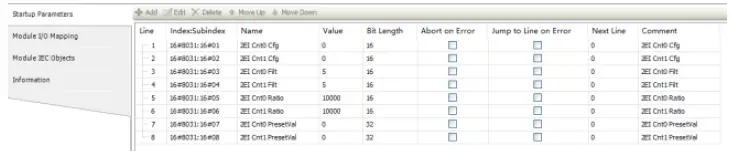

- Paso 2: Elija los parámetros de inicio, configure el contador, el modo de filtrado, la resolución del codificador y los valores preestablecidos del contador según las necesidades reales, con una unidad de filtro de 0.1 μs.

- Cntx Cfg(x=0,1) es el parámetro de configuración del contador de tipo UINT. Tomando como ejemplo la configuración del contador 0ample, la definición de los datos se puede encontrar en la descripción del parámetro.

| Poco | Nombre | Descripción |

|

Bit1–bit0 |

Modo de canal |

00: frecuencia cuádruple de fase A/B; 01: frecuencia doble de fase A/B

10: Frecuencia nominal de fase A/B; 11: Pulso+dirección |

|

Bit3–bit2 |

Periodo de medición de frecuencia |

00: 20 ms; 01: 100 ms; 10: 500 ms; 11: 1000 ms |

| Bit5–bit4 | Habilitación del pestillo de borde | 00: Desactivado; 01: Borde ascendente; 10: Borde descendente; 11: Dos bordes |

| Bit7–bit6 | Reservado | Reservado |

|

Bit9–bit8 |

Ancho de salida del pulso cuando la comparación es consistente |

00: 1 ms; 01: 2 ms; 10: 4 ms; 11: 8 ms |

|

Bit11–bit10 |

Modo de salida de comparación DO |

00: Salida cuando la comparación es consistente

01: Salida cuando la diferencia entre [límite inferior de conteo, valor de comparación] 10: Salida cuando la diferencia entre [valor de comparación, límite superior del recuento] 11: Reservado |

| Bit15–bit12 | Reservado | Reservado |

Suponiendo que el contador 0 está configurado como frecuencia cuádruple de fase A/B, el período de medición de frecuencia es de 100 ms, el enganche de borde ascendente de DI0 está habilitado y el modo está configurado para emitir un pulso de 8 ms cuando la comparación es consistente, Cnt0 Cfg debe configurarse como 788, es decir, 2#0000001100010100, como se detalla a continuación.

| Bit15– bit12 | Bit11 | Bit10 | Bit9 | Bit8 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 0000 | 00 | 11 | 00 | 01 | 01 | 00 | ||||||

|

Reservado |

Salida cuando la comparación es consistente |

8 ms |

Reservado |

Flanco ascendente |

100 ms |

Frecuencia cuádruple de fase A/B | ||||||

- Cntx Filt(x=0,1) es el parámetro de filtro del puerto A/B/Z/DI con una unidad de 0.1 μs. Si se establece en 10, significa que solo se filtran las señales que permanecen estables y no saltan dentro de 1 μs.ampLED.

- La relación Cntx (x=0,1) es la resolución del codificador (número de pulsos que se retroalimentan desde una revolución, es decir, el incremento de pulso entre dos pulsos Z). Suponiendo que la resolución indicada en el codificador es 2500P/R, la relación Cnt0 debe establecerse en 10000, ya que la configuración Cnt0 está configurada como cuádruple de fase A/B.

- Cntx PresetVal(x=0,1) es el valor preestablecido del contador de tipo DINT.

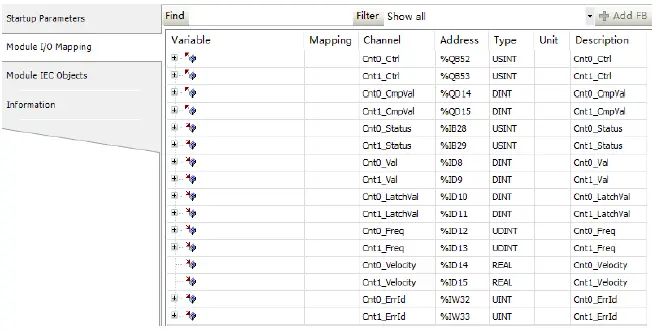

- Paso 3 Después de configurar los parámetros de inicio anteriores y descargar el programa, controle el contador en la interfaz de mapeo de E/S del módulo.

- Cntx_Ctrl(x=0,1) es el parámetro de control del contador. Tomando el contador 0 como un example, la definición de los datos se puede encontrar en la descripción del parámetro.

| Poco | Nombre | Descripción |

| Bit0 | Habilitar el conteo | 0: Desactivar 1: Activar |

| Bit1 | Borrar valor de conteo | Eficaz en el borde ascendente |

| Bit2 | Escribe el valor preestablecido del contador | Eficaz en el borde ascendente |

| Bit3 | La bandera de desbordamiento de conteo claro | Eficaz en el borde ascendente |

| Bit4 | Contracomparación | 0: Desactivar 1: Activar |

| Bit7–bit5 | Reservado | Reservado |

- Cntx_CmpVal(x=0,1) es el valor de comparación del contador de tipo DINT.

- Suponiendo que Cnt0_CmpVal está configurado en 1000000 y desea habilitar el contador para comparación, configure Cnt0_Ctrl en 17, que es 2#00010001. Los detalles son los siguientes.

| Bit7–bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 000 | 1 | 0 | 0 | 0 | 1 |

| Reservado | 1: habilitar | Eficaz en el borde ascendente | Eficaz en el borde ascendente | Eficaz en el borde ascendente | 1: habilitar |

De acuerdo con el valor de configuración 788 de Cnt0 Cfg mencionado anteriormente (que permite que DO emita un pulso de 8 ms cuando la comparación es consistente), cuando el valor de conteo Cnt0_Val es igual a 1000000, DO0 emitirá un pulso de 8 ms.

Para borrar el valor de conteo actual del contador 0, configure Cnt0_Ctrl en 2, que es 2#00000010. Los detalles son los siguientes.

| Bit7–bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 000 | 0 | 0 | 0 | 1 | 0 |

| Reservado | 0: Desactivado | Eficaz en el borde ascendente | Eficaz en el borde ascendente | Eficaz en el borde ascendente | 0: Desactivado |

- En este punto, el bit1 de Cnt0_Ctrl cambia de 0 a 1. El módulo FL6112_2EI monitorea el flanco ascendente de este bit y borra el valor de conteo del contador 0, lo que significa que Cnt0_Val se borra.

Apéndice A Descripción de parámetros

| Nombre del parámetro | Tipo | Descripción |

| Cfg de la cuenta 2EI | UINT | Parámetro de configuración del contador 0: Bit1–bit0: Configuración del modo de canal

00: Frecuencia cuádruple de fase A/B; 01: Frecuencia doble de fase A/B; 10: Frecuencia nominal de fase A/B; 11: Pulso+dirección (nivel alto, positivo) Bit3–bit2: Periodo de medición de frecuencia 00: 20 ms; 01: 100 ms; 10: 500 ms; 11: 1000 ms Bit5–bit4: Habilitación del valor de conteo de enclavamiento de borde 00: Desactivado; 01: Borde ascendente; 10: Borde descendente; 11: Dos bordes Bit7–bit6: Reservado Bit9–bit8: Ancho de salida del pulso cuando la comparación es consistente 00: 1 ms; 01: 2 ms; 10: 4 ms; 11: 8 ms Bit11–bit10: Modo de salida de comparación DO 00: Salida cuando la comparación es consistente; 01: Salida entre [límite inferior del conteo, valor de comparación]; 10: Salida entre [valor de comparación, límite superior del recuento]; 11: Reservado (Salida cuando la comparación es consistente) Bit15–bit12: Reservado |

| Cfg de la cuenta 2EI | UINT | Parámetro de configuración para el contador 1. La configuración del parámetro es consistente con el contador 0. |

| Filtro 2EI Cnt0 | UINT | Parámetro de filtrado para el puerto A/B/Z/DI del contador 0. Ámbito de aplicación: 0–65535 (Unidad: 0.1 μs) |

| Filtro 2EI Cnt1 | UINT | Parámetro de filtrado para el puerto A/B/Z/DI del contador 1. Ámbito de aplicación: 0–65535 (Unidad: 0.1 μs) |

| Relación 2EI Cnt0 | UINT | Resolución del codificador para el contador 0 (número de pulsos realimentados desde una revolución, el incremento de pulso entre dos pulsos Z). |

| Relación 2EI Cnt1 | UINT | Resolución del codificador para el contador 1 (número de pulsos realimentados desde una revolución, el incremento de pulso entre dos pulsos Z). |

| 2EI Cnt0 Valor preestablecido | FUERZA DE | Valor preestablecido del contador 0. |

| Nombre del parámetro | Tipo | Descripción |

| 2EI Cnt1 Valor preestablecido | FUERZA DE | Valor preestablecido del contador 1. |

| Cnt0_Ctrl | SINA | Parámetro de control para el contador 0.

Bit0: Habilitar conteo, válido en niveles altos Bit1: Borrar conteo, válido en el flanco ascendente Bit2: Escribe el valor preestablecido del contador, válido en el flanco ascendente Bit3: Borrar el indicador de desbordamiento de conteo, válido en el flanco ascendente. Bit4: Habilitar la función de comparación de conteo, válida en niveles altos (siempre que el conteo esté habilitado). Bit7–bit5: Reservado |

| Cnt1_Ctrl | SINA | Parámetro de control para el contador 1. El parámetro

La configuración es consistente con el contador 0. |

| Cnt0_CmpVal | FUERZA DE | Valor de comparación del contador 0 |

| Cnt1_CmpVal | FUERZA DE | Valor de comparación del contador 1 |

| Cnt0_Estado | SINA | Contador 0, estado de conteo, retroalimentación Bit0: Bit de bandera de ejecución hacia adelante

Bit1: Bit de bandera de ejecución inversa Bit2: Bit de bandera de desbordamiento Bit3: Bit de bandera de desbordamiento insuficiente Bit4: Indicador de finalización del enclavamiento DI0 Bit7–bit5: Reservado |

| Cnt1_Estado | SINA | Contador 1, estado de conteo, retroalimentación Bit0: Bit de bandera de ejecución hacia adelante

Bit1: Bit de bandera de ejecución inversa Bit2: Bit de bandera de desbordamiento Bit3: Bit de bandera de desbordamiento insuficiente Bit4: Indicador de finalización del enclavamiento DI1 Bit7–bit5: Reservado |

| Cnt0_Val | FUERZA DE | Valor de conteo del contador 0 |

| Cnt1_Val | FUERZA DE | Valor de conteo del contador 1 |

| Cnt0_Valor de cierre | FUERZA DE | Valor bloqueado del contador 0 |

| Cnt1_Valor de cierre | FUERZA DE | Valor bloqueado del contador 1 |

| Frecuencia Cnt0 | UDINT | Contador de frecuencia 0 |

| Frecuencia Cnt1 | UDINT | Contador de frecuencia 1 |

| Cnt0_Velocidad | REAL | Contador de velocidad 0 |

| Cnt1_Velocidad | REAL | Contador de velocidad 1 |

| Cnt0_ErrId | UINT | Código de error del contador 0 |

| Cnt1_ErrId | UINT | Código de error del contador 1 |

Apéndice B Código de falla

| Falla código (decimal) | Código de falla (hexadecimal) |

Falla tipo |

Solución |

|

1 |

0x0001 |

Error de configuración del módulo |

Asegúrese de que haya una asignación correcta entre la configuración de la red del módulo y la configuración física. |

| 2 | 0x0002 | Módulo incorrecto

ajuste de parámetros |

Asegúrese de que el parámetro del módulo

los ajustes son correctos. |

| 3 | 0x0003 | Fallo de la fuente de alimentación del puerto de salida del módulo | Asegúrese de que la fuente de alimentación del puerto de salida del módulo sea normal. |

|

4 |

0x0004 |

Fallo de salida del módulo |

Asegúrese de que la salida del módulo

La carga del puerto está dentro del rango especificado. |

|

18 |

0x0012 |

Configuración de parámetros incorrecta para el canal 0 | Asegúrese de que la configuración de los parámetros para el canal 0 sea

correcto. |

|

20 |

0x0014 |

Fallo de salida en el canal 0 |

Asegúrese de que la salida de

El canal 0 no tiene cortocircuito ni circuito abierto. |

|

21 |

0x0015 |

Falla de circuito abierto en fuente de señal en el canal 0 | Asegúrese de que la conexión física de la fuente de señal del canal

0 es normal. |

|

22 |

0x0016 |

Samplímite de señal ling

Falla excedente en el canal 0 |

Asegúrese de que el sampseñal de lingote

en el canal 0 no supera el límite de chips. |

|

23 |

0x0017 |

SampEl límite superior de la medición de la señal de ling excede la falla

canal 0 |

Asegúrese de que el sampLa señal de salida en el canal 0 no supera el límite superior de medición. |

|

24 |

0x0018 |

SampLímite inferior de medición de señal de ling que excede la falla

canal 0 |

Asegúrese de que el sampLa señal de salida en el canal 0 no supera el límite inferior de medición. |

|

34 |

0x0022 |

Configuración de parámetros incorrecta para el canal 1 | Asegúrese de que el parámetro

Los ajustes del canal 1 son correctos. |

| Falla

código (decimal) |

Código de falla (hexadecimal) |

Falla tipo |

Solución |

|

36 |

0x0024 |

Fallo de salida en el canal 1 |

Asegúrese de que la salida del canal 1 no tenga cortocircuito ni circuito abierto. |

|

37 |

0x0025 |

Falla de circuito abierto en fuente de señal en el canal 1 | Asegúrese de que la conexión física de la fuente de señal del canal 1 sea normal. |

|

38 |

0x0026 |

SampLímite de señal de ling que excede la falla en el canal 1 | Asegúrese de que el sampLa señal de ling en el canal 1 no excede el límite de chip. |

|

39 |

0x0027 |

SampEl límite superior de la medición de la señal de ling excede la falla en el canal 1 | Asegúrese de que el sampLa señal de salida en el canal 1 no supera el límite superior de medición. |

|

40 |

0x0028 |

SampEl límite inferior de la medición de la señal de ling excede la falla en el canal 1 | Asegúrese de que el sampLa señal de salida en el canal 1 no supera el límite inferior de medición. |

CONTACTO

Shenzhen INVT Electric Co., Ltd.

- Dirección: Edificio de tecnología INVT Guangming, Songbai Road, Matian,

- Distrito de Guangming, Shenzhen, China

Electrónica de potencia INVT (Suzhou) Co., Ltd.

- Dirección: No. 1 Kunlun Mountain Road, Ciudad de Ciencia y Tecnología,

- Distrito de Gaoxin, Suzhou, Jiangsu, China

Websitio: www.invt.com

La información del manual puede estar sujeta a cambios sin previo aviso.

Documentos / Recursos

|

Módulo de detección de codificador incremental de canal doble invt FK1100 [pdf] Guía del usuario Módulo de detección de codificador incremental de canal doble FK1100, FK1200, FK1300, TS600, TM700, FK1100, Módulo de detección de codificador incremental de canal doble FK1100, Módulo de detección de codificador incremental de canal, Módulo de detección de codificador incremental, Módulo de detección de codificador, Módulo de detección, Módulo |