intel AN 805 Konfigurasi Parsial Hierarki tina Desain dina Arria 10 SoC Development Board

Hierarki Parsial Reconfiguration Tutorial pikeun Intel® Arria® 10 SoC Development Board

Catetan aplikasi ieu nunjukkeun ngarobih desain anu saderhana janten desain anu tiasa dikonfigurasi deui sacara hierarki, sareng ngalaksanakeun desain dina papan pangembangan Intel® Arria® 10 SoC. Konfigurasi ulang parsial hierarki (HPR) nyaéta tipe husus tina konfigurasi ulang parsial (PR), dimana anjeun ngandung wewengkon PR dina wewengkon PR séjén. Anjeun tiasa nyiptakeun sababaraha personas pikeun partisi anak sareng indungna. Anjeun nyarang partisi anak dina partisi indungna. Konfigurasi ulang partisi anak teu mangaruhan operasi di indungna atawa wewengkon statik. Konfigurasi ulang partisi indungna henteu mangaruhan operasi di daérah statik, tapi ngagentos partisi anak daérah indung sareng personas partisi anak standar. Metodologi ieu mujarab dina sistem dimana sababaraha fungsi waktos ngabagi sumber daya alat FPGA anu sami.

Konfigurasi parsial nyayogikeun kamajuan di handap ieu kana desain datar:

- Ngidinan reconfiguration desain run-time

- Ngaronjatkeun skalabilitas desain

- Ngurangan downtime sistem

- Ngarojong fungsi waktos-multiplexing dinamis dina rarancang

- Turunkeun biaya sareng pamakean listrik ku ngagunakeun rohangan dewan anu efisien

- Catetan:

- Implementasi desain rujukan ieu merlukeun familiarity dasar jeung aliran palaksanaan Intel Quartus® Prime FPGA jeung pangaweruh ngeunaan proyék primér Intel Quartus Prime. files.

Émbaran patali

- Intel Arria 10 SoC Development Kit Pituduh Pamaké

- Konsép Konfigurasi Parsial

- Aliran Desain Reconfiguration parsial

- Sabagéan Rekonfigurasi Rekomendasi Desain

- Pertimbangan Desain Reconfiguration parsial

Syarat Desain Rujukan

Desain rujukan ieu merlukeun di handap:

- Vérsi software Intel Quartus Prime Pro Edition 17.1 pikeun palaksanaan desain.

- Kit pamekaran Intel Arria 10 SoC pikeun palaksanaan FPGA.

Intel Corporation. Sadaya hak disimpen. Intel, logo Intel, sareng merek Intel sanés mangrupikeun mérek dagang Intel Corporation atanapi anak perusahaanna. Intel ngajamin kinerja produk FPGA sareng semikonduktor na kana spésifikasi ayeuna saluyu sareng garansi standar Intel, tapi ngagaduhan hak pikeun ngarobih naon waé produk sareng jasa iraha waé tanpa aya bewara. Intel henteu nanggung tanggung jawab atanapi tanggung jawab anu timbul tina aplikasi atanapi pamakean inpormasi, produk, atanapi jasa anu dijelaskeun di dieu iwal ti dinyatakeun sapuk sacara tinulis ku Intel. Konsumén Intel disarankan pikeun ménta versi panganyarna tina spésifikasi alat sateuacan ngandelkeun inpormasi anu diterbitkeun sareng sateuacan nempatkeun pesenan produk atanapi jasa.

- Ngaran sareng merek sanésna tiasa diklaim salaku hak milik batur.

Desain Rujukan Leuwihview

- Desain rujukan ieu diwangun ku hiji counter 32-bit. Dina tingkat dewan, desain nyambungkeun jam ka sumber 50MHz tur nyambungkeun kaluaran ka opat LEDs on FPGA. Milih kaluaran ti counter bit dina runtuyan husus ngabalukarkeun LEDs ngacieupan dina frékuénsi husus.

Gambar 1. Desain Rujukan Datar tanpa PR Partitioning

Desain Rujukan Files

Tutorial konfigurasi ulang parsial sayogi di lokasi ieu: https://github.com/intel/fpga-partial-reconfig

Pikeun ngundeur tutorialna:

- Pencét Klon atanapi unduh.

- Pencét Unduh ZIP. Buka zip FPGA-partial-config-master.zip file.

- Arahkeun ka tutorials / a10_soc_devkit_blinking_led_hpr sub-folder pikeun ngakses desain rujukan.

Folder datar diwangun ku handap files:

Tabél 1. Desain Rujukan Files

| File Ngaran | Katerangan |

| luhur. SV | Tingkat luhur file ngandung palaksanaan datar desain. modul ieu instantiates blinking_led sub-partisi jeung modul top_counter. |

| top_counter.sv | Top-tingkat counter 32-bit nu ngatur LED [1] langsung. Output kadaptar tina counter ngadalikeun LED [0], sarta ogé kakuatan LED [2] jeung LED [3] via modul blinking_led. |

| blinking_led.sdc | Nangtukeun konstrain timing pikeun proyék. |

| dituluykeun… | |

| File Ngaran | Katerangan |

| blinking_led.SV | Dina tutorial ieu, anjeun ngarobih modul ieu kana partisi PR indungna. modul narima kaluaran didaptarkeun tina modul top_counter, nu ngatur LED [2] jeung LED [3]. |

| blinking_led.qpf | Proyék Intel Quartus Prime file ngandung daptar sadaya révisi dina proyék. |

| blinking_led.qsf | Setélan Intel Quartus Prime file ngandung assignments sareng setelan pikeun proyék. |

Catetan: Folder hpr ngandung set lengkep files anjeun nyieun ngagunakeun catetan aplikasi ieu. Rujukan ieu files iraha wae titik salila walkthrough nu.

Gambar 2. Desain Rujukan Files

Rujukan Desain Walkthrough

Léngkah-léngkah ieu ngajelaskeun aplikasi konfigurasi ulang parsial pikeun desain datar. Tutorial ngagunakeun parangkat lunak Intel Quartus Prime Pro Edition pikeun papan pangembangan Intel Arria 10 SoC:

- Lengkah 1: Ngamimitian dina kaca 6

- Lengkah 2: Jieun Submodul Tingkat Budak dina kaca 6

- Lengkah 3: Nyieun Partisi Desain dina kaca 7

- Lengkah 4: Alokasi Panempatan sareng Routing Wewengkon pikeun Partisi PR dina kaca 9

- Lengkah 5: Nambahkeun Intel Arria 10 Partial Reconfiguration Controller IP Core dina kaca 10

- Lengkah 6: Nangtukeun Personas dina kaca 13

- Lengkah 7: Nyieun Révisi dina kaca 15

- Lengkah 8: Ngahasilkeun Skrip Aliran Konfigurasi Parsial Hierarkis dina kaca 20

- Lengkah 9: Ngajalankeun Skrip Aliran Konfigurasi Parsial Hierarkis dina kaca 21

- Lengkah 10: Programing Board dina kaca 22

Lengkah 1: Ngamimitian

Pikeun nyalin desain rujukan files kana lingkungan kerja anjeun sareng kompilasi desain datar blinking_led:

- Jieun diréktori di lingkungan gawé anjeun, a10_soc_devkit_blinking_led_hpr.

- Nyalin tutorials diundeur / a10_soc_devkit_blinking_led_hpr / sub-folder datar ka diréktori, a10_soc_devkit_blinking_led_hpr.

- Dina parangkat lunak Intel Quartus Prime Pro Edition, klik File ➤ Buka Project tur pilih blinking_led.qpf.

- Pikeun nyusun rarancang datar, klik Processing ➤ Start Compilation.

Lengkah 2: Nyiptakeun Sub-modul Tingkat Budak

Pikeun ngarobah desain datar ieu kana desain PR hirarki, anjeun kudu nyieun sub-modul anak (blinking_led_child. SV) nu nested dina sub-modul indungna (blinking_led.sv).

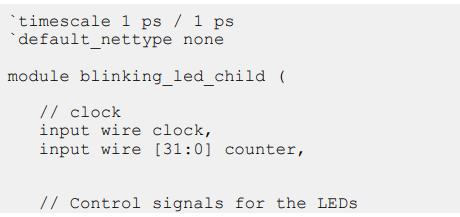

- Ngadamel desain anyar file, blinking_led_child.sv, tur nambahkeun garis handap kode ieu file: skala waktu 1 ps / 1 ps `default_nettype euweuh modul blinking_led_child ( // jam kawat input jam, kawat input [31:0] counter, // sinyal kontrol pikeun LEDs

- Ngaropea blinking_led.sv file pikeun nyambungkeun led_two_on ka bit 23 tina counter ti wewengkon statik, sarta instantiate modul blinking_led_child. Saatos modifikasi, blinking_led.sv Anjeun file kudu muncul saperti kieu:

- Dina ngaropéa sagala rarancang files, recompile proyék ku ngaklik Processing ➤ Mimitian Kompilasi

Lengkah 3: Nyieun Partitions Desain

Anjeun kudu nyieun partisi desain pikeun tiap wewengkon PR nu Anjeun hoyong sawaréh reconfigure. Anjeun tiasa nyiptakeun sajumlah partisi mandiri atanapi daérah PR dina desain anjeun. Tutorial ieu nyiptakeun dua partisi desain pikeun instansi u_blinking_led_child sareng u_blinking_led.

Pikeun nyieun partisi desain pikeun konfigurasi ulang parsial hirarki:

- Klik-katuhu instance u_blinking_led_child dina Project Navigator teras klik Design Partition ➤ Set as Design Partition. Ikon partisi desain nembongan di gigireun unggal conto anu disetél salaku partisi.

Gambar 3. Nyieun Partisi Desain ti Project Navigator

- Pikeun nangtukeun Tipe partisi, klik katuhu u_blinking_led_child instance dina tab Hierarki, klik Design Partition ➤ Reconfigurable. Anjeun ngan bisa nangtukeun Tipe partisi sanggeus netepkeun conto salaku partisi a. Partisi desain nembongan dina Assignments View tab tina Design Partitions Jandela.

angka 4. Desain Partitions Jandela

- Édit nami partisi dina Jandéla Partisi Desain ku ngaklik dua kali nami. Pikeun desain rujukan ieu, ganti ngaran partisi kana pr_partition.

Catetan: Nalika anjeun nyiptakeun partisi, parangkat lunak Intel Quartus Prime otomatis ngahasilkeun nami partisi, dumasar kana nami conto sareng jalur hierarki. Ngaran partisi standar ieu tiasa rupa-rupa sareng unggal conto. - Ulang léngkah 1 jeung 2 pikeun nangtukeun partisi desain reconfigurable kana conto u_blinking_led. Ganti ngaran partisi ieu jadi pr_parent_partition.

Pariksa yén blinking_led.qsf ngandung tugas di handap ieu, pakait jeung partisi desain reconfigurable Anjeun:

Jieun Partitions Desain pikeun Reconfiguration parsial

Lengkah 4: Alokasi Panempatan sareng Wilayah Rute pikeun Partisi PR

Nalika anjeun nyiptakeun révisi dasar, aliran desain PR nganggo alokasi wilayah partisi PR anjeun pikeun nempatkeun inti persona anu aya dina daérah anu ditangtayungan. Pikeun milarian sareng netepkeun wilayah PR dina rencana lantai alat pikeun révisi dasar anjeun:

- Klik-katuhu instance u_blinking_led_child dina Project Navigator teras klik Logic Lock Region ➤ Create New Logic Lock Region. Wewengkon némbongan dina Jandéla Logic Lock Regions.

- Wewengkon panempatan anjeun kedah ngalampirkeun logika blinking_led_child. Pilih wewengkon panempatan ku locating titik dina Chip Nu Ngarencana. Klik-katuhu ngaran wewengkon u_blinking_led_child dina Project Navigator teras klik Locate Node ➤ Locate in Chip Planner.

angka 5. Chip Nu Ngarencana titik lokasi pikeun blinking_led

- Dina jandela Logic Lock Wewengkon, tangtukeun koordinat wilayah panempatan dina kolom Asal. Asalna pakait jeung pojok kénca handap wewengkon. Pikeun example, pikeun set hiji wewengkon panempatan kalawan (X1 Y1) koordinat salaku (69 10), nangtukeun Asal salaku X69_Y10. Parangkat lunak Intel Quartus Prime otomatis ngitung koordinat (X2 Y2) (katuhu luhur) pikeun daérah panempatan, dumasar kana jangkungna sareng lebar anu anjeun pikahoyong.

Catetan: Tutorial ieu nganggo koordinat (X1 Y1) - (69 10), sareng jangkungna sareng rubak 20 pikeun daérah panempatan. Nangtukeun sagala nilai pikeun wewengkon panempatan, disadiakeun yén wewengkon ngawengku logika blinking_led_child. - Aktipkeun pilihan Reserved sareng Inti-Ngan.

- Klik dua kali pilihan Routing Region. Kotak dialog Logic Lock Routing Region Settings nembongan.

- Pilih Maneuh sareng ékspansi pikeun jinis Routing. Milih pilihan ieu otomatis nangtukeun panjang ékspansi 1.

Catetan: Wewengkon routing kudu leuwih badag batan wewengkon panempatan, pikeun nyadiakeun kalenturan tambahan pikeun Fitter nalika mesin ruteu personas béda. - Ulang léngkah 1 -6 pikeun conto u_blinking_led. Panempatan tingkat kolot Ulang léngkah 1 -6 pikeun conto u_blinking_led. Wewengkon panempatan tingkat indungna kedah pinuh ngalampirkeun panempatan tingkat anak sareng daérah rute anu cocog bari ngamungkinkeun rohangan anu cekap pikeun panempatan logika tingkat indungna. Tutorial ieu nganggo koordinat (X1 Y1) - (66 7), jangkungna 47, sareng rubak 26 pikeun daérah panempatan conto u_blinking_led.

Gambar 6. Jandela Wewengkon Konci Logika

Pastikeun yén blinking_led.qsf ngandung tugas-tugas di handap ieu, pakait sareng perencanaan lantai anjeun:

- Floorplan nu Desain Reconfiguration parsial

- Incrementally Ngalaksanakeun Parsial Reconfiguration

Lengkah 5: Nambahkeun Intel Arria 10 Partial Reconfiguration Controller IP Core

- Paké Intel Arria 10 Partial Reconfiguration Controller IP inti pikeun reconfigure partisi PR. Inti IP ieu ngagunakeun JTAG pikeun reconfigure partisi PR. Pikeun nambihan inti Intel Arria 10 Reconfiguration Controller IP inti kana proyék Intel Quartus Prime anjeun:

- Ketik Parsial Reconfiguration dina katalog IP.

- Pikeun ngajalankeun jandela IP Parameter Editor Pro, pilih Intel Arria 10 Partial Reconfiguration Controller IP inti ti perpustakaan IP, tur klik Tambahkeun.

- Dina kotak dialog Varian IP Anyar, ketik pr_ip salaku file nami teras klik Jieun. Anggo parameterisasi standar pikeun pr_ip. Pastikeun yén Aktipkeun JTAG mode debug jeung Aktipkeun freeze pilihan panganteur dihurungkeun, sarta Aktipkeun Avalon-MM pilihan panganteur budak dipareuman.

angka 7. Intel Arria 10 Sabagean Reconfiguration controller IP Core Parameter

- Klik Rengse, sarta kaluar tina editor parameter tanpa ngahasilkeun sistem. Parangkat lunak Intel Quartus Prime nyiptakeun variasi IP pr_ip.ip file, sareng nambihan file kana proyék blinking_led.

Catetan:

- Upami anjeun nyalin pr_ip.ip file ti folder hpr, sacara manual ngédit blinking_led.qsf file ngawengku baris di handap ieu: set_global_assignment -name IP_FILE pr_ip.ip

- Pasang IP_FILE tugas saatos SDC_FILE tugas (jtag.sdc jeung blinking_led.sdc) dina blinking_led.qsf Anjeun file. Pesenan ieu mastikeun konstraining anu pas tina inti IP Reconfiguration Parsial.

Catetan: Pikeun ngadeteksi jam, SDC file pikeun PR IP kudu nuturkeun sagala SDC nu nyiptakeun jam nu ngagunakeun inti IP. Anjeun mempermudah urutan ieu ku mastikeun .ip file pikeun inti PR IP asalna sanggeus sagala .ip files atanapi SDC files dipaké pikeun nyieun jam ieu dina QSF file pikeun révisi proyék Intel Quartus Prime Anjeun. Kanggo inpo nu leuwih lengkep, tingal bagian Watesan Waktu dina Pituduh Pamaké IP Core Konfigurasi Parsial.

Émbaran patali

- Parsial Reconfiguration IP Leyuran Guide pamaké

- Pikeun émbaran ngeunaan Reconfiguration parsial Region Controller IP inti.

- Parsial Reconfiguration IP Core Guide pamaké

- Kanggo inpo tentang watesan waktos.

Ngamutahirkeun Desain Top-Level

Pikeun ngapdet top.SV file kalawan conto PR_IP:

- Pikeun nambahkeun conto PR_IP kana desain tingkat luhur, uncomment blok kode handap di luhur.SV file:

- Pikeun maksakeun palabuhan kaluaran kana logika 1 salami konfigurasi ulang, nganggo kaluaran sinyal kontrol beku tina PR_IP. Sanajan kitu, pikeun niténan LED terus blinking ti partisi PR indungna bari PR programming partisi anak, sinyal kontrol freeze teu mareuman led_two_on. Pastikeun yén pr_led_two_on langsung

- Pikeun napelkeun hiji conto tina standar indungna persona (blinking_led), update top.SV file kalayan blok kode di handap ieu:

angka 8. Parsial Reconfiguration IP Core Pamaduan

Lengkah 6: Nangtukeun Personas

Desain rujukan ieu ngahartikeun lima personas misah pikeun partisi PR indungna jeung anak. Pikeun ngartikeun sareng ngalebetkeun personas dina proyék anjeun:

- Jieun opat SystemVerilog files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv, sarta blinking_led_slow.sv dina diréktori gawé anjeun pikeun lima personas.

Catetan: Lamun anjeun nyieun SystemVerilog files ti Intel Quartus Prime Text Editor, nganonaktipkeun Add file kana pilihan proyék ayeuna, nalika nyimpen files.

Tabél 2. Référénsi Desain Personas

| File Ngaran | Katerangan | Kodeu |

| blinking_led_child.sv | Persona standar pikeun desain tingkat anak |

`skala waktu 1 ps / 1 ps `default_nettype euweuh modul blinking_led_child ( // jam jam kawat input, kawat input [31:0] counter,

// Sinyal kontrol pikeun kawat kaluaran LEDs led_three_on

); localparam COUNTER_TAP = 23; reg led_three_on_r;

napelkeun led_three_on = led_three_on_r; always_ff @(posge jam) dimimitian led_three_on_r <= counter[COUNTER_TAP]; tungtung

modul tungtung |

| dituluykeun… | ||

| File Ngaran | Katerangan | Kodeu |

| blinking_led_child_slow.sv | The

LED_TILU blinks laun |

`skala waktu 1 ps / 1 ps `default_nettype euweuh

modul blinking_led_child_slow (

// jam jam kawat input, kawat input [31:0] counter,

// Sinyal kontrol pikeun kawat kaluaran LEDs led_three_on );

localparam COUNTER_TAP = 27; reg led_three_on_r;

napelkeun led_three_on = led_three_on_r; always_ff @(posge jam) dimimitian led_three_on_r <= counter[COUNTER_TAP]; tungtung

modul tungtung |

| blinking_led_child_empty.sv | The

LED_TILU tetep ON |

`skala waktu 1 ps / 1 ps `default_nettype euweuh

modul blinking_led_child_empty (

// jam jam kawat input, kawat input [31:0] counter,

// Sinyal kontrol pikeun kawat kaluaran LEDs led_three_on

);

// LED aktip low napelkeun led_three_on = 1'b0;

modul tungtung |

| blinking_led_slow.sv | LED_DUA

blinks laun. |

`skala waktu 1 ps / 1 ps `default_nettype euweuh modul blinking_led_slow( // jam jam kawat input, kawat input [31:0] counter,

// Sinyal kontrol pikeun kawat kaluaran LED led_two_on, kawat kaluaran led_three_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; napelkeun led_two_on = led_two_on_r;

// Konter: always_ff @(jam posedge) dimimitian led_two_on_r <= counter[COUNTER_TAP]; tungtung

blinking_led_child u_blinking_led_child( .dipingpin_tilu_asup (dipingpin_tilu_asup), .counter (counter), .jam (jam) |

| File Ngaran | Katerangan | Kodeu |

| );ndmodul |

Lengkah 3: Nyieun Partisi Desain dina kaca 7

Lengkah 7: Nyieun Révisi

Aliran desain PR ngagunakeun fitur révisi proyék dina parangkat lunak Intel Quartus Prime. Desain awal anjeun nyaéta révisi dasar, dimana anjeun nangtukeun wates wilayah statik sareng wilayah anu tiasa dikonfigurasi deui dina FPGA. Tina révisi dasar, anjeun nyiptakeun sababaraha révisi. Révisi ieu ngandung palaksanaan anu béda pikeun daérah PR. Nanging, sadaya révisi palaksanaan PR nganggo panempatan tingkat luhur anu sami sareng hasil routing tina révisi dasar. Pikeun nyusun desain PR, anjeun kedah nyiptakeun révisi palaksanaan PR sareng révisi sintésis pikeun unggal persona. Dina desain rujukan ieu, salian révisi dasar (blinking_led), tilu personas tingkat anak sareng dua personas tingkat kolot ngandung lima révisi sintésis anu misah sareng lima révisi palaksanaan anu misah:

Tabél 3. Révisi pikeun Persona Dua Kolot jeung Persona Tilu Anak

| Révisi Sintésis | Révisi Palaksanaan |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_empty | blinking_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | blinking_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_empty | blinking_led_pr_emma |

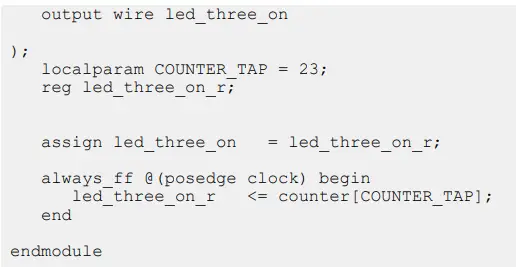

Nyieun Révisi Palaksanaan

Pikeun nyieun révisi palaksanaan PR:

- Pikeun muka kotak dialog Révisi, klik Proyék ➤ Révisi.

- Pikeun nyieun révisi anyar, ganda-klik < >.

- Sebutkeun ngaran Révisi salaku blinking_led_pr_alpha tur pilih blinking_led pikeun Dumasar Révisi.

- Pareuman pilihan Atur salaku révisi ayeuna teras klik OKÉ.

- Nya kitu, jieun blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta, sareng blinking_led_pr_emma révisi, dumasar kana révisi blinking_led.

Catetan: Entong nyetél révisi di luhur salaku révisi ayeuna.

Gambar 9. Nyieun Révisi

Nyieun Sintésis-Ngan Révisi

Pikeun nyieun révisi ngan sintésis pikeun personas, anjeun kedah netepkeun éntitas tingkat luhur sareng SystemVerilog anu saluyu. file pikeun tiap personas:

- Dina parangkat lunak Intel Quartus Prime, klik Proyék ➤ Révisi.

- Jieun révisi blinking_led_default dumasar kana révisi blinking_led. Entong nyetél révisi ieu salaku révisi ayeuna.

- Ngaropea blinking_led_default.qsf file ngawengku tugas di handap ieu:

set_global_assignment -ngaran TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -ngaran SYSTEMVERILOG_FILE - Nya kitu, jieun blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent, sareng blinking_led_parent_slow révisi dumasar kana blinking_led révisi. Entong nyetél révisi ieu salaku révisi ayeuna.

- Apdet blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, sareng blinking_led_parent_slow.qsf files kalawan saluyu maranéhna

TOP_LEVEL_ENTITY sareng SYSTEMVERILOG_FILE tugas:

- Pikeun ngahindarkeun kasalahan sintésis, pastikeun yén révisi sintésis files pikeun partitions anak teu ngandung sagala partisi design, assignments pin, atawa Logic Lock

assignments wewengkon. Ogé, révisi sintésis files pikeun partitions indungna ngan kedah ngandung assignments partisi design keur partitions anak pakait. Hapus tugas ieu, upami aya, dina blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, sareng blinking_led_parent_slow.pdf files

- Lebetkeun tugas di handap ieu dina blinking_led_parent.qsf sareng blinking_led_parent_slow.qsf files:

- Pariksa yén blinking_led.qpf file ngandung révisi di handap ieu, tanpa urutan tinangtu:

- Catetan: Upami anjeun nyalin révisi files ti folder hpr, update sacara manual blinking_led.qpf file kalawan garis kode luhur.

Nangtukeun Tipe Révisi

Anjeun kedah netepkeun jinis révisi pikeun tiap révisi anjeun. Aya tilu jinis révisi:

- Parsial Reconfiguration - Base

- Parsial Reconfiguration - Sintésis persona

- Parsial Reconfiguration - Palaksanaan persona

- Tabel di handap ieu daptar tugas tipe révisi pikeun tiap révisi:

Tabél 4. Jenis Révisi

| Ngaran révisi | Tipe Révisi |

| blinking_led.qsf | Parsial Reconfiguration - Base |

| blinking_led_default.qsf | Parsial Reconfiguration - Sintésis persona |

| blinking_led_child_empty.qsf | Parsial Reconfiguration - Sintésis persona |

| blinking_led_child_slow.qsf | Parsial Reconfiguration - Sintésis persona |

| blinking_led_parent.qsf | Parsial Reconfiguration - Sintésis persona |

| blinking_led_parent_slow.qsf | Parsial Reconfiguration - Sintésis persona |

| blinking_led_pr_alpha.qsf | Parsial Reconfiguration - Palaksanaan persona |

| blinking_led_pr_bravo.qsf | Parsial Reconfiguration - Palaksanaan persona |

| blinking_led_pr_charlie.qsf | Parsial Reconfiguration - Palaksanaan persona |

| blinking_led_pr_delta.qsf | Parsial Reconfiguration - Palaksanaan persona |

| blinking_led_pr_emma.qsf | Parsial Reconfiguration - Palaksanaan persona |

- Klik Project ➤ Révisi. Kotak dialog Révisi nembongan.

- Pilih blinking_led dina kolom Ngaran Révisi, teras klik Atur Ayeuna.

- Klik Larapkeun. Révisi blinking_led muka.

- Pikeun nyetel tipe révisi pikeun blinking_led, klik Assignments ➤ Setélan ➤ Umum.

- Pilih Tipe Révisi salaku Konfigurasi Parsial - Dasar.

- Nya kitu, setel jinis révisi pikeun sapuluh révisi anu sanés, sapertos didaptarkeun dina tabel di luhur.

- Catetan: Anjeun kedah nyetél unggal révisi janten révisi ayeuna sateuacan netepkeun jinis révisi. Pariksa yén unggal .qsf file ngandung tugas di handap ieu:

- Catetan: Tambahkeun setélan Fitter-spésifik nu Anjeun hoyong pake dina palaksanaan PR compile kana révisi palaksanaan persona. Setélan-spésifik Fitter mangaruhan pas persona, tapi teu mangaruhan wewengkon statik diimpor. Anjeun ogé tiasa nambihan setélan khusus sintésis kana révisi sintésis persona individu.

Jieun Révisi pikeun Personas

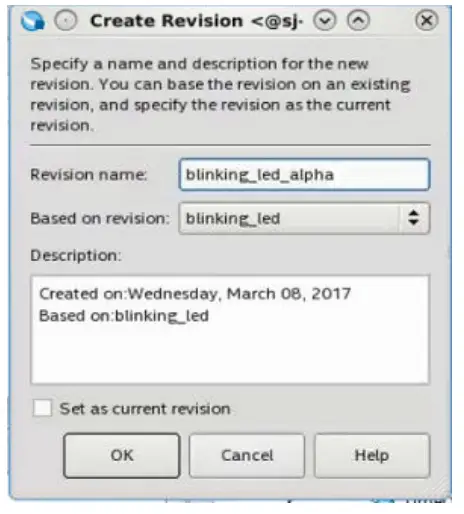

Lengkah 8: Ngahasilkeun Aksara Aliran Konfigurasi Parsial Hierarkis

Pikeun ngahasilkeun skrip aliran konfigurasi ulang parsial hierarki:

- Tina cangkang paréntah Intel Quartus Prime, jieun template aliran ku ngajalankeun paréntah di handap ieu:

- Intel Quartus Prime ngahasilkeun a10_hier_partial_reconfig/flow.tcl file.

- Ganti ngaran anu dihasilkeun a10_hier_partial_reconfig/setup.tcl.example ka a10_hier_partial_reconfig/setup.tcl, sarta ngarobah naskah pikeun nangtukeun detil proyék reconfiguration parsial anjeun:

a. Pikeun ngartikeun nami proyék, ngapdet baris ieu: b. Pikeun nangtukeun révisi dasar, ngapdet baris ieu:

b. Pikeun nangtukeun révisi dasar, ngapdet baris ieu:

- Pikeun nangtukeun unggal révisi palaksanaan rekonfigurasi parsial, sareng nami partisi PR sareng révisi sumber anu ngalaksanakeun révisi, ngapdet baris ieu:

Catetan: Sadaya proyék révisi kedah aya dina diréktori anu sami sareng blinking_led.qpf. Upami teu kitu, ngapdet skrip aliran sasuai.

Lengkah 9: Ngajalankeun Aksara Aliran Konfigurasi Parsial Hierarkis

Pikeun ngajalankeun skrip aliran konfigurasi ulang parsial hierarki:

- Klik Alat ➤ Tcl Scripts. Kotak dialog Tcl Scripts muncul.

- Klik Tambahkeun ka Project, kotektak tur pilih a10_hier_partial_reconfig/flow.tcl.

- Pilih a10_hier_partial_reconfig/flow.tcl dina jandela Perpustakaan, teras klik Run.

Skrip ieu ngajalankeun sintésis pikeun tilu personas. Intel Quartus Prime ngahasilkeun Objék SRAM File (.sof), Objék SRAM Parsial-Masked File (.pmsf), sareng binér atah File (.rbf) pikeun tiap personas.

Catetan: Pikeun ngajalankeun skrip tina cangkang paréntah Intel Quartus Prime, ketik paréntah di handap ieu:

- Kompilasi Desain Konfigurasi Parsial

- Ngagunakeun Parsial Reconfiguration Aliran Script

- Ngonpigurasikeun Aksara Aliran Konfigurasi Parsial

- Ngahasilkeun Programming Files

Lengkah 10: Programming Déwan

Sateuacan anjeun ngamimitian:

- Sambungkeun catu daya ka papan pangembangan Intel Arria 10 SoC.

- Sambungkeun kabel USB Blaster antara port USB PC Anjeun jeung port USB Blaster dina dewan ngembangkeun.

Pikeun ngajalankeun desain dina papan pamekaran Intel Arria 10 SoC:

- Buka software Intel Quartus Prime teras klik Tools ➤ Programmer.

- Dina Programmer, klik Hardware Setup tur pilih USB-Blaster.

- Klik Otomatis Deteksi tur pilih alat, 10AS066N3.

- Pencét OK. Parangkat lunak Intel Quartus Prime ngadeteksi sareng ngapdet Programmer sareng tilu chip FPGA dina papan.

- Pilih alat 10AS066N3, klik Robah File jeung muka blinking_led_pr_alpha.sof file.

- Aktipkeun Program / Konpigurasikeun pikeun blinking_led_pr_alpha.sof file.

- Pencét Mimitian sareng ngantosan bar kamajuan ngahontal 100%.

- Nitenan LEDs dina dewan blinking dina frékuénsi anu sarua sakumaha desain datar aslina.

- Pikeun program ngan wewengkon PR anak, klik katuhu blinking_led_pr_alpha.sof file dina Programmer teras klik Tambahkeun PR Programming File.

- Pilih blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file.

- Nonaktipkeun Program / Konpigurasikeun pikeun blinking_led_pr_alpha.sof file.

- Aktipkeun Program / Konpigurasikeun pikeun blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file tur klik Mimitian. Di papan tulis, perhatikeun LED[0] jeung LED[1] terus kedip-kedip. Nalika bar kamajuan ngahontal 100%, LED[2] kedip-kedip dina laju anu sami, sareng LED[3] kedip-kedip langkung laun.

- Pikeun program duanana wewengkon PR kolot jeung anak,-klik katuhu .rbf file dina Programmer teras klik Robah PR Programing File.

- Pilih blinking_led_pr_delta.pr_parent_partition.rbf file.

- Klik Mimitian. Dina papan tulis, perhatikeun yén LED[0] sareng LED[1] terus kedip-kedip. Lamun bar kamajuan ngahontal 100%, duanana LED[2] jeung LED[3] ngacieupan laun.

- Malikan deui léngkah-léngkah di luhur pikeun ngaprogram deui sacara dinamis ngan daérah PR anak, atanapi daérah PR indungna sareng anak sakaligus.

angka 10. Programming Intel Arria 10 SoC Development Board

Ngarobah hiji Persona Aya

- Anjeun tiasa ngarobih persona anu tos aya, sanaos saatos kompilasi révisi dasar.

- Pikeun example, ngabalukarkeun blinking_led_child_slow persona ka blink malah laun:

- Dina blinking_led_child_slow.sv file, modifikasi parameter COUNTER_TAP tina 27 ka 28.

- Pikeun nyintésis deui sareng ngalaksanakeun deui persona ieu, anjeun kedah nyusun ulang sadaya révisi ngan ukur sintésis sareng révisi palaksanaan anu kapangaruhan ku parobahan éta. Robah skrip setup.tcl pikeun ngalebetkeun garis-garis ieu:

Catetan: Nalika nangtukeun pr_parent_parition pikeun blinking_led_pr_delta révisi, Anjeun ngimpor snapshot ahir persona éta pikeun palaksanaan. Hasilna, palaksanaan logika partisi indungna tetep sarua, bari ngaropéa tur ngalaksanakeun partisi anak pakait.

Catetan: Nalika nangtukeun pr_parent_parition pikeun blinking_led_pr_delta révisi, Anjeun ngimpor snapshot ahir persona éta pikeun palaksanaan. Hasilna, palaksanaan logika partisi indungna tetep sarua, bari ngaropéa tur ngalaksanakeun partisi anak pakait. Paréntah ieu nyintésis ulang révisi sintésis blinking_led_child_slow, teras ngajalankeun kompilasi palaksanaan PR nganggo blinking_led_pr_bravo.

Paréntah ieu nyintésis ulang révisi sintésis blinking_led_child_slow, teras ngajalankeun kompilasi palaksanaan PR nganggo blinking_led_pr_bravo. - Pikeun ngalakukeun kompilasi révisi ngan ukur sintésis, jalankeun paréntah di handap ieu: Paréntah ieu henteu nyusun ulang révisi dasar.

- Pikeun ngalakukeun kompilasi révisi palaksanaan, jalankeun paréntah di handap ieu:

- Paréntah ieu henteu nyusun ulang révisi dasar.

- Turutan léngkah-léngkah dina Lengkah 10: Programming Board dina kaca 22 pikeun ngaprogram RBF anu dihasilkeun file kana FPGA.

Catetan: Pikeun ngahindarkeun ngajalankeun sakabéh alur pikeun unggal révisi, tangtukeun révisi sintésis wungkul jeung révisi palaksanaan dina skrip setup.tcl, tur ngajalankeun naskah.

Nambahkeun Persona Anyar kana Desain

Saatos pinuh kompilasi révisi dasar anjeun, anjeun masih tiasa nambihan personas énggal sareng nyusun individu ieu personas.

Pikeun example, pikeun ngartikeun persona anak anyar pikeun blinking_led_parent_slow, anu mareuman led_three:

- Salin blinking_led_child_empty.sv ka blinking_led_chdild_off.sv.

- Dina blinking_led_child_off.sv file, ngaropéa ngerjakeun, napelkeun led_three_on = 1'b0; pikeun napelkeun led_three_on = 1'b1;. Pastikeun anjeun ngarobah nami modul tina blinking_led_child_empty ka blinking_led_child_off.

- Jieun révisi sintésis anyar, blinking_led_child_off, ku nuturkeun léngkah-léngkah dina Nyieun Révisi Ngan-Sintesis dina kaca 16.

Catetan: Révisi blinking_led_child_off kedah nganggo blinking_led_child_off.sv file. - Jieun révisi palaksanaan anyar, blinking_led_pr_foxtrot, ku nuturkeun léngkah-léngkah dina Nyieun Révisi Palaksanaan dina kaca 15.

- Ngamutahirkeun a10_hier_partial_reconfig/setup.tcl file pikeun nangtukeun palaksanaan PR anyar:

- Kompilkeun ngan ukur sintésis anyar ieu sareng révisi palaksanaan ku ngajalankeun paréntah di handap ieu:

Kanggo inpo lengkep ngeunaan konfigurasi ulang parsial hirarki pikeun alat Intel Arria 10, tingal Nyiptakeun Desain Konfigurasi Parsial dina Jilid 1 tina Buku Panduan Edisi Intel Quartus Prime Pro.

Émbaran patali

- Nyiptakeun Desain Konfigurasi Parsial

- Parsial Reconfiguration Pelatihan Online

Sajarah Révisi Dokumén

Tabél 5. Riwayat Révisi Dokumén

| Vérsi Dokumén | Vérsi Software | Parobahan |

| 2017.11.06 | 17.1.0 | • diropéa dina Syarat Desain Rujukan bagian kalawan versi software

• diropéa dina Desain Rujukan Datar tanpa PR Partitioning inohong kalawan parobahan blok desain • diropéa dina Desain Rujukan Files tabél kalawan informasi dina modul Top_counter.sv • diropéa dina Parsial Reconfiguration IP Core Pamaduan inohong kalawan parobahan blok desain • Diropéa inohong - Desain Partitions Jandela jeung Logika konci Wewengkon Jandela pikeun ngagambarkeun GUI anyar • File robah ngaran • Éditan téks |

| 2017.05.08 | 17.0.0 | Pelepasan awal dokumén |

Dokumén / Sumberdaya

|

intel AN 805 Konfigurasi Parsial Hierarki tina Desain dina Arria 10 SoC Development Board [pdf] Pituduh pamaké AN 805 Hierarki Parsial Reconfiguration of a Desain on Arria 10 SoC Development Board, AN 805, Hierarchical Parsial Reconfiguration of a Design on Arria 10 SoC Development Board, Reconfiguration of a Design on Arria 10 SoC Development Board, Arria 10 SoC Development Board, 10 SoC Déwan Pangwangunan |