intel AN 805 Hierarki Parsial Rekonfigurasi Desain ing Arria 10 SoC Development Board

Tutorial Konfigurasi Sebagean Hierarki kanggo Papan Pangembangan Intel® Arria® 10 SoC

Cathetan aplikasi iki nduduhake ngowahi desain sing prasaja dadi desain sing bisa dikonfigurasi ulang kanthi hierarkis, lan ngleksanakake desain kasebut ing papan pangembangan Intel® Arria® 10 SoC. Hierarchical parsial reconfiguration (HPR) minangka jinis khusus saka konfigurasi ulang parsial (PR), ing ngendi sampeyan ngemot wilayah PR ing wilayah PR liyane. Sampeyan bisa nggawe macem-macem personas kanggo partisi anak lan wong tuwa. Sampeyan nest partisi anak ing partisi induk. Ngonfigurasi ulang partisi anak ora mengaruhi operasi ing wilayah induk utawa statis. Ngonfigurasi ulang partisi induk ora mengaruhi operasi ing wilayah statis, nanging ngganti partisi anak saka wilayah induk kanthi personas partisi anak standar. Metodologi iki efektif ing sistem ing ngendi macem-macem fungsi nuduhake sumber daya piranti FPGA sing padha.

Konfigurasi ulang parsial nyedhiyakake kemajuan ing ngisor iki kanggo desain datar:

- Ngidini konfigurasi ulang desain run-time

- Nambah skalabilitas desain

- Nyuda downtime sistem

- Ndhukung fungsi multiplexing wektu dinamis ing desain

- Ngurangi biaya lan konsumsi daya kanthi nggunakake papan papan sing efisien

- Cathetan:

- Implementasi desain referensi iki mbutuhake kawruh dhasar karo aliran implementasi Intel Quartus® Prime FPGA lan kawruh babagan proyek utama Intel Quartus Prime files.

Informasi sing gegandhengan

- Pandhuan Pangguna Kit Pangembangan Intel Arria 10 SoC

- Konsep Konfigurasi Sebagean

- Alur Desain Konfigurasi Sebagean

- Rekomendasi Desain Konfigurasi Sebagean

- Pertimbangan Desain Konfigurasi Sebagean

Referensi Requirements Desain

Desain referensi iki mbutuhake ing ngisor iki:

- Piranti lunak Intel Quartus Prime Pro Edition versi 17.1 kanggo implementasine desain.

- Kit pangembangan Intel Arria 10 SoC kanggo implementasi FPGA.

Intel Corporation. Kabeh hak dilindhungi undhang-undhang. Intel, logo Intel, lan merek Intel liyane minangka merek dagang saka Intel Corporation utawa anak perusahaan. Intel njamin kinerja produk FPGA lan semikonduktor kanggo specifications saiki miturut babar pisan standar Intel, nanging nduweni hak kanggo owah-owahan ing sembarang produk lan layanan ing sembarang wektu tanpa kabar. Intel ora tanggung jawab utawa tanggung jawab sing muncul saka aplikasi utawa panggunaan informasi, produk, utawa layanan sing diterangake ing kene kajaba sing disepakati kanthi tinulis dening Intel. Pelanggan Intel disaranake njupuk versi paling anyar saka spesifikasi piranti sadurunge ngandelake informasi sing diterbitake lan sadurunge nggawe pesenan kanggo produk utawa layanan.

- Jeneng lan merek liyane bisa diklaim minangka properti wong liya.

Desain referensi liwatview

- Desain referensi iki kasusun saka siji counter 32-bit. Ing tingkat Papan, desain nyambungake jam menyang sumber 50MHz lan nyambungake output kanggo papat LED ing FPGA. Milih output saka counter bit ing urutan tartamtu nyebabake LED kedhip ing frekuensi tartamtu.

Gambar 1. Desain Referensi Datar tanpa Partisi PR

Desain Referensi Files

Tutorial konfigurasi ulang parsial kasedhiya ing lokasi ing ngisor iki: https://github.com/intel/fpga-partial-reconfig

Kanggo ngundhuh tutorial:

- Klik Klone utawa download.

- Klik Unduh ZIP. Unzip FPGA-partial-config-master.zip file.

- Navigasi menyang sub-folder tutorial / a10_soc_devkit_blinking_led_hpr kanggo ngakses desain referensi.

Folder warata kasusun saka ing ngisor iki files:

Tabel 1. Desain Referensi Files

| File jeneng | Katrangan |

| ndhuwur. SV | Tingkat paling dhuwur file ngandhut implementasine flat desain. Modul iki instantiates sub-partisi blinking_led lan modul top_counter. |

| top_counter.sv | Counter 32-bit tingkat ndhuwur sing ngontrol LED [1] langsung. Output kadhaptar saka counter kontrol LED [0], lan uga daya LED [2] lan LED [3] liwat blinking_led modul. |

| blinking_led.sdc | Nemtokake watesan wektu kanggo proyek kasebut. |

| terus… | |

| File jeneng | Katrangan |

| blinking_led.SV | Ing tutorial iki, sampeyan ngowahi modul iki dadi partisi PR induk. Modul nampa output kadhaptar saka modul top_counter, sing ngontrol LED [2] lan LED [3]. |

| blinking_led.qpf | Proyek Intel Quartus Prime file ngemot dhaptar kabeh revisi ing proyek kasebut. |

| blinking_led.qsf | Setelan Intel Quartus Prime file ngemot tugas lan setelan kanggo proyek kasebut. |

Cathetan: Folder hpr ngemot set lengkap files sampeyan nggawe nggunakake cathetan aplikasi iki. Referensi iki files ing sembarang titik sak nglewati.

Gambar 2. Desain Referensi Files

Referensi Desain Walkthrough

Langkah-langkah ing ngisor iki njlèntrèhaké aplikasi saka reconfiguration parsial kanggo desain flat. Tutorial nggunakake piranti lunak Intel Quartus Prime Pro Edition kanggo papan pangembangan Intel Arria 10 SoC:

- Langkah 1: Miwiti ing kaca 6

- Langkah 2: Gawe Submodul Tingkat Bocah ing kaca 6

- Langkah 3: Nggawe Partisi Desain ing kaca 7

- Langkah 4: Alokasi Wilayah Penempatan lan Rute kanggo Partisi PR ing kaca 9

- Langkah 5: Nambahake Intel Arria 10 Partial Reconfiguration Controller IP Core ing kaca 10

- Langkah 6: Nemtokake Persona ing kaca 13

- Langkah 7: Nggawe Revisi ing kaca 15

- Langkah 8: Ngasilake Skrip Aliran Konfigurasi Sebagean Hierarki ing kaca 20

- Langkah 9: Nglakokake Skrip Aliran Konfigurasi Sebagean Hierarki ing kaca 21

- Langkah 10: Pemrograman Papan ing kaca 22

Langkah 1: Miwiti

Kanggo nyalin desain referensi filemenyang lingkungan kerja sampeyan lan ngumpulake desain flat blinking_led:

- Gawe direktori ing lingkungan kerja sampeyan, a10_soc_devkit_blinking_led_hpr.

- Nyalin tutorial sing diundhuh/a10_soc_devkit_blinking_led_hpr/flat sub-folder menyang direktori, a10_soc_devkit_blinking_led_hpr.

- Ing piranti lunak Intel Quartus Prime Pro Edition, klik File ➤ Bukak Project banjur pilih blinking_led.qpf.

- Kanggo ngumpulake desain flat, klik Processing ➤ Mulai Kompilasi.

Langkah 2: Nggawe Sub-modul Tingkat Anak

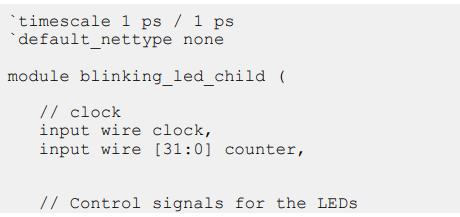

Kanggo ngowahi desain flat iki menyang desain PR hirarkis, sampeyan kudu nggawe sub-modul anak (blinking_led_child. SV) sing nested ing sub-modul tiyang sepah (blinking_led.sv).

- Nggawe desain anyar file, blinking_led_child.sv, lan nambah baris kode ing ngisor iki file: skala waktu 1 ps / 1 ps `default_nettype none module blinking_led_child ( // clock input wire clock, input wire [31:0] counter, // Control signals for the LEDs

- Ngowahi blinking_led.sv file kanggo nyambungake led_two_on kanggo dicokot 23 saka counter saka wilayah statis, lan instantiate modul blinking_led_child. Sawise modifikasi, blinking_led.sv Panjenengan file kudu katon kaya ing ngisor iki:

- Nalika ngowahi kabeh desain files, ngumpulake maneh proyek kanthi ngeklik Processing ➤ Start Compilation

Langkah 3: Nggawe Partisi Desain

Sampeyan kudu nggawe partisi desain kanggo saben wilayah PR sing pengin dikonfigurasi ulang sebagian. Sampeyan bisa nggawe sawetara partisi independen utawa wilayah PR ing desain sampeyan. Tutorial iki nggawe rong partisi desain kanggo u_blinking_led_child lan u_blinking_led.

Kanggo nggawe partisi desain kanggo konfigurasi ulang parsial hirarkis:

- Klik-tengen instance u_blinking_led_child ing Project Navigator lan klik Design Partition ➤ Set as Design Partition. Lambang partisi desain katon ing jejere saben conto sing disetel minangka partisi.

Gambar 3. Nggawe Partisi Desain saka Project Navigator

- Kanggo nemtokake Tipe partisi, klik-tengen conto u_blinking_led_child ing Hierarchy tab, klik Design Partition ➤ Reconfigurable. Sampeyan mung bisa nemtokake Jinis partisi sawise nyetel conto minangka partisi. Partisi desain katon ing Tugas View tab Design Partitions Window.

Gambar 4. Desain Partisi Jendela

- Owahi jeneng partisi ing Design Partitions Window kanthi ngeklik kaping pindho jeneng kasebut. Kanggo desain referensi iki, ganti jeneng partisi dadi pr_partition.

Cathetan: Nalika nggawe partisi, piranti lunak Intel Quartus Prime kanthi otomatis nggawe jeneng partisi, adhedhasar jeneng conto lan path hirarki. Jeneng partisi standar iki bisa beda-beda ing saben conto. - Baleni langkah 1 lan 2 kanggo nemtokake partisi desain reconfigurable kanggo conto u_blinking_led. Ganti jeneng partisi iki dadi pr_parent_partition.

Verifikasi manawa blinking_led.qsf ngemot tugas ing ngisor iki, sing cocog karo partisi desain sing bisa dikonfigurasi maneh:

Nggawe Partisi Desain kanggo Konfigurasi Sebagean

Langkah 4: Alokasi Penempatan lan Wilayah Routing kanggo Partisi PR

Nalika nggawe revisi dhasar, aliran desain PR nggunakake alokasi wilayah partisi PR kanggo nyelehake inti persona sing cocog ing wilayah sing dilindhungi. Kanggo nemokake lan nemtokake wilayah PR ing rencana lantai piranti kanggo revisi dhasar:

- Klik-tengen instance u_blinking_led_child ing Project Navigator banjur klik Logic Lock Region ➤ Create New Logic Lock Region. Wilayah kasebut katon ing Window Logic Lock Regions.

- Wilayah panggonan sampeyan kudu nyakup logika blinking_led_child. Pilih wilayah panggonan kanthi nemokake simpul ing Chip Planner. Klik-tengen jeneng wilayah u_blinking_led_child ing Project Navigator banjur klik Goleki Node ➤ Goleki ing Chip Planner.

Figure 5. Lokasi Chip Planner Node kanggo blinking_led

- Ing jendhela Logic Lock Regions, nemtokake koordinat wilayah panggonan ing kolom Asal. Asal cocog karo pojok kiwa ngisor wilayah kasebut. Kanggo example, kanggo nyetel wilayah panggonan karo (X1 Y1) koordinat minangka (69 10), nemtokake Asal minangka X69_Y10. Piranti lunak Intel Quartus Prime kanthi otomatis ngetung koordinat (X2 Y2) (ndhuwur-tengen) kanggo wilayah panggonan, adhedhasar dhuwur lan jembar sing sampeyan nemtokake.

Cathetan: Tutorial iki nggunakake koordinat (X1 Y1) - (69 10), lan dhuwur lan jembaré 20 kanggo wilayah panggonan. Nemtokake nilai apa wae kanggo wilayah panggonan, yen wilayah kasebut kalebu logika blinking_led_child. - Aktifake pilihan Reserved lan Core-Mung.

- Klik kaping pindho opsi Routing Region. Kothak dialog Logic Lock Routing Region Settings katon.

- Pilih Fixed with expansion kanggo jinis Routing. Milih opsi iki kanthi otomatis nemtokake dawa ekspansi 1.

Cathetan: Wilayah nuntun kudu luwih gedhe tinimbang wilayah panggonan, kanggo nyedhiyani keluwesan ekstra kanggo Fitter nalika engine rute personas beda. - Baleni langkah 1 -6 kanggo conto u_blinking_led. Penempatan tingkat wong tuwa Baleni langkah 1 -6 kanggo conto u_blinking_led. Wilayah penempatan tingkat wong tuwa kudu nutupi wilayah penempatan lan rute tingkat anak sing cocog nalika ngidini papan sing cukup kanggo penempatan logika tingkat wong tuwa. Tutorial iki nggunakake koordinat (X1 Y1) - (66 7), dhuwur 47, lan jembaré 26 kanggo wilayah panggonan saka conto u_blinking_led.

Gambar 6. Jendela Logic Lock Regions

Verifikasi manawa blinking_led.qsf ngemot tugas ing ngisor iki, sing cocog karo rencana lantai sampeyan:

- Floorplan Desain Rekonfigurasi Parsial

- Inkremental Ngleksanakake Konfigurasi Sebagean

Langkah 5: Nambahake Intel Arria 10 Pengontrol Konfigurasi Sebagean IP Core

- Gunakake Intel Arria 10 Partial Reconfiguration Controller IP inti kanggo reconfigure partisi PR. Inti IP iki nggunakake JTAG kanggo reconfigure partisi PR. Kanggo nambah inti IP Pengontrol Konfigurasi Ulang Intel Arria 10 menyang proyek Intel Quartus Prime:

- Ketik Parsial Reconfiguration ing katalog IP.

- Kanggo miwiti jendhela IP Parameter Editor Pro, pilih Intel Arria 10 Partial Reconfiguration Controller IP inti saka perpustakaan IP, lan klik Tambah.

- Ing kothak dialog Varian IP Anyar, ketik pr_ip minangka file jeneng banjur klik Gawe. Gunakake parameterisasi standar kanggo pr_ip. Priksa manawa Aktifake JTAG mode debug lan Aktifake opsi antarmuka beku diuripake, lan Aktifake opsi antarmuka budak Avalon-MM dipateni.

Figure 7. Intel Arria 10 Parameter inti Reconfiguration sebagean Controller IP

- Klik Rampung, lan metu saka editor parameter tanpa ngasilake sistem. Piranti lunak Intel Quartus Prime nggawe variasi IP pr_ip.ip file, lan nambah file menyang proyek blinking_led.

Cathetan:

- Yen sampeyan nyalin pr_ip.ip file saka folder hpr, ngowahi blinking_led.qsf kanthi manual file kanggo nyakup baris ing ngisor iki: set_global_assignment -name IP_FILE pr_ip.ip

- Pasang IP_FILE tugas sawise SDC_FILE tugas (jtag.sdc lan blinking_led.sdc) ing blinking_led.qsf Panjenengan file. Pesenan iki njamin watesan sing cocog saka inti IP Reconfiguration Parsial.

Cathetan: Kanggo ndeteksi jam, SDC file kanggo PR IP kudu tindakake sembarang SDC sing nggawe jam sing nggunakake inti IP. Sampeyan nggampangake pesenan iki kanthi njamin .ip file kanggo inti PR IP rawuh sawise sembarang .ip files utawa SDC files digunakake kanggo nggawe jam iki ing QSF file kanggo revisi proyek Intel Quartus Prime. Kanggo informasi luwih lengkap, waca bagean Watesan Wektu ing Pandhuan Pangguna Inti IP Konfigurasi Ulang Parsial.

Informasi sing gegandhengan

- Pandhuan Pangguna Solusi IP Konfigurasi Ulang Parsial

- Kanggo informasi babagan inti IP Controller Region Reconfiguration parsial.

- Pandhuan Pangguna IP inti konfigurasi ulang parsial

- Kanggo informasi babagan watesan wektu.

Nganyari Desain Top-Level

Kanggo nganyari ndhuwur.SV file karo conto PR_IP:

- Kanggo nambah conto PR_IP menyang desain tingkat paling dhuwur, copot komentar blok kode ing ngisor iki ing sisih ndhuwur.SV file:

- Kanggo meksa port output menyang logika 1 sajrone konfigurasi ulang, gunakake output sinyal kontrol beku saka PR_IP. Nanging, kanggo mirsani LED terus kedhip saka partisi PR induk nalika PR program pemisahan anak, sinyal kontrol beku ora mateni led_two_on. Priksa manawa pr_led_two_on langsung

- Kanggo nemtokake conto saka wong tuwa standar (blinking_led), nganyari top.SV file kanthi blok kode ing ngisor iki:

Gambar 8. Integrasi Inti IP Reconfiguration parsial

Langkah 6: Nemtokake Personas

Desain referensi iki nemtokake limang personas sing kapisah kanggo partisi PR wong tuwa lan anak. Kanggo nemtokake lan nyakup personas ing proyek sampeyan:

- Nggawe papat SystemVerilog files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv, lan blinking_led_slow.sv ing direktori kerja sampeyan kanggo limang personas.

Cathetan: Yen sampeyan nggawe SystemVerilog files saka Intel Quartus Prime Text Editor, mateni Add file kanggo pilihan proyek saiki, nalika nyimpen files.

Tabel 2. Reference Design Personas

| File jeneng | Katrangan | Kode |

| blinking_led_child.sv | Persona standar kanggo desain level bocah |

`skala wektu 1 ps / 1 ps `default_nettype none module blinking_led_child ( // jam jam kawat input, kabel input [31:0] counter,

// Sinyal kontrol kanggo kabel output LED led_three_on

); localparam COUNTER_TAP = 23; reg led_three_on_r;

nemtokake led_three_on = led_three_on_r; always_ff @(jam posedge) diwiwiti led_three_on_r <= counter[COUNTER_TAP]; pungkasan

endmodul |

| terus… | ||

| File jeneng | Katrangan | Kode |

| blinking_led_child_slow.sv | Ing

LED_TELU blinks alon |

`skala wektu 1 ps / 1 ps `default_nettype none

modul blinking_led_child_slow (

// jam jam kawat input, kabel input [31:0] counter,

// Sinyal kontrol kanggo kabel output LED led_three_on );

localparam COUNTER_TAP = 27; reg led_three_on_r;

nemtokake led_three_on = led_three_on_r; always_ff @(jam posedge) diwiwiti led_three_on_r <= counter[COUNTER_TAP]; pungkasan

endmodul |

| blinking_led_child_empty.sv | Ing

LED_TELU tetep ON |

`skala wektu 1 ps / 1 ps `default_nettype none

modul blinking_led_child_empty (

// jam jam kawat input, kabel input [31:0] counter,

// Sinyal kontrol kanggo kabel output LED led_three_on

);

// LED aktif kurang nemtokake led_three_on = 1'b0;

endmodul |

| blinking_led_slow.sv | LED_TWO

blinks alon. |

`skala wektu 1 ps / 1 ps `default_nettype none module blinking_led_slow( // jam jam kawat input, kabel input [31:0] counter,

// Sinyal kontrol kanggo kabel output LED led_two_on, kabel output led_three_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; assign led_two_on = led_two_on_r;

// Konter: always_ff @(jam posedge) wiwiti led_two_on_r <= counter[COUNTER_TAP]; pungkasan

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .counter (counter), .jam (jam) |

| File jeneng | Katrangan | Kode |

| ); modul |

Langkah 3: Nggawe Partisi Desain ing kaca 7

Langkah 7: Nggawe Revisi

Aliran desain PR nggunakake fitur revisi proyek ing piranti lunak Intel Quartus Prime. Desain awal sampeyan minangka revisi dhasar, ing ngendi sampeyan nemtokake wates wilayah statis lan wilayah sing bisa dikonfigurasi maneh ing FPGA. Saka revisi dhasar, sampeyan nggawe pirang-pirang revisi. Revisi kasebut ngemot macem-macem implementasi kanggo wilayah PR. Nanging, kabeh revisi implementasi PR nggunakake panggonan paling dhuwur sing padha lan asil rute saka revisi dhasar. Kanggo nyusun desain PR, sampeyan kudu nggawe revisi implementasi PR lan revisi sintesis kanggo saben persona. Ing desain referensi iki, saliyane revisi dhasar (blinking_led), telung persona tingkat anak lan loro persona tingkat wong tuwa ngemot limang revisi sintesis sing kapisah lan limang revisi implementasine sing kapisah:

Tabel 3. Revisi Persona Loro Wong tuwa lan Persona Anak Telu

| Revisi Sintesis | Revisi Implementasi |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_empty | blinking_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | blinking_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_empty | blinking_led_pr_emma |

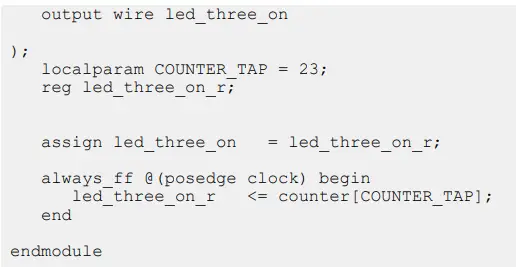

Nggawe Revisi Implementasi

Kanggo nggawe revisi implementasi PR:

- Kanggo mbukak kotak dialog Revisi, klik Project ➤ Revisi.

- Kanggo nggawe revisi anyar, klik kaping pindho < >.

- Nemtokake jeneng Revisi minangka blinking_led_pr_alpha banjur pilih blinking_led kanggo Adhedhasar Revisi.

- Pateni pilihan Setel minangka revisi saiki lan klik OK.

- Kajaba iku, gawe revisi blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta, lan blinking_led_pr_emma, adhedhasar revisi blinking_led.

Cathetan: Aja nyetel revisi ing ndhuwur minangka revisi saiki.

Gambar 9. Nggawe Revisi

Nggawe Revisi Mung Sintesis

Kanggo nggawe revisi mung sintesis kanggo personas, sampeyan kudu nemtokake entitas tingkat paling dhuwur lan SystemVerilog sing cocog. file kanggo saben wong:

- Ing piranti lunak Intel Quartus Prime, klik Project ➤ Revisions.

- Gawe revisi blinking_led_default adhedhasar revisi blinking_led. Aja nyetel revisi iki minangka revisi saiki.

- Ngowahi blinking_led_default.qsf file kalebu tugas ing ngisor iki:

set_global_assignment -jeneng TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -name SYSTEMVERILOG_FILE - Kajaba iku, gawe revisi blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent, lan blinking_led_parent_slow adhedhasar revisi blinking_led. Aja nyetel revisi iki minangka revisi saiki.

- Nganyari blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, lan blinking_led_parent_slow.qsf files karo sing cocog

TOP_LEVEL_ENTITY lan SYSTEMVERILOG_FILE tugas:

- Kanggo ngindhari kesalahan sintesis, priksa manawa revisi sintesis files kanggo partisi anak ora ngemot partisi desain, tugas pin, utawa Kunci Logika

tugas wilayah. Uga, revisi sintesis files kanggo partisi induk mung kudu ngemot tugas partisi desain kanggo partisi anak sing cocog. Mbusak tugas iki, yen ana, ing blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, lan blinking_led_parent_slow.pdf files

- Kalebu tugas ing ngisor iki ing blinking_led_parent.qsf lan blinking_led_parent_slow.qsf files:

- Verifikasi manawa blinking_led.qpf file ngemot revisi ing ngisor iki, tanpa urutan tartamtu:

- Cathetan: Yen sampeyan nyalin revisi files saka folder hpr, nganyari kanthi manual blinking_led.qpf file kanthi baris kode ing ndhuwur.

Nemtokake Tipe Revisi

Sampeyan kudu nemtokake jinis revisi kanggo saben revisi sampeyan. Ana telung jinis revisi:

- Konfigurasi ulang parsial - Base

- Konfigurasi Sebagean - Sintesis Persona

- Konfigurasi ulang parsial - Implementasi Persona

- Tabel ing ngisor iki nampilake tugas jinis revisi kanggo saben revisi:

Tabel 4. Jinis Revisi

| Jeneng Revisi | Jinis Revisi |

| blinking_led.qsf | Konfigurasi ulang parsial - Base |

| blinking_led_default.qsf | Konfigurasi Sebagean - Sintesis Persona |

| blinking_led_child_empty.qsf | Konfigurasi Sebagean - Sintesis Persona |

| blinking_led_child_slow.qsf | Konfigurasi Sebagean - Sintesis Persona |

| blinking_led_parent.qsf | Konfigurasi Sebagean - Sintesis Persona |

| blinking_led_parent_slow.qsf | Konfigurasi Sebagean - Sintesis Persona |

| blinking_led_pr_alpha.qsf | Konfigurasi ulang parsial - Implementasi Persona |

| blinking_led_pr_bravo.qsf | Konfigurasi ulang parsial - Implementasi Persona |

| blinking_led_pr_charlie.qsf | Konfigurasi ulang parsial - Implementasi Persona |

| blinking_led_pr_delta.qsf | Konfigurasi ulang parsial - Implementasi Persona |

| blinking_led_pr_emma.qsf | Konfigurasi ulang parsial - Implementasi Persona |

- Klik Project ➤ Revisions. Kothak dialog Revisi katon.

- Pilih blinking_led ing kolom Jeneng Revisi, banjur klik Setel Saiki.

- Klik Apply. Revisi blinking_led mbukak.

- Kanggo nyetel jinis revisi kanggo blinking_led, klik Tugas ➤ Setelan ➤ Umum.

- Pilih Revision Type as Partial Reconfiguration – Base.

- Kajaba iku, atur jinis revisi kanggo sepuluh revisi liyane, kaya sing kadhaptar ing tabel ing ndhuwur.

- Cathetan: Sampeyan kudu nyetel saben revisi minangka revisi saiki sadurunge nemtokake jinis revisi. Priksa manawa saben .qsf file ngemot tugas ing ngisor iki:

- Cathetan: Tambah setelan khusus Fitter sing pengin digunakake ing implementasi PR kompilasi menyang revisi implementasi persona. Setelan khusus Fitter mengaruhi pas persona, nanging ora mengaruhi wilayah statis diimpor. Sampeyan uga bisa nambah setelan khusus sintesis menyang revisi sintesis persona individu.

Nggawe Revisi kanggo Personas

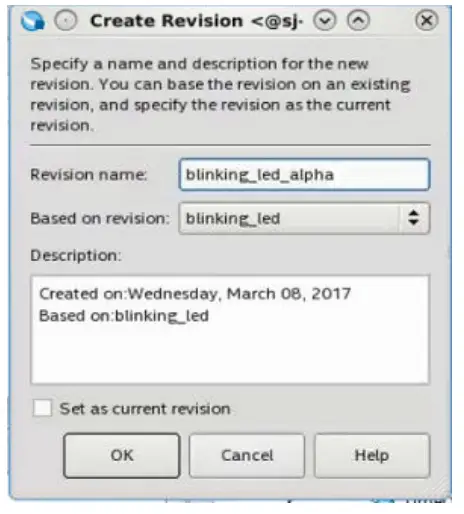

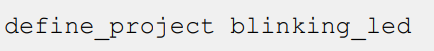

Langkah 8: Ngasilake Skrip Aliran Konfigurasi Sebagean Hierarkis

Kanggo ngasilake skrip alur konfigurasi ulang parsial hirarkis:

- Saka cangkang printah Intel Quartus Prime, gawe cithakan aliran kanthi nglakokake printah ing ngisor iki:

- Intel Quartus Prime ngasilake a10_hier_partial_reconfig/flow.tcl file.

- Ganti jeneng sing digawe a10_hier_partial_reconfig/setup.tcl.example menyang a10_hier_partial_reconfig/setup.tcl, lan ngowahi script kanggo nemtokake rincian proyek reconfiguration parsial Panjenengan:

a. Kanggo nemtokake jeneng proyek, nganyari baris ing ngisor iki: b. Kanggo nemtokake revisi dhasar, nganyari baris ing ngisor iki:

b. Kanggo nemtokake revisi dhasar, nganyari baris ing ngisor iki:

- Kanggo nemtokake saben revisi implementasi konfigurasi ulang parsial, bebarengan karo jeneng partisi PR lan revisi sumber sing ngleksanakake revisi, nganyari baris ing ngisor iki:

Cathetan: Kabeh proyek revisi kudu ana ing direktori sing padha karo blinking_led.qpf. Yen ora, nganyari script aliran kasebut.

Langkah 9: Nglakokake Skrip Aliran Konfigurasi Sebagean Hierarkis

Kanggo mbukak skrip alur konfigurasi ulang parsial hierarkis:

- Klik Tools ➤ Tcl Scripts. Kothak dialog Tcl Scripts katon.

- Klik Tambah kanggo Project, nelusuri lan pilih a10_hier_partial_reconfig/flow.tcl.

- Pilih a10_hier_partial_reconfig/flow.tcl ing panel Libraries, lan klik Run.

Skrip iki nglakokake sintesis kanggo telung personas. Intel Quartus Prime ngasilake Obyek SRAM File (.sof), Obyek SRAM Partial-Masked File (.pmsf), lan Biner Mentah File (.rbf) kanggo saben personas.

Cathetan: Kanggo mbukak skrip saka cangkang perintah Intel Quartus Prime, ketik printah ing ngisor iki:

- Kompilasi Desain Konfigurasi Sebagean

- Nggunakake Skrip Aliran Konfigurasi Ulang Parsial

- Konfigurasi Skrip Aliran Konfigurasi Ulang Parsial

- Generate Pemrograman Files

Langkah 10: Pemrograman Dewan

Sadurunge miwiti:

- Sambungake sumber daya menyang papan pangembangan Intel Arria 10 SoC.

- Sambungake kabel USB Blaster ing antarane port USB PC lan port USB Blaster ing papan pangembangan.

Kanggo mbukak desain ing papan pangembangan Intel Arria 10 SoC:

- Bukak piranti lunak Intel Quartus Prime banjur klik Tools ➤ Programmer.

- Ing Programmer, klik Hardware Setup lan pilih USB-Blaster.

- Klik Deteksi Otomatis banjur pilih piranti, 10AS066N3.

- Klik OK. Piranti lunak Intel Quartus Prime ndeteksi lan nganyari Programmer kanthi telung chip FPGA ing papan kasebut.

- Pilih piranti 10AS066N3, klik Ganti File lan mbukak blinking_led_pr_alpha.sof file.

- Aktifake Program / Konfigurasi kanggo blinking_led_pr_alpha.sof file.

- Klik Mulai lan ngenteni bar kemajuan tekan 100%.

- Mirsani LED ing Papan blinking ing frekuensi padha karo desain flat asli.

- Kanggo program mung wilayah PR anak, klik-tengen ing blinking_led_pr_alpha.sof file di Programmer dan klik Add PR Programming File.

- Pilih blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file.

- Pateni Program / Konfigurasi kanggo blinking_led_pr_alpha.sof file.

- Aktifake Program / Konfigurasi kanggo blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file lan klik Mulai. Ing papan, deleng LED[0] lan LED[1] terus kedhip. Nalika garis kemajuan tekan 100%, LED[2] kedhip kanthi tingkat sing padha, lan LED[3] kedhip luwih alon.

- Kanggo program wilayah PR wong tuwa lan anak, klik-tengen ing .rbf file ing Programmer lan klik Change PR Programing File.

- Pilih blinking_led_pr_delta.pr_parent_partition.rbf file.

- Klik Mulai. Ing papan, deleng yen LED[0] lan LED[1] terus kedhip. Nalika garis kemajuan tekan 100%, LED[2] lan LED[3] kedhip luwih alon.

- Baleni langkah-langkah ing ndhuwur kanggo program maneh kanthi dinamis mung wilayah PR anak, utawa wilayah PR wong tuwa lan anak bebarengan.

Gambar 10. Pemrograman Papan Pangembangan Intel Arria 10 SoC

Ngowahi Persona sing Ana

- Sampeyan bisa ngganti persona sing wis ana, sanajan sawise ngrampungake revisi dhasar.

- Kanggo example, kanggo nimbulaké blinking_led_child_slow persona kanggo kedhip luwih alon:

- Ing blinking_led_child_slow.sv file, ngowahi parameter COUNTER_TAP saka 27 dadi 28.

- Kanggo nyintesis maneh lan ngleksanakake persona iki, sampeyan kudu nglumpukake kabeh revisi mung sintesis lan revisi implementasi sing kena pengaruh owah-owahan kasebut. Owahi skrip setup.tcl kanggo nyakup baris ing ngisor iki:

Cathetan: Nalika nemtokake pr_parent_parition kanggo revisi blinking_led_pr_delta, sampeyan ngimpor gambar asli saka persona kasebut kanggo implementasine. Akibaté, implementasi logika partisi induk tetep padha, nalika ngowahi lan ngleksanakake partisi anak sing cocog.

Cathetan: Nalika nemtokake pr_parent_parition kanggo revisi blinking_led_pr_delta, sampeyan ngimpor gambar asli saka persona kasebut kanggo implementasine. Akibaté, implementasi logika partisi induk tetep padha, nalika ngowahi lan ngleksanakake partisi anak sing cocog. Printah iki re-synthesizes revisi sintesis blinking_led_child_slow, lan banjur mbukak implementasine PR kompilasi nggunakake blinking_led_pr_bravo.

Printah iki re-synthesizes revisi sintesis blinking_led_child_slow, lan banjur mbukak implementasine PR kompilasi nggunakake blinking_led_pr_bravo. - Kanggo nindakake kompilasi revisi mung sintesis, jalanake printah ing ngisor iki: Printah iki ora nyusun ulang revisi dhasar.

- Kanggo nindakake kompilasi revisi implementasine, jalanake printah ing ngisor iki:

- Printah iki ora ngumpulake maneh revisi dhasar.

- Tindakake langkah-langkah ing Langkah 10: Programming Board ing kaca 22 kanggo program RBF asil file menyang FPGA.

Cathetan: Kanggo ngindhari kabeh aliran kanggo saben revisi, netepake revisi mung sintesis lan revisi implementasine ing skrip setup.tcl, banjur jalanake skrip kasebut.

Nambahake Persona Anyar ing Desain

Sawise ngrampungake revisi dhasar, sampeyan isih bisa nambah personas anyar lan ngumpulake personas kasebut kanthi individu.

Kanggo example, kanggo nemtokake persona anak anyar kanggo blinking_led_parent_slow, sing mateni led_three:

- Nyalin blinking_led_child_empty.sv menyang blinking_led_chdild_off.sv.

- Ing blinking_led_child_off.sv file, ngowahi tugas, nemtokake led_three_on = 1'b0; kanggo nemtokake led_three_on = 1'b1;. Priksa manawa sampeyan ngganti jeneng modul saka blinking_led_child_empty dadi blinking_led_child_off.

- Gawe revisi sintesis anyar, blinking_led_child_off, kanthi tindakake langkah-langkah ing Nggawe Revisi Mung Sintesis ing kaca 16.

Cathetan: Revisi blinking_led_child_off kudu nggunakake blinking_led_child_off.sv file. - Gawe revisi implementasi anyar, blinking_led_pr_foxtrot, kanthi tindakake langkah-langkah ing Nggawe Revisi Implementasi ing kaca 15.

- Nganyari a10_hier_partial_reconfig/setup.tcl file kanggo nemtokake implementasi PR anyar:

- Kompilasi mung sintesis anyar lan revisi implementasine kanthi nglakokake printah ing ngisor iki:

Kanggo informasi lengkap babagan konfigurasi ulang sebagean hirarki kanggo piranti Intel Arria 10, waca Nggawe Desain Konfigurasi Sebagean ing Volume 1 saka Buku Pegangan Intel Quartus Prime Pro Edition.

Informasi sing gegandhengan

- Nggawe Desain Konfigurasi Sebagean

- Pelatihan Online Konfigurasi Ulang Parsial

Riwayat Revisi Dokumen

Tabel 5. Riwayat Revisi Dokumen

| Versi Dokumen | Versi Piranti Lunak | Owah-owahan |

| 2017.11.06 | 17.1.0 | • Dianyari ing Referensi Requirements Desain bagean karo versi piranti lunak

• Dianyari ing Desain Referensi Datar tanpa Partisi PR tokoh karo owah-owahan blok desain • Dianyari ing Desain Referensi Files tabel karo informasi ing modul Top_counter.sv • Dianyari ing Integrasi IP inti konfigurasi ulang parsial tokoh karo owah-owahan blok desain • Dianyari angka - Desain Partisi Jendela lan Jendela Wilayah Kunci Logika kanggo nggambarake GUI anyar • File owah-owahan jeneng • Suntingan teks |

| 2017.05.08 | 17.0.0 | Rilis awal saka dokumen |

Dokumen / Sumber Daya

|

intel AN 805 Hierarki Parsial Rekonfigurasi Desain ing Arria 10 SoC Development Board [pdf] Pandhuan pangguna AN 805 Hierarki Parsial Rekonfigurasi Desain ing Arria 10 SoC Development Board, AN 805, Hierarkis Parsial Reconfiguration saka Desain ing Arria 10 SoC Development Board, Reconfiguration saka Desain ing Arria 10 SoC Development Board, Arria 10 SoC Development Board, 10 SoC Papan Pangembangan |