intel AN 805 د Arria 10 SoC پراختیایی بورډ کې د ډیزاین جزوی بیا تنظیم کول

د Intel® Arria® 10 SoC پرمختیایي بورډ لپاره د هراړخیز جزوي بیا تنظیم کولو لارښود

د دې غوښتنلیک یادښت ښیې چې د ساده ډیزاین بدلول په ترتیب سره په جزوي ډول د بیا تنظیم وړ ډیزاین ته بدلول ، او د Intel® Arria® 10 SoC پراختیایی بورډ کې ډیزاین پلي کول ښیې. هراړخیز جزوي بیا تنظیم کول (HPR) یو ځانګړی ډول جزوي بیا تنظیم (PR) دی ، چیرې چې تاسو د PR سیمه په بل PR سیمه کې لرئ. تاسو کولی شئ د ماشوم او والدینو دواړو برخو لپاره ډیری شخصیتونه جوړ کړئ. تاسو د ماشوم ویشونه د دوی په والدینو برخو کې ځړول. د ماشوم د برخې بیا تنظیم کول په مور او پلار یا جامد سیمو کې عملیات اغیزه نه کوي. د مورنۍ برخې بیا تنظیم کول په جامد سیمه کې په عملیاتو اغیزه نه کوي، مګر د اصلي سیمې د ماشومانو برخې د ډیفالټ ماشوم برخې برخې سره بدلوي. دا میتودولوژي په سیسټمونو کې مؤثره ده چیرې چې ډیری دندې د ورته FPGA وسیلې سرچینې شریکوي.

جزوي بیا تنظیم کول د فلیټ ډیزاین ته لاندې پرمختګونه وړاندې کوي:

- د چلولو وخت ډیزاین بیا تنظیمولو ته اجازه ورکوي

- د ډیزاین اندازه کولو وړتیا زیاتوي

- د سیسټم وخت کموي

- په ډیزاین کې د متحرک وخت - ملټيپلیکسینګ افعال ملاتړ کوي

- د تختې ځای د موثر استعمال له لارې لګښت او د بریښنا مصرف کموي

- یادونه:

- د دې حوالې ډیزاین پلي کول د Intel Quartus® Prime FPGA پلي کولو جریان او د لومړني Intel Quartus Prime پروژې پوهه سره لومړني پیژندګلو ته اړتیا لري. files.

اړوند معلومات

- د Intel Arria 10 SoC پراختیایی کټ کارونکي لارښود

- د جزوي بیا تنظیم کولو مفهوم

- د جزوی بیا تنظیم کولو ډیزاین جریان

- د جزوی بیا تنظیم کولو ډیزاین وړاندیزونه

- د جزوی بیا تنظیم کولو ډیزاین نظرونه

د حوالې ډیزاین اړتیاوې

د دې حوالې ډیزاین لاندې ته اړتیا لري:

- د ډیزاین پلي کولو لپاره د Intel Quartus Prime Pro Edition سافټویر نسخه 17.1.

- د FPGA پلي کولو لپاره د Intel Arria 10 SoC پرمختیا کټ.

Intel Corporation. ټول حقونه خوندي دي. Intel، د Intel لوگو، او د Intel نورې نښې د Intel Corporation یا د هغې د فرعي شرکتونو سوداګریزې نښې دي. Intel د خپل FPGA او سیمیکمډکټر محصولاتو فعالیت د Intel معیاري تضمین سره سم اوسني مشخصاتو ته تضمینوي، مګر دا حق خوندي کوي چې په هر وخت کې پرته له خبرتیا څخه په هر محصول او خدماتو کې بدلون راولي. Intel هیڅ مسؤلیت یا مسؤلیت په غاړه نه اخلي چې د غوښتنلیک یا د کوم معلوماتو، محصول، یا خدماتو کارولو څخه رامینځته کیږي چې دلته تشریح شوي پرته له دې چې د Intel لخوا په لیکلي ډول موافقه شوې وي. د انټیل پیرودونکو ته مشوره ورکول کیږي چې د وسیلې ځانګړتیاو وروستۍ نسخه ترلاسه کړي مخکې لدې چې په کوم خپاره شوي معلوماتو تکیه وکړي او د محصولاتو یا خدماتو لپاره امر کولو دمخه.

- نور نومونه او نښې ممکن د نورو ملکیت په توګه ادعا شي.

د حوالې ډیزاین اوورview

- د دې حوالې ډیزاین د یو 32-bit کاونټر څخه جوړ دی. د بورډ په کچه، ډیزاین ساعت د 50MHz سرچینې سره نښلوي او محصول په FPGA کې څلور LEDs سره نښلوي. په یو ځانګړي ترتیب کې د کاونټر بټونو څخه د محصول غوره کول د دې لامل کیږي چې LEDs په ځانګړي فریکونسۍ کې ړنګ شي.

انځور 1. د فلیټ حوالې ډیزاین د PR ویشلو پرته

د حوالې ډیزاین Files

د جزوي بیا تنظیم کولو ښوونه په لاندې ځای کې شتون لري: https://github.com/intel/fpga-partial-reconfig

د ټیوټوریل ډاونلوډ کولو لپاره:

- کلون کلیک وکړئ یا ډاونلوډ کړئ.

- زپ ډاونلوډ کړئ کلیک وکړئ. د FPGA-partial-config-master.zip خلاص کړئ file.

- د حوالې ډیزاین ته د لاسرسي لپاره درسونو/a10_soc_devkit_blinking_led_hpr فرعي فولډر ته لاړشئ.

فلیټ فولډر له لاندې څخه جوړ دی files:

جدول 1. د حوالې ډیزاین Files

| File نوم | تفصیل |

| پورته SV | د لوړې کچې file د ډیزاین فلیټ پلي کول شامل دي. دا ماډل د blinking_led sub-partition او top_counter ماډل انسټاګرام کوي. |

| top_counter.sv | د لوړې کچې 32-bit کاونټر چې LED [1] مستقیم کنټرولوي. د کاونټر ثبت شوی محصول LED[0] کنټرولوي، او همدارنګه د Blinking_led ماډل له لارې LED[2] او LED[3] ته ځواک ورکوي. |

| blinking_led.sdc | د پروژې لپاره د وخت محدودیتونه تعریفوي. |

| ادامه… | |

| File نوم | تفصیل |

| blinking_led.SV | په دې ټیوټوریل کې، تاسو دا ماډل د والدین PR برخې ته بدل کړئ. ماډل د top_counter ماډل راجستر شوي محصول ترلاسه کوي، کوم چې LED [2] او LED [3] کنټرولوي. |

| blinking_led.qpf | د Intel Quartus Prime پروژه file په پروژه کې د ټولو بیاکتنې لیست لري. |

| blinking_led.qsf | د Intel Quartus Prime ترتیبات file د پروژې لپاره دندې او ترتیبات لري. |

یادونه: د hpr فولډر بشپړ سیټ لري fileتاسو د دې غوښتنلیک یادښت په کارولو سره جوړ کړئ. دې ته مراجعه وکړئ files په هر وخت کې د تګ په جریان کې.

شکل 2. د حوالې ډیزاین Files

د حوالې ډیزاین واک تھرو

لاندې مرحلې د فلیټ ډیزاین لپاره د جزوي بیا تنظیم کولو غوښتنلیک تشریح کوي. ټیوټوریل د Intel Arria 10 SoC پراختیایی بورډ لپاره د Intel Quartus Prime Pro Edition سافټویر کاروي:

- لومړی ګام: په 6 پاڼه کې پیل کول

- لومړی ګام: په 6 پاڼه کې د ماشوم کچې فرعي ماډل جوړ کړئ

- لومړی ګام: په 7 پاڼه کې د ډیزاین برخې جوړول

- لومړی ګام: په 9 پاڼه کې د PR برخې لپاره د ځای پرځای کولو او د لارې ټاکلو سیمه

- لومړی ګام: په 10 پاڼه کې د Intel Arria 10 جزوی بیا تنظیم کولو کنټرولر IP کور اضافه کول

- لومړی ګام: د اشخاصو تعریف په 13 پاڼه کې

- لومړی ګام: په 15 پاڼه کې بیاکتنې جوړول

- لومړی ګام: په 20 مخ کې د حیواني جزوي بیا تنظیم کولو جریان سکریپټ رامینځته کول

- لومړی ګام: په 21 مخ کې د هییررکیکل جزوی بیا تنظیم کولو فلو سکریپټ چلول

- لومړی ګام: په 22 پاڼه کې د بورډ پروګرام کول

1 ګام: پیل کول

د حوالې ډیزاین کاپي کولو لپاره fileخپل کاري چاپیریال ته ورشئ او د blinking_led فلیټ ډیزاین ترتیب کړئ:

- په خپل کاري چاپیریال کې یو لارښود جوړ کړئ، a10_soc_devkit_blinking_led_hpr.

- ډاونلوډ شوي ټیوټوریلونه/a10_soc_devkit_blinking_led_hpr/flat فرعي فولډر ډایرکټر ته کاپي کړئ، a10_soc_devkit_blinking_led_hpr.

- د Intel Quartus Prime Pro Edition سافټویر کې، کلیک وکړئ File ➤ پروژه پرانیزئ او blinking_led.qpf غوره کړئ.

- د فلیټ ډیزاین تالیف کولو لپاره، کلیک وکړئ پروسس کول ➤ تالیف پیل کړئ.

2 ګام: د ماشوم کچې فرعي ماډل جوړول

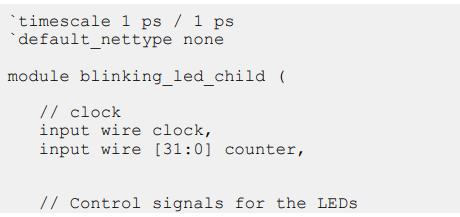

د دې فلیټ ډیزاین په درجه بندي PR ډیزاین بدلولو لپاره، تاسو باید د ماشوم فرعي ماډل (blinking_led_child. SV) جوړ کړئ چې د اصلي فرعي ماډل (blinking_led.sv) کې ځای پر ځای شوی وي.

- یو نوی ډیزاین جوړ کړئ file, blinking_led_child.sv، او په دې کې د کوډ لاندې کرښې اضافه کړئ file: timescale 1 ps / 1 ps `default_nettype none module blinking_led_child ( // د ساعت د ننوتلو تار ساعت، د انپټ تار [31:0] کاونټر، // د LEDs لپاره د کنټرول سیګنالونه

- blinking_led.sv بدل کړئ file د جامد سیمې څخه د کاونټر بټ 23 سره led_two_on وصل کړئ او د blinking_led_child ماډل انسټیټیوټ کړئ. د تعدیلاتو وروسته، ستاسو blinking_led.sv file باید په لاندې ډول څرګند شي:

- په ټول ډیزاین کې بدلون files، د پروسس کولو ➤ تالیف پیل کړئ په کلیک کولو سره پروژه بیا تالیف کړئ

3 ګام: د ډیزاین برخې جوړول

تاسو باید د هرې PR سیمې لپاره ډیزاین برخې رامینځته کړئ چې تاسو غواړئ په جزوي ډول تنظیم کړئ. تاسو کولی شئ په خپل ډیزاین کې هر ډول خپلواکې برخې یا PR سیمې رامینځته کړئ. دا ټیوټوریل د u_blinking_led_child او u_blinking_led مثالونو لپاره دوه ډیزاین برخې جوړوي.

د هراړخیز جزوی بیا تنظیم کولو لپاره د ډیزاین برخې جوړولو لپاره:

- د پروژې نیویګیټر کې د u_blinking_led_child مثال ښي کلیک وکړئ او د ډیزاین پارشن کلیک وکړئ ➤ د ډیزاین برخې په توګه تنظیم کړئ. د ډیزاین برخې آیکون د هرې بیلګې تر څنګ ښکاري چې د برخې په توګه ټاکل شوی.

شکل 3. د پروژې نیویګیټر څخه د ډیزاین برخې جوړول

- د تقسیم ډول تعریفولو لپاره، په هیرارچي ټب کې د u_blinking_led_child مثال ښي کلیک وکړئ، د ډیزاین برخې ➤ د بیا تنظیم وړ کلیک وکړئ. تاسو کولی شئ یوازې د برخې په توګه د مثال تنظیم کولو وروسته د برخې ډول تعریف کړئ. د ډیزاین برخه په دنده کې ښکاري View د ډیزاین برخې کړکۍ ټب.

شکل 4. د ډیزاین برخې کړکۍ

- د ډیزاین برخې کړکۍ کې د برخې نوم په نوم دوه ځله کلیک کولو سره سم کړئ. د دې حوالې ډیزاین لپاره، د برخې نوم pr_partition ته بدل کړئ.

یادونه: کله چې تاسو یوه برخه جوړه کړئ، د Intel Quartus Prime سافټویر په اوتومات ډول د برخې نوم رامینځته کوي، د مثال نوم او درجه بندي لارې پراساس. د دې ډیفالټ برخې نوم د هرې بیلګې سره توپیر کولی شي. - 1 او 2 مرحلې تکرار کړئ ترڅو د u_blinking_led مثال ته د بیا تنظیم کولو وړ ډیزاین برخې وټاکئ. د دې برخې نوم pr_parent_partition ته بدل کړئ.

تایید کړئ چې blinking_led.qsf لاندې دندې لري، ستاسو د بیا تنظیم وړ ډیزاین برخې سره مطابقت لري:

د جزوی بیا تنظیم کولو لپاره ډیزاین پارټیشنونه جوړ کړئ

لومړی ګام: د PR برخو لپاره د ځای پرځای کولو او روټینګ سیمه تخصیص کول

کله چې تاسو د اساس بیاکتنه رامینځته کړئ ، د PR ډیزاین جریان ستاسو د PR برخې برخې تخصیص کاروي ترڅو اړونده شخصي کور په خوندي سیمه کې ځای په ځای کړي. ستاسو د بیس بیاکتنې لپاره د وسیلې فرش پلان کې د PR سیمه موندلو او ټاکلو لپاره:

- د پروژې نیویګیټر کې د u_blinking_led_child مثال ښي کلیک وکړئ او د منطق لاک سیمه کلیک وکړئ ➤ نوی منطق لاک سیمه رامینځته کړئ. سیمه د منطق لاک سیمه کړکۍ کې ښکاري.

- ستاسو د ځای پرځای کولو سیمه باید د blinking_led_child منطق تړلی وي. په چپ پلانر کې د نوډ په موندلو سره د ځای پرځای کولو سیمه غوره کړئ. د پروژې نیویګیټر کې د u_blinking_led_child سیمې نوم ښیې کلیک وکړئ او په چپ پلانر کې د موندلو نوډ کلیک وکړئ.

شکل 5. د چپ پلانر نوډ موقعیت د blinking_led لپاره

- د منطق لاک سیمه کړکۍ کې، د ځای ځای پرځای کولو سیمه همغږي د اصلي کالم کې مشخص کړئ. اصليت د سیمې لاندې کیڼ اړخ ته ورته دی. د مثال لپارهample، د (X1 Y1) همغږي د (69 10) سره د ځای پرځای کولو سیمه ټاکلو لپاره، د X69_Y10 په توګه اصلي ځای مشخص کړئ. د Intel Quartus Prime سافټویر په اوتومات ډول د ځای پرځای کولو سیمې لپاره (X2 Y2) همغږي (پورته ښیې) محاسبه کوي ، د هغه لوړوالي او عرض پراساس چې تاسو یې مشخص کوئ.

یادونه: دا ټیوټوریل (X1 Y1) همغږي کاروي - (69 10)، او د ځای پرځای کولو سیمې لپاره د 20 لوړوالی او عرض. د ځای پرځای کولو سیمې لپاره کوم ارزښت تعریف کړئ ، په دې شرط چې سیمه د blinking_led_child منطق پوښي. - ریزرو شوي او یوازې اصلي اختیارونه فعال کړئ.

- د روټینګ سیمه اختیار دوه ځله کلیک وکړئ. د منطق لاک روټینګ سیمې ترتیباتو ډیالوګ بکس څرګندیږي.

- د روټینګ ډول لپاره د توسیع سره فکسډ غوره کړئ. د دې اختیار غوره کول په اتوماتيک ډول د 1 توسیع اوږدوالی ګماري.

یادونه: د روټینګ ساحه باید د ځای پرځای کولو ساحې څخه لویه وي، ترڅو د فټر لپاره اضافي انعطاف چمتو کړي کله چې انجن مختلف اشخاصو ته لاره هواروي. - د u_blinking_led مثال لپاره 1-6 مرحلې تکرار کړئ. د والدین په کچه ځای پرځای کول د u_blinking_led مثال لپاره 1 -6 مرحلې تکرار کړئ. د مور او پلار په کچه د ځای پرځای کولو سیمه باید په بشپړ ډول د ماشوم په کچه د ځای پرځای کولو او د لارې کولو ساحې په بشپړ ډول تړلي وي پداسې حال کې چې د والدین په کچه منطق ځای پرځای کولو لپاره کافي ځای اجازه ورکوي. دا ټیوټوریل د (X1 Y1) همغږي کاروي - (66 7)، د 47 لوړوالی، او د 26 پلنوالی د u_blinking_led مثال د ځای پرځای کولو سیمې لپاره.

شکل 6. د منطق لاک سیمه کړکۍ

تایید کړئ چې blinking_led.qsf لاندې دندې لري، ستاسو د پوړ پلان کولو سره مطابقت لري:

- فرش پلان د جزوی بیا تنظیم کولو ډیزاین

- په تدریجي ډول د جزوي بیا تنظیم کولو پلي کول

5 ګام: د Intel Arria 10 جزوی بیا تنظیم کولو کنټرولر IP کور اضافه کول

- د PR برخې بیا تنظیم کولو لپاره د Intel Arria 10 جزوی بیا تنظیم کولو کنټرولر IP کور وکاروئ. دا IP کور J کارويTAG د PR برخې بیا تنظیمولو لپاره. ستاسو د Intel Quartus Prime پروژې ته د Intel Arria 10 جزوی بیا تنظیم کولو کنټرولر IP کور اضافه کولو لپاره:

- د IP کتلاګ کې د جزوي بیا تنظیم کولو ټایپ کړئ.

- د IP پیرامیټر ایډیټر پرو کړکۍ لانچ کولو لپاره ، د IP کتابتون څخه د Intel Arria 10 جزوی بیا تنظیم کولو کنټرولر IP کور غوره کړئ ، او اضافه کلیک وکړئ.

- د نوي IP مختلف ډیالوګ بکس کې ، pr_ip د دې په توګه ولیکئ file نوم او جوړ کړئ کلیک وکړئ. د pr_ip لپاره ډیفالټ پیرامیټریزیشن وکاروئ. ډاډ ترلاسه کړئ چې فعال JTAG د ډیبګ حالت او د منجمد انٹرفیس اختیارونه فعال کړئ، او د Avalon-MM غلام انٹرفیس فعالول بند شوي دي.

شکل 7. د Intel Arria 10 جزوی بیا تنظیم کولو کنټرولر IP کور پیرامیټونه

- په پای کې کلیک وکړئ، او د سیسټم رامینځته کولو پرته د پیرامیټر مدیر څخه وتل. د Intel Quartus Prime سافټویر د pr_ip.ip IP توپیر رامینځته کوي file، او اضافه کوي file د blinking_led پروژې ته.

یادونه:

- که تاسو pr_ip.ip کاپي کوئ file د hpr فولډر څخه، په لاسي ډول blinking_led.qsf ایډیټ کړئ file لاندې کرښه شاملولو لپاره: set_global_assignment -name IP_FILE pr_ip.ip

- IP_ ځای په ځای کړئFILE د SDC_ وروسته دندهFILE دندې (jtag.sdc او blinking_led.sdc) ستاسو په blinking_led.qsf کې file. دا ترتیب د جزوی بیا تنظیم IP کور مناسب محدودیت تضمینوي.

یادونه: د ساعتونو د موندلو لپاره، SDC file د PR IP لپاره باید هر SDC تعقیب کړي چې هغه ساعتونه رامینځته کوي چې IP کور یې کاروي. تاسو د .ip په یقیني کولو سره دا امر اسانه کوئ file د PR IP کور د هر .ip وروسته راځي files یا SDC fileپه QSF کې د دې ساعتونو جوړولو لپاره کارول کیږي file ستاسو د Intel Quartus Prime پروژې بیاکتنې لپاره. د نورو معلوماتو لپاره، د جزوی بیا تنظیم کولو IP کور کارونکي لارښود کې د وخت محدودیتونو برخې ته مراجعه وکړئ.

اړوند معلومات

- د جزوی بیا تنظیم کولو IP حلونو کارونکي لارښود

- د جزوی بیا تنظیم کولو سیمې کنټرولر IP کور په اړه د معلوماتو لپاره.

- د جزوي بیا تنظیم کولو IP اصلي کارونکي لارښود

- د وخت محدودیتونو په اړه د معلوماتو لپاره.

د لوړ پوړ ډیزاین تازه کول

د پورته تازه کولو لپاره.SV file د PR_IP مثال سره:

- د لوړې کچې ډیزاین کې د PR_IP مثال اضافه کولو لپاره ، لاندې کوډ بلاک په پورتنۍ برخه کې غیر کمینټ کړئ. SV file:

- د بیا تنظیم کولو پرمهال د محصول بندرونو منطق 1 ته د مجبورولو لپاره ، د PR_IP څخه د کنګل کنټرول سیګنال محصول وکاروئ. په هرصورت، د LED د لیدلو لپاره د والدین PR برخې څخه د څرخیدو ته دوام ورکړئ پداسې حال کې چې PR د ماشوم برخې ته پروګرام کوي، د کنګل کنټرول سیګنال led_two_on نه بندوي. ډاډ ترلاسه کړئ چې pr_led_two_on مستقیم دی

- د ډیفالټ والدین شخصیت (blinking_led) بیلګه وړاندې کولو لپاره، پورته تازه کړئ.SV file د لاندې کوډ بلاک سره:

شکل 8. جزوی بیا تنظیم کول د IP کور ادغام

شپږم ګام: د شخصیتونو تعریف

د دې حوالې ډیزاین د مور او پلار او ماشوم PR برخې لپاره پنځه جلا اشخاص تعریفوي. ستاسو په پروژه کې د اشخاصو تعریف او شاملولو لپاره:

- څلور SystemVerilog جوړ کړئ files، blinking_led_child.sv، blinking_led_child_slow.sv، blinking_led_child_empty.sv، او blinking_led_slow.sv د پنځو کسانو لپاره ستاسو په کاري لارښود کې.

یادونه: که تاسو SystemVerilog جوړ کړئ fileد Intel Quartus Prime Text Editor څخه، اضافه غیر فعال کړئ file د اوسني پروژې اختیار ته، کله چې خوندي کول files.

جدول 2. د حوالې ډیزاین اشخاص

| File نوم | تفصیل | کوډ |

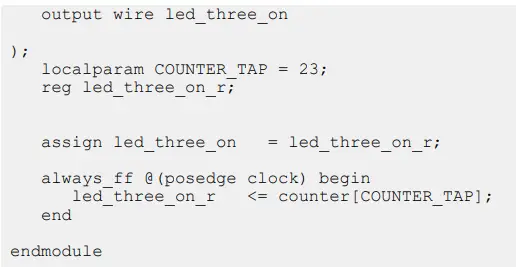

| blinking_led_child.sv | د ماشوم د کچې ډیزاین لپاره ډیفالټ شخصیت |

`timescale 1 ps / 1 ps `default_nettype none ماډل blinking_led_child ( // ساعت د تار ساعت داخل کړئ د ننوتلو تار [31:0] کاونټر،

// د LEDs تولیدي تار led_three_on لپاره د کنټرول سیګنالونه

); localparam COUNTER_TAP = 23; reg led_three_on_r;

assign led_three_on = led_three_on_r ; always_ff @(Podge clock) پیل کیږي led_three_on_r <= counter[COUNTER_TAP]; پای

endmodule |

| ادامه… | ||

| File نوم | تفصیل | کوډ |

| blinking_led_child_slow.sv | د

LED_THREE ورو ورو ځلیږي |

`timescale 1 ps / 1 ps `ډیفالټ_نیټ ډول هیڅ نه

ماډل blinking_led_child_slow (

// ساعت د تار ساعت داخل کړئ د ننوتلو تار [31:0] کاونټر،

// د LEDs تولیدي تار led_three_on لپاره د کنټرول سیګنالونه );

localparam COUNTER_TAP = 27; reg led_three_on_r;

assign led_three_on = led_three_on_r ; always_ff @(Podge clock) پیل کیږي led_three_on_r <= counter[COUNTER_TAP]; پای

endmodule |

| blinking_led_child_empty.sv | د

LED_THREE دوام لري |

`timescale 1 ps / 1 ps `ډیفالټ_نیټ ډول هیڅ نه

ماډل blinking_led_child_empty (

// ساعت د تار ساعت داخل کړئ د ننوتلو تار [31:0] کاونټر،

// د LEDs تولیدي تار led_three_on لپاره د کنټرول سیګنالونه

);

// LED فعال ټیټ دی ټاکل led_three_on = 1'b0;

endmodule |

| blinking_led_slow.sv | LED_TWO

ورو ورو ځلیږي. |

`timescale 1 ps / 1 ps `default_nettype none ماډل blinking_led_slow( // ساعت د تار ساعت داخل کړئ د ننوتلو تار [31:0] کاونټر،

// د LEDs تولیدي تار لپاره د کنټرول سیګنالونه led_two_on، د تولید تار led_three_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; assign led_two_on = led_two_on_r ;

// کاونټر: always_ff @(Podge clock) start led_two_on_r <= counter[COUNTER_TAP]; پای

د_ښکلو_لیدل_ماشوم .led_three_on (led_three_on)، .counter (کاونټر) ساعت (ساعت) |

| File نوم | تفصیل | کوډ |

| );ndmodule |

3 ګام: په 7 پاڼه کې د ډیزاین برخې جوړول

7 ګام: د بیاکتنې رامینځته کول

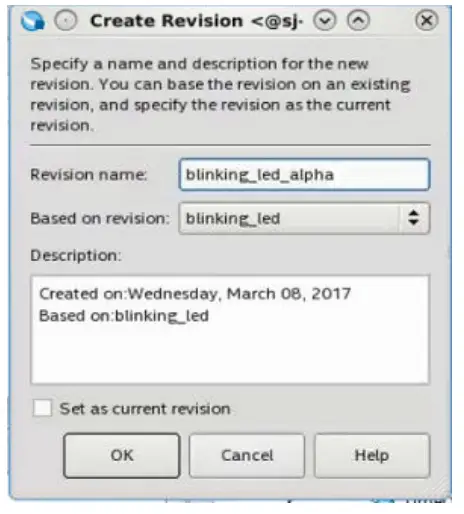

د PR ډیزاین جریان د Intel Quartus Prime سافټویر کې د پروژې بیاکتنې خصوصیت کاروي. ستاسو ابتدايي ډیزاین د اساس بیاکتنه ده، چیرې چې تاسو په FPGA کې د جامد سیمې حدود او د بیا تنظیم وړ سیمې تعریف کړئ. د اساس بیاکتنې څخه ، تاسو ډیری بیاکتنې رامینځته کوئ. دا بیاکتنې د PR سیمو لپاره مختلف تطبیقونه لري. په هرصورت، د PR پلي کولو ټول بیاکتنې د اساس بیاکتنې څخه ورته د لوړ پوړ ځای پرځای کولو او روټینګ پایلې کاروي. د PR ډیزاین ترتیبولو لپاره، تاسو باید د هر شخص لپاره د PR تطبیق بیاکتنه او ترکیب بیاکتنه جوړه کړئ. د دې حوالې ډیزاین کې، د اساس بیاکتنې (blinking_led) سربیره، د ماشوم په کچه درې شخصیتونه او دوه د والدینو په کچه شخصیتونه پنځه جلا ترکیب بیاکتنې او پنځه جلا تطبیق بیاکتنې لري:

جدول 3. د دوو پلرونو او دریو ماشومانو لپاره بیاکتنې

| د ترکیب بیاکتنه | د تطبیق بیاکتنه |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_empty | blinking_led_pr_charlie |

| ړنګول_لارډ_پلار_سلو، ړنګیدل_لیدل_ماشوم_سلو | blinking_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_empty | blinking_led_pr_emma |

د تطبیق بیاکتنې رامینځته کول

د PR پلي کولو بیاکتنې رامینځته کولو لپاره:

- د بیاکتنې ډیالوګ بکس خلاصولو لپاره، د پروژې ➤ بیاکتنې کلیک وکړئ.

- د نوي بیاکتنې جوړولو لپاره، دوه ځله کلیک وکړئ < >.

- د بیاکتنې نوم د blinking_led_pr_alpha په توګه مشخص کړئ او د بیاکتنې پر بنسټ د blinking_led غوره کړئ.

- د اوسني بیاکتنې اختیار په توګه سیټ غیر فعال کړئ او په هو کلیک وکړئ.

- په ورته ډول، blinking_led_pr_bravo، blinking_led_pr_charlie، blinking_led_pr_delta، او blinking_led_pr_emma بیاکتنې، د blinking_led بیاکتنې پر بنسټ جوړ کړئ.

یادونه: پورته بیاکتنې د اوسني بیاکتنې په توګه مه تنظیم کړئ.

شکل 9. د بیاکتنې جوړول

د ترکیب جوړول - یوازې بیاکتنې

د اشخاصو لپاره یوازې ترکیب بیاکتنې رامینځته کولو لپاره ، تاسو باید د لوړې کچې ادارې او اړوند سیسټم ویریلوګ وټاکئ file د هر شخص لپاره:

- د Intel Quartus Prime سافټویر کې، د پروژې ➤ بیاکتنې کلیک وکړئ.

- د blinking_led_default بیاکتنه د blinking_led بیاکتنې پراساس رامینځته کړئ. دا بیاکتنه د اوسني بیاکتنې په توګه مه تنظیم کړئ.

- blinking_led_default.qsf بدل کړئ file د لاندې دندې شاملولو لپاره:

set_global_assignment -نوم TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -نوم SYSTEMVERILOG_FILE - په ورته ډول، blinking_led_child_slow، blinking_led_child_empty، blinking_led_parent، او blinking_led_parent_slow بیاکتنې د blinking_led بیاکتنې پراساس رامینځته کړئ. دا بیاکتنې د اوسني بیاکتنې په توګه مه تنظیم کړئ.

- blinking_led_child_slow.qsf، blinking_led_child_empty.qsf، blinking_led_parent.qsf، او blinking_led_parent_slow.qsf تازه کړئ files د دوی سره مطابقت لري

TOP_LEVEL_ENTITY او SYSTEMVERILOG_FILE دندې:

- د ترکیب غلطیو څخه د مخنیوي لپاره، ډاډ ترلاسه کړئ چې د ترکیب بیاکتنه files د ماشومانو د برخې لپاره هیڅ ډول ډیزاین پارشن، پین دندې، یا منطق لاک نه لري

د سیمې دندې همدارنګه، د ترکیب بیاکتنه files د مورنۍ برخې لپاره باید یوازې د اړونده ماشومانو برخې لپاره ډیزاین برخې دندې ولري. دا دندې لرې کړئ، که کوم وي، په blinking_led_default.qsf، blinking_led_child_slow.qsf، blinking_led_child_empty.qsf، blinking_led_parent.qsf، او blinking_led_parent_slow.pdf files

- لاندې دندې په blinking_led_parent.qsf او blinking_led_parent_slow.qsf کې شامل کړئ files:

- تایید کړئ چې blinking_led.qpf file لاندې بیاکتنې لري، په کوم ځانګړي ترتیب کې:

- یادونه: که تاسو بیاکتنه کاپي کوئ fileد hpr فولډر څخه، په لاسي ډول د blinking_led.qpf تازه کړئ file د پورته کوډونو سره.

د بیاکتنې ډول مشخص کول

تاسو باید د هرې بیاکتنې لپاره د بیاکتنې ډول وټاکئ. د بیاکتنې درې ډولونه شتون لري:

- جزوی بیا تنظیم کول – اساس

- جزوی بیا تنظیم کول - د شخصیت ترکیب

- جزوي بیا تنظیم کول – د شخصیت پلي کول

- لاندې جدول د هرې بیاکتنې لپاره د بیاکتنې ډول دندې لیست کوي:

جدول 4. د بیاکتنې ډولونه

| د بیاکتنې نوم | د بیاکتنې ډول |

| blinking_led.qsf | جزوی بیا تنظیم کول – اساس |

| blinking_led_default.qsf | جزوی بیا تنظیم کول - د شخصیت ترکیب |

| blinking_led_child_empty.qsf | جزوی بیا تنظیم کول - د شخصیت ترکیب |

| blinking_led_child_slow.qsf | جزوی بیا تنظیم کول - د شخصیت ترکیب |

| blinking_led_parent.qsf | جزوی بیا تنظیم کول - د شخصیت ترکیب |

| blinking_led_parent_slow.qsf | جزوی بیا تنظیم کول - د شخصیت ترکیب |

| blinking_led_pr_alpha.qsf | جزوي بیا تنظیم کول – د شخصیت پلي کول |

| blinking_led_pr_bravo.qsf | جزوي بیا تنظیم کول – د شخصیت پلي کول |

| blinking_led_pr_charlie.qsf | جزوي بیا تنظیم کول – د شخصیت پلي کول |

| blinking_led_pr_delta.qsf | جزوي بیا تنظیم کول – د شخصیت پلي کول |

| blinking_led_pr_emma.qsf | جزوي بیا تنظیم کول – د شخصیت پلي کول |

- په پروژه کلیک وکړئ ➤ بیاکتنې. د بیاکتنې ډیالوګ بکس څرګندیږي.

- د بیاکتنې نوم کالم کې blinking_led غوره کړئ، او اوسنی تنظیم کړئ کلیک وکړئ.

- په پلي کولو کلیک وکړئ. blinking_led بیاکتنه خلاصیږي.

- د blinking_led لپاره د بیاکتنې ډول تنظیم کولو لپاره، په دنده کلیک وکړئ ➤ ترتیبات ➤ عمومي.

- د بیاکتنې ډول د جزوی بیا تنظیم کولو - اساس په توګه وټاکئ.

- په ورته ډول، د نورو لسو بیاکتنې لپاره د بیاکتنې ډولونه تنظیم کړئ، لکه څنګه چې په پورته جدول کې لیست شوي.

- یادونه: تاسو باید د بیاکتنې ډول ټاکلو دمخه هره بیاکتنه د اوسني بیاکتنې په توګه تنظیم کړئ. تایید کړئ چې هر .qsf file لاندې دنده لري:

- یادونه: د فټر ځانګړي تنظیمات اضافه کړئ چې تاسو غواړئ د PR پلي کولو تالیف کې د شخصیت پلي کولو بیاکتنې ته وکاروئ. د فټر ځانګړي ترتیبات د شخصیت په فټ اغیزه کوي، مګر په وارد شوي جامد سیمه اغیزه نه کوي. تاسو کولی شئ د انفرادي شخصیت ترکیب بیاکتنې ته د ترکیب ځانګړي تنظیمات هم اضافه کړئ.

د اشخاصو لپاره بیاکتنې رامینځته کړئ

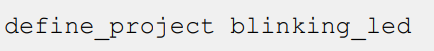

لومړی ګام: د هراړخیز جزوی بیا تنظیم کولو جریان سکریپټ رامینځته کول

د درجه بندي جزوي بیا تنظیم کولو جریان سکریپټ رامینځته کولو لپاره:

- د Intel Quartus Prime کمانډ شیل څخه، د لاندې کمانډ په چلولو سره د جریان ټیمپلیټ جوړ کړئ:

- Intel Quartus Prime A10_hier_partial_reconfig/flow.tcl تولیدوي file.

- د پیدا شوي a10_hier_partial_reconfig/setup.tcl.ex نوم بدل کړئampa10_hier_partial_reconfig/setup.tcl ته لاړ شئ، او سکریپټ بدل کړئ ترڅو ستاسو د جزوي بیا تنظیمولو پروژې توضیحات مشخص کړئ:

a. د پروژې نوم تعریف کولو لپاره، لاندې کرښه تازه کړئ: b. د اساس بیاکتنې تعریف کولو لپاره ، لاندې کرښه تازه کړئ:

b. د اساس بیاکتنې تعریف کولو لپاره ، لاندې کرښه تازه کړئ:

- د هر جزوي بیا تنظیم کولو پلي کولو بیاکتنې تعریف کولو لپاره ، د PR برخې نومونو او د سرچینې بیاکتنې سره چې بیاکتنې پلي کوي ، لاندې لینونه تازه کړئ:

یادونه: د بیاکتنې ټولې پروژې باید په ورته لارښود کې وي لکه blinking_led.qpf. که نه نو، د فلو سکریپټ مطابق مطابق تازه کړئ.

لومړی ګام: د هراړخیز جزوی بیا تنظیم کولو جریان سکریپټ چلول

د درجه بندي جزوي بیا تنظیم کولو جریان سکریپټ چلولو لپاره:

- په وسیلو کلیک وکړئ ➤ Tcl سکریپټونه. د Tcl سکریپټ ډیالوګ بکس څرګندیږي.

- په پروژه کې شامل کړئ کلیک وکړئ، a10_hier_partial_reconfig/flow.tcl براوز کړئ او غوره کړئ.

- د کتابتونونو په پین کې a10_hier_partial_reconfig/flow.tcl غوره کړئ، او په چلولو کلیک وکړئ.

دا سکریپټ د دریو اشخاصو لپاره ترکیب پرمخ وړي. د Intel Quartus Prime یو SRAM آبجیکٹ تولیدوي File (.sof)، یو جزوی ماسک شوی SRAM څیز File (.pmsf)، او یو خام بائنری File (.rbf) د هر شخص لپاره.

یادونه: د Intel Quartus Prime کمانډ شیل څخه سکریپټ چلولو لپاره، لاندې کمانډ ټایپ کړئ:

- د جزوی بیا تنظیم کولو ډیزاین تالیف کړئ

- د جزوی بیا تنظیم کولو جریان سکریپټ کارول

- د جزوی بیا تنظیم کولو جریان سکریپټ ترتیب کول

- پروګرام جوړ کړئ Files

لومړی ګام: د بورډ پروګرام کول

مخکې له دې چې تاسو پیل کړئ:

- د بریښنا رسولو د Intel Arria 10 SoC پراختیایی بورډ سره وصل کړئ.

- د USB بلاسټر کیبل د خپل کمپیوټر USB پورټ او په پراختیایی بورډ کې د USB بلاسټر بندر ترمینځ وصل کړئ.

د Intel Arria 10 SoC پراختیایی بورډ کې ډیزاین چلولو لپاره:

- د Intel Quartus Prime سافټویر خلاص کړئ او په Tools ➤ Programmer کلیک وکړئ.

- په پروګرامر کې، د هارډویر سیټ اپ کلیک وکړئ او USB-Blaster غوره کړئ.

- په اتوماتیک کشف کلیک وکړئ او وسیله غوره کړئ، 10AS066N3.

- په OK کلیک وکړئ. د Intel Quartus Prime سافټویر په بورډ کې د دریو FPGA چپسونو سره پروګرامر کشف او تازه کوي.

- د 10AS066N3 وسیله غوره کړئ، بدلون کلیک وکړئ File او blinking_led_pr_alpha.sof پورته کړئ file.

- د blinking_led_pr_alpha.sof لپاره برنامه/کنفیګر فعال کړئ file.

- په پیل کلیک وکړئ او د پرمختګ بار ته انتظار وکړئ چې 100٪ ته ورسیږي.

- په تخته کې LEDs وګورئ چې په ورته فریکونسۍ کې د اصلي فلیټ ډیزاین په څیر روښانه کیږي.

- یوازې د ماشوم PR سیمه کې برنامه کولو لپاره ، په blinking_led_pr_alpha.sof ښیې کلیک وکړئ file په پروګرامر کې او د PR پروګرامینګ اضافه کړئ کلیک وکړئ File.

- blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf غوره کړئ file.

- برنامه غیر فعال کړئ / د blinking_led_pr_alpha.sof لپاره تنظیم کړئ file.

- د blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf لپاره برنامه/کنفیګر فعال کړئ file او په پیل کلیک وکړئ. په تخته کې، LED [0] او LED [1] وګورئ چې د ړنګیدو دوام لري. کله چې د پرمختګ بار 100٪ ته ورسیږي، LED [2] په ورته نرخ کې راښکاره کیږي، او LED [3] ورو ځلیږي.

- د مور او پلار او ماشوم د PR سیمه د پروګرام کولو لپاره، په .rbf ښي کلیک وکړئ file په پروګرامر کې او د PR پروګرام بدلولو کلیک وکړئ File.

- blinking_led_pr_delta.pr_parent_partition.rbf غوره کړئ file.

- په پیل کلیک وکړئ. په تخته کې، وګورئ چې LED[0] او LED[1] په دوامداره توګه ړنګیږي. کله چې د پرمختګ بار 100٪ ته ورسیږي، دواړه LED [2] او LED [3] ورو ورو روښانه کوي.

- پورتنۍ مرحلې تکرار کړئ ترڅو په متحرک ډول یوازې د ماشوم PR سیمه یا دواړه والدین او د ماشوم PR سیمې په ورته وخت کې بیا برنامه کړئ.

شکل 10. د Intel Arria 10 SoC پراختیایی بورډ پروګرام کول

د موجوده شخصیت بدلول

- تاسو کولی شئ موجوده شخصیت بدل کړئ، حتی د اساس بیاکتنې بشپړولو وروسته.

- د مثال لپارهampد دې لپاره چې د ړنګولو_لډ_ماشوم_سلو شخصیت حتی ورو ورو روښانه شي:

- په blinking_led_child_slow.sv fileد COUNTER_TAP پیرامیټر له 27 څخه تر 28 پورې بدل کړئ.

- د دې شخصیت د بیا ترکیب او بیا پلي کولو لپاره، تاسو باید ټول ترکیبونه بیا تنظیم کړئ - یوازې بیاکتنې او د تطبیق بیاکتنې چې د بدلون لخوا اغیزمن شوي. د لاندې لینونو د شاملولو لپاره د setup.tcl سکریپټ بدل کړئ:

یادونه: کله چې د blinking_led_pr_delta بیاکتنې لپاره pr_parent_parition تعریف کړئ، تاسو د پلي کولو لپاره د هغه شخصیت وروستی سنیپ شاټ واردوئ. د پایلې په توګه، د والدین ویشلو منطق پلي کول ورته پاتې دي، پداسې حال کې چې د ورته ماشوم ویش تعدیل او پلي کول.

یادونه: کله چې د blinking_led_pr_delta بیاکتنې لپاره pr_parent_parition تعریف کړئ، تاسو د پلي کولو لپاره د هغه شخصیت وروستی سنیپ شاټ واردوئ. د پایلې په توګه، د والدین ویشلو منطق پلي کول ورته پاتې دي، پداسې حال کې چې د ورته ماشوم ویش تعدیل او پلي کول. دا کمانډ د blinking_led_child_slow ترکیب بیاکتنه بیا ترکیب کوي، او بیا د blinking_led_pr_bravo په کارولو سره د PR تطبیق تالیف پرمخ وړي.

دا کمانډ د blinking_led_child_slow ترکیب بیاکتنه بیا ترکیب کوي، او بیا د blinking_led_pr_bravo په کارولو سره د PR تطبیق تالیف پرمخ وړي. - یوازې د ترکیب - بیاکتنې تالیف ترسره کولو لپاره ، لاندې کمانډ چل کړئ: دا کمانډ د اساس بیاکتنې بیا تنظیم نه کوي.

- د پلي کولو بیاکتنې تالیف کولو لپاره ، لاندې کمانډ چل کړئ:

- دا کمانډ د اساس بیاکتنه بیا نه تنظیموي.

- په 10 ګام کې مرحلې تعقیب کړئ: په 22 پاڼه کې د بورډ پروګرام کول ترڅو د RBF نتیجه ترلاسه کړي file په FPGA کې

یادونه: د هرې بیاکتنې لپاره د بشپړ جریان د چلولو څخه مخنیوي لپاره، په setup.tcl سکریپټ کې یوازې ترکیب بیاکتنې او پلي کولو بیاکتنې تعریف کړئ، او سکریپټ چل کړئ.

ډیزاین ته د نوي شخصیت اضافه کول

ستاسو د اساس بیاکتنې په بشپړ ډول تالیف کولو وروسته ، تاسو لاهم کولی شئ نوي اشخاص اضافه کړئ او په انفرادي ډول دا اشخاص تالیف کړئ.

د مثال لپارهample، د blinking_led_parent_slow لپاره د نوي ماشوم شخصیت تعریف کول، چې led_three بندوي:

- blinking_led_child_empty.sv blinking_led_chdild_off.sv ته کاپي کړئ.

- په blinking_led_child_off.sv file, دنده تعدیل کړئ، led_three_on = 1'b0; led_three_on = 1'b1; ډاډ ترلاسه کړئ چې تاسو د ماډل نوم له blinking_led_child_empty څخه blinking_led_child_off ته بدل کړئ.

- په 16 مخ کې یوازې د ترکیب بیاکتنې رامینځته کولو کې د ګامونو په تعقیب کولو سره د نوي ترکیب بیاکتنه رامینځته کړئ ، blinking_led_child_off.

یادونه: د blinking_led_child_off بیاکتنه باید blinking_led_child_off.sv وکاروي file. - په 15 مخ کې د پلي کولو بیاکتنې رامینځته کولو کې د ګامونو په تعقیب ، blinking_led_pr_foxtrot ، د پلي کولو نوې بیاکتنه رامینځته کړئ.

- a10_hier_partial_reconfig/setup.tcl تازه کړئ file د نوي PR پلي کولو تعریف کولو لپاره:

- د لاندې کمانډ په چلولو سره یوازې دا نوی ترکیب او د پلي کولو بیاکتنه تالیف کړئ:

د Intel Arria 10 وسیلو لپاره د درجه بندي جزوي بیا تنظیم کولو په اړه د بشپړ معلوماتو لپاره ، د Intel Quartus Prime Pro Edition Handbook حجم 1 کې د جزوي بیا تنظیم کولو ډیزاین رامینځته کولو ته مراجعه وکړئ.

اړوند معلومات

- د جزوی بیا تنظیم کولو ډیزاین رامینځته کول

- د جزوی بیا تنظیم کولو آنلاین روزنه

د اسنادو بیاکتنې تاریخ

جدول 5. د اسنادو د بیاکتنې تاریخ

| د سند نسخه | د ساوتري نسخه | بدلونونه |

| 2017.11.06 | 17.1.0 | • تازه کړی د حوالې ډیزاین اړتیاوې د سافټویر نسخه سره برخه

• تازه کړی د فلیټ حوالې ډیزاین د PR ویشلو پرته شکل د ډیزاین بلاک بدلونونو سره • تازه کړی د حوالې ډیزاین Files د معلوماتو سره جدول Top_counter.sv ماډل • تازه کړی د جزوی بیا تنظیم کول IP کور ادغام شکل د ډیزاین بلاک بدلونونو سره • ارقام تازه کړل - د ډیزاین برخې کړکۍ او منطق لاک سیمه کړکۍ د نوي GUI منعکس کولو لپاره • File د نوم بدلونونه • د متن سمون |

| 2017.05.08 | 17.0.0 | د سند لومړنۍ خوشې کول |

اسناد / سرچینې

|

intel AN 805 د Arria 10 SoC پراختیایی بورډ کې د ډیزاین جزوی بیا تنظیم کول [pdf] د کارونکي لارښود AN 805 د Arria 10 SoC پراختیایی بورډ، AN 805، د اریریا 10 SoC پراختیایی بورډ کې د ډیزاین جزوی بیا ترتیبول، د Arria 10 SoC پراختیایی بورډ، د Arria 10 SoC پراختیایی بورډ، Arria 10 SoC پراختیایی بورډ، XNUMX SoC کې د ډیزاین بیا تنظیم کول پرمختیایي بورډ |