intel AN 805 йерархична частична реконфигурация на дизайн на Arria 10 SoC платка за разработка

Инструкция за йерархично частично преконфигуриране за Intel® Arria® 10 SoC платка за разработка

Тази бележка за приложението демонстрира трансформиране на прост дизайн в йерархично частично реконфигурируем дизайн и внедряване на дизайна върху платката за разработка Intel® Arria® 10 SoC. Йерархичното частично преконфигуриране (HPR) е специален тип частично преконфигуриране (PR), при което съдържате PR регион в друг PR регион. Можете да създадете множество персони както за дъщерния, така и за родителския дял. Влагате дъщерните дялове в техните родителски дялове. Преконфигурирането на дъщерен дял не оказва влияние върху работата в родителския или статични региони. Преконфигурирането на родителски дял не оказва влияние върху операцията в статичния регион, но заменя дъщерните дялове на родителския регион с лица на дъщерен дял по подразбиране. Тази методология е ефективна в системи, където множество функции споделят във времето едни и същи ресурси на FPGA устройство.

Частичното преконфигуриране осигурява следните подобрения на плоския дизайн:

- Позволява преконфигуриране на дизайна по време на изпълнение

- Увеличава мащабируемостта на дизайна

- Намалява времето за престой на системата

- Поддържа динамични функции за времево мултиплексиране в дизайна

- Намалява разходите и консумацията на енергия чрез ефективно използване на пространството на борда

- Забележка:

- Внедряването на този референтен дизайн изисква основно познаване на процеса на внедряване на Intel Quartus® Prime FPGA и познаване на основния проект на Intel Quartus Prime files.

Свързана информация

- Ръководство за потребителя на Intel Arria 10 SoC Development Kit

- Концепции за частично преконфигуриране

- Проектен поток на частично преконфигуриране

- Препоръки за проектиране на частично преконфигуриране

- Съображения за проектиране на частично преконфигуриране

Референтни изисквания за проектиране

Този референтен дизайн изисква следното:

- Софтуер Intel Quartus Prime Pro Edition версия 17.1 за внедряване на дизайна.

- Комплект за разработка на Intel Arria 10 SoC за внедряване на FPGA.

Корпорация Intel. Всички права запазени. Intel, логото на Intel и други марки на Intel са търговски марки на Intel Corporation или нейните филиали. Intel гарантира производителността на своите FPGA и полупроводникови продукти според настоящите спецификации в съответствие със стандартната гаранция на Intel, но си запазва правото да прави промени на продукти и услуги по всяко време без предизвестие. Intel не поема никаква отговорност или задължения, произтичащи от приложението или използването на каквато и да е информация, продукт или услуга, описани тук, освен в случаите, когато Intel е изрично договорено в писмен вид. Клиентите на Intel се съветват да получат най-новата версия на спецификациите на устройството, преди да разчитат на публикувана информация и преди да направят поръчки за продукти или услуги.

- Други имена и марки могат да бъдат заявени като собственост на други.

Референтният дизайн приключиview

- Този референтен дизайн се състои от един 32-битов брояч. На ниво платка дизайнът свързва часовника към 50MHz източник и свързва изхода към четири светодиода на FPGA. Избирането на изхода от битовете на брояча в определена последователност кара светодиодите да мигат с определена честота.

Фигура 1. Плосък референтен дизайн без PR разделяне

Референтен дизайн Files

Урокът за частично преконфигуриране е достъпен на следното място: https://github.com/intel/fpga-partial-reconfig

За да изтеглите урока:

- Щракнете върху Клониране или изтегляне.

- Щракнете върху Изтегляне на ZIP. Разархивирайте FPGA-partial-config-master.zip file.

- Отидете до подпапката tutorials/a10_soc_devkit_blinking_led_hpr за достъп до референтния дизайн.

Плоската папка се състои от следното files:

Таблица 1. Референтен дизайн Files

| File Име | Описание |

| Горна част. СВ | Най-високото ниво file съдържа плоското изпълнение на дизайна. Този модул инстанцира blinking_led поддяла и модула top_counter. |

| top_counter.sv | 32-битов брояч от най-високо ниво, който контролира LED[1] директно. Регистрираният изход на брояча управлява LED[0], а също така захранва LED[2] и LED[3] чрез модула blinking_led. |

| blinking_led.sdc | Определя времевите ограничения за проекта. |

| продължи… | |

| File Име | Описание |

| blinking_led.SV | В този урок преобразувате този модул в родителски PR дял. Модулът получава регистрирания изход на модула top_counter, който управлява LED[2] и LED[3]. |

| blinking_led.qpf | Проект Intel Quartus Prime file съдържащ списък на всички ревизии в проекта. |

| blinking_led.qsf | Настройки на Intel Quartus Prime file съдържащ заданията и настройките за проекта. |

Забележка: Папката hpr съдържа пълния набор от fileсъздавате с помощта на тази бележка за приложението. Препратка към тези files във всеки момент по време на преминаването.

Фигура 2. Референтен дизайн Files

Преглед на референтния дизайн

Следващите стъпки описват прилагането на частично преконфигуриране към плосък дизайн. Урокът използва софтуера Intel Quartus Prime Pro Edition за платката за разработка Intel Arria 10 SoC:

- Стъпка 1: Първи стъпки на страница 6

- Стъпка 2: Създайте подмодул на ниво дете на страница 6

- Стъпка 3: Създаване на дизайнерски дялове на страница 7

- Стъпка 4: Разпределяне на регион за разположение и маршрутизиране за PR дялове на страница 9

- Стъпка 5: Добавяне на Intel Arria 10 Partial Reconfiguration Controller IP Core на страница 10

- Стъпка 6: Дефиниране на лица на страница 13

- Стъпка 7: Създаване на ревизии на страница 15

- Стъпка 8: Генериране на скрипта на потока за йерархична частична реконфигурация на страница 20

- Стъпка 9: Изпълнение на скрипта на потока за йерархична частична реконфигурация на страница 21

- Стъпка 10: Програмиране на платката на страница 22

Стъпка 1: Първи стъпки

За копиране на референтния дизайн files във вашата работна среда и компилирайте blinking_led плоския дизайн:

- Създайте директория във вашата работна среда, a10_soc_devkit_blinking_led_hpr.

- Копирайте изтеглената подпапка tutorials/a10_soc_devkit_blinking_led_hpr/flat в директорията a10_soc_devkit_blinking_led_hpr.

- В софтуера Intel Quartus Prime Pro Edition щракнете върху File ➤ Отворете Project и изберете blinking_led.qpf.

- За да компилирате плоския дизайн, щракнете върху Обработка ➤ Старт на компилация.

Стъпка 2: Създаване на подмодул на ниво дете

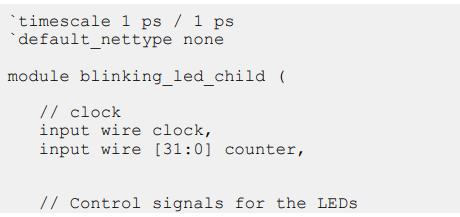

За да преобразувате този плосък дизайн в йерархичен PR дизайн, трябва да създадете дъщерен подмодул (blinking_led_child. SV), който е вложен в родителския подмодул (blinking_led.sv).

- Създайте нов дизайн file, blinking_led_child.sv и добавете следните редове код към това file: времева скала 1 ps / 1 ps `default_nettype няма модул blinking_led_child ( // часовник входен проводник часовник, входен проводник [31:0] брояч, // Контролни сигнали за светодиодите

- Променете blinking_led.sv file за свързване на led_two_on към бит 23 на брояча от статичната област и инстанциране на модула blinking_led_child. След модификации вашият blinking_led.sv file трябва да изглежда както следва:

- При промяна на целия дизайн files, прекомпилирайте проекта, като щракнете върху Обработка ➤ Старт на компилация

Стъпка 3: Създаване на дизайнерски дялове

Трябва да създадете дизайнерски дялове за всеки PR регион, който искате частично да преконфигурирате. Можете да създадете произволен брой независими дялове или PR региони във вашия дизайн. Този урок създава два дизайнерски дяла за екземплярите u_blinking_led_child и u_blinking_led.

За да създадете дизайнерски дялове за йерархично частично преконфигуриране:

- Щракнете с десния бутон върху екземпляра u_blinking_led_child в Project Navigator и щракнете върху Design Partition ➤ Set as Design Partition. Икона за дизайн на дял се появява до всеки екземпляр, който е зададен като дял.

Фигура 3. Създаване на дизайнерски дялове от Project Navigator

- За да дефинирате типа на дяла, щракнете с десния бутон върху екземпляра u_blinking_led_child в раздела Йерархия, щракнете върху Проектен дял ➤ Реконфигурируем. Можете да дефинирате типа на дяла само след като зададете екземпляра като дял. Разделът за дизайн се появява в Заданията View раздел на прозореца Design Partitions.

Фигура 4. Прозорец за проектиране на дялове

- Редактирайте името на дяла в прозореца Design Partitions, като щракнете двукратно върху името. За този референтен дизайн преименувайте името на дяла на pr_partition.

Забележка: Когато създавате дял, софтуерът Intel Quartus Prime автоматично генерира име на дял въз основа на името на екземпляра и йерархичния път. Това име на дял по подразбиране може да варира с всеки екземпляр. - Повторете стъпки 1 и 2, за да присвоите преконфигурируеми дизайнерски дялове на u_blinking_led екземпляра. Преименувайте този дял на pr_parent_partition.

Проверете дали blinking_led.qsf съдържа следните присвоявания, съответстващи на вашите преконфигурируеми дизайнерски дялове:

Създайте дизайнерски дялове за частично преконфигуриране

Стъпка 4: Разпределяне на регион за разположение и маршрутизиране за PR дялове

Когато създавате основната ревизия, потокът на PR дизайн използва вашето разпределение на регион на PR дял, за да постави съответното ядро на личността в резервирания регион. За да намерите и присвоите PR региона в етажния план на устройството за вашата основна ревизия:

- Щракнете с десния бутон върху екземпляра u_blinking_led_child в Project Navigator и щракнете върху Logic Lock Region ➤ Create New Logic Lock Region. Регионът се появява в прозореца Logic Lock Regions.

- Вашият регион на разположение трябва да обхваща логиката blinking_led_child. Изберете региона за разположение, като локализирате възела в Chip Planner. Щракнете с десния бутон върху името на региона u_blinking_led_child в Project Navigator и щракнете върху Locate Node ➤ Locate in Chip Planner.

Фигура 5. Местоположение на възела за планиране на чипове за blinking_led

- В прозореца Logic Lock Regions посочете координатите на региона на разположение в колоната Origin. Началото съответства на долния ляв ъгъл на региона. Напримерample, за да зададете регион на разположение с (X1 Y1) координати като (69 10), посочете произхода като X69_Y10. Софтуерът Intel Quartus Prime автоматично изчислява (X2 Y2) координатите (горе вдясно) за региона на разположение въз основа на височината и ширината, които сте посочили.

Забележка: Този урок използва координатите (X1 Y1) – (69 10) и височина и ширина от 20 за областта на разположение. Дефинирайте произволна стойност за региона на разположение, при условие че регионът покрива логиката blinking_led_child. - Активирайте опциите Reserved и Core-Only.

- Щракнете двукратно върху опцията Routing Region. Появява се диалоговият прозорец Logic Lock Routing Region Settings.

- Изберете Фиксиран с разширение за тип маршрут. Избирането на тази опция автоматично присвоява дължина на разширението 1.

Забележка: Регионът за маршрутизиране трябва да бъде по-голям от региона за поставяне, за да осигури допълнителна гъвкавост за монтажника, когато машината маршрутизира различни персони. - Повторете стъпки 1 -6 за екземпляра u_blinking_led. Разположението на ниво родител Повторете стъпки 1 -6 за екземпляра u_blinking_led. Регионът за разположение на ниво родител трябва напълно да обхваща съответните региони за разположение и маршрутизиране на ниво родител, като същевременно позволява достатъчно място за разположението на логиката на ниво родител. Този урок използва координатите (X1 Y1) – (66 7), височина 47 и ширина 26 за областта на разположение на u_blinking_led екземпляра.

Фигура 6. Прозорец за региони на логическо заключване

Проверете дали blinking_led.qsf съдържа следните присвоявания, съответстващи на вашето етажно планиране:

- Етажен план на проекта за частично преконфигуриране

- Постепенно внедряване на частично преконфигуриране

Стъпка 5: Добавяне на Intel Arria 10 Partial Reconfiguration Controller IP Core

- Използвайте IP ядрото на Intel Arria 10 Partial Reconfiguration Controller, за да преконфигурирате PR дяла. Това IP ядро използва JTAG за преконфигуриране на PR дяла. За да добавите IP ядрото на Intel Arria 10 Partial Reconfiguration Controller към вашия проект Intel Quartus Prime:

- Въведете частично преконфигуриране в IP каталога.

- За да стартирате прозореца на IP Parameter Editor Pro, изберете IP ядрото на Intel Arria 10 Partial Reconfiguration Controller от IP библиотеката и щракнете върху Add.

- В диалоговия прозорец Нов IP вариант въведете pr_ip като file име и щракнете върху Създаване. Използвайте параметризацията по подразбиране за pr_ip. Уверете се, че Enable JTAG опциите за режим на отстраняване на грешки и активиране на интерфейс за замразяване са включени, а опцията за активиране на подчинен интерфейс на Avalon-MM е изключена.

Фигура 7. IP основни параметри на контролера за частично преконфигуриране на Intel Arria 10

- Щракнете върху Готово и излезте от редактора на параметри, без да генерирате системата. Софтуерът Intel Quartus Prime създава IP варианта pr_ip.ip fileи добавя file към blinking_led проекта.

Забележка:

- Ако копирате pr_ip.ip file от папката hpr редактирайте ръчно файла blinking_led.qsf file за да включите следния ред: set_global_assignment -name IP_FILE pr_ip.ip

- Поставете IP_FILE назначение след SDC_FILE задачи (jtag.sdc и blinking_led.sdc) във вашия blinking_led.qsf file. Това подреждане гарантира подходящо ограничаване на IP ядрото за частично преконфигуриране.

Забележка: За откриване на часовниците, SDC file за PR IP трябва да следва всеки SDC, който създава часовниците, които IP ядрото използва. Вие улеснявате тази поръчка, като гарантирате, че .ip file за PR IP ядрото идва след всеки .ip files или SDC fileсе използва за създаване на тези часовници в QSF file за вашата ревизия на проекта Intel Quartus Prime. За повече информация вижте раздела Времеви ограничения в Ръководството за потребителя на IP Core за частично преконфигуриране.

Свързана информация

- Ръководство за потребителя на IP решения за частично преконфигуриране

- За информация относно IP ядрото на контролера за частична реконфигурация.

- Ръководство за потребителя на IP Core за частично преконфигуриране

- За информация относно ограниченията във времето.

Актуализиране на дизайна от най-високо ниво

За да актуализирате top.SV file с екземпляр PR_IP:

- За да добавите екземпляра PR_IP към дизайна от най-високо ниво, разкоментирайте следния кодов блок в горната част.SV file:

- За да принудите изходните портове към логика 1 по време на преконфигуриране, използвайте изходния контролен сигнал на замръзване от PR_IP. Въпреки това, за да наблюдавате как светодиодът продължава да мига от родителския PR дял, докато PR програмира дъщерния дял, контролният сигнал за замразяване не изключва led_two_on. Уверете се, че pr_led_two_on е директно

- За да присвоите екземпляр на родителската личност по подразбиране (blinking_led), актуализирайте top.SV file със следния блок код:

Фигура 8. Частична преконфигурирана интеграция на IP ядро

Стъпка 6: Дефиниране на персони

Този референтен дизайн дефинира пет отделни персони за родителските и дъщерните PR дялове. За да дефинирате и включите персоните във вашия проект:

- Създайте четири SystemVerilog files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv и blinking_led_slow.sv във вашата работна директория за петте персони.

Забележка: Ако създадете SystemVerilog files от текстовия редактор на Intel Quartus Prime, деактивирайте Add file към текущата опция за проект, когато записвате files.

Таблица 2. Персони за референтен дизайн

| File Име | Описание | Код |

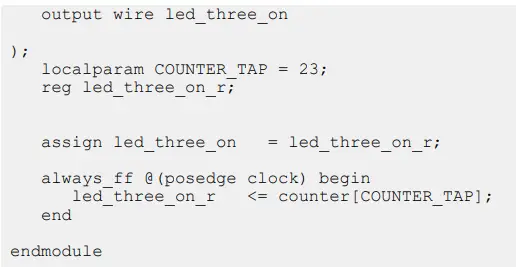

| blinking_led_child.sv | Персона по подразбиране за дизайна на детско ниво |

`времева скала 1 ps / 1 ps `default_nettype няма модул blinking_led_child ( // часовник входен кабелен часовник, входен проводник [31:0] брояч,

// Контролни сигнали за изходния проводник на светодиодите led_three_on

); localparam COUNTER_TAP = 23; reg led_three_on_r;

присвояване led_three_on = led_three_on_r; always_ff @(posedge часовник) започва led_three_on_r <= брояч [COUNTER_TAP]; край

краен модул |

| продължи… | ||

| File Име | Описание | Код |

| blinking_led_child_slow.sv | The

LED_THREE мига по-бавно |

`времева скала 1 ps / 1 ps `default_nettype няма

модул blinking_led_child_slow (

// часовник входен кабелен часовник, входен проводник [31:0] брояч,

// Контролни сигнали за изходния проводник на светодиодите led_three_on );

localparam COUNTER_TAP = 27; reg led_three_on_r;

присвояване led_three_on = led_three_on_r; always_ff @(posedge часовник) започва led_three_on_r <= брояч [COUNTER_TAP]; край

краен модул |

| blinking_led_child_empty.sv | The

LED_THREE остава ВКЛ |

`времева скала 1 ps / 1 ps `default_nettype няма

модул blinking_led_child_empty (

// часовник входен кабелен часовник, входен проводник [31:0] брояч,

// Контролни сигнали за изходния проводник на светодиодите led_three_on

);

// Светодиодът е активен ниско присвояване на led_three_on = 1'b0;

краен модул |

| blinking_led_slow.sv | LED_TWO

мига по-бавно. |

`времева скала 1 ps / 1 ps `default_nettype няма модул blinking_led_slow( // часовник входен кабелен часовник, входен проводник [31:0] брояч,

// Контролни сигнали за изходния проводник на светодиодите led_two_on, изходен проводник led_three_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; присвояване led_two_on = led_two_on_r;

// Броячът: always_ff @(posedge часовник) започва led_two_on_r <= counter[COUNTER_TAP]; край

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .counter (брояч), .clock (часовник) |

| File Име | Описание | Код |

| );ndмодул |

Стъпка 3: Създаване на дизайнерски дялове на страница 7

Стъпка 7: Създаване на ревизии

Потокът на PR дизайн използва функцията за ревизии на проекта в софтуера Intel Quartus Prime. Вашият първоначален дизайн е базовата ревизия, където дефинирате границите на статичните региони и реконфигурируемите региони на FPGA. От основната ревизия създавате множество ревизии. Тези ревизии съдържат различните реализации за PR регионите. Въпреки това, всички ревизии на внедряване на PR използват едно и също разположение от най-високо ниво и резултати от маршрутизирането от основната ревизия. За да компилирате PR дизайн, трябва да създадете ревизия на внедряване на PR и ревизия на синтез за всяка личност. В този референтен дизайн, в допълнение към базовата ревизия (blinking_led), трите персони на ниво дете и двете персони на ниво родител съдържат пет отделни ревизии на синтез и пет отделни ревизии на изпълнение:

Таблица 3. Ревизии за персони с двама родители и персони с три деца

| Ревизия на синтеза | Ревизия на изпълнението |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | мигащ_лед_пр_браво |

| blinking_led_parent, blinking_led_child_empty | blinking_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | blinking_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_empty | blinking_led_pr_emma |

Създаване на ревизии за изпълнение

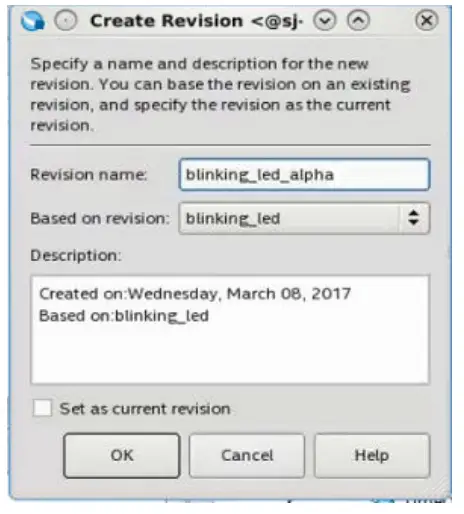

За да създадете ревизии на изпълнението на PR:

- За да отворите диалоговия прозорец Ревизии, щракнете върху Проект ➤ Ревизии.

- За да създадете нова версия, щракнете двукратно върху < >.

- Посочете името на ревизията като blinking_led_pr_alpha и изберете blinking_led за Based on Revision.

- Деактивирайте опцията Задаване като текуща версия и щракнете върху OK.

- По подобен начин създайте ревизии blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta и blinking_led_pr_emma, базирани на ревизията blinking_led.

Забележка: Не задавайте горните ревизии като текуща ревизия.

Фигура 9. Създаване на ревизии

Създаване на ревизии само за синтез

За да създадете ревизии само за синтез за персоните, трябва да присвоите обекта от най-високо ниво и съответния SystemVerilog file за всеки от персонажите:

- В софтуера Intel Quartus Prime щракнете върху Проект ➤ Ревизии.

- Създайте версия blinking_led_default въз основа на версия blinking_led. Не задавайте тази версия като текуща версия.

- Променете blinking_led_default.qsf file да включва следните задачи:

set_global_assignment -име TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -име SYSTEMVERILOG_FILE - По същия начин създайте blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent и blinking_led_parent_slow ревизии въз основа на blinking_led ревизия. Не задавайте тези ревизии като текущи ревизии.

- Актуализирайте blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf и blinking_led_parent_slow.qsf files със съответните им

TOP_LEVEL_ENTITY и SYSTEMVERILOG_FILE задачи:

- За да избегнете грешки при синтеза, уверете се, че ревизията на синтеза files за дъщерните дялове не съдържат дизайнерски дял, присвояване на щифтове или логическо заключване

регионални задачи. Също така, ревизията на синтеза files за родителските дялове трябва да съдържа само присвоявания на проектни дялове за съответните дъщерни дялове. Премахнете тези присвоявания, ако има такива, в blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf и blinking_led_parent_slow.pdf files

- Включете следните присвоявания в blinking_led_parent.qsf и blinking_led_parent_slow.qsf files:

- Проверете дали blinking_led.qpf file съдържа следните ревизии, без конкретен ред:

- Забележка: Ако копирате ревизията files от папка hpr, актуализирайте ръчно blinking_led.qpf file с горните редове код.

Указване на тип ревизия

Трябва да зададете тип ревизия за всяка от вашите ревизии. Има три вида ревизии:

- Частична преконфигурация – База

- Частична реконфигурация – Синтез на личността

- Частична преконфигурация – Внедряване на Persona

- Следната таблица изброява присвояванията на тип ревизия за всяка от ревизиите:

Таблица 4. Типове ревизии

| Име на версията | Тип ревизия |

| blinking_led.qsf | Частична преконфигурация – База |

| blinking_led_default.qsf | Частична реконфигурация – Синтез на личността |

| blinking_led_child_empty.qsf | Частична реконфигурация – Синтез на личността |

| blinking_led_child_slow.qsf | Частична реконфигурация – Синтез на личността |

| blinking_led_parent.qsf | Частична реконфигурация – Синтез на личността |

| blinking_led_parent_slow.qsf | Частична реконфигурация – Синтез на личността |

| blinking_led_pr_alpha.qsf | Частична преконфигурация – Внедряване на Persona |

| blinking_led_pr_bravo.qsf | Частична преконфигурация – Внедряване на Persona |

| blinking_led_pr_charlie.qsf | Частична преконфигурация – Внедряване на Persona |

| blinking_led_pr_delta.qsf | Частична преконфигурация – Внедряване на Persona |

| blinking_led_pr_emma.qsf | Частична преконфигурация – Внедряване на Persona |

- Щракнете върху Проект ➤ Ревизии. Появява се диалоговият прозорец Ревизии.

- Изберете blinking_led в колоната Revision Name и щракнете върху Set Current.

- Кликнете Приложи. Отваря се ревизията blinking_led.

- За да зададете типа ревизия за blinking_led, щракнете върху Присвоения ➤ Настройки ➤ Общи.

- Изберете типа ревизия като Частична преконфигурация – База.

- По същия начин задайте типовете ревизии за останалите десет ревизии, както са изброени в таблицата по-горе.

- Забележка: Трябва да зададете всяка ревизия като текуща ревизия, преди да зададете типа ревизия. Проверете дали всеки .qsf file съдържа следното задание:

- Забележка: Добавете всички специфични за монтажника настройки, които искате да използвате при компилирането на внедряването на PR към ревизиите на изпълнението на персонала. Настройките, специфични за монтьора, засягат прилягането на личността, но не засягат импортирания статичен регион. Можете също така да добавите всякакви специфични за синтеза настройки към индивидуалните ревизии на синтез на персони.

Създаване на ревизии за персони

Стъпка 8: Генериране на йерархичен скрипт за частична реконфигурация на потока

За да генерирате йерархичен скрипт за частична реконфигурация на потока:

- От командната обвивка на Intel Quartus Prime създайте шаблон за поток, като изпълните следната команда:

- Intel Quartus Prime генерира a10_hier_partial_reconfig/flow.tcl file.

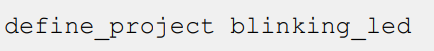

- Преименувайте генерирания a10_hier_partial_reconfig/setup.tcl.exampдо a10_hier_partial_reconfig/setup.tcl и променете скрипта, за да укажете подробности за вашия проект за частично преконфигуриране:

a. За да определите името на проекта, актуализирайте следния ред: b. За да дефинирате основната ревизия, актуализирайте следния ред:

b. За да дефинирате основната ревизия, актуализирайте следния ред:

- За да дефинирате всяка от ревизиите за внедряване на частично преконфигуриране, заедно с имената на PR дяловете и ревизията на източника, която прилага ревизиите, актуализирайте следните редове:

Забележка: Всички ревизионни проекти трябва да са в същата директория като blinking_led.qpf. В противен случай актуализирайте съответно скрипта на потока.

Стъпка 9: Изпълнение на скрипта за поток на йерархична частична реконфигурация

За да изпълните йерархичния скрипт за частична реконфигурация на потока:

- Щракнете върху Инструменти ➤ Tcl скриптове. Появява се диалоговият прозорец Tcl Scripts.

- Щракнете върху Добавяне към проекта, прегледайте и изберете a10_hier_partial_reconfig/flow.tcl.

- Изберете a10_hier_partial_reconfig/flow.tcl в панела Libraries и щракнете върху Run.

Този скрипт изпълнява синтеза за трите персони. Intel Quartus Prime генерира SRAM обект File (.sof), частично маскиран SRAM обект File (.pmsf) и необработен двоичен файл File (.rbf) за всяка от персоните.

Забележка: За да стартирате скрипта от командната обвивка на Intel Quartus Prime, въведете следната команда:

- Компилирайте проекта за частично преконфигуриране

- Използване на скрипта на потока за частично преконфигуриране

- Конфигуриране на скрипта на потока за частично преконфигуриране

- Генериране на програмиране Files

Стъпка 10: Програмиране на дъската

Преди да започнете:

- Свържете захранването към платката за разработка Intel Arria 10 SoC.

- Свържете USB Blaster кабела между USB порта на вашия компютър и USB Blaster порта на развойната платка.

За да стартирате дизайна на платката за разработка Intel Arria 10 SoC:

- Отворете софтуера Intel Quartus Prime и щракнете върху Инструменти ➤ Програмист.

- В Programmer щракнете върху Hardware Setup и изберете USB-Blaster.

- Щракнете върху Автоматично откриване и изберете устройството, 10AS066N3.

- Натиснете OK. Софтуерът Intel Quartus Prime открива и актуализира програмиста с трите FPGA чипа на платката.

- Изберете устройството 10AS066N3, щракнете върху Промяна File и заредете blinking_led_pr_alpha.sof file.

- Активиране на програма/конфигуриране за blinking_led_pr_alpha.sof file.

- Щракнете върху Старт и изчакайте лентата за напредъка да достигне 100%.

- Наблюдавайте светодиодите на платката да мигат със същата честота като оригиналния плосък дизайн.

- За да програмирате само дъщерния PR регион, щракнете с десния бутон върху blinking_led_pr_alpha.sof file в програмиста и щракнете върху Добавяне на PR програмиране File.

- Изберете blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file.

- Деактивирайте програмата/Конфигурирайте за blinking_led_pr_alpha.sof file.

- Активиране на програма/конфигуриране за blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file и щракнете върху Старт. На платката наблюдавайте LED[0] и LED[1], които продължават да мигат. Когато лентата за напредъка достигне 100%, LED[2] мига със същата скорост, а LED[3] мига по-бавно.

- За да програмирате както родителския, така и дъщерния PR регион, щракнете с десния бутон върху .rbf file в програмиста и щракнете върху Промяна на PR програмирането File.

- Изберете blinking_led_pr_delta.pr_parent_partition.rbf file.

- Щракнете върху Старт. На платката наблюдавайте, че светодиодите [0] и светодиодите [1] продължават да мигат. Когато лентата за напредък достигне 100%, и LED[2], и LED[3] мигат по-бавно.

- Повторете горните стъпки, за да препрограмирате динамично само дъщерния PR регион или едновременно родителския и дъщерния PR региони.

Фигура 10. Програмиране на платката за разработка Intel Arria 10 SoC

Модифициране на съществуваща личност

- Можете да промените съществуваща персона, дори след пълно компилиране на основната ревизия.

- Напримерample, за да накара blinking_led_child_slow да мига още по-бавно:

- В blinking_led_child_slow.sv file, променете параметъра COUNTER_TAP от 27 на 28.

- За повторно синтезиране и реимплементиране на тази персона, трябва да компилирате повторно всички ревизии само за синтез и ревизии за изпълнение, засегнати от промяната. Променете скрипта setup.tcl, за да включите следните редове:

Забележка: Когато дефинирате pr_parent_parition за blinking_led_pr_delta ревизия, вие импортирате окончателната моментна снимка на това лице за внедряване. В резултат на това изпълнението на логиката на родителския дял остава същото, като същевременно се модифицира и внедрява съответният дъщерен дял.

Забележка: Когато дефинирате pr_parent_parition за blinking_led_pr_delta ревизия, вие импортирате окончателната моментна снимка на това лице за внедряване. В резултат на това изпълнението на логиката на родителския дял остава същото, като същевременно се модифицира и внедрява съответният дъщерен дял. Тази команда повторно синтезира версията на синтеза на blinking_led_child_slow и след това стартира компилирането на внедряването на PR с помощта на blinking_led_pr_bravo.

Тази команда повторно синтезира версията на синтеза на blinking_led_child_slow и след това стартира компилирането на внедряването на PR с помощта на blinking_led_pr_bravo. - За да извършите компилация на ревизиите само за синтез, изпълнете следната команда: Тази команда не компилира повторно основната ревизия.

- За да извършите компилация на ревизиите на изпълнението, изпълнете следната команда:

- Тази команда не прекомпилира основната ревизия.

- Следвайте стъпките в Стъпка 10: Програмиране на платката на страница 22, за да програмирате получения RBF file в FPGA.

Забележка: За да избегнете изпълнението на целия поток за всяка ревизия, дефинирайте ревизиите само за синтез и ревизиите за изпълнение в скрипта setup.tcl и стартирайте скрипта.

Добавяне на нова личност към дизайна

След пълното компилиране на вашите базови ревизии, все още можете да добавяте нови персони и индивидуално да компилирате тези персони.

Напримерample, за да дефинирате нова детска личност за blinking_led_parent_slow, която изключва led_three:

- Копирайте blinking_led_child_empty.sv в blinking_led_chdild_off.sv.

- В blinking_led_child_off.sv file, модифицирайте присвояването, присвоете led_three_on = 1'b0; за присвояване на led_three_on = 1'b1;. Уверете се, че сте променили името на модула от blinking_led_child_empty на blinking_led_child_off.

- Създайте нова ревизия на синтез, blinking_led_child_off, като следвате стъпките в Създаване на ревизии само за синтез на страница 16.

Забележка: Ревизията blinking_led_child_off трябва да използва blinking_led_child_off.sv file. - Създайте нова ревизия на внедряване, blinking_led_pr_foxtrot, като следвате стъпките в Създаване на ревизии на внедряване на страница 15.

- Актуализирайте a10_hier_partial_reconfig/setup.tcl file за определяне на новото PR изпълнение:

- Компилирайте само тази нова ревизия на синтез и реализация, като изпълните следната команда:

За пълна информация относно йерархичната частична реконфигурация за устройства Intel Arria 10 вижте Създаване на проект за частична реконфигурация в Том 1 на Наръчника за Intel Quartus Prime Pro Edition.

Свързана информация

- Създаване на проект за частично преконфигуриране

- Онлайн обучение за частично преконфигуриране

История на ревизиите на документа

Таблица 5. История на редакциите на документи

| Версия на документа | Софтуерна версия | Промени |

| 2017.11.06 | 17.1.0 | • Актуализиран Референтни изисквания за проектиране раздел с версията на софтуера

• Актуализиран Плосък референтен дизайн без PR разделяне фигура с промени в блока на дизайна • Актуализиран Референтен дизайн Files таблица с информация за Модул Top_counter.sv • Актуализиран Частична преконфигурирана IP ядро интеграция фигура с промени в блока на дизайна • Актуализирани цифрите – Прозорец за проектиране на дялове и Прозорец за региони за логическо заключване за отразяване на новия GUI • File промени в имената • Редакции на текст |

| 2017.05.08 | 17.0.0 | Първоначалното издаване на документа |

Документи / Ресурси

|

intel AN 805 йерархична частична реконфигурация на дизайн на Arria 10 SoC платка за разработка [pdf] Ръководство за потребителя AN 805 Йерархична частична реконфигурация на дизайн на Arria 10 SoC платка за разработка, AN 805, Йерархична частична реконфигурация на дизайн на Arria 10 SoC развойна платка, Реконфигурация на дизайн на Arria 10 SoC развойна платка, Arria 10 SoC развойна платка, 10 SoC Съвет за развитие |