intel AN 805 Arria 10 SoC Geliştirme Kartındaki Tasarımın Hiyerarşik Kısmi Yeniden Yapılandırılması

Intel® Arria® 10 SoC Geliştirme Kartı için Hiyerarşik Kısmi Yeniden Yapılandırma Eğitimi

Bu uygulama notu, basit bir tasarımın hiyerarşik olarak kısmen yeniden yapılandırılabilir bir tasarıma dönüştürülmesini ve tasarımın Intel® Arria® 10 SoC geliştirme kartına uygulanmasını gösterir. Hiyerarşik kısmi yeniden yapılandırma (HPR), başka bir PR bölgesi içinde bir PR bölgesini içerdiğiniz özel bir kısmi yeniden yapılandırma (PR) türüdür. Hem alt hem de üst bölümler için birden fazla kişi oluşturabilirsiniz. Alt bölümleri ana bölümlerinin içine yerleştirirsiniz. Bir alt bölümün yeniden yapılandırılması, üst veya statik bölgelerdeki çalışmayı etkilemez. Bir üst bölümün yeniden yapılandırılması statik bölgedeki işlemi etkilemez ancak üst bölgenin alt bölümlerini varsayılan alt bölüm kişilikleriyle değiştirir. Bu metodoloji, birden fazla işlevin aynı FPGA cihaz kaynaklarını zaman paylaşımında bulunduğu sistemlerde etkilidir.

Kısmi yeniden yapılandırma, düz tasarımda aşağıdaki ilerlemeleri sağlar:

- Çalışma zamanı tasarımının yeniden yapılandırılmasına izin verir

- Tasarımın ölçeklenebilirliğini artırır

- Sistemin kapalı kalma süresini azaltır

- Tasarımda dinamik zaman çoğullama işlevlerini destekler

- Pano alanının verimli kullanımı sayesinde maliyeti ve güç tüketimini azaltır

- Not:

- Bu referans tasarımının uygulanması, Intel Quartus® Prime FPGA uygulama akışına ilişkin temel bilgi ve birincil Intel Quartus Prime projesine ilişkin bilgi gerektirir files.

İlgili Bilgiler

- Intel Arria 10 SoC Geliştirme Kiti Kullanıcı Kılavuzu

- Kısmi Yeniden Yapılandırma Kavramları

- Kısmi Yeniden Yapılandırma Tasarım Akışı

- Kısmi Yeniden Yapılandırma Tasarım Önerileri

- Kısmi Yeniden Yapılandırma Tasarımıyla İlgili Hususlar

Referans Tasarım Gereksinimleri

Bu referans tasarımı aşağıdakileri gerektirir:

- Tasarım uygulaması için Intel Quartus Prime Pro Edition yazılımının 17.1 sürümü.

- FPGA uygulaması için Intel Arria 10 SoC geliştirme kiti.

Intel Kurumu. Her hakkı saklıdır. Intel, Intel logosu ve diğer Intel markaları, Intel Corporation'ın veya yan kuruluşlarının ticari markalarıdır. Intel, FPGA ve yarı iletken ürünlerinin performansını Intel'in standart garantisine uygun olarak mevcut spesifikasyonlara göre garanti eder, ancak herhangi bir zamanda önceden haber vermeksizin herhangi bir ürün ve hizmette değişiklik yapma hakkını saklı tutar. Intel, Intel tarafından yazılı olarak açıkça kabul edilmedikçe, burada açıklanan herhangi bir bilgi, ürün veya hizmetin uygulanmasından veya kullanılmasından kaynaklanan hiçbir sorumluluk veya yükümlülük kabul etmez. Intel müşterilerine, yayınlanan herhangi bir bilgiye güvenmeden ve ürün ya da hizmet siparişi vermeden önce aygıt özelliklerinin en son sürümünü edinmeleri önerilir.

- Diğer isimler ve markalar başkalarının malı olarak iddia edilebilir.

Referans Tasarımı Bittiview

- Bu referans tasarımı bir adet 32 bitlik sayaçtan oluşur. Kart düzeyinde tasarım, saati 50 MHz'lik bir kaynağa bağlar ve çıkışı FPGA üzerindeki dört LED'e bağlar. Sayaç bitlerinden çıkışın belirli bir sırayla seçilmesi, LED'lerin belirli bir frekansta yanıp sönmesine neden olur.

Şekil 1. PR Bölümlendirmesi Olmayan Düz Referans Tasarımı

Referans tasarım Files

Kısmi yeniden yapılandırma eğitimi aşağıdaki konumda mevcuttur: https://github.com/intel/fpga-partial-reconfig

Öğreticiyi indirmek için:

- Klonla veya indir'e tıklayın.

- ZIP'i İndir'i tıklayın. FPGA-partial-config-master.zip dosyasını açın file.

- Referans tasarımına erişmek için öğreticiler/a10_soc_devkit_blinking_led_hpr alt klasörüne gidin.

Düz klasör aşağıdakilerden oluşur files:

Tablo 1. Referans Tasarımı Files

| File İsim | Tanım |

| tepe. SV | üst düzey file tasarımın düz uygulamasını içerir. Bu modül, flashing_led alt bölümünü ve top_counter modülünü başlatır. |

| top_counter.sv | LED'i[32] doğrudan kontrol eden üst düzey 1 bit sayaç. Sayacın kayıtlı çıkışı LED[0]'ı kontrol eder ve ayrıca yanıp sönen_led modülü aracılığıyla LED[2] ve LED[3]'e güç sağlar. |

| yanıp sönen_led.sdc | Proje için zamanlama kısıtlamalarını tanımlar. |

| devam etti… | |

| File İsim | Tanım |

| yanıp sönen_led.SV | Bu öğreticide, bu modülü bir ana PR bölümüne dönüştüreceksiniz. Modül, LED[2] ve LED[3]'ü kontrol eden top_counter modülünün kayıtlı çıkışını alır. |

| yanıp sönen_led.qpf | Intel Quartus Prime projesi file projedeki tüm revizyonların listesini içerir. |

| yanıp sönen_led.qsf | Intel Quartus Prime ayarları file Projeye ilişkin atamaları ve ayarları içerir. |

Not: hpr klasörü tam set içerir fileBu uygulama notunu kullanarak oluşturduğunuz. Bunları referans alın fileİzlenecek yol sırasında herhangi bir noktada.

Şekil 2. Referans Tasarımı Files

Referans Tasarım Çözüm Yolu

Aşağıdaki adımlarda kısmi yeniden yapılandırmanın düz bir tasarıma uygulanması açıklanmaktadır. Eğitimde Intel Arria 10 SoC geliştirme kartı için Intel Quartus Prime Pro Edition yazılımı kullanılıyor:

- Adım 1: Başlarken sayfa 6

- Adım 2: Çocuk Düzeyinde Alt Modül Oluşturma sayfa 6

- Adım 3: Tasarım Bölümleri Oluşturma sayfa 7

- Adım 4: PR Bölümleri için Yerleştirme ve Yönlendirme Bölgesini Tahsis Etme sayfa 9

- Adım 5: Intel Arria 10 Kısmi Yeniden Yapılandırma Denetleyici IP Çekirdeğini Ekleme sayfa 10

- Adım 6: Kişileri Tanımlama sayfa 13

- Adım 7: Revizyon Oluşturma sayfa 15

- Adım 8: Hiyerarşik Kısmi Yeniden Yapılandırma Akış Komut Dosyasını Oluşturma şu sayfada 20

- Adım 9: Hiyerarşik Kısmi Yeniden Yapılandırma Akış Komut Dosyasını Çalıştırma sayfa 21

- Adım 10: Kartın Programlanması sayfa 22

Adım 1: Başlarken

Referans tasarımını kopyalamak için fileçalışma ortamınıza ekleyin ve flashing_led düz tasarımını derleyin:

- Çalışma ortamınızda bir dizin oluşturun: a10_soc_devkit_blinking_led_hpr.

- İndirilen öğreticiler/a10_soc_devkit_blinking_led_hpr/flat alt klasörünü a10_soc_devkit_blinking_led_hpr dizinine kopyalayın.

- Intel Quartus Prime Pro Edition yazılımında, File ➤ Project'i açın ve yanıp sönen_led.qpf'yi seçin.

- Düz tasarımı derlemek için İşleme ➤ Derlemeyi Başlat'a tıklayın.

Adım 2: Çocuk Düzeyinde Alt Modül Oluşturma

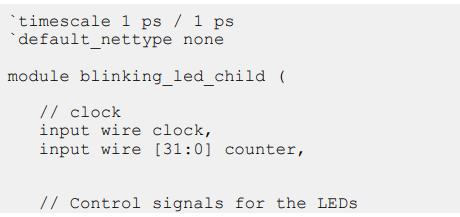

Bu düz tasarımı hiyerarşik bir PR tasarımına dönüştürmek için, üst alt modülün (blinking_led.sv) içine yerleştirilmiş bir alt alt modül (blinking_led_child.SV) oluşturmalısınız.

- Yeni bir tasarım oluşturun file, flashing_led_child.sv'yi oluşturun ve buna aşağıdaki kod satırlarını ekleyin file: zaman ölçeği 1 ps / 1 ps `default_nettype yok modül yanıp sönen_led_child ( // saat giriş kablosu saati, giriş kablosu [31:0] sayacı, // LED'ler için kontrol sinyalleri

- Blinking_led.sv'yi değiştirin file led_two_on'u statik bölgeden sayacın 23. bitine bağlamak ve flashing_led_child modülünü başlatmak için. Değişikliklerden sonra, flashing_led.sv dosyanız file aşağıdaki gibi görünmelidir:

- Tüm tasarımın değiştirilmesi hakkında files, İşleme ➤ Derlemeyi Başlat'ı tıklatarak projeyi yeniden derleyin

Adım 3: Tasarım Bölümleri Oluşturma

Kısmen yeniden yapılandırmak istediğiniz her PR bölgesi için tasarım bölümleri oluşturmalısınız. Tasarımınızda istediğiniz sayıda bağımsız bölüm veya PR bölgesi oluşturabilirsiniz. Bu öğretici, u_blinking_led_child ve u_blinking_led örnekleri için iki tasarım bölümü oluşturur.

Hiyerarşik kısmi yeniden yapılandırmaya yönelik tasarım bölümleri oluşturmak için:

- Proje Gezgini'nde u_blinking_led_child örneğine sağ tıklayın ve Tasarım Bölümü ➤ Tasarım Bölümü Olarak Ayarla seçeneğine tıklayın. Bölüm olarak ayarlanan her örneğin yanında bir tasarım bölümü simgesi görünür.

Şekil 3. Project Navigator'dan Tasarım Bölümleri Oluşturma

- Bölüm Türünü tanımlamak için Hiyerarşi sekmesinde u_blinking_led_child örneğine sağ tıklayın, Tasarım Bölümü ➤ Yeniden Yapılandırılabilir seçeneğine tıklayın. Bölüm Türünü yalnızca örneği bir bölüm olarak ayarladıktan sonra tanımlayabilirsiniz. Tasarım bölümü Ödevler'de görünür View Tasarım Bölümleri Penceresinin sekmesi.

Şekil 4. Tasarım Bölümleri Penceresi

- Tasarım Bölümleri Penceresinde bölüm adını çift tıklatarak düzenleyin. Bu referans tasarımı için bölüm adını pr_partition olarak yeniden adlandırın.

Not: Bir bölüm oluşturduğunuzda Intel Quartus Prime yazılımı, örnek adı ve hiyerarşi yoluna göre otomatik olarak bir bölüm adı oluşturur. Bu varsayılan bölüm adı her örneğe göre değişebilir. - u_blinking_led örneğine yeniden yapılandırılabilir tasarım bölümleri atamak için 1. ve 2. adımları tekrarlayın. Bu bölümü pr_parent_partition olarak yeniden adlandırın.

Blashing_led.qsf dosyasının, yeniden yapılandırılabilir tasarım bölümlerinize karşılık gelen aşağıdaki atamaları içerdiğini doğrulayın:

Kısmi Yeniden Yapılandırma için Tasarım Bölümleri Oluşturun

Adım 4: PR Bölümlerine Yerleştirme ve Yönlendirme Bölgesi Tahsis Etme

Temel revizyonu oluşturduğunuzda, PR tasarım akışı, karşılık gelen personel çekirdeğini ayrılmış bölgeye yerleştirmek için PR bölümleme bölge tahsisinizi kullanır. Temel revizyonunuz için cihaz kat planında PR bölgesini bulmak ve atamak için:

- Proje Gezgini'nde u_blinking_led_child örneğine sağ tıklayın ve Logic Lock Region ➤ Create New Logic Lock Region seçeneğine tıklayın. Bölge, Mantıksal Kilit Bölgeleri Penceresinde görünür.

- Yerleştirme bölgeniz, flashing_led_child mantığını içermelidir. Chip Planner'da düğümü bularak yerleştirme bölgesini seçin. Proje Gezgini'nde u_blinking_led_child bölge adına sağ tıklayın ve Düğümü Bul ➤ Chip Planner'da Bul'a tıklayın.

Şekil 5. Blinking_led için Çip Planlayıcı Düğüm Konumu

- Mantıksal Kilit Bölgeleri penceresinde, Orijin sütununda yerleştirme bölgesi koordinatlarını belirtin. Başlangıç, bölgenin sol alt köşesine karşılık gelir. Eski içinampDosyada (X1 Y1) koordinatları (69 10) olan bir yerleştirme bölgesini ayarlamak için Orijini X69_Y10 olarak belirtin. Intel Quartus Prime yazılımı, belirttiğiniz yükseklik ve genişliğe göre yerleştirme bölgesinin (X2 Y2) koordinatlarını (sağ üstte) otomatik olarak hesaplar.

Not: Bu öğretici, yerleştirme bölgesi için (X1 Y1) koordinatlarını (69 10) ve 20 yükseklik ve genişliğini kullanır. Bölgenin yanıp sönen_led_çocuk mantığını kapsaması koşuluyla, yerleştirme bölgesi için herhangi bir değer tanımlayın. - Ayrılmış ve Yalnızca Çekirdek seçeneklerini etkinleştirin.

- Yönlendirme Bölgesi seçeneğine çift tıklayın. Mantık Kilidi Yönlendirme Bölgesi Ayarları iletişim kutusu görüntülenir.

- Yönlendirme türü için Genişletmeyle sabit'i seçin. Bu seçeneğin seçilmesi otomatik olarak 1'lik bir genişletme uzunluğu atar.

Not: Motor farklı kişileri yönlendirirken Tesisatçıya ekstra esneklik sağlamak için yönlendirme bölgesinin yerleştirme bölgesinden daha büyük olması gerekir. - u_blinking_led örneği için 1-6 arasındaki adımları tekrarlayın. Ebeveyn düzeyinde yerleşim u_blinking_led örneği için 1-6 arasındaki adımları tekrarlayın. Üst düzey yerleşim bölgesi, üst düzey mantık yerleşimi için yeterli alana izin verirken karşılık gelen alt düzey yerleşim ve yönlendirme bölgelerini tamamen kapsamalıdır. Bu öğreticide u_blinking_led örneğinin yerleştirme bölgesi için (X1 Y1) koordinatları – (66 7), 47 yüksekliği ve 26 genişliği kullanılmaktadır.

Şekil 6.Logic Kilit Bölgeleri Penceresi

Blinking_led.qsf dosyasının kat planlamanıza karşılık gelen aşağıdaki atamaları içerdiğini doğrulayın:

- Kısmi Yeniden Yapılandırma Tasarımının Kat Planı

- Kısmi Yeniden Yapılandırmanın Kademeli Olarak Uygulanması

5. Adım: Intel Arria 10 Kısmi Yeniden Yapılandırma Denetleyicisi IP Çekirdeğini Ekleme

- PR bölümünü yeniden yapılandırmak için Intel Arria 10 Kısmi Yeniden Yapılandırma Denetleyicisi IP çekirdeğini kullanın. Bu IP çekirdeği J'yi kullanırTAG PR bölümünü yeniden yapılandırmak için. Intel Arria 10 Kısmi Yeniden Yapılandırma Denetleyicisi IP çekirdeğini Intel Quartus Prime projenize eklemek için:

- IP kataloğuna Kısmi Yeniden Yapılandırma yazın.

- IP Parameter Editor Pro penceresini başlatmak için IP kitaplığından Intel Arria 10 Kısmi Yeniden Yapılandırma Denetleyicisi IP çekirdeğini seçin ve Ekle'ye tıklayın.

- Yeni IP Varyantı iletişim kutusunda pr_ip yazın. file adını seçin ve Oluştur'a tıklayın. pr_ip için varsayılan parametrelendirmeyi kullanın. J'yi Etkinleştir seçeneğinin olduğundan emin olun.TAG hata ayıklama modu ve Arayüz dondurmayı etkinleştir seçenekleri açık ve Avalon-MM yedek arayüzünü etkinleştir seçeneği kapalı.

Şekil 7. Intel Arria 10 Kısmi Yeniden Yapılandırma Denetleyicisi IP Çekirdek Parametreleri

- Son'a tıklayın ve sistemi oluşturmadan parametre düzenleyicisinden çıkın. Intel Quartus Prime yazılımı pr_ip.ip IP varyasyonunu oluşturur fileve şunu ekler: file yanıp sönen_led projesine.

Not:

- pr_ip.ip dosyasını kopyalıyorsanız file hpr klasöründen, flashing_led.qsf dosyasını manuel olarak düzenleyin file şu satırı eklemek için: set_global_questment -name IP_FILE pr_ip.ip

- IP_'yi yerleştirinFILE SDC_ sonrasında atamaFILE ödevler (jtag.sdc ve flashing_led.sdc) flashing_led.qsf dosyanızda file. Bu sıralama, Kısmi Yeniden Yapılandırma IP çekirdeğinin uygun şekilde sınırlandırılmasını sağlar.

Not: Saatleri tespit etmek için SDC file PR için IP, IP çekirdeğinin kullandığı saatleri oluşturan herhangi bir SDC'yi takip etmelidir. .ip'i sağlayarak bu düzeni kolaylaştırırsınız file PR IP çekirdeği için herhangi bir .ip'ten sonra gelir files veya SDC fileQSF'de bu saatleri oluşturmak için kullanılır file Intel Quartus Prime proje revizyonunuz için. Daha fazla bilgi için Kısmi Yeniden Yapılandırma IP Çekirdeği Kullanıcı Kılavuzu'ndaki Zamanlama Kısıtlamaları bölümüne bakın.

İlgili Bilgiler

- Kısmi Yeniden Yapılandırma IP Çözümleri Kullanım Kılavuzu

- Kısmi Yeniden Yapılandırma Bölge Denetleyicisi IP çekirdeği hakkında bilgi için.

- Kısmi Yeniden Yapılandırma IP Çekirdeği Kullanıcı Kılavuzu

- Zamanlama kısıtlamaları hakkında bilgi için.

Üst Düzey Tasarımın Güncellenmesi

Top.SV'yi güncellemek için file PR_IP örneğiyle:

- PR_IP örneğini üst düzey tasarıma eklemek için üstteki aşağıdaki kod bloğunun açıklamasını kaldırın.SV file:

- Yeniden yapılandırma sırasında çıkış bağlantı noktalarını mantık 1'e zorlamak için PR_IP'den gelen dondurma kontrol sinyali çıkışını kullanın. Bununla birlikte, alt bölümü PR programlarken LED'in ana PR bölümünden yanıp sönmeye devam ettiğini gözlemlemek için dondurma kontrol sinyali led_two_on'u kapatmaz. pr_led_two_on'un doğrudan olduğundan emin olun

- Varsayılan ana kişiliğin (yanıp sönen_led) bir örneğini atamak için top.SV'yi güncelleyin. file aşağıdaki kod bloğuyla:

Şekil 8. Kısmi Yeniden Yapılandırma IP Çekirdek Entegrasyonu

Adım 6: Kişileri Tanımlama

Bu referans tasarımı, ebeveyn ve alt PR bölümleri için beş ayrı kişiyi tanımlar. Kişileri tanımlamak ve projenize dahil etmek için:

- Dört SystemVerilog oluşturun fileBeş kişi için çalışma dizininizde s, Blashing_led_child.sv, Blashing_led_child_slow.sv, Blashing_led_child_empty.sv ve Blashing_led_slow.sv.

Not: SystemVerilog'u oluşturursanız fileIntel Quartus Prime Metin Düzenleyicisi'nden Ekle'yi devre dışı bırakın file kaydederken mevcut proje seçeneğine files.

Tablo 2. Referans Tasarım Kişileri

| File İsim | Tanım | Kod |

| yanıp sönen_led_child.sv | Çocuk düzeyindeki tasarım için varsayılan kişilik |

`zaman ölçeği 1 ps / 1 ps `default_nettype yok modül yanıp sönen_led_child ( // saat giriş teli saati, giriş kablosu [31:0] sayacı,

// LED'lerin çıkış kablosu için kontrol sinyalleri led_third_on

); localparam COUNTER_TAP = 23; reg led_third_on_r;

led_third_on = led_third_on_r'yi atayın; Always_ff @(posedge saat) begin led_third_on_r <= sayaç[COUNTER_TAP]; son

modül sonu |

| devam etti… | ||

| File İsim | Tanım | Kod |

| yanıp sönen_led_child_slow.sv | The

LED_THREE daha yavaş yanıp sönüyor |

`zaman ölçeği 1 ps / 1 ps `default_nettype hiçbiri

modül yanıp sönen_led_child_slow (

// saat giriş teli saati, giriş kablosu [31:0] sayacı,

// LED'lerin çıkış kablosu için kontrol sinyalleri led_third_on );

localparam COUNTER_TAP = 27; reg led_third_on_r;

led_third_on = led_third_on_r'yi atayın; Always_ff @(posedge saat) begin led_third_on_r <= sayaç[COUNTER_TAP]; son

modül sonu |

| yanıp sönen_led_child_empty.sv | The

LED_THREE kalmak |

`zaman ölçeği 1 ps / 1 ps `default_nettype hiçbiri

modül yanıp sönen_led_child_empty (

// saat giriş teli saati, giriş kablosu [31:0] sayacı,

// LED'lerin çıkış kablosu için kontrol sinyalleri led_third_on

);

// LED aktif düşük led_third_on = 1'b0'ı atayın;

modül sonu |

| yanıp sönen_led_slow.sv | LED_TWO

daha yavaş yanıp söner. |

`zaman ölçeği 1 ps / 1 ps `default_nettype yok modül flashing_led_slow( // saat giriş teli saati, giriş kablosu [31:0] sayacı,

// LED'lerin çıkış kablosu için kontrol sinyalleri led_two_on, çıkış kablosu led_third_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; led_two_on = led_two_on_r'yi atayın;

// Sayaç: Always_ff @(posedge saat) begin led_two_on_r <= counter[COUNTER_TAP]; son

yanıp sönen_led_child u_blinking_led_child( .led_third_on (led_third_on), .counter (sayaç), .saat (saat) |

| File İsim | Tanım | Kod |

| );ndmodule |

Adım 3: Tasarım Bölümleri Oluşturma sayfa 7

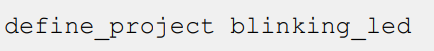

Adım 7: Düzeltme Oluşturma

PR tasarım akışı, Intel Quartus Prime yazılımındaki proje revizyonları özelliğini kullanır. İlk tasarımınız, FPGA üzerinde statik bölge sınırlarını ve yeniden yapılandırılabilir bölgeleri tanımladığınız temel revizyondur. Temel revizyondan birden fazla revizyon oluşturursunuz. Bu revizyonlar PR bölgelerine yönelik farklı uygulamaları içermektedir. Ancak tüm PR uygulama revizyonları, temel revizyondaki aynı üst düzey yerleştirme ve yönlendirme sonuçlarını kullanır. Bir PR tasarımını derlemek için her karakter için bir PR uygulama revizyonu ve sentez revizyonu oluşturmalısınız. Bu referans tasarımında, temel revizyona (blinking_led) ek olarak, çocuk düzeyindeki üç kişilik ve ebeveyn düzeyindeki iki kişilik, beş ayrı sentez revizyonu ve beş ayrı uygulama revizyonu içerir:

Tablo 3. İki Ebeveynli Personalar ve Üç Çocuklu Personalara İlişkin Düzeltmeler

| Sentez Revizyonu | Uygulama Revizyonu |

| yanıp sönen_led_ebeveyn, yanıp sönen_led_varsayılan | yanıp sönen_led_pr_alpha |

| yanıp sönen_led_ebeveyn, yanıp sönen_led_çocuk_yavaş | yanıp sönen_led_pr_bravo |

| yanıp sönen_led_ebeveyn, yanıp sönen_led_çocuk_boş | yanıp sönen_led_pr_charlie |

| yanıp sönen_led_parent_slow, yanıp sönen_led_child_slow | yanıp sönen_led_pr_delta |

| yanıp sönen_led_parent_slow, yanıp sönen_led_child_empty | yanıp sönen_led_pr_emma |

Uygulama Revizyonları Oluşturma

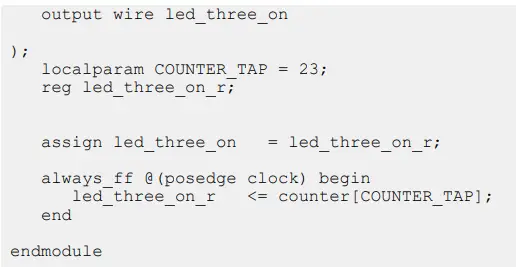

PR uygulama revizyonlarını oluşturmak için:

- Revizyonlar iletişim kutusunu açmak için Proje ➤ Revizyonlar'a tıklayın.

- Yeni bir revizyon oluşturmak için <'ye çift tıklayın. >.

- Revizyon adını yanıp sönen_led_pr_alpha olarak belirtin ve Revizyona Dayalı olarak yanıp sönen_led'i seçin.

- Geçerli revizyon olarak ayarla seçeneğini devre dışı bırakın ve Tamam'a tıklayın.

- Benzer şekilde, Blashing_led revizyonunu temel alarak, Blashing_led_pr_bravo, Blashing_led_pr_charlie, Blashing_led_pr_delta ve Blashing_led_pr_emma revizyonlarını oluşturun.

Not: Yukarıdaki revizyonları güncel revizyon olarak ayarlamayın.

Şekil 9. Revizyon Oluşturma

Yalnızca Sentez Revizyonları Oluşturma

Kişilere yönelik yalnızca sentez revizyonları oluşturmak için üst düzey varlığı ve karşılık gelen SystemVerilog'u atamanız gerekir. file kişiliklerin her biri için:

- Intel Quartus Prime yazılımında Proje ➤ Revizyonlar'a tıklayın.

- Blashing_led revizyonuna dayalı olarak Blashing_led_default revizyonu oluşturun. Bu revizyonu güncel revizyon olarak ayarlamayın.

- Blashing_led_default.qsf dosyasını değiştirin file aşağıdaki görevleri içerecektir:

set_global_questment -name TOP_LEVEL_ENTITY yanıp sönen_led_child

set_global_questment -name SYSTEMVERILOG_FILE - Benzer şekilde, Blashing_led revizyonuna dayalı olarak, Blashing_led_child_slow, Blashing_led_child_empty, Blashing_led_parent ve Blashing_led_parent_slow revizyonlarını oluşturun. Bu revizyonları güncel revizyonlar olarak ayarlamayın.

- Blashing_led_child_slow.qsf, Blashing_led_child_empty.qsf, Blashing_led_parent.qsf ve Blashing_led_parent_slow.qsf'yi güncelleyin filekarşılık gelenleriyle birlikte

TOP_LEVEL_ENTITY ve SYSTEMVERILOG_FILE ödevler:

- Sentez hatalarını önlemek için sentez revizyonunun yapıldığından emin olun. fileAlt bölümlere ait e-postalar herhangi bir tasarım bölümü, pin ataması veya Mantık Kilidi içermez

bölge atamaları Ayrıca sentez revizyonu fileAna bölümlere ait e-postalar yalnızca karşılık gelen alt bölümler için tasarım bölümü atamalarını içermelidir. Blinking_led_default.qsf, Blashing_led_child_slow.qsf, Blashing_led_child_empty.qsf, Blashing_led_parent.qsf ve Blashing_led_parent_slow.pdf dosyasındaki bu atamaları (varsa) kaldırın. files

- Blashing_led_parent.qsf ve flashing_led_parent_slow.qsf dosyasına aşağıdaki atamaları ekleyin files:

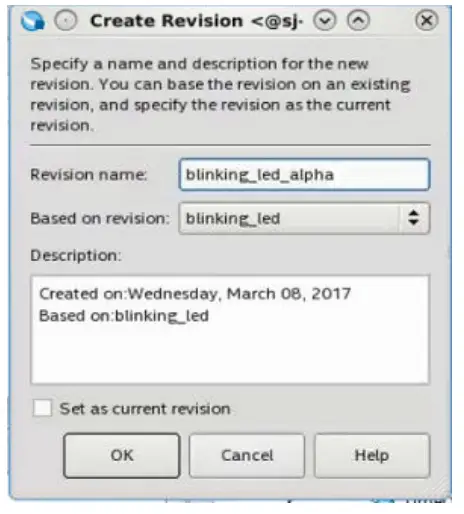

- Blinking_led.qpf dosyasının doğru olduğunu doğrulayın file belirli bir sıraya göre aşağıdaki revizyonları içerir:

- Not: Düzeltmeyi kopyalıyorsanız filehpr klasöründen, flashing_led.qpf dosyasını manuel olarak güncelleyin file yukarıdaki kod satırlarıyla.

Revizyon Türünü Belirleme

Her revizyonunuza revizyon tipi atamanız gerekmektedir. Üç revizyon türü vardır:

- Kısmi Yeniden Yapılandırma – Temel

- Kısmi Yeniden Yapılandırma – Persona Sentezi

- Kısmi Yeniden Yapılandırma – Persona Uygulaması

- Aşağıdaki tablo, revizyonların her biri için revizyon tipi atamaları listelemektedir:

Tablo 4. Revizyon Türleri

| Revizyon Adı | Revizyon Türü |

| yanıp sönen_led.qsf | Kısmi Yeniden Yapılandırma – Temel |

| yanıp sönen_led_default.qsf | Kısmi Yeniden Yapılandırma – Persona Sentezi |

| flashing_led_child_empty.qsf | Kısmi Yeniden Yapılandırma – Persona Sentezi |

| yanıp sönen_led_child_slow.qsf | Kısmi Yeniden Yapılandırma – Persona Sentezi |

| yanıp sönen_led_parent.qsf | Kısmi Yeniden Yapılandırma – Persona Sentezi |

| flashing_led_parent_slow.qsf | Kısmi Yeniden Yapılandırma – Persona Sentezi |

| yanıp sönen_led_pr_alpha.qsf | Kısmi Yeniden Yapılandırma – Persona Uygulaması |

| yanıp sönen_led_pr_bravo.qsf | Kısmi Yeniden Yapılandırma – Persona Uygulaması |

| yanıp sönen_led_pr_charlie.qsf | Kısmi Yeniden Yapılandırma – Persona Uygulaması |

| yanıp sönen_led_pr_delta.qsf | Kısmi Yeniden Yapılandırma – Persona Uygulaması |

| yanıp sönen_led_pr_emma.qsf | Kısmi Yeniden Yapılandırma – Persona Uygulaması |

- Proje ➤ Düzeltmeler'e tıklayın. Düzeltmeler iletişim kutusu görüntülenir.

- Revizyon Adı sütununda flashing_led'i seçin ve Geçerliyi Ayarla'ya tıklayın.

- Uygula'yı tıklayın. Blashing_led revizyonu açılır.

- Blinking_led'in revizyon türünü ayarlamak için Atamalar ➤ Ayarlar ➤ Genel'e tıklayın.

- Revizyon Tipini Kısmi Yeniden Yapılandırma – Temel olarak seçin.

- Benzer şekilde, diğer on revizyon için revizyon türlerini yukarıdaki tabloda listelendiği gibi ayarlayın.

- Not: Revizyon tipini atamadan önce her revizyonu geçerli revizyon olarak ayarlamanız gerekir. Her .qsf dosyasının file aşağıdaki atamayı içerir:

- Not: PR uygulama derlemesinde kullanmak istediğiniz Tesisatçıya özgü ayarları, kişisel uygulama revizyonlarına ekleyin. Tesisatçıya özgü ayarlar, kişiliğin uyumunu etkiler ancak içe aktarılan statik bölgeyi etkilemez. Bireysel kişisel sentez revizyonlarına senteze özel herhangi bir ayar da ekleyebilirsiniz.

Personalar için Revizyonlar Oluşturun

Adım 8: Hiyerarşik Kısmi Yeniden Yapılandırma Akış Komut Dosyasını Oluşturma

Hiyerarşik kısmi yeniden yapılandırma akış komut dosyasını oluşturmak için:

- Intel Quartus Prime komut kabuğundan aşağıdaki komutu çalıştırarak bir akış şablonu oluşturun:

- Intel Quartus Prime, a10_hier_partial_reconfig/flow.tcl dosyasını oluşturur file.

- Oluşturulan a10_hier_partial_reconfig/setup.tcl.ex dosyasını yeniden adlandırınampa10_hier_partial_reconfig/setup.tcl dosyasına gidin ve kısmi yeniden yapılandırma projenizin ayrıntılarını belirtmek için komut dosyasını değiştirin:

a. Projenin adını tanımlamak için aşağıdaki satırı güncelleyin: b. Temel revizyonu tanımlamak için aşağıdaki satırı güncelleyin:

b. Temel revizyonu tanımlamak için aşağıdaki satırı güncelleyin:

- Kısmi yeniden yapılandırma uygulama revizyonlarının her birini, PR bölüm adları ve revizyonları uygulayan kaynak revizyonuyla birlikte tanımlamak için aşağıdaki satırları güncelleyin:

Not: Tüm revizyon projeleri, flashing_led.qpf ile aynı dizinde olmalıdır. Aksi takdirde akış betiğini uygun şekilde güncelleyin.

Adım 9: Hiyerarşik Kısmi Yeniden Yapılandırma Akış Komut Dosyasını Çalıştırma

Hiyerarşik kısmi yeniden yapılandırma akış komut dosyasını çalıştırmak için:

- Araçlar ➤ Tcl Komut Dosyaları'na tıklayın. Tcl Komut Dosyaları iletişim kutusu görüntülenir.

- Projeye Ekle'ye tıklayın, göz atın ve a10_hier_partial_reconfig/flow.tcl dosyasını seçin.

- Kitaplıklar bölmesinde a10_hier_partial_reconfig/flow.tcl dosyasını seçin ve Çalıştır'a tıklayın.

Bu komut dosyası üç kişiliğin sentezini çalıştırır. Intel Quartus Prime bir SRAM Nesnesi oluşturur File (.sof), Kısmi Maskelenmiş bir SRAM Nesnesi File (.pmsf) ve Ham İkili File (.rbf) her bir karakter için.

Not: Komut dosyasını Intel Quartus Prime komut kabuğundan çalıştırmak için aşağıdaki komutu yazın:

- Kısmi Yeniden Yapılandırma Tasarımını Derleyin

- Kısmi Yeniden Yapılandırma Akış Komut Dosyasını Kullanma

- Kısmi Yeniden Yapılandırma Akış Komut Dosyasını Yapılandırma

- Programlama Oluştur Files

Adım 10: Kurulun Programlanması

Başlamadan önce:

- Güç kaynağını Intel Arria 10 SoC geliştirme kartına bağlayın.

- USB Blaster kablosunu bilgisayarınızın USB bağlantı noktası ile geliştirme kartındaki USB Blaster bağlantı noktası arasına bağlayın.

Tasarımı Intel Arria 10 SoC geliştirme kartında çalıştırmak için:

- Intel Quartus Prime yazılımını açın ve Araçlar ➤ Programcı öğesine tıklayın.

- Programcı'da Donanım Kurulumu'na tıklayın ve USB-Blaster'ı seçin.

- Otomatik Algıla'ya tıklayın ve cihazı seçin (10AS066N3).

- Tamam'ı tıklayın. Intel Quartus Prime yazılımı, programlayıcıyı karttaki üç FPGA yongasıyla algılar ve günceller.

- 10AS066N3 cihazını seçin, Değiştir'e tıklayın File ve flashing_led_pr_alpha.sof dosyasını yükleyin file.

- Blashing_led_pr_alpha.sof için Programlamayı/Yapılandırmayı Etkinleştirin file.

- Başlat'a tıklayın ve ilerleme çubuğunun %100'e ulaşmasını bekleyin.

- Kart üzerindeki LED'lerin orijinal düz tasarımla aynı frekansta yanıp söndüğünü gözlemleyin.

- Yalnızca alt PR bölgesini programlamak için, flashing_led_pr_alpha.sof dosyasına sağ tıklayın. file Programcı'da PR Programlaması Ekle'ye tıklayın File.

- Blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf'yi seçin file.

- Blashing_led_pr_alpha.sof için Program/Yapılandırmayı devre dışı bırakın file.

- Blashing_led_pr_bravo.pr_parent_partition.pr_partition.rbf için Program/Yapılandırmayı etkinleştirin file ve Başlat'a tıklayın. Kart üzerinde LED[0] ve LED[1]'in yanıp sönmeye devam ettiğini gözlemleyin. İlerleme çubuğu %100'e ulaştığında LED[2] aynı hızda yanıp söner ve LED[3] daha yavaş yanıp söner.

- Hem ana hem de alt PR bölgesini programlamak için .rbf'ye sağ tıklayın. file Programcı'da ve PR Programlamasını Değiştir'e tıklayın. File.

- Blinking_led_pr_delta.pr_parent_partition.rbf'yi seçin file.

- Başlat'ı tıklayın. Kart üzerinde LED[0] ve LED[1]'in yanıp sönmeye devam ettiğini gözlemleyin. İlerleme çubuğu %100'e ulaştığında hem LED[2] hem de LED[3] daha yavaş yanıp söner.

- Yalnızca alt PR bölgesini veya hem ana hem de alt PR bölgelerini aynı anda dinamik olarak yeniden programlamak için yukarıdaki adımları tekrarlayın.

Şekil 10. Intel Arria 10 SoC Geliştirme Kartını Programlama

Mevcut Bir Kişiliği Değiştirme

- Temel revizyonu tamamen derledikten sonra bile mevcut bir kişiliği değiştirebilirsiniz.

- ÖrneğinampBlinking_led_child_slow kişiliğinin daha da yavaş yanıp sönmesine neden olmak için:

- Blinking_led_child_slow.sv'de fileCOUNTER_TAP parametresini 27'den 28'e değiştirin.

- Bu kişiliği yeniden sentezlemek ve yeniden uygulamak için, değişiklikten etkilenen tüm yalnızca sentez revizyonlarını ve uygulama revizyonlarını yeniden derlemelisiniz. setup.tcl komut dosyasını aşağıdaki satırları içerecek şekilde değiştirin:

Not: Blashing_led_pr_delta revizyonu için pr_parent_parition'ı tanımlarken, uygulama için o kişinin son anlık görüntüsünü içe aktarırsınız. Sonuç olarak, karşılık gelen alt bölüm değiştirilirken ve uygulanırken ana bölüm mantığının uygulanması aynı kalır.

Not: Blashing_led_pr_delta revizyonu için pr_parent_parition'ı tanımlarken, uygulama için o kişinin son anlık görüntüsünü içe aktarırsınız. Sonuç olarak, karşılık gelen alt bölüm değiştirilirken ve uygulanırken ana bölüm mantığının uygulanması aynı kalır. Bu komut, Blashing_led_child_slow sentez revizyonunu yeniden sentezler ve ardından Blashing_led_pr_bravo'yu kullanarak PR uygulama derlemesini çalıştırır.

Bu komut, Blashing_led_child_slow sentez revizyonunu yeniden sentezler ve ardından Blashing_led_pr_bravo'yu kullanarak PR uygulama derlemesini çalıştırır. - Yalnızca sentez revizyonlarının derlemesini gerçekleştirmek için aşağıdaki komutu çalıştırın: Bu komut, temel revizyonu yeniden derlemez.

- Uygulama revizyonlarının derlemesini gerçekleştirmek için aşağıdaki komutu çalıştırın:

- Bu komut temel revizyonu yeniden derlemez.

- Ortaya çıkan RBF'yi programlamak için Adım 10: Kartın Programlanması sayfa 22 bölümündeki adımları izleyin. file FPGA'ya girin.

Not: Her revizyon için akışın tamamını çalıştırmayı önlemek için, setup.tcl betiğinde yalnızca sentez revizyonlarını ve uygulama revizyonlarını tanımlayın ve betiği çalıştırın.

Tasarıma Yeni Bir Persona Eklemek

Temel revizyonlarınızı tamamen derledikten sonra yine de yeni kişiler ekleyebilir ve bu kişileri ayrı ayrı derleyebilirsiniz.

ÖrneğinampBlinking_led_parent_slow için led_third'i kapatan yeni bir alt karakter tanımlamak için:

- Blashing_led_child_empty.sv'yi Blashing_led_chdild_off.sv'ye kopyalayın.

- Blinking_led_child_off.sv'de file, atamayı değiştirin, led_third_on = 1'b0; atayın led_third_on = 1'b1; atamak için. Modül adını yanıp sönen_led_child_empty'den, yanıp sönen_led_child_off'a değiştirdiğinizden emin olun.

- Yalnızca Sentez Revizyonları Oluşturma sayfa 16 bölümündeki adımları takip ederek yeni bir sentez revizyonu ( Blashing_led_child_off) oluşturun.

Not: Blashing_led_child_off düzeltmesi, flashing_led_child_off.sv dosyasını kullanmalıdır file. - Uygulama Revizyonları Oluşturma sayfa 15 bölümündeki adımları takip ederek yeni bir uygulama revizyonu ( Blashing_led_pr_foxtrot) oluşturun.

- a10_hier_partial_reconfig/setup.tcl dosyasını güncelleyin file yeni PR uygulamasını tanımlamak için:

- Aşağıdaki komutu çalıştırarak yalnızca bu yeni sentez ve uygulama revizyonunu derleyin:

Intel Arria 10 aygıtlarına yönelik hiyerarşik kısmi yeniden yapılandırma hakkında tam bilgi için Intel Quartus Prime Pro Edition El Kitabı'nın 1. Cildinde Kısmi Yeniden Yapılandırma Tasarımı Oluşturma konusuna bakın.

İlgili Bilgiler

- Kısmi Yeniden Yapılandırma Tasarımı Oluşturma

- Kısmi Yeniden Yapılandırma Çevrimiçi Eğitimi

Belge Revizyon Geçmişi

Tablo 5. Belge Revizyon Geçmişi

| Belge Sürümü | Yazılım versiyonu | Değişiklikler |

| 2017.11.06 | 17.1.0 | • Güncellendi Referans Tasarım Gereksinimleri yazılım sürümünün bulunduğu bölüm

• Güncellendi PR Bölümlendirmesi Olmayan Düz Referans Tasarımı tasarım bloğu değişikliklerini içeren şekil • Güncellendi Referans tasarım Files ile ilgili bilgilerin yer aldığı tablo Top_counter.sv modülü • Güncellendi Kısmi Yeniden Yapılandırma IP Çekirdek Entegrasyonu tasarım bloğu değişikliklerini içeren şekil • Rakamlar güncellendi – Tasarım Bölümleri Penceresi Ve Mantık Kilit Bölgeleri Penceresi yeni GUI'yi yansıtacak şekilde • File isim değişiklikleri • Metin düzenlemeleri |

| 2017.05.08 | 17.0.0 | Belgenin ilk sürümü |

Belgeler / Kaynaklar

|

intel AN 805 Arria 10 SoC Geliştirme Kartındaki Tasarımın Hiyerarşik Kısmi Yeniden Yapılandırılması [pdf] Kullanıcı Kılavuzu AN 805 Arria 10 SoC Geliştirme Kartında Bir Tasarımın Hiyerarşik Kısmi Yeniden Yapılandırılması, AN 805, Arria 10 SoC Geliştirme Kartında Bir Tasarımın Hiyerarşik Kısmi Yeniden Yapılandırılması, Arria 10 SoC Geliştirme Kartında Bir Tasarımın Yeniden Yapılandırılması, Arria 10 SoC Geliştirme Kartı, 10 SoC Geliştirme Kurulu |