Intel AN 805 Rekonfigurasyon pasyèl hierarchique nan yon konsepsyon sou Komisyon Konsèy Devlopman SoC Arria 10

Tutorial Rekonfigurasyon Pasyèl yerarchize pou Komisyon Konsèy Devlopman SoC Intel® Arria® 10

Nòt aplikasyon sa a demontre transfòmasyon yon konsepsyon senp nan yon konsepsyon yerarchikman pasyèlman rekonfigurab, epi mete ann aplikasyon konsepsyon an sou tablo devlopman Intel® Arria® 10 SoC. Rekonfigurasyon pasyèl hierarchique (HPR) se yon kalite espesyal reconfiguration pasyèl (PR), kote ou genyen yon rejyon PR nan yon lòt rejyon PR. Ou ka kreye plizyè pèsonaj pou tou de patisyon timoun yo ak paran yo. Ou fè nich patisyon timoun yo nan patisyon paran yo. Rekonfigirasyon yon patisyon timoun pa gen enpak sou operasyon nan paran oswa rejyon estatik yo. Rekonfigirasyon yon patisyon paran pa gen enpak sou operasyon an nan rejyon estatik la, men ranplase patisyon timoun yo nan rejyon paran an ak pèsonaj patisyon timoun default. Metodoloji sa a efikas nan sistèm kote plizyè fonksyon pataje menm resous aparèy FPGA yo.

Rekonfigurasyon pasyèl bay avansman sa yo nan yon konsepsyon plat:

- Pèmèt rekonfigirasyon konsepsyon an tan kouri

- Ogmante évolutivité nan konsepsyon an

- Diminye D' sistèm

- Sipòte fonksyon tan-multiplexing dinamik nan konsepsyon an

- Diminye pri ak konsomasyon pouvwa atravè itilizasyon efikas espas tablo

- Nòt:

- Aplikasyon konsepsyon referans sa a mande pou yon konesans debaz ak koule aplikasyon Intel Quartus® Prime FPGA ak konesans sou pwojè prensipal Intel Quartus Prime. files.

Enfòmasyon ki gen rapò

- Intel Arria 10 SoC Development Kit Gid itilizatè

- Konsèp Rekonfigurasyon Pasyèl

- Pasyèl Rekonfigurasyon Design Flow

- Rekòmandasyon Konsepsyon Rekonfigurasyon Pasyèl

- Konsiderasyon Konsepsyon Rekonfigurasyon Pasyèl

Kondisyon konsepsyon referans

Konsepsyon referans sa a mande sa ki annapre yo:

- Intel Quartus Prime Pro Edition lojisyèl vèsyon 17.1 pou aplikasyon konsepsyon an.

- Intel Arria 10 SoC devlopman twous pou aplikasyon FPGA.

Intel Corporation. Tout dwa rezève. Intel, logo Intel ak lòt mak Intel yo se mak komèsyal Intel Corporation oswa filiales li yo. Intel garanti pèfòmans pwodwi FPGA ak semi-conducteurs li yo selon espesifikasyon aktyèl yo an akò ak garanti estanda Intel a, men li rezève dwa pou fè chanjman nan nenpòt pwodwi ak sèvis nenpòt ki lè san avètisman. Intel pa asime okenn responsablite oswa responsablite ki soti nan aplikasyon an oswa itilizasyon nenpòt enfòmasyon, pwodwi oswa sèvis ki dekri la a eksepte si Intel te dakò ekspreseman alekri. Yo konseye kliyan Intel yo pou yo jwenn dènye vèsyon espesifikasyon aparèy yo anvan yo konte sou nenpòt enfòmasyon ki pibliye epi anvan yo pase lòd pou pwodwi oswa sèvis yo.

- Lòt non ak mak yo ka reklame kòm pwopriyete lòt moun.

Konsepsyon referans souview

- Konsepsyon referans sa a konsiste de yon kontwa 32-bit. Nan nivo tablo a, konsepsyon an konekte revèy la nan yon sous 50MHz epi konekte pwodiksyon an nan kat LED sou FPGA la. Chwazi pwodiksyon an soti nan Bits yo vann san preskripsyon nan yon sekans espesifik lakòz LED yo bat je nan yon frekans espesifik.

Figi 1. Konsepsyon referans plat san patisyon PR

Konsepsyon referans Files

Tutorial pou rekonfigirasyon pasyèl la disponib nan kote sa a: https://github.com/intel/fpga-partial-reconfig

Pou telechaje leson patikilye a:

- Klike sou klonaj oswa telechaje.

- Klike sou Download ZIP. Dekonprime FPGA-partial-config-master.zip la file.

- Navige nan tutoryèl/a10_soc_devkit_blinking_led_hpr sou-dosyè pou jwenn aksè nan konsepsyon referans la.

Katab plat la konsiste de bagay sa yo files:

Tablo 1. Konsepsyon referans Files

| File Non | Deskripsyon |

| tèt. SV | Nivo nan tèt file gen aplikasyon an plat nan konsepsyon an. Modil sa a enstansye sou-patisyon blinking_led ak modil top_counter la. |

| top_counter.sv | Top-nivo kontwa 32-bit ki kontwole dirije[1] dirèkteman. Pwodiksyon ki anrejistre nan kontwa an kontwole dirije [0], epi tou li pouvwa dirije [2] ak dirije [3] atravè modil la blinking_led. |

| blinking_led.sdc | Defini kontrent tan pou pwojè a. |

| kontinye… | |

| File Non | Deskripsyon |

| blinking_led.SV | Nan leson patikilye sa a, ou konvèti modil sa a nan yon patisyon PR paran. Modil la resevwa pwodiksyon an anrejistre nan modil la top_counter, ki kontwole LED[2] ak LED[3]. |

| blinking_led.qpf | Pwojè Intel Quartus Prime file ki gen lis tout revizyon yo nan pwojè a. |

| blinking_led.qsf | Anviwònman Intel Quartus Prime file ki gen devwa yo ak paramèt pou pwojè a. |

Nòt: Katab hpr a gen ansanm nèt sou tout pwen files ou kreye lè l sèvi avèk nòt aplikasyon sa a. Referans sa yo files nan nenpòt ki pwen pandan pwosedi a.

Figi 2. Konsepsyon referans Files

Referans Design Pajman

Etap sa yo dekri aplikasyon an nan rekonfigirasyon pasyèl nan yon konsepsyon plat. Leson patikilye a sèvi ak lojisyèl Intel Quartus Prime Pro Edition pou tablo devlopman Intel Arria 10 SoC:

- Etap 1: Kòmanse nan paj 6

- Etap 2: Kreye yon Sou-modil Nivo Timoun nan paj 6

- Etap 3: Kreye patisyon konsepsyon nan paj 7

- Etap 4: Afektasyon Plasman ak Rejyon Wout pou Patisyon PR nan paj 9

- Etap 5: Ajoute Intel Arria 10 Patial Reconfiguration Controller IP Core nan paj 10

- Etap 6: Defini Personas nan paj 13

- Etap 7: Kreye revizyon nan paj 15

- Etap 8: Jenere Script Flow Rekonfigurasyon Pasyèl Hierachik la nan paj 20

- Etap 9: Egzekite Script Flow Rekonfigurasyon Pasyèl Hierachik la nan paj 21

- Etap 10: Pwogramasyon Komisyon Konsèy la nan paj 22

Etap 1: Kòmanse

Pou kopye konsepsyon referans la files nan anviwònman k ap travay ou ak konpile konsepsyon plat blinking_led la:

- Kreye yon anyè nan anviwònman k ap travay ou a, a10_soc_devkit_blinking_led_hpr.

- Kopi leson patikilye yo telechaje/a10_soc_devkit_blinking_led_hpr/flat sou-dosyè nan anyè a, a10_soc_devkit_blinking_led_hpr.

- Nan lojisyèl Intel Quartus Prime Pro Edition, klike sou File ➤ Louvri Pwojè epi chwazi blinking_led.qpf.

- Pou konpile konsepsyon plat la, klike sou Processing ➤ Kòmanse Konpilasyon.

Etap 2: Kreye yon Sou-modil Nivo Timoun

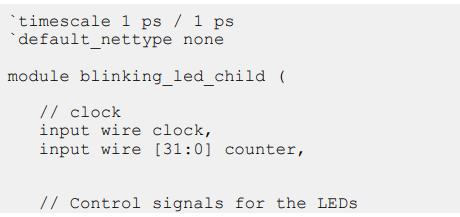

Pou konvèti konsepsyon plat sa a nan yon konsepsyon PR yerarchize, ou dwe kreye yon sou-modil timoun (blinking_led_child. SV) ki enbrike nan sou-modil paran an (blinking_led.sv).

- Kreye yon nouvo konsepsyon file, blinking_led_child.sv, epi ajoute liy kòd sa yo nan sa a file: echèl 1 ps / 1 ps `default_nettype okenn modil blinking_led_child ( // revèy antre fil revèy, fil antre [31:0] kontwa, // siyal kontwòl pou dirije yo

- Modifye blinking_led.sv la file konekte led_two_on nan ti jan 23 nan kontwa a soti nan rejyon an estatik, ak enstansye modil la blinking_led_child. Apre modifikasyon, blinking_led.sv ou file dwe parèt jan sa a:

- Sou modifye tout konsepsyon an files, rekonpile pwojè a lè w klike sou Processing ➤ Kòmanse Konpilasyon

Etap 3: Kreye patisyon konsepsyon

Ou dwe kreye patisyon konsepsyon pou chak rejyon PR ke ou vle pasyèlman rekonfigire. Ou ka kreye nenpòt ki kantite patisyon endepandan oswa rejyon PR nan konsepsyon ou. Tutorial sa a kreye de patisyon konsepsyon pou ka u_blinking_led_child ak u_blinking_led.

Pou kreye patisyon konsepsyon pou rekonfigirasyon yerarchik pasyèl:

- Dwa-klike sou egzanp u_blinking_led_child nan Project Navigator epi klike sou Design Partition ➤ Mete kòm Design Partition. Yon icon patisyon konsepsyon parèt akote chak egzanp ki mete kòm yon patisyon.

Figi 3. Kreye patisyon konsepsyon soti nan Project Navigator

- Pou defini Kalite patisyon an, klike sou egzanp u_blinking_led_child la nan tab Hierarchy la, klike sou Design Partition ➤ Reconfigurable. Ou ka defini Kalite patisyon an sèlman apre ou fin mete egzanp lan kòm yon patisyon. Patisyon konsepsyon an parèt sou Devwa yo View tab nan Fenèt la Design Partitions.

Figi 4. Fenèt Partitions Design

- Edit non patisyon an nan Fenèt Partitions Design la lè w klike sou non an doub. Pou konsepsyon referans sa a, chanje non patisyon an pr_partition.

Nòt: Lè ou kreye yon patisyon, lojisyèl Intel Quartus Prime otomatikman jenere yon non patisyon, ki baze sou non egzanp lan ak chemen yerachi. Non patisyon default sa a ka varye selon chak egzanp. - Repete etap 1 ak 2 pou bay patisyon konsepsyon rekonfigurabl nan egzanp u_blinking_led la. Chanje non patisyon sa a an pr_parent_partition.

Verifye ke blinking_led.qsf gen devwa sa yo, ki koresponn ak patisyon konsepsyon rekonfigurab ou yo:

Kreye Partitions Design pou Rekonfigurasyon Pasyèl

Etap 4: Afektasyon Plasman ak Rejyon Wout pou Patisyon PR

Lè ou kreye revizyon baz la, koule konsepsyon PR a sèvi ak alokasyon rejyon patisyon PR ou a pou mete nwayo pèsonaj ki koresponn lan nan rejyon rezève a. Pou lokalize epi bay rejyon PR a nan plan etaj aparèy la pou revizyon baz ou a:

- Klike sou egzanp u_blinking_led_child a nan Project Navigator epi klike sou Rejyon Logic Lock ➤ Kreye Nouvo Rejyon Logic Lock. Rejyon an parèt sou Fenèt Rejyon Lojik Lock.

- Rejyon plasman ou a dwe mete lojik blinking_led_child la. Chwazi rejyon plasman an lè w lokalize ne nan Chip Planner. Dwa-klike sou non rejyon u_blinking_led_child nan Project Navigator epi klike sou Locate Node ➤ Locate in Chip Planner.

Figi 5. Chip Planner Node Location pou blinking_led

- Nan fenèt Rejyon lojik Lock yo, presize kowòdone rejyon plasman yo nan kolòn Orijin. Orijin nan koresponn ak kwen ki pi ba-gòch nan rejyon an. Pou egzanpample, pou mete yon rejyon plasman ak (X1 Y1) kowòdone kòm (69 10), presize Orijin nan kòm X69_Y10. Lojisyèl Intel Quartus Prime otomatikman kalkile kowòdone (X2 Y2) (anwo adwat) pou rejyon plasman an, dapre wotè ak lajè ou presize.

Nòt: Tutorial sa a sèvi ak kowòdone (X1 Y1) - (69 10), ak yon wotè ak lajè 20 pou rejyon plasman an. Defini nenpòt valè pou rejyon plasman an, depi rejyon an kouvri lojik blinking_led_child la. - Pèmèt opsyon rezève ak debaz sèlman.

- Double-klike sou opsyon nan Rejyon Route. Bwat dyalòg Anviwònman Rejyon lojik Lock Routing la parèt.

- Chwazi Fiks ak ekspansyon pou kalite Routage. Chwazi opsyon sa a otomatikman bay yon longè ekspansyon 1.

Nòt: Rejyon routage a dwe pi gwo pase rejyon plasman an, pou bay plis fleksibilite pou Fitter la lè motè a travèse diferan pèsonaj. - Repete etap 1 -6 pou egzanp u_blinking_led la. Plasman nan nivo paran Repete etap 1 -6 pou egzanp u_blinking_led la. Rejyon plasman nan nivo paran an dwe konplètman fèmen rejyon plasman ak wout ki koresponn nan nivo timoun pandan y ap pèmèt ase espas pou plasman lojik nivo paran an. Didacticiel sa a itilize kowòdone (X1 Y1) - (66 7), yon wotè 47, ak yon lajè 26 pou rejyon plasman egzanp u_blinking_led la.

Figi 6.Lojik Lock Rejyon Fenèt

Verifye ke blinking_led.qsf genyen devwa sa yo, ki koresponn ak planifikasyon ou a:

- Plan Plan Rekonfigurasyon Pasyèl la

- Enplimante yon pati nan rekonfigurasyon

Etap 5: Ajoute Intel Arria 10 Patial Reconfiguration Controller IP Core

- Sèvi ak Intel Arria 10 Patial Reconfiguration Controller IP nwayo a pou rekonfigire patisyon PR a. Nwayo IP sa a itilize JTAG pou rekonfigire patisyon PR a. Pou ajoute Intel Arria 10 Patial Reconfiguration Controller IP core nan pwojè Intel Quartus Prime ou a:

- Tape Rekonfigurasyon Pasyèl nan katalòg IP la.

- Pou lanse fenèt IP Parameter Editor Pro, chwazi Intel Arria 10 Patial Reconfiguration Controller IP core nan bibliyotèk IP la, epi klike sou Add.

- Nan bwat dyalòg New IP Variant, tape pr_ip kòm file non epi klike sou Kreye. Sèvi ak paramètrizasyon default pou pr_ip. Asire w ke Pèmèt JTAG mòd debug ak Pèmèt opsyon koòdone friz yo vire sou, epi Pèmèt opsyon koòdone esklav Avalon-MM yo etenn.

Figi 7. Intel Arria 10 Patial Reconfiguration Controller IP Core Parameters

- Klike sou Fini, epi sòti editè paramèt la san yo pa jenere sistèm lan. Lojisyèl Intel Quartus Prime kreye varyasyon IP pr_ip.ip file, epi ajoute a file nan pwojè blinking_led la.

Nòt:

- Si w ap kopye pr_ip.ip la file soti nan katab hpr la, manyèlman modifye blinking_led.qsf la file enkli liy sa a: set_global_assignment -name IP_FILE pr_ip.ip

- Mete IP_ laFILE devwa apre SDC_ laFILE devwa (jtag.sdc ak blinking_led.sdc) nan blinking_led.qsf ou file. Kòmandman sa a asire kontrent apwopriye nan nwayo IP Rekonfigurasyon Pasyèl la.

Nòt: Pou detekte revèy yo, SDC a file pou PR IP a dwe swiv nenpòt SDC ki kreye revèy yo ke nwayo IP a itilize. Ou fasilite lòd sa a lè w asire .ip file pou nwayo a IP PR vini apre nenpòt ki .ip files oswa SDC fileyo itilize pou kreye revèy sa yo nan QSF la file pou revizyon pwojè Intel Quartus Prime ou a. Pou plis enfòmasyon, al gade nan seksyon Kontrent Distribisyon nan Gid Itilizatè IP Nwayo Rekonfigirasyon Pasyèl la.

Enfòmasyon ki gen rapò

- Rekonfigurasyon pasyèl IP Solutions Gid itilizatè

- Pou enfòmasyon sou debaz IP Kontwolè Rejyon Rekonfigurasyon Pasyèl la.

- Rekonfigurasyon pasyèl IP Nwayo Itilizatè Gid

- Pou enfòmasyon sou kontrent tan yo.

Mete ajou konsepsyon an tèt nivo

Pou mete ajou tèt la.SV file ak egzanp PR_IP la:

- Pou ajoute egzanp PR_IP a nan konsepsyon nivo siperyè a, dekomantè blòk kòd sa a nan tèt la.SV file:

- Pou fòse pò pwodiksyon yo nan lojik 1 pandan rekonfigirasyon, sèvi ak pwodiksyon siyal kontwòl friz ki soti nan PR_IP. Sepandan, pou obsève LED la kontinye kliyote nan patisyon PR paran an pandan y ap PR pwograme patisyon timoun nan, siyal kontwòl friz la pa etenn led_two_on la. Asire w ke pr_led_two_on a dirèkteman

- Pou bay yon egzanp pèsonaj paran an default (blinking_led), mete ajou top.SV la file ak blòk kòd sa a:

Figi 8. Rekonfigurasyon Pasyèl Entegrasyon Nwayo IP

Etap 6: Defini Personas

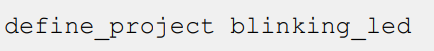

Konsepsyon referans sa a defini senk pèsonaj separe pou patisyon PR paran ak timoun. Pou defini epi mete pèsonaj yo nan pwojè ou a:

- Kreye kat SystemVerilog files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv, ak blinking_led_slow.sv nan anyè k ap travay ou pou senk pèsonaj yo.

Nòt: Si ou kreye SystemVerilog la files soti nan Intel Quartus Prime Text Editè a, enfim Add la file nan opsyon pwojè aktyèl la, lè sove a files.

Tablo 2. Referans Design Personas

| File Non | Deskripsyon | Kòd |

| blinking_led_child.sv | Pèsonaj default pou konsepsyon nivo timoun |

`echèl 1 ps / 1 ps `default_nettype okenn modil blinking_led_child ( // revèy revèy fil antre, fil antre [31:0] kontwa,

// Siyal kontwòl pou fil pwodiksyon LED led_three_on

); localparam COUNTER_TAP = 23; reg led_three_on_r;

plase led_three_on = led_three_on_r; always_ff @(posedge revèy) kòmanse led_three_on_r <= counter[COUNTER_TAP]; fini

modil final |

| kontinye… | ||

| File Non | Deskripsyon | Kòd |

| blinking_led_child_slow.sv | La

LED_THREE bat pi dousman |

`echèl 1 ps / 1 ps `tip_net_default okenn

modil blinking_led_child_slow (

// revèy revèy fil antre, fil antre [31:0] kontwa,

// Siyal kontwòl pou fil pwodiksyon LED led_three_on );

localparam COUNTER_TAP = 27; reg led_three_on_r;

plase led_three_on = led_three_on_r; always_ff @(posedge revèy) kòmanse led_three_on_r <= counter[COUNTER_TAP]; fini

modil final |

| blinking_led_child_empty.sv | La

LED_THREE rete ON |

`echèl 1 ps / 1 ps `tip_net_default okenn

modil blinking_led_child_empty (

// revèy revèy fil antre, fil antre [31:0] kontwa,

// Siyal kontwòl pou fil pwodiksyon LED led_three_on

);

// LED aktif ba plase led_three_on = 1'b0;

modil final |

| blinking_led_slow.sv | LED_TWO a

bat pi dousman. |

`echèl 1 ps / 1 ps `default_nettype okenn modil blinking_led_slow( // revèy revèy fil antre, fil antre [31:0] kontwa,

// Siyal kontwòl pou fil pwodiksyon LED led_two_on, fil pwodiksyon led_three_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; plase led_two_on = led_two_on_r;

// Kontwa a: always_ff @(posedge clock) begin led_two_on_r <= counter[COUNTER_TAP]; fini

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .counter (kontan), .clock (revèy) |

| File Non | Deskripsyon | Kòd |

| );ndmodule |

Etap 3: Kreye patisyon konsepsyon nan paj 7

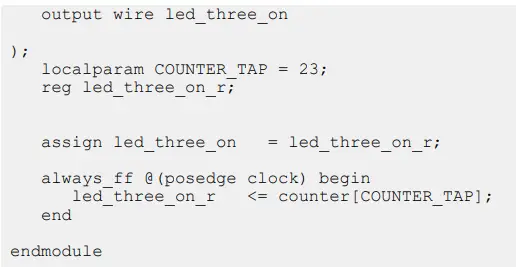

Etap 7: Kreye revizyon

Flux konsepsyon PR a itilize karakteristik revizyon pwojè a nan lojisyèl Intel Quartus Prime. Inisyal konsepsyon ou a se revizyon baz la, kote ou defini fwontyè rejyon estatik ak rejyon reconfigurable sou FPGA la. Soti nan revizyon debaz la, ou kreye revizyon miltip. Revizyon sa yo genyen diferan aplikasyon pou rejyon PR yo. Sepandan, tout revizyon egzekisyon PR yo itilize menm rezilta plasman nan nivo siperyè ak menm rezilta revizyon debaz la. Pou konpile yon konsepsyon PR, ou dwe kreye yon revizyon aplikasyon PR ak revizyon sentèz pou chak pèsonaj. Nan konsepsyon referans sa a, anplis de revizyon baz la (blinking_led), twa pèsonaj nivo timoun yo ak de pèsonaj nivo paran yo genyen senk revizyon sentèz separe ak senk revizyon aplikasyon separe:

Tablo 3. Revizyon pou moun ki gen de paran ak moun ki gen twa timoun yo

| Revizyon sentèz | Revizyon Aplikasyon |

| blinking_led_parent, blinking_led_default | clignotant_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_vid | blinking_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | clignotant_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_vid | clignotant_led_pr_emma |

Kreye revizyon aplikasyon

Pou kreye revizyon aplikasyon PR yo:

- Pou ouvri bwat dyalòg Revizyon an, klike sou Pwojè ➤ Revizyon.

- Pou kreye yon nouvo revizyon, double-klike sou < >.

- Espesifye non Revizyon an kòm blinking_led_pr_alpha epi chwazi blinking_led pou Baze sou Revizyon.

- Enfim opsyon Mete kòm revizyon aktyèl la epi klike sou OK.

- Menm jan an tou, kreye revizyon blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta, ak blinking_led_pr_emma, ki baze sou revizyon blinking_led.

Nòt: Pa mete revizyon ki anwo yo kòm revizyon aktyèl la.

Figi 9. Kreye revizyon

Kreye Revizyon Sentèz-Sèlman

Pou kreye revizyon sentèz sèlman pou pèsonaj yo, ou dwe bay antite ki pi wo a ak SystemVerilog ki koresponn lan. file pou chak pèsonaj yo:

- Nan lojisyèl Intel Quartus Prime, klike sou Pwojè ➤ Revizyon.

- Kreye revizyon blinking_led_default ki baze sou revizyon blinking_led. Pa mete revizyon sa a kòm revizyon aktyèl la.

- Modifye blinking_led_default.qsf la file pou mete devwa sa yo:

set_global_assignment -name TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -name SYSTEMVERILOG_FILE - Menm jan an tou, kreye revizyon blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent, ak blinking_led_parent_slow ki baze sou revizyon blinking_led. Pa mete revizyon sa yo kòm revizyon aktyèl yo.

- Mete ajou blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, ak blinking_led_parent_slow.qsf files ak korespondan yo

TOP_LEVEL_ENTITY ak SYSTEMVERILOG_FILE devwa:

- Pou evite erè sentèz, asire ke revizyon an sentèz files pou patisyon timoun yo pa genyen okenn patisyon konsepsyon, devwa pin, oswa Lock lojik

devwa rejyon an. Epitou, revizyon an sentèz files pou patisyon paran yo dwe genyen sèlman devwa patisyon konsepsyon pou patisyon pitit korespondan yo. Retire devwa sa yo, si genyen, nan blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, ak blinking_led_parent_slow.pdf files

- Mete devwa sa yo nan blinking_led_parent.qsf ak blinking_led_parent_slow.qsf files:

- Verifye ke blinking_led.qpf la file gen revizyon sa yo, nan okenn lòd patikilye:

- Nòt: Si w ap kopye revizyon an files soti nan katab hpr, manyèlman mete ajou blinking_led.qpf la file ak liy ki anwo yo nan kòd.

Espesifye Kalite Revizyon

Ou dwe bay kalite revizyon pou chak revizyon ou yo. Gen twa kalite revizyon:

- Rekonfigurasyon pasyèl - Baz

- Rekonfigurasyon pasyèl - Sentèz pèsona

- Rekonfigurasyon Pasyèl - Aplikasyon Persona

- Tablo ki anba la a bay lis devwa kalite revizyon pou chak revizyon yo:

Tablo 4. Kalite revizyon

| Non Revizyon | Kalite revizyon |

| blinking_led.qsf | Rekonfigurasyon pasyèl - Baz |

| blinking_led_default.qsf | Rekonfigurasyon pasyèl - Sentèz pèsona |

| blinking_led_child_empty.qsf | Rekonfigurasyon pasyèl - Sentèz pèsona |

| blinking_led_child_slow.qsf | Rekonfigurasyon pasyèl - Sentèz pèsona |

| blinking_led_parent.qsf | Rekonfigurasyon pasyèl - Sentèz pèsona |

| blinking_led_parent_slow.qsf | Rekonfigurasyon pasyèl - Sentèz pèsona |

| blinking_led_pr_alpha.qsf | Rekonfigurasyon Pasyèl - Aplikasyon Persona |

| blinking_led_pr_bravo.qsf | Rekonfigurasyon Pasyèl - Aplikasyon Persona |

| blinking_led_pr_charlie.qsf | Rekonfigurasyon Pasyèl - Aplikasyon Persona |

| blinking_led_pr_delta.qsf | Rekonfigurasyon Pasyèl - Aplikasyon Persona |

| blinking_led_pr_emma.qsf | Rekonfigurasyon Pasyèl - Aplikasyon Persona |

- Klike sou Pwojè ➤ Revizyon. Bwat dyalòg Revizyon an parèt.

- Chwazi blinking_led nan kolòn Non Revizyon an, epi klike sou Mete Kouran.

- Klike sou Aplike. Blinking_led revizyon an ouvri.

- Pou mete kalite revizyon pou blinking_led, klike sou Devwa ➤ Anviwònman ➤ Jeneral.

- Chwazi Kalite Revizyon an kòm Rekonfigirasyon Pasyèl - Baz.

- Menm jan an tou, mete kalite revizyon yo pou dis lòt revizyon yo, jan lis nan tablo ki anwo a.

- Nòt: Ou dwe mete chak revizyon kòm revizyon aktyèl la anvan ou bay kalite revizyon an. Verifye ke chak .qsf file gen devwa sa a:

- Nòt: Ajoute nenpòt paramèt espesifik Fitter ke ou vle itilize nan konpile aplikasyon PR a nan revizyon aplikasyon pèsonaj yo. Anviwònman Fitter-espesifik yo afekte anfòm pèsonaj la, men yo pa afekte rejyon estatik enpòte a. Ou kapab tou ajoute nenpòt anviwònman sentèz espesifik nan revizyon sentèz pèsonaj endividyèl yo.

Kreye Revizyon pou Personas

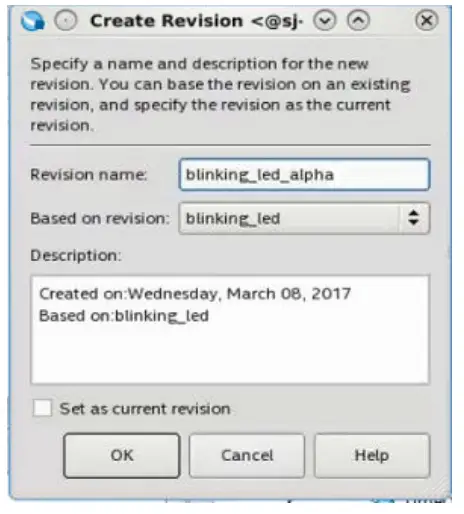

Etap 8: Jenere Script Flow Rekonfigurasyon Pasyèl Hierachik la

Pou jenere script yerarchize yon pati nan rekonfigirasyon koule:

- Soti nan koki kòmand Intel Quartus Prime, kreye yon modèl koule lè w ap kouri lòd sa a:

- Intel Quartus Prime jenere a10_hier_partial_reconfig/flow.tcl file.

- Chanje non pwodwi a10_hier_partial_reconfig/setup.tcl.exampli nan a10_hier_partial_reconfig/setup.tcl, epi modifye script la pou presize detay pwojè rekonfigirasyon pasyèl ou a:

a. Pou defini non pwojè a, mete ajou liy sa a: b. Pou defini revizyon baz la, mete ajou liy sa a:

b. Pou defini revizyon baz la, mete ajou liy sa a:

- Pou defini chak revizyon an aplikasyon pou rekonfigirasyon pasyèl yo, ansanm ak non patisyon PR yo ak revizyon sous ki aplike revizyon yo, mete ajou liy sa yo:

Nòt: Tout pwojè revizyon yo dwe nan menm anyè ak blinking_led.qpf. Sinon, mete ajou script koule a kòmsadwa.

Etap 9: Kouri Script Flow Rekonfigurasyon Pasyèl Hierachik la

Pou kouri script yerarchize a yon pati nan rekonfigirasyon koule:

- Klike sou Zouti ➤ Tcl Scripts. Bwat dyalòg Tcl Scripts la parèt.

- Klike sou Add to Project, browse epi chwazi a10_hier_partial_reconfig/flow.tcl.

- Chwazi a10_hier_partial_reconfig/flow.tcl nan fenèt Bibliyotèk la, epi klike sou Kouri.

Script sa a kouri sentèz la pou twa pèsonaj yo. Intel Quartus Prime jenere yon objè SRAM File (.sof), yon Objè SRAM Pasyèl-Maske File (.pmsf), ak yon Binè kri File (.rbf) pou chak moun yo.

Remak: Pou kouri script la soti nan koki kòmand Intel Quartus Prime, tape lòd sa a:

- Konpile konsepsyon Rekonfigurasyon Pasyèl la

- Sèvi ak Script Flow Rekonfigurasyon Pasyèl la

- Konfigirasyon Script Flow Rekonfigurasyon Pasyèl la

- Jenere pwogramasyon Files

Etap 10: Pwogramasyon Komisyon Konsèy la

Anvan ou kòmanse:

- Konekte ekipman pou pouvwa a nan tablo devlopman Intel Arria 10 SoC.

- Konekte kab USB Blaster ant pò USB PC ou ak pò USB Blaster sou tablo devlopman an.

Pou kouri konsepsyon an sou tablo devlopman Intel Arria 10 SoC:

- Louvri lojisyèl Intel Quartus Prime a epi klike sou Zouti ➤ Pwogramè.

- Nan pwogramè a, klike sou Enstalasyon Materyèl epi chwazi USB-Blaster.

- Klike sou Auto Detect epi chwazi aparèy la, 10AS066N3.

- Klike sou OK. Lojisyèl Intel Quartus Prime la detekte ak mete ajou pwogramè a ak twa chips FPGA yo sou tablo a.

- Chwazi aparèy 10AS066N3 a, klike sou Chanje File epi chaje blinking_led_pr_alpha.sof la file.

- Pèmèt Pwogram/Konfigure pou blinking_led_pr_alpha.sof file.

- Klike sou Kòmanse epi tann ba pwogrè a rive nan 100%.

- Obsève LED yo sou tablo a k ap flache nan menm frekans ak konsepsyon plat orijinal la.

- Pou pwograme rejyon PR timoun nan sèlman, klike sou blinking_led_pr_alpha.sof file nan Pwogramè a epi klike sou Add PR Programming File.

- Chwazi blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf la file.

- Enfim Pwogram/Konfigure pou blinking_led_pr_alpha.sof file.

- Pèmèt pwogram/konfigirasyon pou blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file epi klike sou Kòmanse. Sou tablo a, obsève LED[0] ak LED[1] kontinye ap bat. Lè ba pwogrè a rive nan 100%, LED[2] ap bat nan menm vitès la, ak LED[3] vin pi dousman.

- Pou pwograme rejyon PR paran ak timoun, klike sou .rbf la file nan Pwogramasyon an epi klike sou Chanje pwogram PR File.

- Chwazi blinking_led_pr_delta.pr_parent_partition.rbf la file.

- Klike sou Kòmanse. Sou tablo a, obsève ke LED[0] ak LED[1] kontinye ap bat. Lè ba pwogrè a rive nan 100%, tou de ki ap dirije [2] ak ki ap dirije [3] vin pi dousman.

- Repete etap ki anwo yo pou re-pwograme yon fason dinamik jis rejyon PR timoun lan, oswa toude rejyon PR paran ak timoun an menm tan.

Figi 10. Pwogramasyon Intel Arria 10 SoC Development Board

Modifye yon pèsonaj ki egziste deja

- Ou ka chanje yon pèsonaj ki egziste deja, menm apre yo fin konpile konplètman revizyon baz la.

- Pou egzanpample, pou lakòz pèsonaj la blinking_led_child_slow bat menm pi dousman:

- Nan blinking_led_child_slow.sv la file, modifye paramèt COUNTER_TAP soti nan 27 a 28.

- Pou re-sentèz ak re-aplike pèsonaj sa a, ou dwe rekonpile tout revizyon-sèlman sentèz ak revizyon aplikasyon ki afekte nan chanjman an. Modifye script setup.tcl pou mete liy sa yo:

Nòt: Lè w ap defini pr_parent_parition pou revizyon blinking_led_pr_delta, ou enpòte snapshot final la nan pèsonaj sa a pou aplikasyon an. Kòm yon rezilta, aplikasyon lojik patisyon paran an rete menm jan an, pandan y ap modifye ak aplike patisyon timoun ki koresponn lan.

Nòt: Lè w ap defini pr_parent_parition pou revizyon blinking_led_pr_delta, ou enpòte snapshot final la nan pèsonaj sa a pou aplikasyon an. Kòm yon rezilta, aplikasyon lojik patisyon paran an rete menm jan an, pandan y ap modifye ak aplike patisyon timoun ki koresponn lan. Kòmandman sa a re-sintetize revizyon sentèz blinking_led_child_slow la, epi li fè konpile aplikasyon PR lè l sèvi avèk blinking_led_pr_bravo.

Kòmandman sa a re-sintetize revizyon sentèz blinking_led_child_slow la, epi li fè konpile aplikasyon PR lè l sèvi avèk blinking_led_pr_bravo. - Pou fè konpilasyon revizyon sentèz yo sèlman, kouri kòmandman sa a: Kòmandman sa a pa rekonpile revizyon debaz la.

- Pou fè konpilasyon revizyon aplikasyon yo, kouri lòd sa a:

- Kòmandman sa a pa rekonpile revizyon baz la.

- Swiv etap sa yo nan Etap 10: Pwogramasyon Komisyon Konsèy la nan paj 22 pou pwograme RBF ki lakòz. file nan FPGA la.

Nòt: Pou evite kouri tout koule a pou chak revizyon, defini revizyon sentèz sèlman ak revizyon aplikasyon yo nan script setup.tcl, epi kouri script la.

Ajoute yon nouvo pèsonaj nan konsepsyon an

Apre konplètman konpile revizyon baz ou yo, ou ka toujou ajoute nouvo pèsonaj ak endividyèlman konpile pèsonaj sa yo.

Pou egzanpample, pou defini yon nouvo pèsonaj timoun pou blinking_led_parent_slow, ki etenn led_three:

- Kopi blinking_led_child_empty.sv nan blinking_led_chdild_off.sv.

- Nan blinking_led_child_off.sv la file, modifye plasman an, bay led_three_on = 1'b0; bay led_three_on = 1'b1;. Asire w ou chanje non modil la soti nan blinking_led_child_empty a blinking_led_child_off.

- Kreye yon nouvo revizyon sentèz, blinking_led_child_off, lè w suiv etap sa yo nan Kreye revizyon sentèz sèlman nan paj 16.

Nòt: Revizyon blinking_led_child_off la dwe itilize blinking_led_child_off.sv. file. - Kreye yon nouvo revizyon aplikasyon, blinking_led_pr_foxtrot, nan swiv etap sa yo nan Kreye revizyon aplikasyon nan paj 15.

- Mete ajou a10_hier_partial_reconfig/setup.tcl file defini nouvo aplikasyon PR:

- Konpile jis nouvo sentèz ak revizyon aplikasyon sa a lè w ap kouri lòd sa a:

Pou jwenn enfòmasyon konplè sou rekonfigirasyon pasyèl yerarchize pou aparèy Intel Arria 10, al gade nan Kreye yon konsepsyon rekonfigurasyon pasyèl nan Volim 1 nan Manyèl Intel Quartus Prime Pro Edition.

Enfòmasyon ki gen rapò

- Kreye yon konsepsyon Rekonfigurasyon Pasyèl

- Rekonfigurasyon pasyèl fòmasyon sou entènèt

Istwa revizyon dokiman

Tablo 5. Istwa Revizyon Dokiman

| Vèsyon dokiman an | Software Version | Chanjman |

| 2017.11.06 | 17.1.0 | • Mete ajou a Kondisyon konsepsyon referans seksyon ak vèsyon lojisyèl an

• Mete ajou a Konsepsyon referans plat san patisyon PR figi ak chanjman blòk konsepsyon • Mete ajou a Konsepsyon referans Files tablo ak enfòmasyon sou la Top_counter.sv modil • Mete ajou a Rekonfigurasyon Pasyèl Entegrasyon Nwayo IP figi ak chanjman blòk konsepsyon • Mete ajou figi yo - Design Partitions Fenèt epi Lojik Lock Rejyon Fenèt pou reflete nouvo entèfas • File chanjman non • Modifikasyon tèks |

| 2017.05.08 | 17.0.0 | Premye piblikasyon dokiman an |

Dokiman / Resous

|

Intel AN 805 Rekonfigurasyon pasyèl hierarchique nan yon konsepsyon sou Komisyon Konsèy Devlopman SoC Arria 10 [pdfGid Itilizatè AN 805 Rekonfigirasyon Pasyèl Yerachik yon Konsepsyon sou Kat Devlopman Arria 10 SoC, AN 805, Rekonfigirasyon Pasyèl Yerachik yon Konsepsyon sou Kat Devlopman Arria 10 SoC, Rekonfigirasyon yon Konsepsyon sou Kat Devlopman Arria 10 SoC, Kat Devlopman Arria 10 SoC, Kat Devlopman 10 SoC |