intel AN 805 Hierarchical Ib Feem Reconfiguration ntawm Kev Tsim Kho ntawm Arria 10 SoC Development Board

Hierarchical Partial Reconfiguration Tutorial rau Intel® Arria® 10 SoC Development Board

Daim ntawv thov no qhia txog kev hloov pauv tus qauv tsim yooj yim rau hauv ib feem ntawm cov qauv tsim kho, thiab siv tus qauv tsim ntawm Intel® Arria® 10 SoC kev txhim kho pawg thawj coj. Hierarchical partial reconfiguration (HPR) yog ib hom tshwj xeeb ntawm ib nrab reconfiguration (PR), uas koj muaj ib cheeb tsam PR nyob rau hauv lwm cheeb tsam PR. Koj tuaj yeem tsim ntau tus neeg rau ob tus menyuam thiab niam txiv muab faib. Koj zes cov menyuam partitions hauv lawv niam txiv partitions. Reconfigure ib tug me nyuam muab faib tsis cuam tshuam kev ua hauj lwm nyob rau hauv cov niam txiv los yog static cheeb tsam. Reconfigure ib tug niam txiv muab faib tsis cuam tshuam rau kev khiav hauj lwm hauv cheeb tsam zoo li qub, tab sis hloov cov me nyuam partitions ntawm niam txiv cheeb tsam nrog default me nyuam partition personas. Cov txheej txheem no muaj txiaj ntsig zoo hauv cov kab ke uas muaj ntau lub sijhawm ua haujlwm-sib qhia tib yam FPGA cov khoom siv.

Ib nrab reconfiguration muab kev nce qib hauv qab no rau kev tsim vaj tsev:

- Tso cai rau lub sijhawm ua haujlwm tsim kho dua tshiab

- Nce scalability ntawm tus tsim

- Txo qhov system downtime

- Txhawb dynamic lub sij hawm-multiplexing zog nyob rau hauv tus tsim

- Txo tus nqi thiab kev siv hluav taws xob los ntawm kev siv lub rooj tsav xwm zoo

- Nco tseg:

- Kev ua raws li kev tsim qauv siv no yuav tsum muaj kev paub yooj yim nrog Intel Quartus® Prime FPGA kev siv ntws thiab kev paub txog thawj Intel Quartus Prime project files.

Cov ntaub ntawv ntsig txog

- Intel Arria 10 SoC Development Kit User Guide

- Ib nrab Reconfiguration Concepts

- Ib nrab Reconfiguration Design Flow

- Ib feem Reconfiguration Design Recommendations

- Ib nrab Reconfiguration Design Considerations

Reference Design Requirements

Qhov kev tsim qauv siv no xav tau cov hauv qab no:

- Intel Quartus Prime Pro Edition software version 17.1 rau kev tsim qauv siv.

- Intel Arria 10 SoC cov khoom siv txhim kho rau kev siv FPGA.

Intel Corporation. Txhua txoj cai. Intel, Intel logo, thiab lwm yam Intel cov cim yog cov cim lag luam ntawm Intel Corporation lossis nws cov koom haum. Intel lav kev ua tau zoo ntawm nws cov FPGA thiab cov khoom lag luam semiconductor rau cov kev qhia tshwj xeeb tam sim no raws li Intel tus qauv kev lees paub, tab sis muaj txoj cai los hloov cov khoom thiab cov kev pabcuam txhua lub sijhawm yam tsis muaj ntawv ceeb toom. Intel xav tias tsis muaj lub luag haujlwm lossis kev lav phib xaub uas tshwm sim los ntawm daim ntawv thov lossis siv cov ntaub ntawv, cov khoom lag luam, lossis cov kev pabcuam uas tau piav qhia hauv no tshwj tsis yog raws li tau pom zoo hauv kev sau ntawv los ntawm Intel. Intel cov neeg siv khoom tau qhia kom tau txais qhov tseeb version ntawm cov cuab yeej tshwj xeeb ua ntej tso siab rau cov ntaub ntawv tshaj tawm thiab ua ntej muab xaj rau cov khoom lossis cov kev pabcuam.

- Lwm lub npe thiab cov npe yuav raug lees paub tias yog cov cuab yeej ntawm lwm tus.

Reference Design Overview

- Cov qauv siv no muaj ib lub txee 32-ntsis. Nyob rau theem ntawm pawg thawj coj, tus qauv tsim txuas lub moos mus rau 50MHz qhov chaw thiab txuas cov zis rau plaub LEDs ntawm FPGA. Xaiv cov khoom tso tawm los ntawm cov khoom txee hauv ib ntu ua rau cov LEDs ntsais ntawm ib lub sijhawm tshwj xeeb.

Daim duab 1. Flat Reference Design yam tsis muaj PR Partitioning

Kev Tsim Qauv Files

Cov kev qhia ib nrab ntawm kev teeb tsa muaj nyob rau hauv qhov chaw hauv qab no: https://github.com/intel/fpga-partial-reconfig

Mus download tau lub tutorial:

- Nyem Clone los yog download tau.

- Nyem Download ZIP. Unzip FPGA-ib nrab-config-master.zip file.

- Nkag mus rau cov ntawv qhia / a10_soc_devkit_blinking_led_hpr sub-folder kom nkag mus rau tus qauv siv.

Cov ntaub ntawv tiaj tus muaj cov hauv qab no files:

Table 1. Reference Design Files

| File Lub npe | Kev piav qhia |

| saum. SV | Cov theem sab saum toj file muaj cov kev siv tiaj tus tsim. Qhov no module instantiates lub blinking_led sub-partition thiab lub top_counter module. |

| top_counter.sv | Sab saum toj-theem 32-ntsis txee uas tswj LED[1] ncaj qha. Cov tso zis tso npe ntawm lub txee tswj LED[0], thiab tseem muaj zog LED[2] thiab LED[3] ntawm lub blinking_led module. |

| blinking_led.sdc | Txhais lub sijhawm txwv rau qhov project. |

| txuas ntxiv… | |

| File Lub npe | Kev piav qhia |

| blinking_led.SV | Hauv qhov kev qhia no, koj hloov qhov module no rau hauv niam txiv PR muab faib. Lub module tau txais kev tso npe tso tawm ntawm top_counter module, uas tswj LED[2] thiab LED[3]. |

| blinking_led.qpf | Qhov project Intel Quartus Prime file muaj cov npe ntawm txhua qhov kev hloov kho hauv qhov project. |

| blinking_led.qsf | Intel Quartus Prime nqis file muaj cov haujlwm thiab kev teeb tsa rau qhov project. |

Nco tseg: Lub hpr nplaub tshev muaj cov txheej txheem tiav files koj tsim siv daim ntawv thov no. Siv cov no files ntawm txhua qhov chaw thaum lub sijhawm taug kev.

Daim duab 2. Kev Tsim Qauv Files

Reference Design Walkthrough

Cov kauj ruam hauv qab no piav qhia txog daim ntawv thov ntawm ib nrab reconfiguration rau ib qho kev tsim tiaj tus. Cov kev qhia siv Intel Quartus Prime Pro Edition software rau Intel Arria 10 SoC txhim kho pawg thawj coj saib:

- Kauj ruam 1: Pib ntawm nplooj 6

- Kauj ruam 2: Tsim Ib Tus Menyuam Qib Sub-module ntawm nplooj 6

- Kauj ruam 3: Tsim cov qauv tsim partitions ntawm nplooj 7

- Kauj ruam 4: Muab Kev Tso Npe thiab Routing Thaj Chaw rau PR Partitions ntawm nplooj 9

- Kauj ruam 5: Ntxiv Intel Arria 10 Ib Feem Kev Txhim Kho Kev Tswj Xyuas IP Core ntawm nplooj 10

- Kauj ruam 6: Defining Personas ntawm nplooj 13

- Kauj ruam 7: Tsim Kev Hloov Kho ntawm nplooj 15

- Kauj ruam 8: Tsim cov Hierarchical Partial Reconfiguration Flow Script ntawm nplooj 20

- Kauj ruam 9: Khiav lub Hierarchical Ib Feem Reconfiguration Flow Script ntawm nplooj 21

- Kauj ruam 10: Programming Pawg Thawj Coj ntawm nplooj 22

Kauj ruam 1: Pib pib

Yuav luam cov qauv siv files rau koj qhov chaw ua haujlwm thiab suav nrog blinking_led flat design:

- Tsim cov npe hauv koj qhov chaw ua haujlwm, a10_soc_devkit_blinking_led_hpr.

- Luam the downloaded tutorials/a10_soc_devkit_blinking_led_hpr/flat sub-folder to the directory, a10_soc_devkit_blinking_led_hpr.

- Hauv Intel Quartus Prime Pro Edition software, nyem File ➤ Qhib Project thiab xaiv blinking_led.qpf.

- Txhawm rau sau cov qauv tsim, nyem Ua tiav ➤ Pib Muab tso ua ke.

Kauj Ruam 2: Tsim Tus Menyuam Qib Qib Sub-module

Txhawm rau hloov lub tiaj tus qauv no mus rau hauv hierarchical PR tsim, koj yuav tsum tsim tus me nyuam sub-module (blinking_led_child. SV) uas yog ze rau hauv niam txiv sub-module (blinking_led.sv).

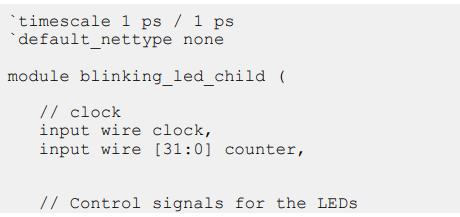

- Tsim tus qauv tshiab file, blinking_led_child.sv, thiab ntxiv cov kab hauv qab no ntawm cov cai rau qhov no file: timescale 1 ps / 1 ps `default_nettype tsis muaj module blinking_led_child ( // moos input hlau moos, input hlau [31:0] txee, // Tswj cov teeb liab rau cov LEDs

- Hloov kho lub blinking_led.sv file txhawm rau txuas tus led_two_on mus rau me ntsis 23 ntawm lub txee los ntawm thaj chaw zoo li qub, thiab ua kom lub blinking_led_child module. Tom qab hloov kho, koj blinking_led.sv file yuav tsum tshwm sim raws li nram no:

- Thaum hloov tag nrho cov tsim files, rov ua kom tiav qhov project los ntawm kev nyem Ua Haujlwm ➤ Pib Compilation

Kauj Ruam 3: Tsim cov qauv tsim partitions

Koj yuav tsum tsim cov qauv tsim rau txhua cheeb tsam PR uas koj xav kom rov kho dua ib nrab. Koj tuaj yeem tsim ib tus lej ntawm kev ywj pheej los yog thaj tsam PR hauv koj tus qauv tsim. Qhov kev qhia no tsim ob qho qauv tsim rau qhov u_blinking_led_child thiab u_blinking_led instances.

Txhawm rau tsim kev tsim partitions rau hierarchical ib nrab reconfiguration:

- Txoj cai-nias ntawm u_blinking_led_child piv txwv nyob rau hauv qhov Project Navigator thiab nyem Tsim Partition ➤ Teem raws li Design Partition. Ib tug tsim muab faib icon tshwm nyob ib sab ntawm txhua qhov piv txwv uas yog teem raws li ib tug muab faib.

Daim duab 3. Tsim cov qauv tsim los ntawm Project Navigator

- Txhawm rau txheeb xyuas hom muab faib, txoj cai-nias ntawm u_blinking_led_child piv txwv nyob rau hauv Hierarchy tab, nyem Tsim Partition ➤ Reconfigurable. Koj tsuas tuaj yeem txhais hom muab faib tom qab teeb tsa qhov piv txwv li kev faib tawm. Qhov kev faib tawm tsim tshwm rau ntawm Kev Ua Haujlwm View tab ntawm Design Partitions Window.

Daim duab 4. Tsim Partitions Qhov rai

- Kho lub npe muab faib nyob rau hauv Tsim Partitions Qhov rai los ntawm ob-nias lub npe. Rau qhov qauv siv no, hloov lub npe muab faib rau pr_partition.

Nco tseg: Thaum koj tsim ib qho kev faib tawm, Intel Quartus Prime software cia li tsim lub npe muab faib, raws li lub npe piv txwv thiab txoj hauv kev hierarchy. Lub npe muab faib no tuaj yeem sib txawv nrog txhua qhov piv txwv. - Rov ua cov kauj ruam 1 thiab 2 txhawm rau muab cov qauv tsim rov ua dua tshiab rau qhov piv txwv u_blinking_led. Rename no partition rau pr_parent_partition.

Xyuas kom tseeb tias lub blinking_led.qsf muaj cov haujlwm hauv qab no, sib xws rau koj qhov kev tsim qauv tsim rov ua dua tshiab:

Tsim Tsim Partitions rau ib nrab Reconfiguration

Kauj ruam 4: Kev faib chaw thiab Routing Region rau PR Partitions

Thaum koj tsim lub hauv paus kev kho dua tshiab, PR tsim ntws siv koj PR muab faib thaj tsam faib rau qhov sib thooj persona core hauv cheeb tsam tshwj tseg. Txhawm rau nrhiav thiab muab PR cheeb tsam hauv cov phiaj xwm hauv pem teb rau koj qhov kev hloov kho hauv paus:

- Txoj cai-nias ntawm u_blinking_led_child piv txwv hauv Project Navigator thiab nyem Logic Lock Region ➤ Tsim Logic Lock Region tshiab. Cov cheeb tsam tshwm nyob rau ntawm Logic Lock Regions Qhov rai.

- Koj cheeb tsam chaw tso kawm yuav tsum nyob nrog lub blinking_led_child logic. Xaiv thaj chaw tso kawm los ntawm kev nrhiav cov node hauv Chip Planner. Txoj cai-nias lub npe thaj tsam u_blinking_led_child hauv Project Navigator thiab nyem Locate Node ➤ Nrhiav hauv Chip Planner.

Daim duab 5. Chip Planner Node Qhov chaw rau blinking_led

- Nyob rau hauv Logic Lock Regions qhov rais, qhia qhov chaw muab kev koom tes hauv cheeb tsam hauv keeb kwm kab. Lub hauv paus chiv keeb sib raug rau lub kaum sab laug sab laug ntawm thaj av. Rau example, txhawm rau teeb tsa thaj chaw tso nrog (X1 Y1) kev tswj hwm raws li (69 10), qhia qhov Keeb Kwm li X69_Y10. Intel Quartus Prime software cia li suav cov (X2 Y2) kev tswj hwm (sab saum toj-txoj cai) rau thaj chaw tso, raws li qhov siab thiab qhov dav koj teev.

Nco tseg: Qhov kev qhia no siv (X1 Y1) kev tswj hwm - (69 10), thiab qhov siab thiab dav ntawm 20 rau thaj tsam tso kawm. Txhais ib qho txiaj ntsig rau thaj chaw tso kawm, yog tias cheeb tsam npog qhov blinking_led_child logic. - Qhib cov kev xaiv Reserved thiab Core-Tsuas.

- Ob-nias qhov kev xaiv Routing Region. Lub Logic Lock Routing Region Settings dialog box tshwm.

- Xaiv Tsau nrog nthuav dav rau hom Routing. Xaiv qhov kev xaiv no cia li muab qhov nthuav dav ntawm 1.

Nco tseg: Lub cheeb tsam routing yuav tsum loj dua qhov chaw tso chaw, muab kev yooj yim ntxiv rau Fitter thaum lub cav khiav cov neeg sib txawv. - Rov ua cov kauj ruam 1 -6 rau qhov piv txwv u_blinking_led. Parent-level placement Rov ua kauj ruam 1 -6 rau qhov piv txwv u_blinking_led. Lub cheeb tsam chaw niam txiv-theem yuav tsum tau kaw tag nrho qhov sib thooj ntawm qhov chaw me nyuam thiab cov cheeb tsam routing thaum tso cai rau qhov chaw txaus rau niam txiv-qib kev tso kawm. Qhov kev qhia no siv (X1 Y1) kev tswj hwm - (66 7), qhov siab ntawm 47, thiab qhov dav ntawm 26 rau thaj chaw tso kawm ntawm u_blinking_led piv txwv.

Daim duab 6.Logic Lock Regions Qhov rai

Xyuas kom tseeb tias blinking_led.qsf muaj cov haujlwm hauv qab no, sib xws rau koj qhov kev npaj hauv pem teb:

- Floorplan lub Ib Feem Reconfiguration Design

- Incrementally Implementing Partial Reconfiguration

Kauj Ruam 5: Ntxiv Intel Arria 10 Ib Feem Reconfiguration Controller IP Core

- Siv Intel Arria 10 Ib Feem Reconfiguration Controller IP core los kho qhov PR faib. Cov tub ntxhais IP no siv JTAG los kho qhov kev faib tawm PR. Txhawm rau ntxiv Intel Arria 10 Ib Feem Kev Txhim Kho Kev Tswj Xyuas IP core rau koj qhov project Intel Quartus Prime:

- Ntaus Ib Feem Reconfiguration hauv IP catalog.

- Txhawm rau tso lub IP Parameter Editor Pro qhov rais, xaiv Intel Arria 10 Ib Feem Kev Txhim Kho Kev Tswj Xyuas IP core los ntawm IP tsev qiv ntawv, thiab nyem Ntxiv.

- Hauv New IP Variant dialog box, ntaus pr_ip ua tus file npe thiab nyem Tsim. Siv lub default parameterization rau pr_ip. Xyuas kom meej tias Enable JTAG hom kev debug thiab Pab kom khov kev xaiv interface yog qhib, thiab Pab kom Avalon-MM qhev interface xaiv raug muab tua.

Daim duab 7. Intel Arria 10 Ib Feem Reconfiguration Controller IP Core Parameters

- Nyem Xauv, thiab tawm ntawm qhov parameter editor yam tsis tau tsim lub kaw lus. Intel Quartus Prime software tsim pr_ip.ip IP variation file, thiab ntxiv cov file mus rau qhov project blinking_led.

Nco tseg:

- Yog tias koj luam tawm pr_ip.ip file los ntawm hpr nplaub tshev, manually kho lub blinking_led.qsf file kom suav nrog cov kab hauv qab no: set_global_assignment -name IP_FILE pr_ip.ip ib

- Muab tus IP_FILE ua haujlwm tom qab SDC_FILE cov haujlwm (jtag.sdc thiab blinking_led.sdc) hauv koj li blinking_led.qsf file. Qhov kev txiav txim no ua kom muaj kev txwv tsim nyog ntawm Ib Feem Kev Txhim Kho IP core.

Nco tseg: Txhawm rau txheeb xyuas cov moos, SDC file rau PR IP yuav tsum ua raws li SDC uas tsim cov moos uas tus tub ntxhais IP siv. Koj pab txhawb qhov kev txiav txim no los ntawm kev ua kom lub .ip file rau PR IP core tuaj tom qab ib qho .ip files lub SDC files siv los tsim cov moos no hauv QSF file rau koj qhov kev hloov kho tshiab ntawm Intel Quartus Prime. Yog xav paub ntxiv, xa mus rau ntu Kev txwv Sijhawm nyob rau hauv Ib Feem Kev Txhim Kho IP Core User Guide.

Cov ntaub ntawv ntsig txog

- Ib Feem Reconfiguration IP Solutions Cov Neeg Siv Phau Ntawv Qhia

- Rau cov ntaub ntawv ntawm Ib Cheeb Tsam Reconfiguration Region Controller IP core.

- Ib Feem Reconfiguration IP Core User Guide

- Rau cov lus qhia txog kev txwv lub sijhawm.

Hloov kho cov qauv tsim sab saum toj

Hloov kho saum toj.SV file nrog PR_IP piv txwv:

- Txhawm rau ntxiv PR_IP piv txwv rau cov qauv tsim sab saum toj, tsis hais cov cai hauv qab no rau saum toj.SV file:

- Txhawm rau yuam kom cov chaw nres nkoj tso tawm mus rau lub logic 1 thaum lub sijhawm rov teeb tsa, siv lub zog tswj cov teeb liab tso tawm los ntawm PR_IP. Txawm li cas los xij, txhawm rau saib cov LED txuas ntxiv blinking los ntawm niam txiv PR muab faib thaum PR programming tus me nyuam muab faib, lub teeb liab tswj tsis pub dhau lub led_two_on. Xyuas kom meej tias pr_led_two_on ncaj qha

- Txhawm rau muab ib qho piv txwv ntawm tus niam txiv lub neej qub (blinking_led), hloov kho saum toj kawg nkaus.SV file nrog cov nram qab no thaiv ntawm code:

Daim duab 8. Ib Feem Reconfiguration IP Core Integration

Kauj Ruam 6: Txhais Cov Neeg

Qhov kev tsim qauv siv no txhais tau tsib tus neeg sib cais rau niam txiv thiab menyuam PR partitions. Txhawm rau txhais thiab suav nrog cov neeg hauv koj qhov project:

- Tsim plaub SystemVerilog files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv, thiab blinking_led_slow.sv hauv koj phau ntawv qhia ua haujlwm rau tsib tus neeg.

Nco tseg: Yog tias koj tsim qhov SystemVerilog files los ntawm Intel Quartus Prime Text Editor, lov tes taw Ntxiv file rau qhov kev xaiv tam sim no, thaum txuag lub files.

Table 2. Reference Design Personas

| File Lub npe | Kev piav qhia | Code |

| blinking_led_chid.sv | Default persona rau tus me nyuam-level tsim |

`timescale 1 ps / 1 ps `default_nettype tsis muaj module blinking_led_child ( // moos input hlau moos, input hlau [31:0] txee,

// Tswj teeb liab rau LEDs tso zis hlau led_three_on

); localparam COUNTER_TAP = 23; reg led_three_on_r;

assign led_three_on = led_three_on_r; always_ff @(posedge moos) pib led_three_on_r <= counter[COUNTER_TAP]; kawg

endmodule |

| txuas ntxiv… | ||

| File Lub npe | Kev piav qhia | Code |

| blinking_led_child_slow.sv | Cov

LED_THREE blinks qeeb |

`timescale 1 ps / 1 ps `default_nettype tsis muaj

module blinking_led_child_slow (

// moos input hlau moos, input hlau [31:0] txee,

// Tswj teeb liab rau LEDs tso zis hlau led_three_on );

localparam COUNTER_TAP = 27; reg led_three_on_r;

assign led_three_on = led_three_on_r; always_ff @(posedge moos) pib led_three_on_r <= counter[COUNTER_TAP]; kawg

endmodule |

| blinking_led_child_empty.sv | Cov

LED_THREE nyob twj ywm ON |

`timescale 1 ps / 1 ps `default_nettype tsis muaj

module blinking_led_child_empty (

// moos input hlau moos, input hlau [31:0] txee,

// Tswj teeb liab rau LEDs tso zis hlau led_three_on

);

// LED yog qis qis assign led_three_on = 1'b0;

endmodule |

| blinking_led_slow.sv | LED_TWO

blinks qeeb. |

`timescale 1 ps / 1 ps `default_nettype tsis muaj module blinking_led_slow( // moos input hlau moos, input hlau [31:0] txee,

// Tswj cov teeb liab rau LEDs tso zis hlau led_two_on, tso zis hlau led_three_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; assign led_two_on = led_two_on_r;

// Lub counter: always_ff @(posdge moos) pib led_two_on_r <= counter[COUNTER_TAP]; kawg

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .counter (ntaub ntawv), . moos (clock) |

| File Lub npe | Kev piav qhia | Code |

| ); ndmodule |

Kauj Ruam 3: Tsim cov qauv tsim partitions ntawm nplooj 7

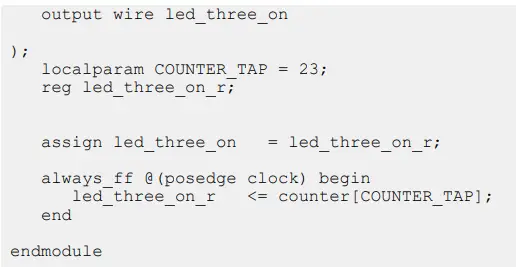

Kauj Ruam 7: Tsim cov kev hloov kho

PR tsim ntws siv qhov kev hloov kho qhov project hauv Intel Quartus Prime software. Koj qhov kev tsim thawj zaug yog lub hauv paus kev kho dua tshiab, qhov twg koj txhais cov cheeb tsam zoo li qub ciam teb thiab thaj chaw rov kho dua ntawm FPGA. Los ntawm kev hloov kho hauv paus, koj tsim ntau qhov kev hloov kho. Cov kev hloov kho no muaj cov kev siv sib txawv rau thaj tsam PR. Txawm li cas los xij, txhua qhov kev hloov kho PR siv tib qhov kev tso kawm saum toj kawg nkaus thiab cov txiaj ntsig tau los ntawm kev hloov kho hauv paus. Txhawm rau sau tus qauv PR, koj yuav tsum tsim kho PR kev siv thiab kev hloov kho rau txhua tus neeg. Hauv kev tsim qauv siv no, ntxiv rau qhov kev hloov kho hauv paus (blinking_led), peb tus me nyuam-theem tus neeg thiab ob tus niam txiv-theem tus neeg muaj tsib qhov kev hloov kho sib cais thiab tsib qhov kev hloov kho sib cais:

Table 3. Kev kho dua tshiab rau ob niam txiv thiab peb tus me nyuam

| Synthesis Revision | Kev kho dua tshiab |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_empty | blinking_led_pr_charlie ua |

| blinking_led_parent_slow, blinking_led_child_slow | blinking_led_pr_delta ua |

| blinking_led_parent_slow, blinking_led_child_empty | blinking_led_pr_emma |

Tsim cov kev hloov kho tshiab

Txhawm rau tsim cov kev hloov kho PR siv:

- Txhawm rau qhib lub Khoos Kas Kho Mob, nyem qhov Project ➤ Hloov kho.

- Txhawm rau tsim kho tshiab, nyem ob npaug rau < >.

- Qhia meej lub npe Hloov Kho raws li blinking_led_pr_alpha thiab xaiv blinking_led rau Raws li Kev Kho.

- Lov tes taw Teem raws li qhov kev hloov kho tam sim no thiab nyem OK.

- Ib yam li ntawd, tsim blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta, thiab blinking_led_pr_emma hloov kho, raws li kev hloov kho blinking_led.

Nco tseg: Tsis txhob muab cov kev hloov kho saum toj no raws li kev kho tam sim no.

Daim duab 9. Tsim Kho Kho

Tsim Synthesis-tsuas yog kho dua tshiab

Txhawm rau tsim cov kev hloov kho-tsuas yog rau cov neeg, koj yuav tsum muab cov chaw sab saum toj thiab sib haum SystemVerilog file rau txhua tus neeg:

- Hauv Intel Quartus Prime software, nyem qhov Project ➤ Hloov kho.

- Tsim blinking_led_default hloov kho raws li kev hloov kho blinking_led. Tsis txhob muab qhov kev hloov kho no raws li kev kho tam sim no.

- Hloov kho lub blinking_led_default.qsf file kom suav nrog cov haujlwm hauv qab no:

set_global_assignment -name TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -name SYSTEMVERILOG_FILE - Ib yam li ntawd, tsim blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent, thiab blinking_led_parent_slow revisions raws li blinking_led kho. Tsis txhob muab cov kev hloov kho no ua kev hloov kho tam sim no.

- Hloov tshiab blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, thiab blinking_led_parent_slow.qsf files nrog lawv sib xws

TOP_LEVEL_ENTITY thiab SYSTEMVERILOG_FILE tej hauj lwm:

- Txhawm rau kom tsis txhob muaj cov synthesis yuam kev, xyuas kom meej tias qhov kev hloov kho synthesis files rau cov me nyuam partitions tsis muaj ib tug tsim muab faib, pin assignments, los yog Logic Lock

cov hauj lwm hauv cheeb tsam. Tsis tas li ntawd, kev hloov kho synthesis files rau cov niam txiv partitions yuav tsum tsuas muaj tsim muab faib assignments rau tus me nyuam partitions. Tshem tawm cov haujlwm no, yog tias muaj, hauv blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, thiab blinking_led_parent_slow.pdf files

- suav nrog cov haujlwm hauv qab no hauv blinking_led_parent.qsf thiab blinking_led_parent_slow.qsf files:

- Xyuas kom tseeb tias blinking_led.qpf file muaj cov kev hloov kho hauv qab no, tsis muaj kev txiav txim tshwj xeeb:

- Nco tseg: Yog tias koj luam qhov hloov kho files los ntawm hpr nplaub tshev, manually hloov kho lub blinking_led.qpf file nrog cov kab saum toj no ntawm cov cai.

Specification Revision Hom

Koj yuav tsum muab hom kho dua tshiab rau txhua qhov kev kho dua tshiab. Muaj peb hom kev kho dua tshiab:

- Ib nrab Reconfiguration – Base

- Ib nrab Reconfiguration – Persona Synthesis

- Ib nrab Reconfiguration – Persona Implementation

- Cov lus hauv qab no teev cov kev hloov kho hom haujlwm rau txhua qhov kev hloov kho:

Table 4. Hom kev kho dua tshiab

| Kho lub npe | Kev kho hom |

| blinking_led.qsf | Ib nrab Reconfiguration – Base |

| blinking_led_default.qsf | Ib nrab Reconfiguration – Persona Synthesis |

| blinking_led_child_empty.qsf | Ib nrab Reconfiguration – Persona Synthesis |

| blinking_led_child_slow.qsf | Ib nrab Reconfiguration – Persona Synthesis |

| blinking_led_parent.qsf | Ib nrab Reconfiguration – Persona Synthesis |

| blinking_led_parent_slow.qsf | Ib nrab Reconfiguration – Persona Synthesis |

| blinking_led_pr_alpha.qsf | Ib nrab Reconfiguration – Persona Implementation |

| blinking_led_pr_bravo.qsf | Ib nrab Reconfiguration – Persona Implementation |

| blinking_led_pr_charlie.qsf | Ib nrab Reconfiguration – Persona Implementation |

| blinking_led_pr_delta.qsf | Ib nrab Reconfiguration – Persona Implementation |

| blinking_led_pr_emma.qsf | Ib nrab Reconfiguration – Persona Implementation |

- Nyem qhov Project ➤ Hloov kho. Lub Revisions dialog box tshwm.

- Xaiv blinking_led nyob rau hauv Revision Name kem, thiab nyem Teem Tam sim no.

- Nyem Thov. Qhov kev hloov kho blinking_led qhib.

- Txhawm rau teeb tsa hom kev hloov kho rau blinking_led, nyem Assignments ➤ Chaw ➤ General.

- Xaiv Hom Kho Kho raws li Ib Feem Kev Txhim Kho - Base.

- Ib yam li ntawd, teeb tsa cov kev hloov kho rau lwm kaum qhov kev hloov kho, raws li tau teev tseg hauv cov lus saum toj no.

- Nco tseg: Koj yuav tsum teeb tsa txhua qhov kev kho dua tshiab raws li qhov kev hloov kho tam sim no ua ntej muab cov kev hloov kho tshiab. Xyuas kom tseeb tias txhua .qsf file muaj cov haujlwm hauv qab no:

- Nco tseg: Ntxiv ib qho Fitter-tshwj xeeb cov chaw uas koj xav siv hauv kev siv PR suav nrog rau kev hloov kho tus neeg siv. Fitter-specific settings cuam tshuam qhov haum ntawm tus neeg, tab sis tsis cuam tshuam rau thaj av zoo li qub. Koj tuaj yeem ntxiv ib qho kev sib txuas tshwj xeeb rau kev hloov kho tus kheej ntawm tus kheej.

Tsim Kev Hloov Kho rau Personas

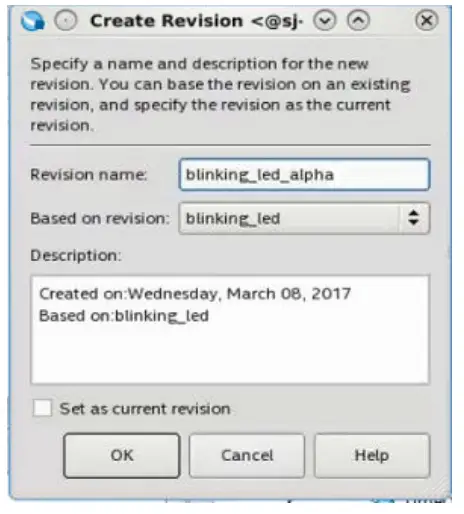

Kauj ruam 8: Tsim cov Hierarchical Partial Reconfiguration Flow Script

Los tsim cov hierarchical ib nrab reconfiguration flow tsab ntawv:

- Los ntawm Intel Quartus Prime cov lus txib plhaub, tsim cov qauv ntws los ntawm kev khiav cov lus txib hauv qab no:

- Intel Quartus Prime tsim cov a10_hier_partial_reconfig/flow.tcl file.

- Rename lub generated a10_hier_partial_reconfig/setup.tcl.example mus rau a10_hier_partial_reconfig/setup.tcl, thiab hloov cov ntawv los qhia koj cov ntsiab lus ntawm ib feem ntawm qhov project reconfiguration:

a. Txhawm rau txheeb xyuas lub npe ntawm qhov project, hloov cov kab hauv qab no: b. Txhawm rau txheeb xyuas lub hauv paus hloov kho, hloov cov kab hauv qab no:

b. Txhawm rau txheeb xyuas lub hauv paus hloov kho, hloov cov kab hauv qab no:

- Txhawm rau txheeb xyuas txhua qhov kev hloov kho ib nrab ntawm kev siv cov kev hloov kho, nrog rau cov npe PR muab faib thiab cov kev hloov kho uas siv cov kev hloov kho, hloov kho cov kab hauv qab no:

Nco tseg: Tag nrho cov kev kho dua tshiab yuav tsum nyob hauv tib phau ntawv raws li blinking_led.qpf. Txwv tsis pub, hloov kho cov ntawv ntws raws li.

Kauj ruam 9: Khiav lub Hierarchical Partial Reconfiguration Flow Script

Txhawm rau khiav lub hierarchical ib nrab reconfiguration flow tsab ntawv:

- Nyem Tools ➤ Tcl Scripts. Tcl Scripts dialog box tshwm.

- Nyem Ntxiv rau qhov Project, xauj thiab xaiv a10_hier_partial_reconfig/flow.tcl.

- Xaiv lub a10_hier_partial_reconfig/flow.tcl nyob rau hauv lub Libraries pane, thiab nyem Khiav.

Tsab ntawv no sau cov synthesis rau peb tus neeg. Intel Quartus Prime tsim cov khoom SRAM File (.sof), Ib Nrab-Masked SRAM Object File (.pmsf), thiab Raw Binary File (.rbf) rau txhua tus neeg.

Nco tseg: Txhawm rau khiav cov ntawv los ntawm Intel Quartus Prime cov lus txib plhaub, ntaus cov lus txib hauv qab no:

- Compile lub Ib Feem Reconfiguration Design

- Siv Ib Feem Reconfiguration Flow Script

- Configuring Partial Reconfiguration Flow Script

- Tsim Programming Files

Kauj ruam 10: Programming lub Rooj Tswjhwm Saib

Ua ntej koj pib:

- Txuas lub hwj huam mov mus rau Intel Arria 10 SoC txhim kho pawg thawj coj.

- Txuas lub USB Blaster cable ntawm koj lub PC USB chaw nres nkoj thiab USB Blaster chaw nres nkoj ntawm lub rooj tsav xwm kev loj hlob.

Txhawm rau khiav tus tsim ntawm Intel Arria 10 SoC kev txhim kho pawg thawj coj saib:

- Qhib Intel Quartus Prime software thiab nyem Cov Cuab Yeej ➤ Programmer.

- Hauv Programmer, nyem Hardware Setup thiab xaiv USB-Blaster.

- Nyem Pib Tshawb Nrhiav thiab xaiv lub cuab yeej, 10AS066N3.

- Nyem OK. Intel Quartus Prime software tshawb pom thiab hloov kho Programmer nrog peb FPGA chips ntawm lub rooj tsavxwm.

- Xaiv 10AS066N3 ntaus ntawv, nyem Hloov File thiab thauj cov blinking_led_pr_alpha.sof file.

- Qhib Program/Configure rau blinking_led_pr_alpha.sof file.

- Nyem Pib thiab tos rau qhov kev nce qib kom ncav cuag 100%.

- Saib xyuas cov LEDs ntawm lub rooj tsavxwm blinking ntawm tib zaus raws li tus qauv qub.

- Txhawm rau program tsuas yog tus me nyuam PR cheeb tsam, right-click lub blinking_led_pr_alpha.sof file hauv Programmer thiab nyem Ntxiv PR Programming File.

- Xaiv lub blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file.

- Disable Program/Configure rau blinking_led_pr_alpha.sof file.

- Pab kom Program/Configure rau blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file thiab nias Start. Ntawm lub rooj tsavxwm, saib LED[0] thiab LED[1] txuas ntxiv mus ntsais. Thaum qhov kev nce qib nce mus txog 100%, LED [2] blinks ntawm tib tus nqi, thiab LED [3] blinks qeeb.

- Txhawm rau muab ob qho tib si niam txiv thiab menyuam PR cheeb tsam, right-click lub .rbf file hauv Programmer thiab nyem Hloov PR Programing File.

- Xaiv lub blinking_led_pr_delta.pr_parent_partition.rbf file.

- Nyem Pib. Ntawm lub rooj tsavxwm, saib xyuas tias LED[0] thiab LED[1] txuas ntxiv mus ntsais. Thaum qhov kev nce qib nce mus txog 100%, ob qho tib si LED [2] thiab LED [3] blink qeeb.

- Rov ua cov kauj ruam saum toj no kom rov ua haujlwm rov ua haujlwm tsuas yog cheeb tsam PR tus menyuam, lossis ob qho tib si niam txiv thiab menyuam PR cheeb tsam ib txhij.

Daim duab 10. Programming Intel Arria 10 SoC Development Board

Hloov kho tus neeg uas twb muaj lawm

- Koj tuaj yeem hloov tus neeg uas twb muaj lawm, txawm tias tom qab sau tag nrho cov kev hloov kho hauv paus.

- Rau example, ua rau blinking_led_child_slow persona kom ntsais txawm qeeb:

- Hauv blinking_led_child_slow.sv file, hloov COUNTER_TAP parameter los ntawm 27 txog 28.

- Txhawm rau rov ua kom rov ua dua thiab rov ua dua tus neeg no, koj yuav tsum rov ua dua tag nrho cov kev hloov kho-tsuas yog kho dua tshiab thiab kho dua tshiab uas cuam tshuam los ntawm kev hloov pauv. Hloov kho cov ntawv setup.tcl kom suav nrog cov kab hauv qab no:

Nco tseg: Thaum txhais cov pr_parent_parition rau blinking_led_pr_delta kho, koj import qhov kawg snapshot ntawm tus neeg ntawd rau kev siv. Yog li ntawd, qhov kev siv ntawm niam txiv muab faib logic tseem zoo li qub, thaum hloov kho thiab siv cov kev faib me nyuam sib raug.

Nco tseg: Thaum txhais cov pr_parent_parition rau blinking_led_pr_delta kho, koj import qhov kawg snapshot ntawm tus neeg ntawd rau kev siv. Yog li ntawd, qhov kev siv ntawm niam txiv muab faib logic tseem zoo li qub, thaum hloov kho thiab siv cov kev faib me nyuam sib raug. Qhov kev hais kom ua no rov ua kom rov ua kom lub blinking_led_child_slow synthesis hloov kho, thiab tom qab ntawd sau cov kev siv PR suav nrog siv blinking_led_pr_bravo.

Qhov kev hais kom ua no rov ua kom rov ua kom lub blinking_led_child_slow synthesis hloov kho, thiab tom qab ntawd sau cov kev siv PR suav nrog siv blinking_led_pr_bravo. - Txhawm rau ua qhov kev sib sau ua ke ntawm cov kev hloov pauv nkaus xwb, khiav cov lus txib hauv qab no: Cov lus txib no tsis rov ua dua qhov hloov kho hauv paus.

- Txhawm rau ua kev suav sau ua ke ntawm kev hloov kho kev siv, khiav cov lus txib hauv qab no:

- Cov lus txib no tsis rov ua dua qhov kev hloov kho hauv paus.

- Ua raws li cov kauj ruam hauv Kauj Ruam 10: Kev Pabcuam Pawg Thawj Coj ntawm nplooj 22 txhawm rau tsim cov txiaj ntsig RBF file hauv FPGA.

Nco tseg: Txhawm rau zam kom tsis txhob khiav tag nrho cov dej ntws rau txhua qhov kev hloov kho, txhais cov kev hloov kho-tsuas yog kev hloov kho thiab kev siv cov kev hloov kho hauv cov ntawv setup.tcl, thiab khiav cov ntawv.

Ntxiv Tus Neeg Tshiab rau Tus Tsim

Tom qab sau tag nrho koj cov kev hloov kho hauv paus, koj tseem tuaj yeem ntxiv tus neeg tshiab thiab sau tus kheej cov neeg no.

Rau example, los txhais ib tug me nyuam tshiab persona rau blinking_led_parent_slow, uas tig led_three tawm:

- Luam blinking_led_child_empty.sv rau blinking_led_chdild_off.sv.

- Hauv blinking_led_child_off.sv file, hloov txoj haujlwm, muab led_three_on = 1'b0; assign led_three_on = 1'b1;. Xyuas kom koj hloov lub npe module ntawm blinking_led_child_empty rau blinking_led_child_off.

- Tsim ib qho kev kho tshiab synthesis, blinking_led_child_off, ua raws li cov kauj ruam hauv Kev Tsim Kev Hloov Kho-tsuas yog hloov kho ntawm nplooj 16.

Nco tseg: Kev hloov kho blinking_led_child_off yuav tsum siv lub blinking_led_child_off.sv file. - Tsim ib qho kev hloov kho tshiab, blinking_led_pr_foxtrot, los ntawm kev ua raws cov kauj ruam hauv Tsim Kev Hloov Kho Kev Ua Haujlwm ntawm nplooj 15.

- Hloov kho lub a10_hier_partial_reconfig/setup.tcl file los txhais qhov kev siv PR tshiab:

- Muab tso ua ke tsuas yog qhov kev sib txuas tshiab no thiab kev kho dua tshiab los ntawm kev khiav cov lus txib hauv qab no:

Txhawm rau ua tiav cov ntaub ntawv ntawm hierarchical ib nrab reconfiguration rau Intel Arria 10 cov khoom siv, xa mus rau Kev Tsim Kho Ib Nrab Reconfiguration Design nyob rau hauv Volume 1 ntawm Intel Quartus Prime Pro Edition Phau Ntawv.

Cov ntaub ntawv ntsig txog

- Tsim ib feem Reconfiguration Design

- Ib Feem Reconfiguration Online Training

Cov ntaub ntawv kho dua tshiab

Rooj 5. Cov ntaub ntawv kho dua keeb kwm

| Cov ntaub ntawv Version | Software Version | Hloov |

| 2017.11.06 | 17.1.0 | • Hloov kho cov Reference Design Requirements ntu nrog lub software version

• Hloov kho cov Flat Reference Design yam tsis muaj PR Partitioning daim duab nrog tsim thaiv kev hloov pauv • Hloov kho cov Kev Tsim Qauv Files rooj nrog cov ntaub ntawv ntawm lub Top_counter.sv module • Hloov kho cov Ib nrab Reconfiguration IP Core Integration daim duab nrog tsim thaiv kev hloov pauv • Hloov kho cov duab – Tsim Partitions Qhov rai thiab Logic Lock Regions Qhov rai los cuam tshuam qhov GUI tshiab • File npe hloov • Cov ntawv hloov kho |

| 2017.05.08 | 17.0.0 | Thawj qhov kev tso tawm ntawm cov ntaub ntawv |

Cov ntaub ntawv / Cov ntaub ntawv

|

intel AN 805 Hierarchical Ib Feem Reconfiguration ntawm Kev Tsim Kho ntawm Arria 10 SoC Development Board [ua pdf] Cov neeg siv phau ntawv qhia AN 805 Hierarchical Partial Reconfiguration of a Design on Arria 10 SoC Development Board, AN 805, Hierarchical Partial Reconfiguration of a Design on Arria 10 SoC Development Board, Reconfiguration of a Design on Arria 10 SoC Development Board, Arria 10 SoC Development Board, 10 SoC Pawg Neeg Saib Xyuas Kev Txhim Kho |