Arria 805 SoC ਵਿਕਾਸ ਬੋਰਡ 'ਤੇ ਡਿਜ਼ਾਈਨ ਦੀ intel AN 10 ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ

Intel® Arria® 10 SoC ਵਿਕਾਸ ਬੋਰਡ ਲਈ ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਟਿਊਟੋਰਿਅਲ

ਇਹ ਐਪਲੀਕੇਸ਼ਨ ਨੋਟ ਇੱਕ ਸਧਾਰਨ ਡਿਜ਼ਾਇਨ ਨੂੰ ਲੜੀਵਾਰ ਤੌਰ 'ਤੇ ਅੰਸ਼ਕ ਤੌਰ 'ਤੇ ਮੁੜ ਸੰਰਚਨਾਯੋਗ ਡਿਜ਼ਾਈਨ ਵਿੱਚ ਬਦਲਣ ਅਤੇ Intel® Arria® 10 SoC ਵਿਕਾਸ ਬੋਰਡ 'ਤੇ ਡਿਜ਼ਾਈਨ ਨੂੰ ਲਾਗੂ ਕਰਨ ਦਾ ਪ੍ਰਦਰਸ਼ਨ ਕਰਦਾ ਹੈ। ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ (HPR) ਇੱਕ ਵਿਸ਼ੇਸ਼ ਕਿਸਮ ਦੀ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ (PR), ਜਿੱਥੇ ਤੁਸੀਂ ਕਿਸੇ ਹੋਰ PR ਖੇਤਰ ਦੇ ਅੰਦਰ ਇੱਕ PR ਖੇਤਰ ਰੱਖਦੇ ਹੋ। ਤੁਸੀਂ ਬੱਚੇ ਅਤੇ ਮਾਤਾ-ਪਿਤਾ ਦੋਵਾਂ ਭਾਗਾਂ ਲਈ ਮਲਟੀਪਲ ਵਿਅਕਤੀ ਬਣਾ ਸਕਦੇ ਹੋ। ਤੁਸੀਂ ਚਾਈਲਡ ਭਾਗਾਂ ਨੂੰ ਉਹਨਾਂ ਦੇ ਪੇਰੈਂਟ ਭਾਗਾਂ ਵਿੱਚ ਨੇਸਟ ਕਰਦੇ ਹੋ। ਇੱਕ ਚਾਈਲਡ ਭਾਗ ਨੂੰ ਮੁੜ ਸੰਰਚਿਤ ਕਰਨਾ ਮਾਤਾ ਜਾਂ ਸਥਿਰ ਖੇਤਰਾਂ ਵਿੱਚ ਕਾਰਵਾਈ ਨੂੰ ਪ੍ਰਭਾਵਿਤ ਨਹੀਂ ਕਰਦਾ ਹੈ। ਇੱਕ ਪੇਰੈਂਟ ਭਾਗ ਨੂੰ ਮੁੜ ਸੰਰਚਿਤ ਕਰਨਾ ਸਥਿਰ ਖੇਤਰ ਵਿੱਚ ਕਾਰਵਾਈ ਨੂੰ ਪ੍ਰਭਾਵਤ ਨਹੀਂ ਕਰਦਾ ਹੈ, ਪਰ ਮੂਲ ਖੇਤਰ ਦੇ ਚਾਈਲਡ ਭਾਗਾਂ ਨੂੰ ਡਿਫਾਲਟ ਚਾਈਲਡ ਪਾਰਟੀਸ਼ਨ ਵਿਅਕਤੀਆਂ ਨਾਲ ਬਦਲਦਾ ਹੈ। ਇਹ ਵਿਧੀ ਉਹਨਾਂ ਪ੍ਰਣਾਲੀਆਂ ਵਿੱਚ ਪ੍ਰਭਾਵਸ਼ਾਲੀ ਹੈ ਜਿੱਥੇ ਮਲਟੀਪਲ ਫੰਕਸ਼ਨ ਇੱਕੋ FPGA ਡਿਵਾਈਸ ਸਰੋਤਾਂ ਨੂੰ ਸਮਾਂ-ਸਾਂਝਾ ਕਰਦੇ ਹਨ।

ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਇੱਕ ਫਲੈਟ ਡਿਜ਼ਾਈਨ ਲਈ ਹੇਠ ਲਿਖੀਆਂ ਤਰੱਕੀ ਪ੍ਰਦਾਨ ਕਰਦੀ ਹੈ:

- ਰਨ-ਟਾਈਮ ਡਿਜ਼ਾਈਨ ਰੀਕਨਫਿਗਰੇਸ਼ਨ ਦੀ ਆਗਿਆ ਦਿੰਦਾ ਹੈ

- ਡਿਜ਼ਾਈਨ ਦੀ ਮਾਪਯੋਗਤਾ ਨੂੰ ਵਧਾਉਂਦਾ ਹੈ

- ਸਿਸਟਮ ਡਾਊਨਟਾਈਮ ਨੂੰ ਘਟਾਉਂਦਾ ਹੈ

- ਡਿਜ਼ਾਈਨ ਵਿੱਚ ਡਾਇਨਾਮਿਕ ਟਾਈਮ-ਮਲਟੀਪਲੈਕਸਿੰਗ ਫੰਕਸ਼ਨਾਂ ਦਾ ਸਮਰਥਨ ਕਰਦਾ ਹੈ

- ਬੋਰਡ ਸਪੇਸ ਦੀ ਕੁਸ਼ਲ ਵਰਤੋਂ ਦੁਆਰਾ ਲਾਗਤ ਅਤੇ ਬਿਜਲੀ ਦੀ ਖਪਤ ਨੂੰ ਘਟਾਉਂਦਾ ਹੈ

- ਨੋਟ:

- ਇਸ ਸੰਦਰਭ ਡਿਜ਼ਾਈਨ ਨੂੰ ਲਾਗੂ ਕਰਨ ਲਈ Intel Quartus® Prime FPGA ਲਾਗੂਕਰਨ ਪ੍ਰਵਾਹ ਅਤੇ ਪ੍ਰਾਇਮਰੀ Intel Quartus Prime ਪ੍ਰੋਜੈਕਟ ਦੇ ਗਿਆਨ ਨਾਲ ਮੁੱਢਲੀ ਜਾਣ-ਪਛਾਣ ਦੀ ਲੋੜ ਹੈ। files.

ਸੰਬੰਧਿਤ ਜਾਣਕਾਰੀ

- Intel Arria 10 SoC ਵਿਕਾਸ ਕਿੱਟ ਯੂਜ਼ਰ ਗਾਈਡ

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਸੰਕਲਪ

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਡਿਜ਼ਾਈਨ ਪ੍ਰਵਾਹ

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਡਿਜ਼ਾਈਨ ਸਿਫ਼ਾਰਿਸ਼ਾਂ

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਡਿਜ਼ਾਈਨ ਵਿਚਾਰ

ਸੰਦਰਭ ਡਿਜ਼ਾਈਨ ਲੋੜਾਂ

ਇਸ ਸੰਦਰਭ ਡਿਜ਼ਾਈਨ ਲਈ ਹੇਠ ਲਿਖੇ ਦੀ ਲੋੜ ਹੈ:

- ਡਿਜ਼ਾਈਨ ਲਾਗੂ ਕਰਨ ਲਈ Intel Quartus Prime Pro ਐਡੀਸ਼ਨ ਸਾਫਟਵੇਅਰ ਵਰਜਨ 17.1।

- FPGA ਲਾਗੂ ਕਰਨ ਲਈ Intel Arria 10 SoC ਵਿਕਾਸ ਕਿੱਟ।

ਇੰਟੇਲ ਕਾਰਪੋਰੇਸ਼ਨ. ਸਾਰੇ ਹੱਕ ਰਾਖਵੇਂ ਹਨ. Intel, Intel ਲੋਗੋ, ਅਤੇ ਹੋਰ Intel ਚਿੰਨ੍ਹ Intel ਕਾਰਪੋਰੇਸ਼ਨ ਜਾਂ ਇਸਦੀਆਂ ਸਹਾਇਕ ਕੰਪਨੀਆਂ ਦੇ ਟ੍ਰੇਡਮਾਰਕ ਹਨ। Intel ਆਪਣੇ FPGA ਅਤੇ ਸੈਮੀਕੰਡਕਟਰ ਉਤਪਾਦਾਂ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ ਦੀ ਵਾਰੰਟੀ Intel ਦੀ ਸਟੈਂਡਰਡ ਵਾਰੰਟੀ ਦੇ ਅਨੁਸਾਰ ਮੌਜੂਦਾ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਦੇ ਅਨੁਸਾਰ ਕਰਦਾ ਹੈ, ਪਰ ਬਿਨਾਂ ਨੋਟਿਸ ਦੇ ਕਿਸੇ ਵੀ ਸਮੇਂ ਕਿਸੇ ਵੀ ਉਤਪਾਦ ਅਤੇ ਸੇਵਾਵਾਂ ਵਿੱਚ ਤਬਦੀਲੀਆਂ ਕਰਨ ਦਾ ਅਧਿਕਾਰ ਰਾਖਵਾਂ ਰੱਖਦਾ ਹੈ। ਇੰਟੇਲ ਇੱਥੇ ਵਰਣਿਤ ਕਿਸੇ ਵੀ ਜਾਣਕਾਰੀ, ਉਤਪਾਦ, ਜਾਂ ਸੇਵਾ ਦੀ ਐਪਲੀਕੇਸ਼ਨ ਜਾਂ ਵਰਤੋਂ ਤੋਂ ਪੈਦਾ ਹੋਣ ਵਾਲੀ ਕੋਈ ਜ਼ਿੰਮੇਵਾਰੀ ਜਾਂ ਜ਼ਿੰਮੇਵਾਰੀ ਨਹੀਂ ਲੈਂਦਾ, ਸਿਵਾਏ ਇੰਟੇਲ ਦੁਆਰਾ ਲਿਖਤੀ ਤੌਰ 'ਤੇ ਸਪੱਸ਼ਟ ਤੌਰ 'ਤੇ ਸਹਿਮਤ ਹੋਏ। Intel ਗਾਹਕਾਂ ਨੂੰ ਸਲਾਹ ਦਿੱਤੀ ਜਾਂਦੀ ਹੈ ਕਿ ਉਹ ਕਿਸੇ ਵੀ ਪ੍ਰਕਾਸ਼ਿਤ ਜਾਣਕਾਰੀ 'ਤੇ ਭਰੋਸਾ ਕਰਨ ਤੋਂ ਪਹਿਲਾਂ ਅਤੇ ਉਤਪਾਦਾਂ ਜਾਂ ਸੇਵਾਵਾਂ ਲਈ ਆਰਡਰ ਦੇਣ ਤੋਂ ਪਹਿਲਾਂ ਡਿਵਾਈਸ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਦਾ ਨਵੀਨਤਮ ਸੰਸਕਰਣ ਪ੍ਰਾਪਤ ਕਰਨ।

- ਹੋਰ ਨਾਵਾਂ ਅਤੇ ਬ੍ਰਾਂਡਾਂ 'ਤੇ ਦੂਜਿਆਂ ਦੀ ਸੰਪਤੀ ਵਜੋਂ ਦਾਅਵਾ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ।

ਸੰਦਰਭ ਡਿਜ਼ਾਈਨ ਓਵਰview

- ਇਸ ਸੰਦਰਭ ਡਿਜ਼ਾਈਨ ਵਿੱਚ ਇੱਕ 32-ਬਿੱਟ ਕਾਊਂਟਰ ਹੁੰਦਾ ਹੈ। ਬੋਰਡ ਪੱਧਰ 'ਤੇ, ਡਿਜ਼ਾਈਨ ਘੜੀ ਨੂੰ 50MHz ਸਰੋਤ ਨਾਲ ਜੋੜਦਾ ਹੈ ਅਤੇ ਆਊਟਪੁੱਟ ਨੂੰ FPGA 'ਤੇ ਚਾਰ LEDs ਨਾਲ ਜੋੜਦਾ ਹੈ। ਇੱਕ ਖਾਸ ਕ੍ਰਮ ਵਿੱਚ ਕਾਊਂਟਰ ਬਿੱਟਾਂ ਤੋਂ ਆਉਟਪੁੱਟ ਦੀ ਚੋਣ ਕਰਨ ਨਾਲ ਇੱਕ ਖਾਸ ਬਾਰੰਬਾਰਤਾ 'ਤੇ LEDs ਝਪਕਦੇ ਹਨ।

ਚਿੱਤਰ 1. PR ਵਿਭਾਗੀਕਰਨ ਦੇ ਬਿਨਾਂ ਫਲੈਟ ਰੈਫਰੈਂਸ ਡਿਜ਼ਾਈਨ

ਹਵਾਲਾ ਡਿਜ਼ਾਈਨ Files

ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਟਿਊਟੋਰਿਅਲ ਹੇਠ ਦਿੱਤੇ ਸਥਾਨ 'ਤੇ ਉਪਲਬਧ ਹੈ: https://github.com/intel/fpga-partial-reconfig

ਟਿਊਟੋਰਿਅਲ ਨੂੰ ਡਾਊਨਲੋਡ ਕਰਨ ਲਈ:

- ਕਲੋਨ 'ਤੇ ਕਲਿੱਕ ਕਰੋ ਜਾਂ ਡਾਊਨਲੋਡ ਕਰੋ।

- ਜ਼ਿਪ ਡਾਊਨਲੋਡ ਕਰੋ 'ਤੇ ਕਲਿੱਕ ਕਰੋ। FPGA-partial-config-master.zip ਨੂੰ ਅਨਜ਼ਿਪ ਕਰੋ file.

- ਹਵਾਲਾ ਡਿਜ਼ਾਈਨ ਤੱਕ ਪਹੁੰਚ ਕਰਨ ਲਈ ਟਿਊਟੋਰਿਅਲਸ/a10_soc_devkit_blinking_led_hpr ਸਬ-ਫੋਲਡਰ 'ਤੇ ਜਾਓ।

ਫਲੈਟ ਫੋਲਡਰ ਵਿੱਚ ਹੇਠ ਲਿਖੇ ਸ਼ਾਮਲ ਹਨ files:

ਸਾਰਣੀ 1. ਹਵਾਲਾ ਡਿਜ਼ਾਈਨ Files

| File ਨਾਮ | ਵਰਣਨ |

| ਸਿਖਰ ਐੱਸ.ਵੀ | ਸਿਖਰ-ਪੱਧਰ file ਡਿਜ਼ਾਈਨ ਦਾ ਫਲੈਟ ਲਾਗੂ ਕਰਨਾ ਸ਼ਾਮਲ ਹੈ। ਇਹ ਮੋਡੀਊਲ blinking_led ਸਬ-ਪਾਰਟੀਸ਼ਨ ਅਤੇ top_counter ਮੋਡੀਊਲ ਨੂੰ ਤੁਰੰਤ ਬਣਾਉਂਦਾ ਹੈ। |

| top_counter.sv | ਸਿਖਰ-ਪੱਧਰ ਦਾ 32-ਬਿੱਟ ਕਾਊਂਟਰ ਜੋ LED[1] ਨੂੰ ਸਿੱਧਾ ਕੰਟਰੋਲ ਕਰਦਾ ਹੈ। ਕਾਊਂਟਰ ਦਾ ਰਜਿਸਟਰਡ ਆਉਟਪੁੱਟ LED[0] ਨੂੰ ਕੰਟਰੋਲ ਕਰਦਾ ਹੈ, ਅਤੇ Blinking_led ਮੋਡੀਊਲ ਰਾਹੀਂ LED[2] ਅਤੇ LED[3] ਨੂੰ ਵੀ ਪਾਵਰ ਦਿੰਦਾ ਹੈ। |

| blinking_led.sdc | ਪ੍ਰੋਜੈਕਟ ਲਈ ਸਮਾਂ ਸੀਮਾਵਾਂ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਦਾ ਹੈ। |

| ਜਾਰੀ… | |

| File ਨਾਮ | ਵਰਣਨ |

| blinking_led.SV | ਇਸ ਟਿਊਟੋਰਿਅਲ ਵਿੱਚ, ਤੁਸੀਂ ਇਸ ਮੋਡੀਊਲ ਨੂੰ ਇੱਕ ਪੇਰੈਂਟ PR ਭਾਗ ਵਿੱਚ ਬਦਲਦੇ ਹੋ। ਮੋਡੀਊਲ top_counter ਮੋਡੀਊਲ ਦਾ ਰਜਿਸਟਰਡ ਆਉਟਪੁੱਟ ਪ੍ਰਾਪਤ ਕਰਦਾ ਹੈ, ਜੋ LED[2] ਅਤੇ LED[3] ਨੂੰ ਕੰਟਰੋਲ ਕਰਦਾ ਹੈ। |

| blinking_led.qpf | Intel Quartus Prime ਪ੍ਰੋਜੈਕਟ file ਪ੍ਰੋਜੈਕਟ ਵਿੱਚ ਸਾਰੇ ਸੰਸ਼ੋਧਨਾਂ ਦੀ ਸੂਚੀ ਰੱਖਦਾ ਹੈ। |

| blinking_led.qsf | Intel Quartus Prime ਸੈਟਿੰਗਾਂ file ਪ੍ਰੋਜੈਕਟ ਲਈ ਅਸਾਈਨਮੈਂਟ ਅਤੇ ਸੈਟਿੰਗਾਂ ਨੂੰ ਸ਼ਾਮਲ ਕਰਦਾ ਹੈ। |

ਨੋਟ: hpr ਫੋਲਡਰ ਵਿੱਚ ਦਾ ਪੂਰਾ ਸੈੱਟ ਹੁੰਦਾ ਹੈ fileਤੁਸੀਂ ਇਸ ਐਪਲੀਕੇਸ਼ਨ ਨੋਟ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਬਣਾਉਂਦੇ ਹੋ। ਇਹਨਾਂ ਦਾ ਹਵਾਲਾ ਦਿਓ fileਵਾਕਥਰੂ ਦੌਰਾਨ ਕਿਸੇ ਵੀ ਬਿੰਦੂ 'ਤੇ s.

ਚਿੱਤਰ 2. ਹਵਾਲਾ ਡਿਜ਼ਾਈਨ Files

ਹਵਾਲਾ ਡਿਜ਼ਾਈਨ ਵਾਕਥਰੂ

ਹੇਠਾਂ ਦਿੱਤੇ ਕਦਮ ਫਲੈਟ ਡਿਜ਼ਾਈਨ ਲਈ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਦੀ ਵਰਤੋਂ ਦਾ ਵਰਣਨ ਕਰਦੇ ਹਨ। ਟਿਊਟੋਰਿਅਲ ਇੰਟੇਲ ਅਰਰੀਆ 10 SoC ਡਿਵੈਲਪਮੈਂਟ ਬੋਰਡ ਲਈ Intel Quartus Prime Pro ਐਡੀਸ਼ਨ ਸੌਫਟਵੇਅਰ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ:

- ਕਦਮ 1: ਪੰਨਾ 6 'ਤੇ ਸ਼ੁਰੂਆਤ ਕਰਨਾ

- ਕਦਮ 2: ਪੰਨਾ 6 'ਤੇ ਬਾਲ ਪੱਧਰ ਦਾ ਸਬ-ਮੋਡਿਊਲ ਬਣਾਓ

- ਕਦਮ 3: ਸਫ਼ਾ 7 'ਤੇ ਡਿਜ਼ਾਈਨ ਭਾਗ ਬਣਾਉਣਾ

- ਕਦਮ 4: ਪੰਨਾ 9 'ਤੇ PR ਭਾਗਾਂ ਲਈ ਪਲੇਸਮੈਂਟ ਅਤੇ ਰੂਟਿੰਗ ਖੇਤਰ ਨਿਰਧਾਰਤ ਕਰਨਾ

- ਕਦਮ 5: ਪੰਨਾ 10 'ਤੇ Intel Arria 10 ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਕੰਟਰੋਲਰ IP ਕੋਰ ਨੂੰ ਜੋੜਨਾ

- ਕਦਮ 6: ਪੰਨਾ 13 'ਤੇ ਵਿਅਕਤੀਆਂ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਨਾ

- ਕਦਮ 7: ਪੰਨਾ 15 'ਤੇ ਸੰਸ਼ੋਧਨ ਬਣਾਉਣਾ

- ਕਦਮ 8: ਪੰਨਾ 20 'ਤੇ ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਪ੍ਰਵਾਹ ਸਕ੍ਰਿਪਟ ਤਿਆਰ ਕਰਨਾ

- ਕਦਮ 9: ਪੰਨਾ 21 'ਤੇ ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਪ੍ਰਵਾਹ ਸਕ੍ਰਿਪਟ ਨੂੰ ਚਲਾਉਣਾ

- ਕਦਮ 10: ਪੰਨਾ 22 'ਤੇ ਬੋਰਡ ਦਾ ਪ੍ਰੋਗਰਾਮਿੰਗ

ਕਦਮ 1: ਸ਼ੁਰੂ ਕਰਨਾ

ਹਵਾਲਾ ਡਿਜ਼ਾਈਨ ਦੀ ਨਕਲ ਕਰਨ ਲਈ files ਨੂੰ ਤੁਹਾਡੇ ਕੰਮ ਕਰਨ ਵਾਲੇ ਵਾਤਾਵਰਣ ਨਾਲ ਜੋੜੋ ਅਤੇ blinking_led ਫਲੈਟ ਡਿਜ਼ਾਈਨ ਨੂੰ ਕੰਪਾਇਲ ਕਰੋ:

- ਆਪਣੇ ਕੰਮ ਕਰਨ ਵਾਲੇ ਵਾਤਾਵਰਣ ਵਿੱਚ ਇੱਕ ਡਾਇਰੈਕਟਰੀ ਬਣਾਓ, a10_soc_devkit_blinking_led_hpr.

- ਡਾਉਨਲੋਡ ਕੀਤੇ ਟਿਊਟੋਰਿਅਲਸ/a10_soc_devkit_blinking_led_hpr/flat ਸਬ-ਫੋਲਡਰ ਨੂੰ ਡਾਇਰੈਕਟਰੀ, a10_soc_devkit_blinking_led_hpr ਵਿੱਚ ਕਾਪੀ ਕਰੋ।

- Intel Quartus Prime Pro Edition ਸਾਫਟਵੇਅਰ ਵਿੱਚ, ਕਲਿੱਕ ਕਰੋ File ➤ ਪ੍ਰੋਜੈਕਟ ਖੋਲ੍ਹੋ ਅਤੇ blinking_led.qpf ਚੁਣੋ।

- ਫਲੈਟ ਡਿਜ਼ਾਈਨ ਨੂੰ ਕੰਪਾਇਲ ਕਰਨ ਲਈ, ਪ੍ਰੋਸੈਸਿੰਗ ➤ ਸੰਕਲਨ ਸ਼ੁਰੂ ਕਰੋ 'ਤੇ ਕਲਿੱਕ ਕਰੋ।

ਕਦਮ 2: ਇੱਕ ਬਾਲ ਪੱਧਰ ਉਪ-ਮੋਡਿਊਲ ਬਣਾਉਣਾ

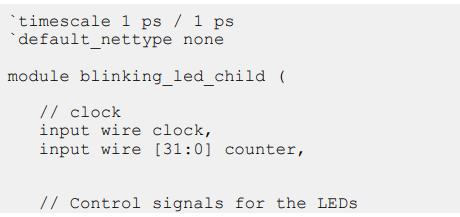

ਇਸ ਫਲੈਟ ਡਿਜ਼ਾਈਨ ਨੂੰ ਇੱਕ ਲੜੀਵਾਰ PR ਡਿਜ਼ਾਈਨ ਵਿੱਚ ਬਦਲਣ ਲਈ, ਤੁਹਾਨੂੰ ਇੱਕ ਚਾਈਲਡ ਸਬ-ਮੋਡਿਊਲ (blinking_led_child. SV) ਬਣਾਉਣਾ ਚਾਹੀਦਾ ਹੈ ਜੋ ਕਿ ਪੇਰੈਂਟ ਸਬ-ਮੋਡਿਊਲ (blinking_led.sv) ਦੇ ਅੰਦਰ ਸਥਿਤ ਹੈ।

- ਇੱਕ ਨਵਾਂ ਡਿਜ਼ਾਈਨ ਬਣਾਓ file, blinking_led_child.sv, ਅਤੇ ਇਸ ਵਿੱਚ ਕੋਡ ਦੀਆਂ ਹੇਠ ਲਿਖੀਆਂ ਲਾਈਨਾਂ ਜੋੜੋ file: ਟਾਈਮਸਕੇਲ 1 ps / 1 ps `default_nettype none ਮੋਡੀਊਲ blinking_led_child ( // ਘੜੀ ਇਨਪੁਟ ਵਾਇਰ ਘੜੀ, ਇਨਪੁਟ ਤਾਰ [31:0] ਕਾਊਂਟਰ, // LEDs ਲਈ ਕੰਟਰੋਲ ਸਿਗਨਲ

- blinking_led.sv ਨੂੰ ਸੋਧੋ file led_two_on ਨੂੰ ਸਥਿਰ ਖੇਤਰ ਤੋਂ ਕਾਊਂਟਰ ਦੇ ਬਿੱਟ 23 ਨਾਲ ਕਨੈਕਟ ਕਰਨ ਲਈ, ਅਤੇ blinking_led_child ਮੋਡੀਊਲ ਨੂੰ ਚਾਲੂ ਕਰੋ। ਸੋਧਾਂ ਤੋਂ ਬਾਅਦ, ਤੁਹਾਡੀ blinking_led.sv file ਹੇਠ ਲਿਖੇ ਅਨੁਸਾਰ ਪ੍ਰਗਟ ਹੋਣਾ ਚਾਹੀਦਾ ਹੈ:

- ਸਾਰੇ ਡਿਜ਼ਾਈਨ ਨੂੰ ਸੋਧਣ 'ਤੇ files, ਪ੍ਰੋਸੈਸਿੰਗ ➤ ਸੰਕਲਨ ਸ਼ੁਰੂ ਕਰੋ 'ਤੇ ਕਲਿੱਕ ਕਰਕੇ ਪ੍ਰੋਜੈਕਟ ਨੂੰ ਦੁਬਾਰਾ ਕੰਪਾਈਲ ਕਰੋ

ਕਦਮ 3: ਡਿਜ਼ਾਈਨ ਭਾਗ ਬਣਾਉਣਾ

ਤੁਹਾਨੂੰ ਹਰੇਕ PR ਖੇਤਰ ਲਈ ਡਿਜ਼ਾਈਨ ਭਾਗ ਬਣਾਉਣੇ ਚਾਹੀਦੇ ਹਨ ਜਿਸਨੂੰ ਤੁਸੀਂ ਅੰਸ਼ਕ ਤੌਰ 'ਤੇ ਮੁੜ ਸੰਰਚਿਤ ਕਰਨਾ ਚਾਹੁੰਦੇ ਹੋ। ਤੁਸੀਂ ਆਪਣੇ ਡਿਜ਼ਾਈਨ ਵਿੱਚ ਕਿਸੇ ਵੀ ਗਿਣਤੀ ਵਿੱਚ ਸੁਤੰਤਰ ਭਾਗ ਜਾਂ PR ਖੇਤਰ ਬਣਾ ਸਕਦੇ ਹੋ। ਇਹ ਟਿਊਟੋਰਿਅਲ u_blinking_led_child ਅਤੇ u_blinking_led ਉਦਾਹਰਨਾਂ ਲਈ ਦੋ ਡਿਜ਼ਾਈਨ ਭਾਗ ਬਣਾਉਂਦਾ ਹੈ।

ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਲਈ ਡਿਜ਼ਾਈਨ ਭਾਗ ਬਣਾਉਣ ਲਈ:

- ਪ੍ਰੋਜੈਕਟ ਨੈਵੀਗੇਟਰ ਵਿੱਚ u_blinking_led_child ਉਦਾਹਰਨ ਉੱਤੇ ਸੱਜਾ-ਕਲਿੱਕ ਕਰੋ ਅਤੇ ਡਿਜ਼ਾਈਨ ਭਾਗ ➤ ਡਿਜ਼ਾਈਨ ਭਾਗ ਵਜੋਂ ਸੈੱਟ ਕਰੋ 'ਤੇ ਕਲਿੱਕ ਕਰੋ। ਇੱਕ ਡਿਜ਼ਾਇਨ ਭਾਗ ਆਈਕਨ ਹਰੇਕ ਉਦਾਹਰਣ ਦੇ ਅੱਗੇ ਦਿਖਾਈ ਦਿੰਦਾ ਹੈ ਜੋ ਕਿ ਇੱਕ ਭਾਗ ਵਜੋਂ ਸੈੱਟ ਕੀਤਾ ਗਿਆ ਹੈ।

ਚਿੱਤਰ 3. ਪ੍ਰੋਜੈਕਟ ਨੇਵੀਗੇਟਰ ਤੋਂ ਡਿਜ਼ਾਈਨ ਭਾਗ ਬਣਾਉਣਾ

- ਭਾਗ ਦੀ ਕਿਸਮ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਨ ਲਈ, Hierarchy ਟੈਬ ਵਿੱਚ u_blinking_led_child ਉਦਾਹਰਨ ਉੱਤੇ ਸੱਜਾ-ਕਲਿੱਕ ਕਰੋ, ਡਿਜ਼ਾਇਨ ਭਾਗ ➤ ਮੁੜ ਸੰਰਚਨਾਯੋਗ ਕਲਿੱਕ ਕਰੋ। ਤੁਸੀਂ ਭਾਗ ਦੀ ਕਿਸਮ ਨੂੰ ਸਿਰਫ਼ ਇੱਕ ਭਾਗ ਵਜੋਂ ਸੈੱਟ ਕਰਨ ਤੋਂ ਬਾਅਦ ਹੀ ਪਰਿਭਾਸ਼ਿਤ ਕਰ ਸਕਦੇ ਹੋ। ਡਿਜ਼ਾਈਨ ਭਾਗ ਅਸਾਈਨਮੈਂਟਸ 'ਤੇ ਦਿਖਾਈ ਦਿੰਦਾ ਹੈ View ਡਿਜ਼ਾਈਨ ਭਾਗ ਵਿੰਡੋ ਦੀ ਟੈਬ।

ਚਿੱਤਰ 4. ਡਿਜ਼ਾਇਨ ਭਾਗ ਵਿੰਡੋ

- ਡਿਜ਼ਾਇਨ ਭਾਗ ਵਿੰਡੋ ਵਿੱਚ ਭਾਗ ਦੇ ਨਾਮ ਨੂੰ ਦੋ ਵਾਰ ਕਲਿੱਕ ਕਰਕੇ ਸੰਪਾਦਿਤ ਕਰੋ। ਇਸ ਸੰਦਰਭ ਡਿਜ਼ਾਈਨ ਲਈ, ਭਾਗ ਦਾ ਨਾਂ pr_partition ਵਿੱਚ ਬਦਲੋ।

ਨੋਟ: ਜਦੋਂ ਤੁਸੀਂ ਇੱਕ ਭਾਗ ਬਣਾਉਂਦੇ ਹੋ, ਤਾਂ Intel Quartus Prime ਸਾਫਟਵੇਅਰ ਆਟੋਮੈਟਿਕਲੀ ਇੱਕ ਭਾਗ ਨਾਮ ਤਿਆਰ ਕਰਦਾ ਹੈ, ਉਦਾਹਰਣ ਦੇ ਨਾਮ ਅਤੇ ਦਰਜਾਬੰਦੀ ਮਾਰਗ ਦੇ ਅਧਾਰ ਤੇ। ਇਹ ਡਿਫਾਲਟ ਭਾਗ ਨਾਂ ਹਰੇਕ ਮੌਕੇ ਨਾਲ ਬਦਲ ਸਕਦਾ ਹੈ। - u_blinking_led ਉਦਾਹਰਨ ਲਈ ਪੁਨਰ-ਸੰਰਚਨਾਯੋਗ ਡਿਜ਼ਾਈਨ ਭਾਗ ਨਿਰਧਾਰਤ ਕਰਨ ਲਈ ਕਦਮ 1 ਅਤੇ 2 ਨੂੰ ਦੁਹਰਾਓ। ਇਸ ਭਾਗ ਨੂੰ pr_parent_partition ਦਾ ਨਾਂ ਦਿਓ।

ਤਸਦੀਕ ਕਰੋ ਕਿ blinking_led.qsf ਵਿੱਚ ਤੁਹਾਡੇ ਪੁਨਰ-ਸੰਰਚਨਾਯੋਗ ਡਿਜ਼ਾਈਨ ਭਾਗਾਂ ਦੇ ਅਨੁਸਾਰੀ ਹੇਠ ਦਿੱਤੇ ਅਸਾਈਨਮੈਂਟ ਹਨ:

ਅੰਸ਼ਕ ਮੁੜ ਸੰਰਚਨਾ ਲਈ ਡਿਜ਼ਾਈਨ ਭਾਗ ਬਣਾਓ

ਕਦਮ 4: PR ਭਾਗਾਂ ਲਈ ਪਲੇਸਮੈਂਟ ਅਤੇ ਰੂਟਿੰਗ ਖੇਤਰ ਨਿਰਧਾਰਤ ਕਰਨਾ

ਜਦੋਂ ਤੁਸੀਂ ਅਧਾਰ ਸੰਸ਼ੋਧਨ ਬਣਾਉਂਦੇ ਹੋ, ਤਾਂ PR ਡਿਜ਼ਾਇਨ ਪ੍ਰਵਾਹ ਤੁਹਾਡੇ PR ਭਾਗ ਖੇਤਰ ਦੀ ਵੰਡ ਦੀ ਵਰਤੋਂ ਰਿਜ਼ਰਵਡ ਖੇਤਰ ਵਿੱਚ ਸੰਬੰਧਿਤ ਵਿਅਕਤੀ ਕੋਰ ਨੂੰ ਰੱਖਣ ਲਈ ਕਰਦਾ ਹੈ। ਤੁਹਾਡੇ ਅਧਾਰ ਸੰਸ਼ੋਧਨ ਲਈ ਡਿਵਾਈਸ ਫਲੋਰ ਪਲਾਨ ਵਿੱਚ PR ਖੇਤਰ ਨੂੰ ਲੱਭਣ ਅਤੇ ਨਿਰਧਾਰਤ ਕਰਨ ਲਈ:

- ਪ੍ਰੋਜੈਕਟ ਨੈਵੀਗੇਟਰ ਵਿੱਚ u_blinking_led_child ਉਦਾਹਰਨ ਉੱਤੇ ਸੱਜਾ-ਕਲਿੱਕ ਕਰੋ ਅਤੇ Logic Lock Region ➤ ਨਵਾਂ Logic Lock Region ਬਣਾਓ। ਖੇਤਰ Logic Lock Regions ਵਿੰਡੋ 'ਤੇ ਦਿਖਾਈ ਦਿੰਦਾ ਹੈ।

- ਤੁਹਾਡੇ ਪਲੇਸਮੈਂਟ ਖੇਤਰ ਵਿੱਚ blinking_led_child ਤਰਕ ਸ਼ਾਮਲ ਹੋਣਾ ਚਾਹੀਦਾ ਹੈ। ਚਿੱਪ ਪਲੈਨਰ ਵਿੱਚ ਨੋਡ ਦਾ ਪਤਾ ਲਗਾ ਕੇ ਪਲੇਸਮੈਂਟ ਖੇਤਰ ਦੀ ਚੋਣ ਕਰੋ। ਪ੍ਰੋਜੈਕਟ ਨੈਵੀਗੇਟਰ ਵਿੱਚ u_blinking_led_child ਖੇਤਰ ਦੇ ਨਾਮ ਉੱਤੇ ਸੱਜਾ-ਕਲਿੱਕ ਕਰੋ ਅਤੇ Locate Node ➤ Locate in Chip Planner ਉੱਤੇ ਕਲਿਕ ਕਰੋ।

ਚਿੱਤਰ 5. blinking_led ਲਈ ਚਿੱਪ ਪਲੈਨਰ ਨੋਡ ਟਿਕਾਣਾ

- ਤਰਕ ਲੌਕ ਖੇਤਰ ਵਿੰਡੋ ਵਿੱਚ, ਮੂਲ ਕਾਲਮ ਵਿੱਚ ਪਲੇਸਮੈਂਟ ਖੇਤਰ ਦੇ ਨਿਰਦੇਸ਼ਾਂਕ ਨੂੰ ਨਿਸ਼ਚਿਤ ਕਰੋ। ਮੂਲ ਖੇਤਰ ਦੇ ਹੇਠਲੇ-ਖੱਬੇ ਕੋਨੇ ਨਾਲ ਮੇਲ ਖਾਂਦਾ ਹੈ। ਸਾਬਕਾ ਲਈample, (X1 Y1) ਕੋਆਰਡੀਨੇਟਸ (69 10) ਦੇ ਨਾਲ ਇੱਕ ਪਲੇਸਮੈਂਟ ਖੇਤਰ ਨੂੰ ਸੈੱਟ ਕਰਨ ਲਈ, X69_Y10 ਦੇ ਤੌਰ 'ਤੇ ਮੂਲ ਨਿਸ਼ਚਿਤ ਕਰੋ। Intel Quartus Prime ਸਾਫਟਵੇਅਰ ਤੁਹਾਡੇ ਦੁਆਰਾ ਨਿਰਧਾਰਿਤ ਉਚਾਈ ਅਤੇ ਚੌੜਾਈ ਦੇ ਆਧਾਰ 'ਤੇ ਪਲੇਸਮੈਂਟ ਖੇਤਰ ਲਈ (X2 Y2) ਕੋਆਰਡੀਨੇਟਸ (ਉੱਪਰ-ਸੱਜੇ) ਦੀ ਗਣਨਾ ਕਰਦਾ ਹੈ।

ਨੋਟ: ਇਹ ਟਿਊਟੋਰਿਅਲ ਪਲੇਸਮੈਂਟ ਖੇਤਰ ਲਈ (X1 Y1) ਕੋਆਰਡੀਨੇਟਸ - (69 10), ਅਤੇ 20 ਦੀ ਉਚਾਈ ਅਤੇ ਚੌੜਾਈ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ। ਪਲੇਸਮੈਂਟ ਖੇਤਰ ਲਈ ਕਿਸੇ ਵੀ ਮੁੱਲ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰੋ, ਬਸ਼ਰਤੇ ਕਿ ਖੇਤਰ blinking_led_child ਤਰਕ ਨੂੰ ਕਵਰ ਕਰਦਾ ਹੈ। - ਰਿਜ਼ਰਵਡ ਅਤੇ ਕੋਰ-ਓਨਲੀ ਵਿਕਲਪਾਂ ਨੂੰ ਸਮਰੱਥ ਬਣਾਓ।

- ਰੂਟਿੰਗ ਖੇਤਰ ਵਿਕਲਪ 'ਤੇ ਦੋ ਵਾਰ ਕਲਿੱਕ ਕਰੋ। ਲਾਜਿਕ ਲਾਕ ਰੂਟਿੰਗ ਰੀਜਨ ਸੈਟਿੰਗਜ਼ ਡਾਇਲਾਗ ਬਾਕਸ ਦਿਖਾਈ ਦਿੰਦਾ ਹੈ।

- ਰਾਊਟਿੰਗ ਕਿਸਮ ਲਈ ਵਿਸਤਾਰ ਨਾਲ ਸਥਿਰ ਚੁਣੋ। ਇਸ ਵਿਕਲਪ ਨੂੰ ਚੁਣਨਾ ਆਪਣੇ ਆਪ 1 ਦੀ ਵਿਸਤਾਰ ਲੰਬਾਈ ਨਿਰਧਾਰਤ ਕਰਦਾ ਹੈ।

ਨੋਟ: ਜਦੋਂ ਇੰਜਣ ਵੱਖ-ਵੱਖ ਵਿਅਕਤੀਆਂ ਨੂੰ ਰੂਟ ਕਰਦਾ ਹੈ ਤਾਂ ਫਿਟਰ ਲਈ ਵਾਧੂ ਲਚਕਤਾ ਪ੍ਰਦਾਨ ਕਰਨ ਲਈ ਰੂਟਿੰਗ ਖੇਤਰ ਪਲੇਸਮੈਂਟ ਖੇਤਰ ਤੋਂ ਵੱਡਾ ਹੋਣਾ ਚਾਹੀਦਾ ਹੈ। - u_blinking_led ਉਦਾਹਰਨ ਲਈ ਕਦਮ 1 -6 ਨੂੰ ਦੁਹਰਾਓ। ਪੇਰੈਂਟ-ਲੈਵਲ ਪਲੇਸਮੈਂਟ u_blinking_led ਉਦਾਹਰਨ ਲਈ ਕਦਮ 1 -6 ਨੂੰ ਦੁਹਰਾਓ। ਮਾਤਾ-ਪਿਤਾ-ਪੱਧਰ ਦੀ ਪਲੇਸਮੈਂਟ ਖੇਤਰ ਨੂੰ ਮਾਤਾ-ਪਿਤਾ-ਪੱਧਰ ਦੀ ਤਰਕ ਪਲੇਸਮੈਂਟ ਲਈ ਲੋੜੀਂਦੀ ਥਾਂ ਦੀ ਇਜਾਜ਼ਤ ਦਿੰਦੇ ਹੋਏ, ਅਨੁਸਾਰੀ ਬਾਲ-ਪੱਧਰੀ ਪਲੇਸਮੈਂਟ ਅਤੇ ਰੂਟਿੰਗ ਖੇਤਰਾਂ ਨੂੰ ਪੂਰੀ ਤਰ੍ਹਾਂ ਨਾਲ ਨੱਥੀ ਕਰਨਾ ਚਾਹੀਦਾ ਹੈ। ਇਹ ਟਿਊਟੋਰਿਅਲ u_blinking_led ਉਦਾਹਰਨ ਦੇ ਪਲੇਸਮੈਂਟ ਖੇਤਰ ਲਈ (X1 Y1) ਕੋਆਰਡੀਨੇਟਸ - (66 7), 47 ਦੀ ਉਚਾਈ, ਅਤੇ 26 ਦੀ ਚੌੜਾਈ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ।

ਚਿੱਤਰ 6. ਤਰਕ ਲਾਕ ਖੇਤਰ ਵਿੰਡੋ

ਤਸਦੀਕ ਕਰੋ ਕਿ blinking_led.qsf ਵਿੱਚ ਤੁਹਾਡੀ ਫਲੋਰ ਪਲੈਨਿੰਗ ਦੇ ਅਨੁਸਾਰੀ ਨਿਮਨਲਿਖਤ ਅਸਾਈਨਮੈਂਟ ਹਨ:

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਡਿਜ਼ਾਈਨ ਦੀ ਫਲੋਰ ਪਲਾਨ

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਨੂੰ ਲਗਾਤਾਰ ਲਾਗੂ ਕਰਨਾ

ਕਦਮ 5: Intel Arria 10 ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਕੰਟਰੋਲਰ IP ਕੋਰ ਨੂੰ ਜੋੜਨਾ

- PR ਭਾਗ ਨੂੰ ਮੁੜ ਸੰਰਚਿਤ ਕਰਨ ਲਈ Intel Arria 10 ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਕੰਟਰੋਲਰ IP ਕੋਰ ਦੀ ਵਰਤੋਂ ਕਰੋ। ਇਹ IP ਕੋਰ ਜੇTAG PR ਭਾਗ ਨੂੰ ਮੁੜ ਸੰਰਚਿਤ ਕਰਨ ਲਈ। ਤੁਹਾਡੇ Intel Quartus Prime ਪ੍ਰੋਜੈਕਟ ਵਿੱਚ Intel Arria 10 ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਕੰਟਰੋਲਰ IP ਕੋਰ ਨੂੰ ਜੋੜਨ ਲਈ:

- IP ਕੈਟਾਲਾਗ ਵਿੱਚ ਅਧੂਰਾ ਰੀਕਨਫਿਗਰੇਸ਼ਨ ਟਾਈਪ ਕਰੋ।

- IP ਪੈਰਾਮੀਟਰ ਐਡੀਟਰ ਪ੍ਰੋ ਵਿੰਡੋ ਨੂੰ ਸ਼ੁਰੂ ਕਰਨ ਲਈ, IP ਲਾਇਬ੍ਰੇਰੀ ਤੋਂ Intel Arria 10 ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਕੰਟਰੋਲਰ IP ਕੋਰ ਦੀ ਚੋਣ ਕਰੋ, ਅਤੇ ਐਡ 'ਤੇ ਕਲਿੱਕ ਕਰੋ।

- ਨਵੇਂ IP ਵੇਰੀਐਂਟ ਡਾਇਲਾਗ ਬਾਕਸ ਵਿੱਚ, pr_ip ਟਾਈਪ ਕਰੋ file ਨਾਮ ਅਤੇ ਬਣਾਓ 'ਤੇ ਕਲਿੱਕ ਕਰੋ। pr_ip ਲਈ ਡਿਫੌਲਟ ਪੈਰਾਮੀਟਰਾਈਜ਼ੇਸ਼ਨ ਦੀ ਵਰਤੋਂ ਕਰੋ। ਯਕੀਨੀ ਬਣਾਓ ਕਿ ਯੋਗ ਜੇTAG ਡੀਬੱਗ ਮੋਡ ਅਤੇ ਇਨੇਬਲ ਫ੍ਰੀਜ਼ ਇੰਟਰਫੇਸ ਵਿਕਲਪ ਚਾਲੂ ਹਨ, ਅਤੇ Avalon-MM ਸਲੇਵ ਇੰਟਰਫੇਸ ਵਿਕਲਪ ਨੂੰ ਸਮਰੱਥ ਕਰੋ ਬੰਦ ਹੈ।

ਚਿੱਤਰ 7. Intel Arria 10 ਅੰਸ਼ਕ ਮੁੜ ਸੰਰਚਨਾ ਕੰਟਰੋਲਰ IP ਕੋਰ ਪੈਰਾਮੀਟਰ

- ਫਿਨਿਸ਼ 'ਤੇ ਕਲਿੱਕ ਕਰੋ, ਅਤੇ ਸਿਸਟਮ ਤਿਆਰ ਕੀਤੇ ਬਿਨਾਂ ਪੈਰਾਮੀਟਰ ਐਡੀਟਰ ਤੋਂ ਬਾਹਰ ਜਾਓ। Intel Quartus Prime ਸਾਫਟਵੇਅਰ pr_ip.ip IP ਪਰਿਵਰਤਨ ਬਣਾਉਂਦਾ ਹੈ file, ਅਤੇ ਜੋੜਦਾ ਹੈ file blinking_led ਪ੍ਰੋਜੈਕਟ ਲਈ।

ਨੋਟ:

- ਜੇਕਰ ਤੁਸੀਂ pr_ip.ip ਦੀ ਨਕਲ ਕਰ ਰਹੇ ਹੋ file hpr ਫੋਲਡਰ ਤੋਂ, blinking_led.qsf ਨੂੰ ਹੱਥੀਂ ਸੰਪਾਦਿਤ ਕਰੋ file ਹੇਠ ਦਿੱਤੀ ਲਾਈਨ ਨੂੰ ਸ਼ਾਮਲ ਕਰਨ ਲਈ: set_global_assignment -name IP_FILE pr_ip.ip

- IP_ ਰੱਖੋFILE SDC_ ਦੇ ਬਾਅਦ ਅਸਾਈਨਮੈਂਟFILE ਅਸਾਈਨਮੈਂਟ (ਜੇtagਤੁਹਾਡੇ blinking_led.qsf ਵਿੱਚ .sdc ਅਤੇ blinking_led.sdc) file. ਇਹ ਆਰਡਰਿੰਗ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ IP ਕੋਰ ਦੀ ਢੁਕਵੀਂ ਰੁਕਾਵਟ ਨੂੰ ਯਕੀਨੀ ਬਣਾਉਂਦਾ ਹੈ।

ਨੋਟ: ਘੜੀਆਂ ਦਾ ਪਤਾ ਲਗਾਉਣ ਲਈ ਐਸ.ਡੀ.ਸੀ file PR IP ਲਈ ਕਿਸੇ ਵੀ SDC ਦੀ ਪਾਲਣਾ ਕਰਨੀ ਚਾਹੀਦੀ ਹੈ ਜੋ ਉਹ ਘੜੀਆਂ ਬਣਾਉਂਦਾ ਹੈ ਜੋ IP ਕੋਰ ਵਰਤਦਾ ਹੈ। ਤੁਸੀਂ .ip ਨੂੰ ਯਕੀਨੀ ਬਣਾ ਕੇ ਇਸ ਆਰਡਰ ਦੀ ਸਹੂਲਤ ਦਿੰਦੇ ਹੋ file PR IP ਕੋਰ ਲਈ ਕਿਸੇ ਵੀ .ip ਤੋਂ ਬਾਅਦ ਆਉਂਦਾ ਹੈ files ਜਾਂ SDC files ਦੀ ਵਰਤੋਂ QSF ਵਿੱਚ ਇਹਨਾਂ ਘੜੀਆਂ ਨੂੰ ਬਣਾਉਣ ਲਈ ਕੀਤੀ ਜਾਂਦੀ ਹੈ file ਤੁਹਾਡੇ Intel Quartus Prime ਪ੍ਰੋਜੈਕਟ ਦੇ ਸੰਸ਼ੋਧਨ ਲਈ। ਵਧੇਰੇ ਜਾਣਕਾਰੀ ਲਈ, ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ IP ਕੋਰ ਉਪਭੋਗਤਾ ਗਾਈਡ ਵਿੱਚ ਟਾਈਮਿੰਗ ਸੀਮਾਵਾਂ ਭਾਗ ਵੇਖੋ।

ਸੰਬੰਧਿਤ ਜਾਣਕਾਰੀ

- ਅੰਸ਼ਕ ਮੁੜ ਸੰਰਚਨਾ IP ਹੱਲ ਯੂਜ਼ਰ ਗਾਈਡ

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਖੇਤਰ ਕੰਟਰੋਲਰ IP ਕੋਰ ਬਾਰੇ ਜਾਣਕਾਰੀ ਲਈ।

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ IP ਕੋਰ ਉਪਭੋਗਤਾ ਗਾਈਡ

- ਸਮੇਂ ਦੀਆਂ ਕਮੀਆਂ ਬਾਰੇ ਜਾਣਕਾਰੀ ਲਈ।

ਸਿਖਰ-ਪੱਧਰ ਦੇ ਡਿਜ਼ਾਈਨ ਨੂੰ ਅੱਪਡੇਟ ਕਰਨਾ

ਅੱਪਡੇਟ ਕਰਨ ਲਈ top.SV file PR_IP ਉਦਾਹਰਨ ਦੇ ਨਾਲ:

- PR_IP ਉਦਾਹਰਨ ਨੂੰ ਸਿਖਰ-ਪੱਧਰ ਦੇ ਡਿਜ਼ਾਈਨ ਵਿੱਚ ਜੋੜਨ ਲਈ, ਸਿਖਰ 'ਤੇ ਹੇਠਾਂ ਦਿੱਤੇ ਕੋਡ ਬਲਾਕ ਨੂੰ ਅਨਕਮੈਂਟ ਕਰੋ। file:

- ਪੁਨਰ-ਸੰਰਚਨਾ ਦੌਰਾਨ ਆਉਟਪੁੱਟ ਪੋਰਟਾਂ ਨੂੰ ਤਰਕ 1 ਲਈ ਮਜਬੂਰ ਕਰਨ ਲਈ, PR_IP ਤੋਂ ਫ੍ਰੀਜ਼ ਕੰਟਰੋਲ ਸਿਗਨਲ ਆਉਟਪੁੱਟ ਦੀ ਵਰਤੋਂ ਕਰੋ। ਹਾਲਾਂਕਿ, ਚਾਈਲਡ ਪਾਰਟੀਸ਼ਨ ਨੂੰ PR ਪ੍ਰੋਗਰਾਮਿੰਗ ਕਰਦੇ ਸਮੇਂ LED ਨੂੰ ਪੇਰੈਂਟ PR ਭਾਗ ਤੋਂ ਝਪਕਣਾ ਜਾਰੀ ਰੱਖਣ ਲਈ, ਫ੍ਰੀਜ਼ ਕੰਟਰੋਲ ਸਿਗਨਲ led_two_on ਨੂੰ ਬੰਦ ਨਹੀਂ ਕਰਦਾ ਹੈ। ਯਕੀਨੀ ਬਣਾਓ ਕਿ pr_led_two_on ਸਿੱਧਾ ਹੈ

- ਪੂਰਵ-ਨਿਰਧਾਰਤ ਪੇਰੈਂਟ ਸ਼ਖਸੀਅਤ (ਬਲਿੰਕਿੰਗ_ਲੀਡ) ਦੀ ਇੱਕ ਉਦਾਹਰਨ ਦੇਣ ਲਈ, ਸਿਖਰ ਨੂੰ ਅੱਪਡੇਟ ਕਰੋ।SV file ਕੋਡ ਦੇ ਹੇਠ ਦਿੱਤੇ ਬਲਾਕ ਦੇ ਨਾਲ:

ਚਿੱਤਰ 8. ਅੰਸ਼ਕ ਮੁੜ ਸੰਰਚਨਾ IP ਕੋਰ ਏਕੀਕਰਣ

ਕਦਮ 6: ਵਿਅਕਤੀਆਂ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਨਾ

ਇਹ ਸੰਦਰਭ ਡਿਜ਼ਾਈਨ ਮਾਤਾ-ਪਿਤਾ ਅਤੇ ਬੱਚੇ ਦੇ PR ਭਾਗਾਂ ਲਈ ਪੰਜ ਵੱਖਰੇ ਵਿਅਕਤੀਆਂ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਦਾ ਹੈ। ਆਪਣੇ ਪ੍ਰੋਜੈਕਟ ਵਿੱਚ ਵਿਅਕਤੀਆਂ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਨ ਅਤੇ ਸ਼ਾਮਲ ਕਰਨ ਲਈ:

- ਚਾਰ SystemVerilog ਬਣਾਓ fileਪੰਜ ਵਿਅਕਤੀਆਂ ਲਈ ਤੁਹਾਡੀ ਕਾਰਜਕਾਰੀ ਡਾਇਰੈਕਟਰੀ ਵਿੱਚ s, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv, ਅਤੇ blinking_led_slow.sv।

ਨੋਟ: ਜੇਕਰ ਤੁਸੀਂ SystemVerilog ਬਣਾਉਂਦੇ ਹੋ files Intel Quartus Prime Text Editor ਤੋਂ, Add ਨੂੰ ਅਯੋਗ ਕਰੋ file ਮੌਜੂਦਾ ਪ੍ਰੋਜੈਕਟ ਵਿਕਲਪ ਲਈ, ਨੂੰ ਸੰਭਾਲਣ ਵੇਲੇ files.

ਸਾਰਣੀ 2. ਸੰਦਰਭ ਡਿਜ਼ਾਈਨ ਵਿਅਕਤੀ

| File ਨਾਮ | ਵਰਣਨ | ਕੋਡ |

| blinking_led_child.sv | ਬਾਲ-ਪੱਧਰ ਦੇ ਡਿਜ਼ਾਈਨ ਲਈ ਪੂਰਵ-ਨਿਰਧਾਰਤ ਸ਼ਖਸੀਅਤ |

`ਟਾਈਮ ਸਕੇਲ 1 ps / 1 ps `default_nettype none ਮੋਡੀਊਲ blinking_led_child ( // ਘੜੀ ਇਨਪੁਟ ਤਾਰ ਘੜੀ, ਇਨਪੁਟ ਵਾਇਰ [31:0] ਕਾਊਂਟਰ,

// LEDs ਆਉਟਪੁੱਟ ਤਾਰ ਲਈ ਕੰਟਰੋਲ ਸਿਗਨਲ led_three_on

); ਸਥਾਨਕਪਰਮ COUNTER_TAP = 23; reg led_three_on_r;

ਅਸਾਈਨ led_three_on = led_three_on_r; always_ff @(ਪੋਜ਼ੇਜ ਕਲਾਕ) ਸ਼ੁਰੂ led_three_on_r <= counter[COUNTER_TAP]; ਅੰਤ

endmodule |

| ਜਾਰੀ… | ||

| File ਨਾਮ | ਵਰਣਨ | ਕੋਡ |

| blinking_led_child_slow.sv | ਦ

LED_THREE ਹੌਲੀ ਝਪਕਦਾ ਹੈ |

`ਟਾਈਮ ਸਕੇਲ 1 ps / 1 ps `default_nettype ਕੋਈ ਨਹੀਂ

ਮੋਡੀਊਲ blinking_led_child_slow (

// ਘੜੀ ਇਨਪੁਟ ਤਾਰ ਘੜੀ, ਇਨਪੁਟ ਵਾਇਰ [31:0] ਕਾਊਂਟਰ,

// LEDs ਆਉਟਪੁੱਟ ਤਾਰ ਲਈ ਕੰਟਰੋਲ ਸਿਗਨਲ led_three_on );

ਸਥਾਨਕਪਰਮ COUNTER_TAP = 27; reg led_three_on_r;

ਅਸਾਈਨ led_three_on = led_three_on_r; always_ff @(ਪੋਜ਼ੇਜ ਕਲਾਕ) ਸ਼ੁਰੂ led_three_on_r <= counter[COUNTER_TAP]; ਅੰਤ

endmodule |

| blinking_led_child_empty.sv | ਦ

LED_THREE ਚਾਲੂ ਰਹਿੰਦਾ ਹੈ |

`ਟਾਈਮ ਸਕੇਲ 1 ps / 1 ps `default_nettype ਕੋਈ ਨਹੀਂ

ਮੋਡੀਊਲ blinking_led_child_empty (

// ਘੜੀ ਇਨਪੁਟ ਤਾਰ ਘੜੀ, ਇਨਪੁਟ ਵਾਇਰ [31:0] ਕਾਊਂਟਰ,

// LEDs ਆਉਟਪੁੱਟ ਤਾਰ ਲਈ ਕੰਟਰੋਲ ਸਿਗਨਲ led_three_on

);

// LED ਸਰਗਰਮ ਘੱਟ ਹੈ led_three_on = 1'b0 ਨਿਰਧਾਰਤ ਕਰੋ;

endmodule |

| blinking_led_slow.sv | LED_TWO

ਹੌਲੀ ਝਪਕਦਾ ਹੈ। |

`ਟਾਈਮ ਸਕੇਲ 1 ps / 1 ps `default_nettype none ਮੋਡੀਊਲ blinking_led_slow( // ਘੜੀ ਇਨਪੁਟ ਤਾਰ ਘੜੀ, ਇਨਪੁਟ ਵਾਇਰ [31:0] ਕਾਊਂਟਰ,

// LEDs ਆਉਟਪੁੱਟ ਤਾਰ ਲਈ ਕੰਟਰੋਲ ਸਿਗਨਲ led_two_on, ਆਉਟਪੁੱਟ ਤਾਰ led_three_on

);

ਸਥਾਨਕਪਰਮ COUNTER_TAP = 27; reg led_two_on_r; ਅਸਾਈਨ led_two_on = led_two_on_r;

// ਕਾਊਂਟਰ: always_ff @(posdge clock) start led_two_on_r <= counter[COUNTER_TAP]; ਅੰਤ

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .counter (ਕਾਊਂਟਰ), .clock (ਘੜੀ) |

| File ਨਾਮ | ਵਰਣਨ | ਕੋਡ |

| );ndmodule |

ਕਦਮ 3: ਸਫ਼ਾ 7 'ਤੇ ਡਿਜ਼ਾਈਨ ਭਾਗ ਬਣਾਉਣਾ

ਕਦਮ 7: ਸੰਸ਼ੋਧਨ ਬਣਾਉਣਾ

PR ਡਿਜ਼ਾਈਨ ਪ੍ਰਵਾਹ ਇੰਟੇਲ ਕੁਆਰਟਸ ਪ੍ਰਾਈਮ ਸੌਫਟਵੇਅਰ ਵਿੱਚ ਪ੍ਰੋਜੈਕਟ ਸੰਸ਼ੋਧਨ ਵਿਸ਼ੇਸ਼ਤਾ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ। ਤੁਹਾਡਾ ਸ਼ੁਰੂਆਤੀ ਡਿਜ਼ਾਈਨ ਬੇਸ ਰੀਵਿਜ਼ਨ ਹੈ, ਜਿੱਥੇ ਤੁਸੀਂ FPGA 'ਤੇ ਸਥਿਰ ਖੇਤਰ ਦੀਆਂ ਸੀਮਾਵਾਂ ਅਤੇ ਮੁੜ ਸੰਰਚਨਾਯੋਗ ਖੇਤਰਾਂ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਦੇ ਹੋ। ਅਧਾਰ ਸੰਸ਼ੋਧਨ ਤੋਂ, ਤੁਸੀਂ ਕਈ ਸੰਸ਼ੋਧਨ ਬਣਾਉਂਦੇ ਹੋ। ਇਹਨਾਂ ਸੰਸ਼ੋਧਨਾਂ ਵਿੱਚ PR ਖੇਤਰਾਂ ਲਈ ਵੱਖ-ਵੱਖ ਲਾਗੂਕਰਨ ਸ਼ਾਮਲ ਹਨ। ਹਾਲਾਂਕਿ, ਸਾਰੇ PR ਲਾਗੂਕਰਨ ਸੰਸ਼ੋਧਨ ਅਧਾਰ ਸੰਸ਼ੋਧਨ ਤੋਂ ਇੱਕੋ ਉੱਚ-ਪੱਧਰੀ ਪਲੇਸਮੈਂਟ ਅਤੇ ਰੂਟਿੰਗ ਨਤੀਜਿਆਂ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹਨ। ਇੱਕ PR ਡਿਜ਼ਾਈਨ ਨੂੰ ਕੰਪਾਇਲ ਕਰਨ ਲਈ, ਤੁਹਾਨੂੰ ਹਰੇਕ ਵਿਅਕਤੀ ਲਈ ਇੱਕ PR ਲਾਗੂਕਰਨ ਸੰਸ਼ੋਧਨ ਅਤੇ ਸੰਸ਼ਲੇਸ਼ਣ ਸੰਸ਼ੋਧਨ ਬਣਾਉਣਾ ਚਾਹੀਦਾ ਹੈ। ਇਸ ਸੰਦਰਭ ਡਿਜ਼ਾਈਨ ਵਿੱਚ, ਅਧਾਰ ਸੰਸ਼ੋਧਨ (ਬਲਿੰਕਿੰਗ_ਲੀਡ) ਤੋਂ ਇਲਾਵਾ, ਤਿੰਨ ਬਾਲ-ਪੱਧਰੀ ਵਿਅਕਤੀਆਂ ਅਤੇ ਦੋ ਮਾਤਾ-ਪਿਤਾ-ਪੱਧਰ ਦੇ ਵਿਅਕਤੀਆਂ ਵਿੱਚ ਪੰਜ ਵੱਖਰੇ ਸੰਸ਼ਲੇਸ਼ਣ ਸੰਸ਼ੋਧਨ ਅਤੇ ਪੰਜ ਵੱਖਰੇ ਲਾਗੂ ਸੰਸ਼ੋਧਨ ਸ਼ਾਮਲ ਹਨ:

ਸਾਰਣੀ 3. ਦੋ-ਮਾਪਿਆਂ ਦੇ ਵਿਅਕਤੀਆਂ ਅਤੇ ਤਿੰਨ-ਬੱਚਿਆਂ ਦੇ ਵਿਅਕਤੀਆਂ ਲਈ ਸੰਸ਼ੋਧਨ

| ਸੰਸਲੇਸ਼ਣ ਸੰਸ਼ੋਧਨ | ਲਾਗੂ ਸੰਸ਼ੋਧਨ |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_empty | blinking_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | blinking_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_empty | blinking_led_pr_emma |

ਲਾਗੂ ਸੰਸ਼ੋਧਨ ਬਣਾਉਣਾ

PR ਲਾਗੂਕਰਨ ਸੋਧਾਂ ਨੂੰ ਬਣਾਉਣ ਲਈ:

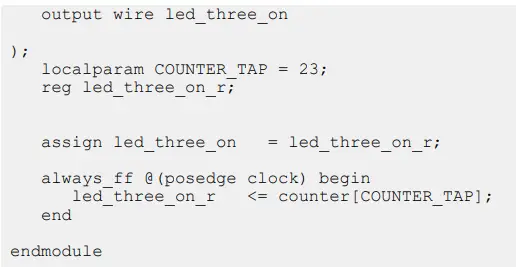

- ਸੰਸ਼ੋਧਨ ਡਾਇਲਾਗ ਬਾਕਸ ਨੂੰ ਖੋਲ੍ਹਣ ਲਈ, ਪ੍ਰੋਜੈਕਟ ➤ ਸੰਸ਼ੋਧਨ 'ਤੇ ਕਲਿੱਕ ਕਰੋ।

- ਇੱਕ ਨਵਾਂ ਸੰਸ਼ੋਧਨ ਬਣਾਉਣ ਲਈ, < 'ਤੇ ਦੋ ਵਾਰ ਕਲਿੱਕ ਕਰੋ >।

- ਸੰਸ਼ੋਧਨ ਨਾਮ ਨੂੰ blinking_led_pr_alpha ਦੇ ਤੌਰ ਤੇ ਦਿਓ ਅਤੇ ਸੰਸ਼ੋਧਨ ਦੇ ਅਧਾਰ ਤੇ ਲਈ blinking_led ਦੀ ਚੋਣ ਕਰੋ।

- ਮੌਜੂਦਾ ਸੰਸ਼ੋਧਨ ਵਿਕਲਪ ਵਜੋਂ ਸੈੱਟ ਨੂੰ ਅਸਮਰੱਥ ਕਰੋ ਅਤੇ ਠੀਕ ਹੈ 'ਤੇ ਕਲਿੱਕ ਕਰੋ।

- ਇਸੇ ਤਰ੍ਹਾਂ, blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta, ਅਤੇ blinking_led_pr_emma ਸੰਸ਼ੋਧਨ, ਬਲਿੰਕਿੰਗ_led ਸੰਸ਼ੋਧਨ ਦੇ ਅਧਾਰ ਤੇ ਬਣਾਓ।

ਨੋਟ: ਉਪਰੋਕਤ ਸੰਸ਼ੋਧਨਾਂ ਨੂੰ ਮੌਜੂਦਾ ਸੰਸ਼ੋਧਨ ਦੇ ਤੌਰ ਤੇ ਸੈਟ ਨਾ ਕਰੋ।

ਚਿੱਤਰ 9. ਸੰਸ਼ੋਧਨ ਬਣਾਉਣਾ

ਸਿੰਥੇਸਿਸ-ਸਿਰਫ ਸੰਸ਼ੋਧਨ ਬਣਾਉਣਾ

ਵਿਅਕਤੀਆਂ ਲਈ ਸੰਸ਼ਲੇਸ਼ਣ-ਸਿਰਫ਼ ਸੰਸ਼ੋਧਨ ਬਣਾਉਣ ਲਈ, ਤੁਹਾਨੂੰ ਉੱਚ-ਪੱਧਰੀ ਇਕਾਈ ਅਤੇ ਸੰਬੰਧਿਤ ਸਿਸਟਮਵੇਰੀਲੌਗ ਨੂੰ ਨਿਰਧਾਰਤ ਕਰਨਾ ਚਾਹੀਦਾ ਹੈ file ਹਰੇਕ ਵਿਅਕਤੀ ਲਈ:

- Intel Quartus Prime ਸਾਫਟਵੇਅਰ ਵਿੱਚ, Project ➤ Revisions 'ਤੇ ਕਲਿੱਕ ਕਰੋ।

- blinking_led_default ਸੰਸ਼ੋਧਨ blinking_led ਸੰਸ਼ੋਧਨ ਦੇ ਅਧਾਰ ਤੇ ਬਣਾਓ। ਇਸ ਸੰਸ਼ੋਧਨ ਨੂੰ ਮੌਜੂਦਾ ਸੰਸ਼ੋਧਨ ਵਜੋਂ ਸੈਟ ਨਾ ਕਰੋ।

- blinking_led_default.qsf ਨੂੰ ਸੋਧੋ file ਹੇਠ ਲਿਖੇ ਕਾਰਜਾਂ ਨੂੰ ਸ਼ਾਮਲ ਕਰਨ ਲਈ:

set_global_assignment -name TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -ਨਾਮ SYSTEMVERILOG_FILE - ਇਸੇ ਤਰ੍ਹਾਂ, blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent, ਅਤੇ blinking_led_parent_slow ਸੰਸ਼ੋਧਨ blinking_led ਸੰਸ਼ੋਧਨ ਦੇ ਅਧਾਰ ਤੇ ਬਣਾਓ। ਇਹਨਾਂ ਸੰਸ਼ੋਧਨਾਂ ਨੂੰ ਮੌਜੂਦਾ ਸੰਸ਼ੋਧਨਾਂ ਵਜੋਂ ਸੈਟ ਨਾ ਕਰੋ।

- blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, ਅਤੇ blinking_led_parent_slow.qsf ਨੂੰ ਅੱਪਡੇਟ ਕਰੋ files ਉਹਨਾਂ ਦੇ ਅਨੁਸਾਰੀ ਨਾਲ

TOP_LEVEL_ENTITY ਅਤੇ SYSTEMVERILOG_FILE ਅਸਾਈਨਮੈਂਟ:

- ਸੰਸਲੇਸ਼ਣ ਦੀਆਂ ਗਲਤੀਆਂ ਤੋਂ ਬਚਣ ਲਈ, ਇਹ ਯਕੀਨੀ ਬਣਾਓ ਕਿ ਸੰਸਲੇਸ਼ਣ ਸੰਸ਼ੋਧਨ fileਚਾਈਲਡ ਭਾਗਾਂ ਲਈ s ਵਿੱਚ ਕੋਈ ਡਿਜ਼ਾਇਨ ਭਾਗ, ਪਿੰਨ ਅਸਾਈਨਮੈਂਟ, ਜਾਂ ਲਾਜਿਕ ਲਾਕ ਸ਼ਾਮਲ ਨਹੀਂ ਹੈ

ਖੇਤਰ ਅਸਾਈਨਮੈਂਟ ਨਾਲ ਹੀ, ਸੰਸਲੇਸ਼ਣ ਸੰਸ਼ੋਧਨ fileਪੇਰੈਂਟ ਭਾਗਾਂ ਲਈ s ਵਿੱਚ ਸਿਰਫ਼ ਸੰਬੰਧਿਤ ਚਾਈਲਡ ਭਾਗਾਂ ਲਈ ਡਿਜ਼ਾਈਨ ਭਾਗ ਅਸਾਈਨਮੈਂਟ ਹੋਣੇ ਚਾਹੀਦੇ ਹਨ। blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, ਅਤੇ blinking_led_parent_slow.pdf ਵਿੱਚ, ਇਹਨਾਂ ਅਸਾਈਨਮੈਂਟਾਂ ਨੂੰ ਹਟਾਓ। files

- blinking_led_parent.qsf ਅਤੇ blinking_led_parent_slow.qsf ਵਿੱਚ ਹੇਠਾਂ ਦਿੱਤੀਆਂ ਅਸਾਈਨਮੈਂਟਾਂ ਨੂੰ ਸ਼ਾਮਲ ਕਰੋ files:

- ਪੁਸ਼ਟੀ ਕਰੋ ਕਿ blinking_led.qpf file ਹੇਠ ਲਿਖੇ ਸੰਸ਼ੋਧਨ ਸ਼ਾਮਲ ਹਨ, ਕਿਸੇ ਖਾਸ ਕ੍ਰਮ ਵਿੱਚ:

- ਨੋਟ: ਜੇਕਰ ਤੁਸੀਂ ਸੰਸ਼ੋਧਨ ਦੀ ਨਕਲ ਕਰ ਰਹੇ ਹੋ files hpr ਫੋਲਡਰ ਤੋਂ, blinking_led.qpf ਨੂੰ ਦਸਤੀ ਅਪਡੇਟ ਕਰੋ file ਕੋਡ ਦੀਆਂ ਉਪਰੋਕਤ ਲਾਈਨਾਂ ਦੇ ਨਾਲ।

ਸੰਸ਼ੋਧਨ ਦੀ ਕਿਸਮ ਨਿਰਧਾਰਤ ਕਰਨਾ

ਤੁਹਾਨੂੰ ਆਪਣੇ ਹਰੇਕ ਸੰਸ਼ੋਧਨ ਲਈ ਸੰਸ਼ੋਧਨ ਕਿਸਮ ਨਿਰਧਾਰਤ ਕਰਨੀ ਚਾਹੀਦੀ ਹੈ। ਇੱਥੇ ਤਿੰਨ ਸੰਸ਼ੋਧਨ ਕਿਸਮ ਹਨ:

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਅਧਾਰ

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਸਿੰਥੇਸਿਸ

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਲਾਗੂ ਕਰਨਾ

- ਹੇਠ ਦਿੱਤੀ ਸਾਰਣੀ ਹਰੇਕ ਸੰਸ਼ੋਧਨ ਲਈ ਸੰਸ਼ੋਧਨ-ਕਿਸਮ ਦੇ ਅਸਾਈਨਮੈਂਟਾਂ ਨੂੰ ਸੂਚੀਬੱਧ ਕਰਦੀ ਹੈ:

ਸਾਰਣੀ 4. ਸੰਸ਼ੋਧਨ ਦੀਆਂ ਕਿਸਮਾਂ

| ਸੰਸ਼ੋਧਨ ਨਾਮ | ਸੰਸ਼ੋਧਨ ਦੀ ਕਿਸਮ |

| blinking_led.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਅਧਾਰ |

| blinking_led_default.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਸਿੰਥੇਸਿਸ |

| blinking_led_child_empty.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਸਿੰਥੇਸਿਸ |

| blinking_led_child_slow.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਸਿੰਥੇਸਿਸ |

| blinking_led_parent.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਸਿੰਥੇਸਿਸ |

| blinking_led_parent_slow.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਸਿੰਥੇਸਿਸ |

| blinking_led_pr_alpha.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਲਾਗੂ ਕਰਨਾ |

| blinking_led_pr_bravo.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਲਾਗੂ ਕਰਨਾ |

| blinking_led_pr_charlie.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਲਾਗੂ ਕਰਨਾ |

| blinking_led_pr_delta.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਲਾਗੂ ਕਰਨਾ |

| blinking_led_pr_emma.qsf | ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਪਰਸੋਨਾ ਲਾਗੂ ਕਰਨਾ |

- ਪ੍ਰੋਜੈਕਟ ➤ ਸੰਸ਼ੋਧਨ 'ਤੇ ਕਲਿੱਕ ਕਰੋ। ਸੰਸ਼ੋਧਨ ਡਾਇਲਾਗ ਬਾਕਸ ਦਿਸਦਾ ਹੈ।

- ਸੰਸ਼ੋਧਨ ਨਾਮ ਕਾਲਮ ਵਿੱਚ blinking_led ਦੀ ਚੋਣ ਕਰੋ, ਅਤੇ ਮੌਜੂਦਾ ਸੈੱਟ ਕਰੋ 'ਤੇ ਕਲਿੱਕ ਕਰੋ।

- ਲਾਗੂ ਕਰੋ 'ਤੇ ਕਲਿੱਕ ਕਰੋ। blinking_led ਸੰਸ਼ੋਧਨ ਖੁੱਲ੍ਹਦਾ ਹੈ।

- blinking_led ਲਈ ਸੰਸ਼ੋਧਨ ਦੀ ਕਿਸਮ ਸੈੱਟ ਕਰਨ ਲਈ, ਅਸਾਈਨਮੈਂਟ ➤ ਸੈਟਿੰਗਾਂ ➤ ਜਨਰਲ 'ਤੇ ਕਲਿੱਕ ਕਰੋ।

- ਸੰਸ਼ੋਧਨ ਕਿਸਮ ਨੂੰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ - ਅਧਾਰ ਵਜੋਂ ਚੁਣੋ।

- ਇਸੇ ਤਰ੍ਹਾਂ, ਹੋਰ ਦਸ ਸੰਸ਼ੋਧਨਾਂ ਲਈ ਸੰਸ਼ੋਧਨ ਕਿਸਮਾਂ ਨੂੰ ਸੈੱਟ ਕਰੋ, ਜਿਵੇਂ ਕਿ ਉਪਰੋਕਤ ਸਾਰਣੀ ਵਿੱਚ ਸੂਚੀਬੱਧ ਕੀਤਾ ਗਿਆ ਹੈ।

- ਨੋਟ: ਤੁਹਾਨੂੰ ਸੰਸ਼ੋਧਨ ਕਿਸਮ ਨਿਰਧਾਰਤ ਕਰਨ ਤੋਂ ਪਹਿਲਾਂ ਹਰੇਕ ਸੰਸ਼ੋਧਨ ਨੂੰ ਮੌਜੂਦਾ ਸੰਸ਼ੋਧਨ ਦੇ ਤੌਰ 'ਤੇ ਸੈੱਟ ਕਰਨਾ ਚਾਹੀਦਾ ਹੈ। ਪੁਸ਼ਟੀ ਕਰੋ ਕਿ ਹਰੇਕ .qsf file ਹੇਠ ਦਿੱਤੀ ਅਸਾਈਨਮੈਂਟ ਸ਼ਾਮਲ ਹੈ:

- ਨੋਟ: ਕੋਈ ਵੀ ਫਿਟਰ-ਵਿਸ਼ੇਸ਼ ਸੈਟਿੰਗਾਂ ਸ਼ਾਮਲ ਕਰੋ ਜੋ ਤੁਸੀਂ PR ਲਾਗੂਕਰਨ ਕੰਪਾਈਲ ਵਿੱਚ ਵਿਅਕਤੀਗਤ ਲਾਗੂਕਰਨ ਸੰਸ਼ੋਧਨਾਂ ਵਿੱਚ ਵਰਤਣਾ ਚਾਹੁੰਦੇ ਹੋ। ਫਿਟਰ-ਵਿਸ਼ੇਸ਼ ਸੈਟਿੰਗਾਂ ਵਿਅਕਤੀ ਦੇ ਫਿੱਟ ਨੂੰ ਪ੍ਰਭਾਵਤ ਕਰਦੀਆਂ ਹਨ, ਪਰ ਆਯਾਤ ਕੀਤੇ ਸਥਿਰ ਖੇਤਰ ਨੂੰ ਪ੍ਰਭਾਵਤ ਨਹੀਂ ਕਰਦੀਆਂ ਹਨ। ਤੁਸੀਂ ਵਿਅਕਤੀਗਤ ਵਿਅਕਤੀਗਤ ਸੰਸ਼ਲੇਸ਼ਣ ਸੰਸ਼ੋਧਨਾਂ ਵਿੱਚ ਕੋਈ ਵੀ ਸੰਸ਼ਲੇਸ਼ਣ-ਵਿਸ਼ੇਸ਼ ਸੈਟਿੰਗਾਂ ਵੀ ਜੋੜ ਸਕਦੇ ਹੋ।

Personas ਲਈ ਸੰਸ਼ੋਧਨ ਬਣਾਓ

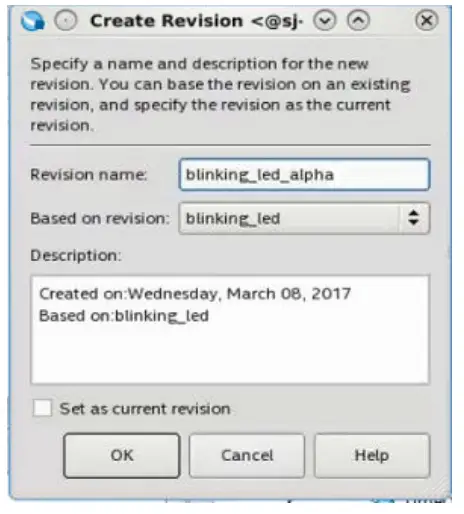

ਕਦਮ 8: ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਫਲੋ ਸਕ੍ਰਿਪਟ ਤਿਆਰ ਕਰਨਾ

ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਪ੍ਰਵਾਹ ਸਕ੍ਰਿਪਟ ਬਣਾਉਣ ਲਈ:

- Intel Quartus Prime ਕਮਾਂਡ ਸ਼ੈੱਲ ਤੋਂ, ਹੇਠ ਦਿੱਤੀ ਕਮਾਂਡ ਚਲਾ ਕੇ ਇੱਕ ਫਲੋ ਟੈਂਪਲੇਟ ਬਣਾਓ:

- Intel Quartus Prime a10_hier_partial_reconfig/flow.tcl ਤਿਆਰ ਕਰਦਾ ਹੈ file.

- ਤਿਆਰ ਕੀਤੇ a10_hier_partial_reconfig/setup.tcl.ex ਦਾ ਨਾਮ ਬਦਲੋampa10_hier_partial_reconfig/setup.tcl 'ਤੇ ਜਾਓ, ਅਤੇ ਆਪਣੇ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਪ੍ਰੋਜੈਕਟ ਵੇਰਵਿਆਂ ਨੂੰ ਨਿਸ਼ਚਿਤ ਕਰਨ ਲਈ ਸਕ੍ਰਿਪਟ ਨੂੰ ਸੋਧੋ:

a. ਪ੍ਰੋਜੈਕਟ ਦੇ ਨਾਮ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਨ ਲਈ, ਹੇਠ ਦਿੱਤੀ ਲਾਈਨ ਨੂੰ ਅੱਪਡੇਟ ਕਰੋ: b. ਬੇਸ ਰੀਵਿਜ਼ਨ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਨ ਲਈ, ਹੇਠ ਦਿੱਤੀ ਲਾਈਨ ਨੂੰ ਅੱਪਡੇਟ ਕਰੋ:

b. ਬੇਸ ਰੀਵਿਜ਼ਨ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਨ ਲਈ, ਹੇਠ ਦਿੱਤੀ ਲਾਈਨ ਨੂੰ ਅੱਪਡੇਟ ਕਰੋ:

- PR ਭਾਗ ਨਾਮ ਅਤੇ ਸੰਸ਼ੋਧਨ ਲਾਗੂ ਕਰਨ ਵਾਲੇ ਸਰੋਤ ਸੰਸ਼ੋਧਨ ਦੇ ਨਾਲ, ਹਰੇਕ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਲਾਗੂਕਰਨ ਸੰਸ਼ੋਧਨ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਨ ਲਈ, ਹੇਠ ਲਿਖੀਆਂ ਲਾਈਨਾਂ ਨੂੰ ਅੱਪਡੇਟ ਕਰੋ:

ਨੋਟ: ਸਾਰੇ ਸੰਸ਼ੋਧਨ ਪ੍ਰੋਜੈਕਟ blinking_led.qpf ਦੀ ਉਸੇ ਡਾਇਰੈਕਟਰੀ ਵਿੱਚ ਹੋਣੇ ਚਾਹੀਦੇ ਹਨ। ਨਹੀਂ ਤਾਂ, ਉਸ ਅਨੁਸਾਰ ਪ੍ਰਵਾਹ ਸਕ੍ਰਿਪਟ ਨੂੰ ਅਪਡੇਟ ਕਰੋ।

ਕਦਮ 9: ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਪ੍ਰਵਾਹ ਸਕ੍ਰਿਪਟ ਨੂੰ ਚਲਾਉਣਾ

ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਪ੍ਰਵਾਹ ਸਕ੍ਰਿਪਟ ਨੂੰ ਚਲਾਉਣ ਲਈ:

- ਟੂਲਸ ➤ Tcl ਸਕ੍ਰਿਪਟਾਂ 'ਤੇ ਕਲਿੱਕ ਕਰੋ। Tcl ਸਕ੍ਰਿਪਟ ਡਾਇਲਾਗ ਬਾਕਸ ਦਿਸਦਾ ਹੈ।

- ਪ੍ਰੋਜੈਕਟ ਵਿੱਚ ਸ਼ਾਮਲ ਕਰੋ 'ਤੇ ਕਲਿੱਕ ਕਰੋ, a10_hier_partial_reconfig/flow.tcl ਨੂੰ ਬ੍ਰਾਊਜ਼ ਕਰੋ ਅਤੇ ਚੁਣੋ।

- ਲਾਇਬ੍ਰੇਰੀਆਂ ਪੈਨ ਵਿੱਚ a10_hier_partial_reconfig/flow.tcl ਨੂੰ ਚੁਣੋ, ਅਤੇ ਚਲਾਓ 'ਤੇ ਕਲਿੱਕ ਕਰੋ।

ਇਹ ਲਿਪੀ ਤਿੰਨ ਵਿਅਕਤੀਆਂ ਲਈ ਸੰਸਲੇਸ਼ਣ ਚਲਾਉਂਦੀ ਹੈ। Intel Quartus Prime ਇੱਕ SRAM ਆਬਜੈਕਟ ਤਿਆਰ ਕਰਦਾ ਹੈ File (.sof), ਇੱਕ ਅੰਸ਼ਕ-ਮਾਸਕਡ SRAM ਵਸਤੂ File (.pmsf), ਅਤੇ ਇੱਕ ਰਾਅ ਬਾਈਨਰੀ File (.rbf) ਹਰੇਕ ਵਿਅਕਤੀ ਲਈ।

ਨੋਟ: Intel Quartus Prime ਕਮਾਂਡ ਸ਼ੈੱਲ ਤੋਂ ਸਕ੍ਰਿਪਟ ਚਲਾਉਣ ਲਈ, ਹੇਠ ਦਿੱਤੀ ਕਮਾਂਡ ਟਾਈਪ ਕਰੋ:

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਡਿਜ਼ਾਈਨ ਨੂੰ ਕੰਪਾਇਲ ਕਰੋ

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਫਲੋ ਸਕ੍ਰਿਪਟ ਦੀ ਵਰਤੋਂ ਕਰਨਾ

- ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਪ੍ਰਵਾਹ ਸਕ੍ਰਿਪਟ ਨੂੰ ਸੰਰਚਿਤ ਕਰਨਾ

- ਪ੍ਰੋਗਰਾਮਿੰਗ ਤਿਆਰ ਕਰੋ Files

ਕਦਮ 10: ਬੋਰਡ ਦਾ ਪ੍ਰੋਗਰਾਮਿੰਗ

ਸ਼ੁਰੂ ਕਰਨ ਤੋਂ ਪਹਿਲਾਂ:

- ਪਾਵਰ ਸਪਲਾਈ ਨੂੰ Intel Arria 10 SoC ਵਿਕਾਸ ਬੋਰਡ ਨਾਲ ਕਨੈਕਟ ਕਰੋ।

- USB ਬਲਾਸਟਰ ਕੇਬਲ ਨੂੰ ਆਪਣੇ PC USB ਪੋਰਟ ਅਤੇ ਵਿਕਾਸ ਬੋਰਡ 'ਤੇ USB ਬਲਾਸਟਰ ਪੋਰਟ ਦੇ ਵਿਚਕਾਰ ਕਨੈਕਟ ਕਰੋ।

Intel Arria 10 SoC ਵਿਕਾਸ ਬੋਰਡ 'ਤੇ ਡਿਜ਼ਾਈਨ ਨੂੰ ਚਲਾਉਣ ਲਈ:

- Intel Quartus Prime ਸਾਫਟਵੇਅਰ ਖੋਲ੍ਹੋ ਅਤੇ Tools ➤ Programmer 'ਤੇ ਕਲਿੱਕ ਕਰੋ।

- ਪ੍ਰੋਗਰਾਮਰ ਵਿੱਚ, ਹਾਰਡਵੇਅਰ ਸੈੱਟਅੱਪ 'ਤੇ ਕਲਿੱਕ ਕਰੋ ਅਤੇ USB-ਬਲਾਸਟਰ ਦੀ ਚੋਣ ਕਰੋ।

- ਆਟੋ ਡਿਟੈਕਟ 'ਤੇ ਕਲਿੱਕ ਕਰੋ ਅਤੇ ਡਿਵਾਈਸ ਚੁਣੋ, 10AS066N3।

- ਕਲਿਕ ਕਰੋ ਠੀਕ ਹੈ. Intel Quartus Prime ਸਾਫਟਵੇਅਰ ਬੋਰਡ 'ਤੇ ਤਿੰਨ FPGA ਚਿਪਸ ਨਾਲ ਪ੍ਰੋਗਰਾਮਰ ਨੂੰ ਖੋਜਦਾ ਅਤੇ ਅੱਪਡੇਟ ਕਰਦਾ ਹੈ।

- 10AS066N3 ਡਿਵਾਈਸ ਚੁਣੋ, ਬਦਲੋ 'ਤੇ ਕਲਿੱਕ ਕਰੋ File ਅਤੇ blinking_led_pr_alpha.sof ਨੂੰ ਲੋਡ ਕਰੋ file.

- blinking_led_pr_alpha.sof ਲਈ ਪ੍ਰੋਗਰਾਮ/ਸੰਰਚਨਾ ਨੂੰ ਸਮਰੱਥ ਬਣਾਓ file.

- ਸਟਾਰਟ 'ਤੇ ਕਲਿੱਕ ਕਰੋ ਅਤੇ ਪ੍ਰਗਤੀ ਪੱਟੀ ਦੇ 100% ਤੱਕ ਪਹੁੰਚਣ ਦੀ ਉਡੀਕ ਕਰੋ।

- ਮੂਲ ਫਲੈਟ ਡਿਜ਼ਾਇਨ ਵਾਂਗ ਹੀ ਬਾਰੰਬਾਰਤਾ 'ਤੇ ਝਪਕਦੇ ਹੋਏ ਬੋਰਡ 'ਤੇ LEDs ਨੂੰ ਵੇਖੋ।

- ਸਿਰਫ਼ ਚਾਈਲਡ PR ਖੇਤਰ ਨੂੰ ਪ੍ਰੋਗਰਾਮ ਕਰਨ ਲਈ, blinking_led_pr_alpha.sof 'ਤੇ ਸੱਜਾ-ਕਲਿੱਕ ਕਰੋ। file ਪ੍ਰੋਗਰਾਮਰ ਵਿੱਚ ਅਤੇ ਐਡ ਪੀਆਰ ਪ੍ਰੋਗਰਾਮਿੰਗ 'ਤੇ ਕਲਿੱਕ ਕਰੋ File.

- blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf ਚੁਣੋ file.

- blinking_led_pr_alpha.sof ਲਈ ਪ੍ਰੋਗਰਾਮ/ਸੰਰਚਨਾ ਨੂੰ ਅਯੋਗ ਕਰੋ file.

- blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf ਲਈ ਪ੍ਰੋਗਰਾਮ/ਸੰਰਚਨਾ ਨੂੰ ਸਮਰੱਥ ਬਣਾਓ file ਅਤੇ ਸਟਾਰਟ 'ਤੇ ਕਲਿੱਕ ਕਰੋ। ਬੋਰਡ 'ਤੇ, LED[0] ਅਤੇ LED[1] ਨੂੰ ਲਗਾਤਾਰ ਝਪਕਦੇ ਹੋਏ ਵੇਖੋ। ਜਦੋਂ ਪ੍ਰਗਤੀ ਪੱਟੀ 100% ਤੱਕ ਪਹੁੰਚ ਜਾਂਦੀ ਹੈ, ਤਾਂ LED[2] ਉਸੇ ਦਰ 'ਤੇ ਝਪਕਦਾ ਹੈ, ਅਤੇ LED[3] ਹੌਲੀ ਹੌਲੀ ਝਪਕਦਾ ਹੈ।

- ਮਾਤਾ-ਪਿਤਾ ਅਤੇ ਬੱਚੇ ਦੇ ਪੀਆਰ ਖੇਤਰ ਦੋਵਾਂ ਨੂੰ ਪ੍ਰੋਗਰਾਮ ਕਰਨ ਲਈ, .rbf 'ਤੇ ਸੱਜਾ-ਕਲਿੱਕ ਕਰੋ file ਪ੍ਰੋਗਰਾਮਰ ਵਿੱਚ ਅਤੇ PR ਪ੍ਰੋਗਰਾਮਿੰਗ ਬਦਲੋ 'ਤੇ ਕਲਿੱਕ ਕਰੋ File.

- blinking_led_pr_delta.pr_parent_partition.rbf ਚੁਣੋ file.

- ਸਟਾਰਟ 'ਤੇ ਕਲਿੱਕ ਕਰੋ। ਬੋਰਡ 'ਤੇ, ਵੇਖੋ ਕਿ LED[0] ਅਤੇ LED[1] ਝਪਕਦੇ ਰਹਿੰਦੇ ਹਨ। ਜਦੋਂ ਪ੍ਰਗਤੀ ਪੱਟੀ 100% ਤੱਕ ਪਹੁੰਚ ਜਾਂਦੀ ਹੈ, LED[2] ਅਤੇ LED[3] ਦੋਵੇਂ ਹੌਲੀ ਝਪਕਦੇ ਹਨ।

- ਸਿਰਫ਼ ਚਾਈਲਡ PR ਖੇਤਰ, ਜਾਂ ਮਾਤਾ-ਪਿਤਾ ਅਤੇ ਚਾਈਲਡ PR ਖੇਤਰਾਂ ਦੋਵਾਂ ਨੂੰ ਇੱਕੋ ਸਮੇਂ ਗਤੀਸ਼ੀਲ ਤੌਰ 'ਤੇ ਮੁੜ-ਪ੍ਰੋਗਰਾਮ ਕਰਨ ਲਈ ਉਪਰੋਕਤ ਕਦਮਾਂ ਨੂੰ ਦੁਹਰਾਓ।

ਚਿੱਤਰ 10. Intel Arria 10 SoC ਵਿਕਾਸ ਬੋਰਡ ਦਾ ਪ੍ਰੋਗਰਾਮਿੰਗ

ਇੱਕ ਮੌਜੂਦਾ ਸ਼ਖਸੀਅਤ ਨੂੰ ਸੋਧਣਾ

- ਅਧਾਰ ਸੰਸ਼ੋਧਨ ਨੂੰ ਪੂਰੀ ਤਰ੍ਹਾਂ ਕੰਪਾਇਲ ਕਰਨ ਤੋਂ ਬਾਅਦ ਵੀ, ਤੁਸੀਂ ਮੌਜੂਦਾ ਵਿਅਕਤੀ ਨੂੰ ਬਦਲ ਸਕਦੇ ਹੋ।

- ਸਾਬਕਾ ਲਈample, blinking_led_child_slow ਵਿਅਕਤੀ ਨੂੰ ਹੋਰ ਵੀ ਹੌਲੀ ਝਪਕਾਉਣ ਲਈ:

- ਬਲਿੰਕਿੰਗ_ਲੇਡ_ਚਾਈਲਡ_ਸਲੋ.ਐਸ.ਵੀ file, COUNTER_TAP ਪੈਰਾਮੀਟਰ ਨੂੰ 27 ਤੋਂ 28 ਤੱਕ ਸੋਧੋ।

- ਇਸ ਸ਼ਖਸੀਅਤ ਨੂੰ ਮੁੜ-ਸਿੰਥੇਸਾਈਜ਼ ਕਰਨ ਅਤੇ ਮੁੜ-ਲਾਗੂ ਕਰਨ ਲਈ, ਤੁਹਾਨੂੰ ਪਰਿਵਰਤਨ ਦੁਆਰਾ ਪ੍ਰਭਾਵਿਤ ਸਾਰੇ ਸੰਸ਼ਲੇਸ਼ਣ-ਸਿਰਫ਼ ਸੰਸ਼ੋਧਨਾਂ ਅਤੇ ਲਾਗੂਕਰਨ ਸੰਸ਼ੋਧਨਾਂ ਨੂੰ ਦੁਬਾਰਾ ਕੰਪਾਇਲ ਕਰਨਾ ਚਾਹੀਦਾ ਹੈ। ਹੇਠ ਲਿਖੀਆਂ ਲਾਈਨਾਂ ਨੂੰ ਸ਼ਾਮਲ ਕਰਨ ਲਈ setup.tcl ਸਕ੍ਰਿਪਟ ਨੂੰ ਸੋਧੋ:

ਨੋਟ: blinking_led_pr_delta ਸੰਸ਼ੋਧਨ ਲਈ pr_parent_parition ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਦੇ ਸਮੇਂ, ਤੁਸੀਂ ਲਾਗੂ ਕਰਨ ਲਈ ਉਸ ਵਿਅਕਤੀ ਦਾ ਅੰਤਿਮ ਸਨੈਪਸ਼ਾਟ ਆਯਾਤ ਕਰਦੇ ਹੋ। ਨਤੀਜੇ ਵਜੋਂ, ਅਨੁਸਾਰੀ ਚਾਈਲਡ ਭਾਗ ਨੂੰ ਸੋਧਣ ਅਤੇ ਲਾਗੂ ਕਰਨ ਦੌਰਾਨ, ਪੇਰੈਂਟ ਪਾਰਟੀਸ਼ਨ ਤਰਕ ਨੂੰ ਲਾਗੂ ਕਰਨਾ ਇੱਕੋ ਜਿਹਾ ਰਹਿੰਦਾ ਹੈ।

ਨੋਟ: blinking_led_pr_delta ਸੰਸ਼ੋਧਨ ਲਈ pr_parent_parition ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਦੇ ਸਮੇਂ, ਤੁਸੀਂ ਲਾਗੂ ਕਰਨ ਲਈ ਉਸ ਵਿਅਕਤੀ ਦਾ ਅੰਤਿਮ ਸਨੈਪਸ਼ਾਟ ਆਯਾਤ ਕਰਦੇ ਹੋ। ਨਤੀਜੇ ਵਜੋਂ, ਅਨੁਸਾਰੀ ਚਾਈਲਡ ਭਾਗ ਨੂੰ ਸੋਧਣ ਅਤੇ ਲਾਗੂ ਕਰਨ ਦੌਰਾਨ, ਪੇਰੈਂਟ ਪਾਰਟੀਸ਼ਨ ਤਰਕ ਨੂੰ ਲਾਗੂ ਕਰਨਾ ਇੱਕੋ ਜਿਹਾ ਰਹਿੰਦਾ ਹੈ। ਇਹ ਕਮਾਂਡ blinking_led_child_slow ਸੰਸ਼ਲੇਸ਼ਣ ਸੰਸ਼ੋਧਨ ਨੂੰ ਮੁੜ-ਸਿੰਥੇਸਾਈਜ਼ ਕਰਦੀ ਹੈ, ਅਤੇ ਫਿਰ blinking_led_pr_bravo ਦੀ ਵਰਤੋਂ ਕਰਕੇ PR ਲਾਗੂਕਰਨ ਕੰਪਾਇਲ ਨੂੰ ਚਲਾਉਂਦੀ ਹੈ।

ਇਹ ਕਮਾਂਡ blinking_led_child_slow ਸੰਸ਼ਲੇਸ਼ਣ ਸੰਸ਼ੋਧਨ ਨੂੰ ਮੁੜ-ਸਿੰਥੇਸਾਈਜ਼ ਕਰਦੀ ਹੈ, ਅਤੇ ਫਿਰ blinking_led_pr_bravo ਦੀ ਵਰਤੋਂ ਕਰਕੇ PR ਲਾਗੂਕਰਨ ਕੰਪਾਇਲ ਨੂੰ ਚਲਾਉਂਦੀ ਹੈ। - ਸੰਸ਼ਲੇਸ਼ਣ-ਸਿਰਫ਼ ਸੰਸ਼ੋਧਨਾਂ ਦਾ ਸੰਕਲਨ ਕਰਨ ਲਈ, ਹੇਠ ਦਿੱਤੀ ਕਮਾਂਡ ਚਲਾਓ: ਇਹ ਕਮਾਂਡ ਬੇਸ ਰੀਵਿਜ਼ਨ ਨੂੰ ਮੁੜ ਕੰਪਾਇਲ ਨਹੀਂ ਕਰਦੀ ਹੈ।

- ਲਾਗੂਕਰਨ ਸੋਧਾਂ ਦਾ ਸੰਕਲਨ ਕਰਨ ਲਈ, ਹੇਠ ਦਿੱਤੀ ਕਮਾਂਡ ਚਲਾਓ:

- ਇਹ ਕਮਾਂਡ ਬੇਸ ਰੀਵਿਜ਼ਨ ਨੂੰ ਮੁੜ ਕੰਪਾਇਲ ਨਹੀਂ ਕਰਦੀ ਹੈ।

- ਕਦਮ 10 ਵਿੱਚ ਦਿੱਤੇ ਕਦਮਾਂ ਦੀ ਪਾਲਣਾ ਕਰੋ: ਨਤੀਜੇ ਵਜੋਂ ਆਰਬੀਐਫ ਨੂੰ ਪ੍ਰੋਗਰਾਮ ਕਰਨ ਲਈ ਪੰਨਾ 22 'ਤੇ ਬੋਰਡ ਨੂੰ ਪ੍ਰੋਗਰਾਮਿੰਗ ਕਰੋ file FPGA ਵਿੱਚ.

ਨੋਟ: ਹਰੇਕ ਸੰਸ਼ੋਧਨ ਲਈ ਪੂਰੇ ਪ੍ਰਵਾਹ ਨੂੰ ਚਲਾਉਣ ਤੋਂ ਬਚਣ ਲਈ, setup.tcl ਸਕ੍ਰਿਪਟ ਵਿੱਚ ਸੰਸ਼ਲੇਸ਼ਣ-ਸਿਰਫ ਸੰਸ਼ੋਧਨ ਅਤੇ ਲਾਗੂਕਰਨ ਸੰਸ਼ੋਧਨਾਂ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰੋ, ਅਤੇ ਸਕ੍ਰਿਪਟ ਚਲਾਓ।

ਡਿਜ਼ਾਈਨ ਵਿੱਚ ਇੱਕ ਨਵਾਂ ਵਿਅਕਤੀ ਸ਼ਾਮਲ ਕਰਨਾ

ਆਪਣੇ ਅਧਾਰ ਸੰਸ਼ੋਧਨ ਨੂੰ ਪੂਰੀ ਤਰ੍ਹਾਂ ਕੰਪਾਇਲ ਕਰਨ ਤੋਂ ਬਾਅਦ, ਤੁਸੀਂ ਅਜੇ ਵੀ ਨਵੇਂ ਵਿਅਕਤੀ ਸ਼ਾਮਲ ਕਰ ਸਕਦੇ ਹੋ ਅਤੇ ਵਿਅਕਤੀਗਤ ਤੌਰ 'ਤੇ ਇਹਨਾਂ ਵਿਅਕਤੀਆਂ ਨੂੰ ਕੰਪਾਇਲ ਕਰ ਸਕਦੇ ਹੋ।

ਸਾਬਕਾ ਲਈample, blinking_led_parent_slow ਲਈ ਇੱਕ ਨਵੇਂ ਬੱਚੇ ਦੀ ਸ਼ਖਸੀਅਤ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਨ ਲਈ, ਜੋ led_three ਨੂੰ ਬੰਦ ਕਰ ਦਿੰਦਾ ਹੈ:

- blinking_led_child_empty.sv ਨੂੰ blinking_led_chdild_off.sv ਵਿੱਚ ਕਾਪੀ ਕਰੋ।

- ਬਲਿੰਕਿੰਗ_ਲੇਡ_ਚਾਈਲਡ_off.sv ਵਿੱਚ file, ਅਸਾਈਨਮੈਂਟ ਨੂੰ ਸੋਧੋ, led_three_on = 1'b0 ਨਿਰਧਾਰਤ ਕਰੋ; led_three_on = 1'b1; ਨਿਰਧਾਰਤ ਕਰਨ ਲਈ. ਯਕੀਨੀ ਬਣਾਓ ਕਿ ਤੁਸੀਂ ਮੋਡੀਊਲ ਦਾ ਨਾਮ blinking_led_child_empty ਤੋਂ blinking_led_child_off ਵਿੱਚ ਬਦਲਿਆ ਹੈ।

- ਪੰਨਾ 16 'ਤੇ ਸੰਸ਼ਲੇਸ਼ਣ-ਸਿਰਫ਼ ਸੰਸ਼ੋਧਨ ਬਣਾਉਣ ਦੇ ਕਦਮਾਂ ਦੀ ਪਾਲਣਾ ਕਰਕੇ, ਇੱਕ ਨਵਾਂ ਸੰਸ਼ਲੇਸ਼ਣ ਸੰਸ਼ੋਧਨ ਬਣਾਓ, blinking_led_child_off।

ਨੋਟ: blinking_led_child_off ਸੰਸ਼ੋਧਨ ਨੂੰ blinking_led_child_off.sv ਦੀ ਵਰਤੋਂ ਕਰਨੀ ਚਾਹੀਦੀ ਹੈ file. - ਸਫ਼ਾ 15 'ਤੇ ਲਾਗੂ ਸੰਸ਼ੋਧਨ ਬਣਾਉਣ ਦੇ ਕਦਮਾਂ ਦੀ ਪਾਲਣਾ ਕਰਕੇ, ਇੱਕ ਨਵਾਂ ਲਾਗੂਕਰਨ ਸੰਸ਼ੋਧਨ ਬਣਾਓ, blinking_led_pr_foxtrot।

- a10_hier_partial_reconfig/setup.tcl ਨੂੰ ਅੱਪਡੇਟ ਕਰੋ file ਨਵੇਂ PR ਲਾਗੂਕਰਨ ਨੂੰ ਪਰਿਭਾਸ਼ਿਤ ਕਰਨ ਲਈ:

- ਹੇਠ ਦਿੱਤੀ ਕਮਾਂਡ ਚਲਾ ਕੇ ਸਿਰਫ ਇਸ ਨਵੇਂ ਸੰਸਲੇਸ਼ਣ ਅਤੇ ਲਾਗੂਕਰਨ ਸੰਸ਼ੋਧਨ ਨੂੰ ਕੰਪਾਇਲ ਕਰੋ:

Intel Arria 10 ਡਿਵਾਈਸਾਂ ਲਈ ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਬਾਰੇ ਪੂਰੀ ਜਾਣਕਾਰੀ ਲਈ, Intel Quartus Prime Pro ਐਡੀਸ਼ਨ ਹੈਂਡਬੁੱਕ ਦੇ ਵਾਲੀਅਮ 1 ਵਿੱਚ ਇੱਕ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ ਡਿਜ਼ਾਈਨ ਬਣਾਉਣਾ ਵੇਖੋ।

ਸੰਬੰਧਿਤ ਜਾਣਕਾਰੀ

- ਇੱਕ ਅੰਸ਼ਕ ਮੁੜ ਸੰਰਚਨਾ ਡਿਜ਼ਾਈਨ ਬਣਾਉਣਾ

- ਅੰਸ਼ਕ ਪੁਨਰਗਠਨ ਔਨਲਾਈਨ ਸਿਖਲਾਈ

ਦਸਤਾਵੇਜ਼ ਸੰਸ਼ੋਧਨ ਇਤਿਹਾਸ

ਸਾਰਣੀ 5. ਦਸਤਾਵੇਜ਼ ਸੋਧ ਇਤਿਹਾਸ

| ਦਸਤਾਵੇਜ਼ ਸੰਸਕਰਣ | ਸਾਫਟਵੇਅਰ ਵਰਜਨ | ਤਬਦੀਲੀਆਂ |

| 2017.11.06 | 17.1.0 | • ਅੱਪਡੇਟ ਕੀਤਾ ਸੰਦਰਭ ਡਿਜ਼ਾਈਨ ਲੋੜਾਂ ਸਾਫਟਵੇਅਰ ਸੰਸਕਰਣ ਦੇ ਨਾਲ ਭਾਗ

• ਅੱਪਡੇਟ ਕੀਤਾ PR ਵਿਭਾਗੀਕਰਨ ਦੇ ਬਿਨਾਂ ਫਲੈਟ ਰੈਫਰੈਂਸ ਡਿਜ਼ਾਈਨ ਡਿਜ਼ਾਇਨ ਬਲਾਕ ਬਦਲਾਅ ਦੇ ਨਾਲ ਚਿੱਤਰ • ਅੱਪਡੇਟ ਕੀਤਾ ਹਵਾਲਾ ਡਿਜ਼ਾਈਨ Files 'ਤੇ ਜਾਣਕਾਰੀ ਦੇ ਨਾਲ ਸਾਰਣੀ Top_counter.sv ਮੋਡੀਊਲ • ਅੱਪਡੇਟ ਕੀਤਾ ਅੰਸ਼ਕ ਮੁੜ ਸੰਰਚਨਾ IP ਕੋਰ ਏਕੀਕਰਣ ਡਿਜ਼ਾਇਨ ਬਲਾਕ ਬਦਲਾਅ ਦੇ ਨਾਲ ਚਿੱਤਰ • ਅੰਕੜਿਆਂ ਨੂੰ ਅਪਡੇਟ ਕੀਤਾ - ਡਿਜ਼ਾਇਨ ਭਾਗ ਵਿੰਡੋ ਅਤੇ ਤਰਕ ਲਾਕ ਖੇਤਰ ਵਿੰਡੋ ਨਵੀਂ GUI ਨੂੰ ਦਰਸਾਉਣ ਲਈ • File ਨਾਮ ਤਬਦੀਲੀ • ਟੈਕਸਟ ਸੰਪਾਦਨ |

| 2017.05.08 | 17.0.0 | ਦਸਤਾਵੇਜ਼ ਦੀ ਸ਼ੁਰੂਆਤੀ ਰੀਲੀਜ਼ |

ਦਸਤਾਵੇਜ਼ / ਸਰੋਤ

|

Arria 805 SoC ਵਿਕਾਸ ਬੋਰਡ 'ਤੇ ਡਿਜ਼ਾਈਨ ਦੀ intel AN 10 ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ [pdf] ਯੂਜ਼ਰ ਗਾਈਡ ਏਰੀਆ 805 ਐਸਓਸੀ ਡਿਵੈਲਪਮੈਂਟ ਬੋਰਡ, ਏਐਨ 10, ਏਰੀਆ 805 ਐਸਓਸੀ ਡਿਵੈਲਪਮੈਂਟ ਬੋਰਡ ਉੱਤੇ ਇੱਕ ਡਿਜ਼ਾਈਨ ਦੀ ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ, ਏਰੀਆ 10 ਐਸਓਸੀ ਵਿਕਾਸ ਬੋਰਡ ਉੱਤੇ ਇੱਕ ਡਿਜ਼ਾਈਨ ਦੀ ਲੜੀਵਾਰ ਅੰਸ਼ਕ ਪੁਨਰ-ਸੰਰਚਨਾ, ਏਰੀਆ 10 ਐਸਓਸੀ ਵਿਕਾਸ ਬੋਰਡ ਉੱਤੇ ਇੱਕ ਡਿਜ਼ਾਈਨ ਦੀ ਮੁੜ ਸੰਰਚਨਾ, ਅਰਰੀਆ 10 ਐਸਓਸੀ ਵਿਕਾਸ ਬੋਰਡ, 10 ਐਸਓਸੀ ਵਿਕਾਸ ਬੋਰਡ |