intel AN 805 Arria 10 SoC ဖွံ့ဖြိုးတိုးတက်ရေးဘုတ်အဖွဲ့တွင် ဒီဇိုင်းတစ်ခု၏ အထက်အောက် တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း

Intel® Arria® 10 SoC ဖွံ့ဖြိုးတိုးတက်မှုဘုတ်အဖွဲ့အတွက် အထက်အောက် တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်မှု ကျူတိုရီရယ်

ဤအပလီကေးရှင်းမှတ်စုသည် ရိုးရှင်းသော ဒီဇိုင်းကို အထက်အောက် တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်နိုင်သော ဒီဇိုင်းအဖြစ် ပြောင်းလဲခြင်းနှင့် Intel® Arria® 10 SoC ဖွံ့ဖြိုးတိုးတက်မှုဘုတ်အဖွဲ့တွင် ဒီဇိုင်းကို အကောင်အထည်ဖော်ခြင်းတို့ကို သရုပ်ပြသည်။ Hierarchical partial reconfiguration (HPR) သည် အခြား PR ဒေသအတွင်းတွင် PR နယ်မြေတစ်ခုပါ၀င်သော အထူးအမျိုးအစားတစ်ခုဖြစ်သည်။ ကလေးနှင့် မိဘအကန့်များအတွက် လူအများအပြားကို သင်ဖန်တီးနိုင်သည်။ ကလေးအကန့်များကို ၎င်းတို့၏ မိဘအကန့်များအတွင်းတွင် သင်ထည့်သွင်းထားသည်။ ကလေးအခန်းကန့်ကို ပြန်လည်ပြင်ဆင်ခြင်းသည် မိဘ သို့မဟုတ် တည်ငြိမ်သောဒေသများတွင် လုပ်ဆောင်မှုကို သက်ရောက်မှုမရှိပါ။ parent partition ကို ပြန်လည်ပြင်ဆင်ခြင်းသည် တည်ငြိမ်သောဒေသရှိ လုပ်ဆောင်ချက်ကို သက်ရောက်မှုမရှိပါ၊ သို့သော်၊ မိဘဒေသ၏ ကလေးအပိုင်းခွဲများကို မူရင်းကလေးအပိုင်းပိုင်းခွဲရေးကိုယ်တာများဖြင့် အစားထိုးပါသည်။ ဤနည်းစနစ်သည် တူညီသော FPGA စက်ပစ္စည်းအရင်းအမြစ်များကို အချိန်နှင့်အမျှ အများအပြားလုပ်ဆောင်သည့်စနစ်များတွင် ထိရောက်မှုရှိသည်။

တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်းသည် ပြားချပ်ချပ်ဒီဇိုင်းအတွက် အောက်ပါတိုးတက်မှုများကို ပံ့ပိုးပေးသည်-

- လည်ပတ်ချိန် ဒီဇိုင်းကို ပြန်လည်ပြင်ဆင်ခြင်းကို ခွင့်ပြုသည်။

- ဒီဇိုင်း၏ အတိုင်းအတာကို တိုးစေသည်။

- စနစ်ပျက်ချိန်ကို လျှော့ချပေးသည်။

- ဒီဇိုင်းတွင် ဒိုင်းနမစ်အချိန်-များစွာသော လုပ်ဆောင်ချက်များကို ပံ့ပိုးပေးသည်။

- ဘုတ်နေရာကို ထိရောက်စွာအသုံးပြုခြင်းဖြင့် ကုန်ကျစရိတ်နှင့် ပါဝါသုံးစွဲမှုကို သက်သာစေသည်။

- မှတ်ချက် -

- ဤအကိုးအကားဒီဇိုင်းကို အကောင်အထည်ဖော်ရာတွင် Intel Quartus® Prime FPGA အကောင်အထည်ဖော်မှုစီးဆင်းမှုနှင့် အခြေခံ Intel Quartus Prime ပရောဂျက်၏ အသိပညာနှင့် အခြေခံရင်းနှီးမှုရှိရန် လိုအပ်ပါသည်။ files.

ဆက်စပ်အချက်အလက်

- Intel Arria 10 SoC Development Kit အသုံးပြုသူလမ်းညွှန်

- တစ်စိတ်တစ်ပိုင်း ပြန်လည်ဖွဲ့စည်းမှု အယူအဆများ

- Partial Reconfiguration Design Flow

- တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း ဒီဇိုင်း အကြံပြုချက်များ

- တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်မှု ဒီဇိုင်းထည့်သွင်းစဉ်းစားမှုများ

အကိုးအကား ဒီဇိုင်းလိုအပ်ချက်များ

ဤအကိုးအကား ဒီဇိုင်းသည် အောက်ပါတို့ လိုအပ်သည်-

- ဒီဇိုင်းအကောင်အထည်ဖော်မှုအတွက် Intel Quartus Prime Pro Edition ဆော့ဖ်ဝဲဗားရှင်း 17.1။

- FPGA အကောင်အထည်ဖော်မှုအတွက် Intel Arria 10 SoC ဖွံ့ဖြိုးတိုးတက်ရေးကိရိယာအစုံ။

Intel ကော်ပိုရေးရှင်း။ မူပိုင်ခွင့်ကိုလက်ဝယ်ထားသည်။ Intel၊ Intel လိုဂိုနှင့် အခြားသော Intel အမှတ်အသားများသည် Intel ကော်ပိုရေးရှင်း သို့မဟုတ် ၎င်း၏လုပ်ငန်းခွဲများ၏ အမှတ်တံဆိပ်များဖြစ်သည်။ Intel သည် Intel ၏ စံအာမခံချက်နှင့်အညီ ၎င်း၏ FPGA နှင့် တစ်ပိုင်းလျှပ်ကူးပစ္စည်းထုတ်ကုန်များ၏ စွမ်းဆောင်ရည်ကို လက်ရှိ သတ်မှတ်ချက်များအတိုင်း အာမခံထားသော်လည်း မည်သည့်ထုတ်ကုန်နှင့် ဝန်ဆောင်မှုများကိုမဆို အသိပေးခြင်းမရှိဘဲ အချိန်မရွေး အပြောင်းအလဲပြုလုပ်ပိုင်ခွင့်ကို လက်ဝယ်ရှိပါသည်။ Intel မှ စာဖြင့် အတိအလင်း သဘောတူထားသည့်အတိုင်း ဤနေရာတွင် ဖော်ပြထားသော အချက်အလက်၊ ထုတ်ကုန် သို့မဟုတ် ဝန်ဆောင်မှုကို အသုံးပြုခြင်း သို့မဟုတ် အသုံးပြုခြင်းမှ ဖြစ်ပေါ်လာသော တာဝန် သို့မဟုတ် တာဝန်ခံမှု မရှိဟု ယူဆပါသည်။ Intel သုံးစွဲသူများသည် ထုတ်ဝေထားသော အချက်အလက်များနှင့် ထုတ်ကုန် သို့မဟုတ် ဝန်ဆောင်မှုများအတွက် အမှာစာမတင်မီ နောက်ဆုံးဗားရှင်းကို ရယူရန် အကြံပြုအပ်ပါသည်။

- အခြားအမည်များနှင့် အမှတ်တံဆိပ်များကို အခြားသူများ၏ ပိုင်ဆိုင်မှုအဖြစ် တောင်းဆိုနိုင်ပါသည်။

Reference Design Overview

- ဤရည်ညွှန်းဒီဇိုင်းတွင် 32-bit ကောင်တာတစ်ခု ပါဝင်ပါသည်။ ဘုတ်အဆင့်တွင်၊ ဒီဇိုင်းသည် နာရီကို 50MHz အရင်းအမြစ်နှင့် ချိတ်ဆက်ပြီး FPGA ရှိ LED လေးလုံးနှင့် အထွက်ကို ချိတ်ဆက်သည်။ တိကျသောအစီအစဥ်တစ်ခုရှိ ကောင်တာဘစ်များမှ အထွက်ကိုရွေးချယ်ခြင်းသည် LED များကို တိကျသောကြိမ်နှုန်းတစ်ခုတွင် မှိတ်တုတ်ဖြစ်စေသည်။

ပုံ ၇။ PR Partitioning မပါဘဲ Flat Reference Design

ရည်ညွှန်းဒီဇိုင်း Files

တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်းဆိုင်ရာ သင်ခန်းစာကို အောက်ပါတည်နေရာတွင် ရရှိနိုင်ပါသည်။ https://github.com/intel/fpga-partial-reconfig

သင်ခန်းစာကို ဒေါင်းလုဒ်လုပ်ရန်-

- Clone ကိုနှိပ်ပါ သို့မဟုတ် ဒေါင်းလုဒ်လုပ်ပါ။

- Download ZIP ကိုနှိပ်ပါ။ FPGA-partial-config-master.zip ကို ဇစ်ဖွင့်ပါ။ file.

- ရည်ညွှန်းဒီဇိုင်းကို ဝင်ရောက်ကြည့်ရှုရန် ကျူတိုရီရယ်များ/a10_soc_devkit_blinking_led_hpr ဖိုင်တွဲခွဲသို့ သွားပါ။

Flat folder တွင် အောက်ပါတို့ ပါဝင်ပါသည်။ files:

ဇယား 1. အကိုးအကား ဒီဇိုင်း Files

| File နာမည် | ဖော်ပြချက် |

| ထိပ်တန်း။ SV | ထိပ်တန်းအဆင့် file ဒီဇိုင်းကို အပြားလိုက် အကောင်အထည်ဖော်မှု ပါရှိသည်။ ဤ module သည် blinking_led အပိုင်းခွဲခွဲနှင့် top_counter module ကို ချက်ချင်းလုပ်ဆောင်ပေးသည်။ |

| top_counter.sv | LED[32] တိုက်ရိုက်ထိန်းချုပ်သည့် ထိပ်တန်းအဆင့် 1-ဘစ်ကောင်တာ။ ကောင်တာ၏ မှတ်ပုံတင်ထားသော အထွက်အထွက်သည် LED[0] ကို ထိန်းချုပ်ထားပြီး blinking_led module မှတဆင့် LED[2] နှင့် LED[3] ကို ပါဝါပေးပါသည်။ |

| blinking_led.sdc | ပရောဂျက်အတွက် အချိန်ကန့်သတ်ချက်များကို သတ်မှတ်သည်။ |

| ဆက်ရန်… | |

| File နာမည် | ဖော်ပြချက် |

| blinking_led.SV | ဤသင်ခန်းစာတွင်၊ သင်သည် ဤ module ကို parent PR partition အဖြစ်သို့ပြောင်းလဲပါ။ မော်ဂျူးသည် LED[2] နှင့် LED[3] ကို ထိန်းချုပ်သည့် top_counter module ၏ မှတ်ပုံတင်ထားသော အထွက်ကို လက်ခံရရှိသည် ။ |

| blinking_led.qpf | Intel Quartus Prime ပရောဂျက် file ပရောဂျက်ရှိ ပြန်လည်ပြင်ဆင်မှုအားလုံး၏ စာရင်းပါရှိသည်။ |

| blinking_led.qsf | Intel Quartus Prime ဆက်တင်များ file ပရောဂျက်အတွက် တာဝန်များနှင့် ဆက်တင်များ ပါဝင်သည်။ |

မှတ်ချက် - hpr ဖိုင်တွဲတွင် အစုံအလင်ပါရှိသည်။ fileဤအပလီကေးရှင်းကို အသုံးပြု၍ ဖန်တီးထားသည်ကို မှတ်သားပါ။ ဒါတွေကို ကိုးကားပါ။ fileလေ့ကျင့်ခန်းလုပ်နေစဉ်အတွင်း မည်သည့်အမှတ်တွင်မဆို။

ပုံ 2. အကိုးအကား ဒီဇိုင်း Files

အကိုးအကား Design Walkthrough

အောက်ဖော်ပြပါအဆင့်များသည် ပြားချပ်ချပ်ဒီဇိုင်းတစ်ခုသို့ တစ်စိတ်တစ်ပိုင်းပြန်လည်ဖွဲ့စည်းခြင်းဆိုင်ရာ အသုံးချမှုကို ဖော်ပြသည်။ သင်ခန်းစာတွင် Intel Arria 10 SoC ဖွံ့ဖြိုးတိုးတက်မှုဘုတ်အဖွဲ့အတွက် Intel Quartus Prime Pro Edition ဆော့ဖ်ဝဲကို အသုံးပြုသည်-

- အဆင့် 1- စာမျက်နှာ ၆ တွင် စတင်ခြင်း

- အဆင့် 2- စာမျက်နှာ 6 တွင် ကလေးအဆင့်ခွဲမော်ဂျူးတစ်ခု ဖန်တီးပါ။

- အဆင့် 3- စာမျက်နှာ ၇ တွင် ဒီဇိုင်းအပိုင်းများကို ဖန်တီးခြင်း။

- အဆင့် 4- စာမျက်နှာ ၉ တွင် PR Partitions အတွက် နေရာချထားခြင်းနှင့် လမ်းကြောင်းသတ်မှတ်ခြင်း တိုင်းဒေသကြီး

- အဆင့် 5- စာမျက်နှာ 10 တွင် Intel Arria 10 Partial Reconfiguration Controller IP Core ကို ထည့်သွင်းခြင်း။

- အဆင့် 6- စာမျက်နှာ 13 တွင် ပုဂ္ဂိုလ်များကို သတ်မှတ်ခြင်း

- အဆင့် 7- စာမျက်နှာ 15 တွင် ပြန်လည်ပြင်ဆင်မှုများ ပြုလုပ်ခြင်း။

- အဆင့် 8- စာမျက်နှာ 20 တွင် Hierarchical Partial Reconfiguration Flow Script ကို ထုတ်လုပ်ခြင်း။

- အဆင့် 9- စာမျက်နှာ 21 တွင် Hierarchical Partial Reconfiguration Flow Script ကို လုပ်ဆောင်ခြင်း။

- အဆင့် 10- စာမျက်နှာ ၂၂ တွင် ဘုတ်အဖွဲ့ကို ပရိုဂရမ်ရေးဆွဲခြင်း။

အဆင့် 1: စတင်လိုက်ပါ။

အကိုးအကား ဒီဇိုင်းကို ကူးယူရန် fileသင့်လုပ်ငန်းခွင်ပတ်ဝန်းကျင်သို့ blinking_led ပြားချပ်ချပ်ဒီဇိုင်းကို စုစည်းပါ-

- သင့်လုပ်ငန်းခွင်ပတ်ဝန်းကျင်တွင် a10_soc_devkit_blinking_led_hpr လမ်းညွှန်တစ်ခု ဖန်တီးပါ။

- ဒေါင်းလုဒ်လုပ်ထားသော သင်ခန်းစာများ/a10_soc_devkit_blinking_led_hpr/flat sub-folder ကို a10_soc_devkit_blinking_led_hpr လမ်းညွှန်သို့ ကူးယူပါ။

- Intel Quartus Prime Pro Edition ဆော့ဖ်ဝဲတွင်၊ နှိပ်ပါ။ File ➤ ပရောဂျက်ကိုဖွင့်ပြီး blinking_led.qpf ကို ရွေးပါ။

- ပြားချပ်ချပ်ဒီဇိုင်းကို စုစည်းရန်၊ လုပ်ဆောင်ခြင်း ➤ စတင်စုစည်းခြင်းကို နှိပ်ပါ။

အဆင့် 2- ကလေးအဆင့်ခွဲမော်ဂျူးတစ်ခု ဖန်တီးခြင်း။

ဤပြားချပ်ချပ်ဒီဇိုင်းကို အထက်တန်းကျသော PR ဒီဇိုင်းအဖြစ်သို့ ပြောင်းလဲရန်၊ ပင်မမော်ဂျူးခွဲ (blinking_led.sv) အတွင်းရှိ ကလေးခွဲမော်ဂျူး (blinking_led_child. SV) ကို ဖန်တီးရပါမည်။

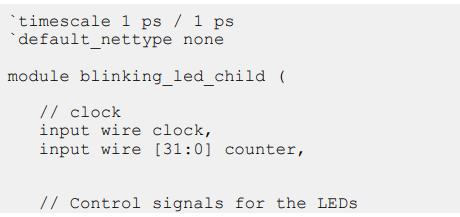

- ဒီဇိုင်းအသစ်ဖန်တီးပါ။ file, blinking_led_child.sv နှင့် အောက်ပါ ကုဒ်လိုင်းများကို ဤသို့ ထည့်ပါ။ file: timescale 1 ps / 1 ps `default_nettype none module မှိတ်တုတ်မှိတ်တုတ်_led_child ( // နာရီထည့်သွင်းမှုဝါယာကြိုးနာရီ၊ အဝင်ဝါယာကြိုး [31:0] တန်ပြန်၊ // LED မီးများအတွက် ထိန်းချုပ်အချက်ပြမှုများ

- blinking_led.sv ကို မွမ်းမံပါ။ file led_two_on ကို တည်ငြိမ်ဒေသမှ ကောင်တာ၏ bit 23 သို့ ချိတ်ဆက်ရန်နှင့် blinking_led_child module ကို ချက်ချင်းလုပ်ဆောင်ရန်။ ပြုပြင်မွမ်းမံပြီးနောက်၊ သင်၏ blinking_led.sv file အောက်ပါအတိုင်းပေါ်လာရမည်-

- ဒီဇိုင်းအားလုံးကို ပြုပြင်မွမ်းမံခြင်း။ files၊ Processing ➤ Start Compilation ကိုနှိပ်ခြင်းဖြင့် ပရောဂျက်ကို ပြန်လည်စုစည်းပါ။

အဆင့် 3- ဒီဇိုင်းအပိုင်းများကို ဖန်တီးခြင်း။

သင်သည် တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်လိုသော PR ဒေသတစ်ခုစီအတွက် ဒီဇိုင်းအပိုင်းများကို ဖန်တီးရပါမည်။ သင့်ဒီဇိုင်းတွင် သီးခြားခွဲခြမ်းများ သို့မဟုတ် PR နယ်ပယ်များကို သင်ဖန်တီးနိုင်သည်။ ဤသင်ခန်းစာသည် u_blinking_led_child နှင့် u_blinking_led ဖြစ်ရပ်များအတွက် ဒီဇိုင်းအပိုင်းနှစ်ခုကို ဖန်တီးပေးသည်။

hierarchical partial reconfiguration အတွက် ဒီဇိုင်းအပိုင်းများကို ဖန်တီးရန်-

- Project Navigator ရှိ u_blinking_led_child instance ကို right-click နှိပ်ပြီး Design Partition ➤ Design Partition အဖြစ် သတ်မှတ်ပါ။ အခန်းကန့်တစ်ခုအဖြစ်သတ်မှတ်ထားသည့် instance တစ်ခုစီ၏ဘေးတွင် ဒီဇိုင်းအပိုင်းပိုင်းအိုင်ကွန်တစ်ခုပေါ်လာသည်။

ပုံ 3။ Project Navigator မှ ဒီဇိုင်းအပိုင်းများကို ဖန်တီးခြင်း။

- အခန်းကန့်အမျိုးအစားကို သတ်မှတ်ရန်၊ Hierarchy တက်ဘ်ရှိ u_blinking_led_child instance ကို right-click နှိပ်ပြီး Design Partition ➤ ပြန်လည်ပြင်ဆင်နိုင်သောကို နှိပ်ပါ။ instance ကို partition တစ်ခုအဖြစ် သတ်မှတ်ပြီးမှသာ partition Type ကို သတ်မှတ်နိုင်ပါတယ်။ ဒီဇိုင်းအပိုင်းသည် Assignments တွင်ပေါ်လာသည်။ View Design Partitions Window ၏ tab

ပုံ 4. Design Partitions Window

- အမည်ကို နှစ်ချက်နှိပ်ခြင်းဖြင့် အပိုင်းခွဲအမည်ကို ဒီဇိုင်းအပိုင်းများဝင်းဒိုးတွင် တည်းဖြတ်ပါ။ ဤအကိုးအကားဒီဇိုင်းအတွက်၊ အခန်းကန့်အမည်ကို pr_partition သို့ အမည်ပြောင်းပါ။

မှတ်ချက် - အခန်းကန့်တစ်ခုကို သင်ဖန်တီးသောအခါ၊ Intel Quartus Prime ဆော့ဖ်ဝဲလ်သည် instance အမည်နှင့် အထက်အောက် လမ်းကြောင်းပေါ်အခြေခံ၍ အခန်းကန့်အမည်ကို အလိုအလျောက်ထုတ်ပေးပါသည်။ ဤမူလအပိုင်းခွဲအမည်သည် ဥပမာတစ်ခုစီနှင့် ကွဲပြားနိုင်သည်။ - u_blinking_led စံနမူနာသို့ ပြန်လည်ပြင်ဆင်နိုင်သော ဒီဇိုင်းအပိုင်းများကို သတ်မှတ်ရန် အဆင့် ၁ နှင့် ၂ ကို ပြန်လုပ်ပါ။ ဤအခန်းကန့်ကို pr_parent_partition သို့ အမည်ပြောင်းပါ။

blinking_led.qsf တွင် သင်၏ပြန်လည်ပြင်ဆင်နိုင်သော ဒီဇိုင်းအပိုင်းပိုင်းများနှင့် သက်ဆိုင်သော အောက်ပါတာဝန်များ ပါဝင်ကြောင်း အတည်ပြုပါ-

တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်းအတွက် ဒီဇိုင်းအပိုင်းများကို ဖန်တီးပါ။

အဆင့် 4- PR Partitions အတွက် နေရာချထားခြင်းနှင့် လမ်းကြောင်းသတ်မှတ်ခြင်း တိုင်းဒေသကြီး

အခြေခံပြန်လည်ပြင်ဆင်မှုကို သင်ဖန်တီးသောအခါ၊ PR ဒီဇိုင်းစီးဆင်းမှုသည် သက်ဆိုင်ရာ persona core ကို reserved region တွင်ထားရန် သင်၏ PR partition ဒေသခွဲဝေမှုကို အသုံးပြုသည်။ သင်၏အခြေခံပြန်လည်ပြင်ဆင်မှုအတွက် စက်ကြမ်းပြင်အစီအစဥ်ရှိ PR ဒေသကို ရှာဖွေပြီး သတ်မှတ်သတ်မှတ်ရန်-

- Project Navigator ရှိ u_blinking_led_child instance ကို right-click နှိပ်ပြီး Logic Lock Region ➤ New Logic Lock Region ကိုဖန်တီးပါ။ ဒေသသည် Logic Lock Regions Window တွင်ပေါ်လာသည်။

- သင်၏နေရာချထားမှုဒေသသည် blinking_led_child ယုတ္တိဗေဒကို ခိုင်ခံ့စေရမည်။ Chip Planner တွင် node ကိုရှာဖွေခြင်းဖြင့် နေရာချထားရာဒေသကို ရွေးချယ်ပါ။ Project Navigator ရှိ u_blinking_led_child ဒေသအမည်ကို ညာကလစ်နှိပ်ပြီး Locate Node ➤ Chip Planner တွင် Locate ကိုနှိပ်ပါ။

ပုံ 5. blinking_led အတွက် Chip Planner Node တည်နေရာ

- Logic Lock Regions ဝင်းဒိုးတွင်၊ မူလကော်လံရှိ နေရာချထားရာဒေသ သြဒိနိတ်များကို သတ်မှတ်ပါ။ မူလအစသည် ဒေသ၏ ဘယ်ဘက်အောက်ထောင့်နှင့် သက်ဆိုင်သည်။ ဟောင်းအတွက်ample၊ (X1 Y1) သြဒိနိတ်များဖြင့် နေရာချထားရန် (69 10) အဖြစ် မူလအစကို X69_Y10 အဖြစ် သတ်မှတ်ပါ။ Intel Quartus Prime ဆော့ဖ်ဝဲလ်သည် သင်သတ်မှတ်ပေးသည့် အမြင့်နှင့် အကျယ်ကို အခြေခံ၍ နေရာချထားရာဒေသအတွက် (X2 Y2) သြဒိနိတ်များ (ညာဘက်အပေါ်) ကို အလိုအလျောက် တွက်ချက်ပေးပါသည်။

မှတ်ချက် - ဤသင်ခန်းစာတွင် (X1 Y1) သြဒိနိတ်များ – (69 10) နှင့် နေရာချထားရာဒေသအတွက် အမြင့်နှင့် အကျယ် 20 ကို အသုံးပြုသည်။ blinking_led_child ယုတ္တိဗေဒကို ဖုံးအုပ်ပေးထားသည့် နေရာချထားမှုဒေသအတွက် မည်သည့်တန်ဖိုးကိုမဆို သတ်မှတ်ပါ။ - Reserved နှင့် Core-Only ရွေးစရာများကို ဖွင့်ပါ။

- Routing Region ရွေးချယ်မှုကို နှစ်ချက်နှိပ်ပါ။ Logic Lock Routing Region Settings Dialog Box ပေါ်လာပါမည်။

- Routing အမျိုးအစားအတွက် Fixed with expansion ကိုရွေးချယ်ပါ။ ဤရွေးချယ်မှုကို ရွေးချယ်ခြင်းသည် တိုးချဲ့မှု အရှည်ကို အလိုအလျောက် သတ်မှတ်ပေးပါသည်။

မှတ်ချက် - Fitter သည် အင်ဂျင်မှ မတူညီသော လူများကို လမ်းကြောင်းပြောင်းသည့်အခါ Fitter အတွက် အပိုပြောင်းလွယ်ပြင်လွယ်ပေးနိုင်ရန် လမ်းကြောင်းပြသည့်နေရာသည် နေရာချထားသည့်ဒေသထက် ပိုကြီးရပါမည်။ - u_blinking_led ဥပမာအတွက် အဆင့် 1 -6 ကို ပြန်လုပ်ပါ။ မိဘအဆင့်နေရာချထားမှု u_blinking_led ဥပမာအတွက် အဆင့် 1 -6 ကို ထပ်လုပ်ပါ။ မိဘအဆင့် နေရာချထားမှု နယ်မြေသည် မိဘအဆင့် ယုတ္တိဗေဒနေရာချထားမှုအတွက် လုံလောက်သောနေရာလွတ်ခွင့်ပြုထားပြီး သက်ဆိုင်ရာ ကလေးအဆင့်နေရာချထားမှုနှင့် လမ်းကြောင်းသတ်မှတ်သည့်နေရာများကို အပြည့်အဝထည့်သွင်းရပါမည်။ ဤသင်ခန်းစာတွင် (X1 Y1) သြဒိနိတ်များ – (66 7)၊ အမြင့် 47 နှင့် u_blinking_led ဥပမာ၏နေရာချထားမှုဧရိယာအတွက် အကျယ် 26 ကိုအသုံးပြုသည်။

ပုံ 6.Logic Lock Regions Window

blinking_led.qsf တွင် သင့်ကြမ်းပြင်အစီအစဉ်နှင့် သက်ဆိုင်သော အောက်ပါတာဝန်များ ပါဝင်ကြောင်း အတည်ပြုပါ-

- Partial Reconfiguration Design ကို ကြမ်းပြင်ရေးဆွဲပါ။

- တစ်စိတ်တစ်ပိုင်း ပြန်လည်ဖွဲ့စည်းမှုကို ဖြည်းဖြည်းချင်း အကောင်အထည်ဖော်ခြင်း။

အဆင့် 5- Intel Arria 10 Partial Reconfiguration Controller IP Core ကို ထည့်ခြင်း။

- PR အခန်းကန့်ကို ပြန်လည်ပြင်ဆင်ရန်အတွက် Intel Arria 10 Partial Reconfiguration Controller IP core ကို အသုံးပြုပါ။ ဤ IP core သည် J ကိုအသုံးပြုသည်။TAG PR အခန်းကန့်ကို ပြန်လည်ပြင်ဆင်ရန်။ Intel Arria 10 Partial Reconfiguration Controller IP core ကို သင်၏ Intel Quartus Prime ပရောဂျက်သို့ ထည့်ရန်-

- IP ကတ်တလောက်တွင် Partial Reconfiguration ကို ရိုက်ထည့်ပါ။

- IP Parameter Editor Pro ဝင်းဒိုးကို စတင်ရန်၊ IP စာကြည့်တိုက်မှ Intel Arria 10 Partial Reconfiguration Controller IP core ကို ရွေးချယ်ပြီး Add ကိုနှိပ်ပါ။

- New IP Variant dialog box တွင် pr_ip ကို ရိုက်ထည့်ပါ။ file အမည်နှင့် Create ကိုနှိပ်ပါ။ pr_ip အတွက် မူရင်းသတ်မှတ်ချက်ကို အသုံးပြုပါ။ Enable J ကိုသေချာစေပါ။TAG အမှားရှာပြင်မုဒ်နှင့် အေးခဲသောအင်တာဖေ့စကိုဖွင့်ရန် ရွေးချယ်စရာများကို ဖွင့်ထားပြီး Avalon-MM slave အင်တာဖေ့စကိုဖွင့်ရန် ရွေးချယ်မှုကို ပိတ်ထားသည်။

ပုံ 7. Intel Arria 10 Partial Reconfiguration Controller IP Core ကန့်သတ်ချက်များ

- Finish ကိုနှိပ်ပါ၊ စနစ်မထုတ်ဘဲ ပါရာမီတာတည်းဖြတ်မှုမှ ထွက်ပါ။ Intel Quartus Prime ဆော့ဖ်ဝဲသည် pr_ip.ip IP ကွဲပြားမှုကို ဖန်တီးပေးသည်။ file, နှင့် adds file blinking_led ပရောဂျက်သို့။

မှတ်ချက် -

- အကယ်၍ သင်သည် pr_ip.ip ကိုကူးယူပါ။ file hpr ဖိုင်တွဲမှ၊ blinking_led.qsf ကို ကိုယ်တိုင် တည်းဖြတ်ပါ။ file အောက်ပါစာကြောင်းကို ထည့်သွင်းရန်- set_global_assignment -name IP_FILE pr_ip.ip

- IP_ကို နေရာချပါFILE SDC_ ပြီးနောက် တာဝန်၊FILE တာဝန်များ (ညtagသင်၏ blinking_led.qsf တွင် .sdc နှင့် blinking_led.sdc) file. ဤအမိန့်စာသည် Partial Reconfiguration IP core ၏ သင့်လျော်သော ကန့်သတ်မှုကို သေချာစေသည်။

မှတ်ချက် - နာရီများကိုထောက်လှမ်းရန်၊ SDC file PR IP အတွက် IP core အသုံးပြုသည့် နာရီများကို ဖန်တီးပေးသည့် SDC တိုင်းကို လိုက်နာရမည်ဖြစ်သည်။ သင်သည် .ip ကိုသေချာစေခြင်းဖြင့် ဤအမှာစာကို အဆင်ပြေချောမွေ့စေပါသည်။ file PR IP core သည် .ip တစ်ခုခုနောက်တွင် ပါလာသည်။ files သို့မဟုတ် SDC fileQSF တွင် ဤနာရီများကို ဖန်တီးရန် အသုံးပြုသည်။ file သင်၏ Intel Quartus Prime ပရောဂျက်ပြန်လည်ပြင်ဆင်မှုအတွက်။ ပိုမိုသိရှိလိုပါက၊ Partial Reconfiguration IP Core အသုံးပြုသူလမ်းညွှန်ရှိ Timing Constraints ကဏ္ဍကို ကိုးကားပါ။

ဆက်စပ်အချက်အလက်

- Partial Reconfiguration IP Solutions အသုံးပြုသူလမ်းညွှန်

- Partial Reconfiguration Region Controller IP core ဆိုင်ရာ အချက်အလက်အတွက်။

- တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း IP Core အသုံးပြုသူလမ်းညွှန်

- အချိန်ကန့်သတ်ချက်များဆိုင်ရာ အချက်အလက်များအတွက်။

ထိပ်တန်းအဆင့် ဒီဇိုင်းကို အပ်ဒိတ်လုပ်ခြင်း။

top.SV ကို အပ်ဒိတ်လုပ်ရန် file PR_IP ဥပမာဖြင့်

- PR_IP စံနမူနာကို ထိပ်တန်းအဆင့် ဒီဇိုင်းသို့ ထည့်ရန်၊ ထိပ်တွင် အောက်ပါ ကုဒ်ပိတ်ဆို့ခြင်းကို မှတ်ချက်ရေးပါ။SV file:

- ပြန်လည်ဖွဲ့စည်းမှုအတွင်း အထွက်ပေါက်များကို logic 1 သို့ တွန်းအားပေးရန်၊ PR_IP မှ အေးခဲထိန်းချုပ်မှု အချက်ပြအထွက်ကို အသုံးပြုပါ။ သို့သော်၊ PR ပရိုဂရမ်ကို ကလေးအခန်းကန့်ကို လုပ်ဆောင်နေချိန်တွင် ပင်မ PR အကန့်မှ မှိတ်တုတ်မှိတ်တုတ်မှိတ်တုတ်မှိတ်တုတ်မှိတ်တုတ်မှိတ်တုတ် LED သည် ဆက်လက်စောင့်ကြည့်ရန်၊ freeze control signal သည် led_two_on ကို ပိတ်မည်မဟုတ်ပါ။ pr_led_two_on သည် တိုက်ရိုက်ဖြစ်ကြောင်း သေချာပါစေ။

- မူရင်းမိဘပုဂ္ဂိုလ် (blinking_led) ၏ ဥပမာတစ်ခုကို သတ်မှတ်ရန်၊ top.SV ကို အပ်ဒိတ်လုပ်ပါ။ file အောက်ဖော်ပြပါ ကုဒ်ဘလော့ဂ်ဖြင့်

ပုံ 8. Partial Reconfiguration IP Core ပေါင်းစပ်မှု

အဆင့် 6- ပုဂ္ဂိုလ်များကို သတ်မှတ်ခြင်း။

ဤအကိုးအကားဒီဇိုင်းသည် မိဘနှင့်ကလေး PR အပိုင်းများအတွက် သီးခြားပုဂ္ဂိုလ်ငါးဦးကို သတ်မှတ်ပေးသည်။ သင့်ပရောဂျက်တွင် လူပုဂ္ဂိုလ်များကို သတ်မှတ်ရန်နှင့် ထည့်သွင်းရန်-

- SystemVerilog လေးခုဖန်တီးပါ။ files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv, နှင့် blinking_led_slow.sv စသည့် ပုဂ္ဂိုလ်ငါးဦးအတွက် သင့်လုပ်ဆောင်နေသော လမ်းညွှန်ချက်။

မှတ်ချက် - SystemVerilog ကိုဖန်တီးလျှင် files Intel Quartus Prime Text Editor မှ Add ကို ပိတ်ပါ။ file သိမ်းဆည်းသောအခါတွင် လက်ရှိ ပရောဂျက်ရွေးချယ်မှုသို့ files.

ဇယား ၂။ ရည်ညွှန်းဒီဇိုင်း ပုဂ္ဂိုလ်များ

| File နာမည် | ဖော်ပြချက် | ကုတ် |

| blinking_led_child.sv | ကလေးအဆင့် ဒီဇိုင်းအတွက် မူရင်းပုဂ္ဂိုလ် |

`timescale 1 ps / 1 ps `default_nettype none module မှိတ်တုတ်မှိတ်တုတ်_led_child ( // နာရီ input ဝါယာကြိုးနာရီ၊ အဝင်ဝါယာကြိုး [31:0] တန်ပြန်၊

// LEDs အထွက်ဝါယာကြိုး led_three_on အတွက် ထိန်းချုပ်အချက်ပြမှုများ

); localparam COUNTER_TAP = 23; reg led_three_on_r;

led_three_on = led_three_on_r ; always_ff @(posdge clock) စတင်သည်။ led_three_on_r <= တန်ပြန်[COUNTER_TAP]; အဆုံး

endmodule |

| ဆက်ရန်… | ||

| File နာမည် | ဖော်ပြချက် | ကုတ် |

| blinking_led_child_slow.sv | ဟိ

LED_THREE မျက်တောင်ခတ်တာ နှေးတယ်။ |

`timescale 1 ps / 1 ps `default_nettype မရှိပါ။

မော်ဂျူး blinking_led_child_slow (

// နာရီ input ဝါယာကြိုးနာရီ၊ အဝင်ဝါယာကြိုး [31:0] တန်ပြန်၊

// LEDs အထွက်ဝါယာကြိုး led_three_on အတွက် ထိန်းချုပ်အချက်ပြမှုများ );

localparam COUNTER_TAP = 27; reg led_three_on_r;

led_three_on = led_three_on_r ; always_ff @(posdge clock) စတင်သည်။ led_three_on_r <= တန်ပြန်[COUNTER_TAP]; အဆုံး

endmodule |

| blinking_led_child_empty.sv | ဟိ

LED_THREE ON ထားသည်။ |

`timescale 1 ps / 1 ps `default_nettype မရှိပါ။

မော်ဂျူး blinking_led_child_ဗလာ (

// နာရီ input ဝါယာကြိုးနာရီ၊ အဝင်ဝါယာကြိုး [31:0] တန်ပြန်၊

// LEDs အထွက်ဝါယာကြိုး led_three_on အတွက် ထိန်းချုပ်အချက်ပြမှုများ

);

// LED သည် တက်ကြွမှုနည်းသည်။ led_three_on = 1'b0;

endmodule |

| blinking_led_slow.sv | LED_TWO

မျက်တောင်ခတ်တာ နှေးတယ်။ |

`timescale 1 ps / 1 ps `default_nettype none module မှိတ်တုတ်မှိတ်တုတ်_led_slow( // နာရီ input ဝါယာကြိုးနာရီ၊ အဝင်ဝါယာကြိုး [31:0] တန်ပြန်၊

// LEDs အထွက်ဝါယာကြိုးများအတွက် ထိန်းချုပ်အချက်ပြမှုများ led_two_on၊ အထွက်ဝါယာကြိုး led_three_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; led_two_on = led_two_on_r;

// ကောင်တာ: always_ff @(ပုံဆောင်နာရီ) စတင် led_two_on_r <= counter[COUNTER_TAP]; အဆုံး

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on)၊ ။counter (ကောင်တာ)၊ နာရီ (နာရီ) |

| File နာမည် | ဖော်ပြချက် | ကုတ် |

| );ndmodule |

အဆင့် 3- စာမျက်နှာ 7 ရှိ ဒီဇိုင်းအပိုင်းများကို ဖန်တီးခြင်း။

အဆင့် 7- တည်းဖြတ်မှုများကို ဖန်တီးခြင်း။

PR ဒီဇိုင်းစီးဆင်းမှုသည် Intel Quartus Prime ဆော့ဖ်ဝဲလ်တွင် ပရောဂျက်ပြန်လည်ပြင်ဆင်ခြင်းအင်္ဂါရပ်ကို အသုံးပြုသည်။ သင့်၏ကနဦးဒီဇိုင်းသည် FPGA တွင် တည်ငြိမ်ဒေသနယ်နိမိတ်များနှင့် ပြန်လည်ပြင်ဆင်နိုင်သော ဒေသများကို သတ်မှတ်ပေးသည့် အခြေခံပြန်လည်ပြင်ဆင်မှုဖြစ်သည်။ အခြေခံတည်းဖြတ်မှုမှ၊ သင်သည် ပြန်လည်ပြင်ဆင်မှုများစွာကို ဖန်တီးသည်။ ဤပြင်ဆင်ချက်များတွင် PR ဒေသများအတွက် မတူညီသော အကောင်အထည်ဖော်မှုများ ပါဝင်သည်။ သို့သော်၊ PR အကောင်အထည်ဖော်မှု ပြန်လည်ပြင်ဆင်မှုအားလုံးသည် အခြေခံပြန်လည်ပြင်ဆင်မှုမှ တူညီသောထိပ်တန်းအဆင့်နေရာချထားမှုနှင့် လမ်းကြောင်းသတ်မှတ်ခြင်းရလဒ်များကို အသုံးပြုသည်။ PR ဒီဇိုင်းကို စုစည်းရန်၊ လူတစ်ဦးစီအတွက် PR အကောင်အထည်ဖော်မှု ပြန်လည်ပြင်ဆင်မှုနှင့် ပေါင်းစပ်ပြင်ဆင်မှုတစ်ခုကို ဖန်တီးရပါမည်။ ဤအကိုးအကားဒီဇိုင်းတွင်၊ အခြေခံပြန်လည်ပြင်ဆင်မှု (blinking_led) အပြင် ကလေးအဆင့်ပုဂ္ဂိုလ်သုံးဦးနှင့် မိဘအဆင့်ပုဂ္ဂိုလ်နှစ်ဦးတို့သည် သီးခြားပေါင်းစပ်ပြင်ဆင်မှုငါးခုနှင့် သီးခြားအကောင်အထည်ဖော်မှုပြင်ဆင်ချက်ငါးခုပါရှိသည်။

ဇယား ၃။ မိဘနှစ်ပါးနှင့် ကလေးသုံးယောက်အတွက် ပြန်လည်ပြင်ဆင်မှုများ

| Synthesis Revision | အကောင်အထည်ဖော်ရေး ပြန်လည်ပြင်ဆင်ခြင်း။ |

| blinking_led_parent၊ blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent၊ blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent၊ blinking_led_child_ဗလာ | blinking_led_pr_charlie |

| blinking_led_parent_slow၊ blinking_led_child_slow | blinking_led_pr_delta |

| blinking_led_parent_slow၊ blinking_led_child_ဗလာ | blinking_led_pr_emma |

အကောင်အထည်ဖော်မှု ပြင်ဆင်ချက်များကို ဖန်တီးခြင်း။

PR အကောင်အထည်ဖော်မှု ပြန်လည်ပြင်ဆင်မှုများကို ဖန်တီးရန်-

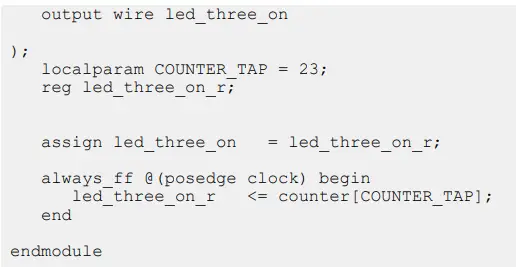

- Revisions dialog box ကိုဖွင့်ရန်၊ Project ➤ Revisions ကိုနှိပ်ပါ။

- တည်းဖြတ်မှုအသစ်ဖန်တီးရန် <ကိုနှစ်ချက်နှိပ်ပါ။ >

- တည်းဖြတ်မှုအမည်ကို blinking_led_pr_alpha အဖြစ် သတ်မှတ်ပြီး ပြုပြင်မှုအပေါ်အခြေခံ၍ blinking_led ကို ရွေးချယ်ပါ။

- Set as current revision option ကို ပိတ်ပြီး OK ကိုနှိပ်ပါ။

- အလားတူ၊ blinking_led_pr_bravo၊ blinking_led_pr_charlie၊ blinking_led_pr_delta နှင့် blinking_led_pr_emma တည်းဖြတ်မှုများကို အခြေခံ၍ blinking_led_pr_emma ပြင်ဆင်မှုများကို ပြုလုပ်ပါ။

မှတ်ချက် - အထက်ပါပြင်ဆင်ချက်များကို လက်ရှိပြင်ဆင်မှုအဖြစ် မသတ်မှတ်ပါနှင့်။

ပုံ ၉။ ပြင်ဆင်မှုများ ဖန်တီးခြင်း။

Synthesis-Only Revisions ဖန်တီးခြင်း။

ပုဂ္ဂိုလ်များအတွက် ပေါင်းစပ်သီးသန့် တည်းဖြတ်မှုများကို ဖန်တီးရန်၊ သင်သည် ထိပ်တန်းအဆင့် အဖွဲ့အစည်းနှင့် သက်ဆိုင်ရာ SystemVerilog ကို တာဝန်ပေးရပါမည်။ file ပုဂ္ဂိုလ်တစ်ဦးချင်းစီအတွက်

- Intel Quartus Prime ဆော့ဖ်ဝဲတွင်၊ Project ➤ ပြန်လည်ပြင်ဆင်မှုများကို နှိပ်ပါ။

- blinking_led_led တည်းဖြတ်မှုကို အခြေခံ၍ blinking_led_default တည်းဖြတ်မှုကို ဖန်တီးပါ။ ဤပြင်ဆင်ချက်ကို လက်ရှိတည်းဖြတ်မှုအဖြစ် မသတ်မှတ်ပါနှင့်။

- blinking_led_default.qsf ကို ပြင်ဆင်ပါ။ file အောက်ပါတာဝန်များကို ထည့်သွင်းရန်-

set_global_assignment -name TOP_LEVEL_ENTITY မှိတ်တုတ်မှိတ်တုတ်_led_child

set_global_assignment -name SYSTEMVERILOG_FILE - အလားတူပင်၊ blinking_led_child_slow၊ blinking_led_child_empty၊ blinking_led_parent၊ နှင့် blinking_led_parent_slow တည်းဖြတ်မှုများကို ဖန်တီးပါ။ ဤပြင်ဆင်ချက်များကို လက်ရှိပြင်ဆင်မှုများအဖြစ် မသတ်မှတ်ပါနှင့်။

- blinking_led_child_slow.qsf၊ blinking_led_child_empty.qsf၊ blinking_led_parent.qsf နှင့် blinking_led_parent_slow.qsf ကို အပ်ဒိတ်လုပ်ပါ files သူတို့ရဲ့သက်ဆိုင်ရာ

TOP_LEVEL_ENTITY နှင့် SYSTEMVERILOG_FILE တာဝန်များ-

- ပေါင်းစပ်မှုအမှားများကိုရှောင်ရှားရန်, ပေါင်းစပ်ပြန်လည်ပြင်ဆင်မှုကိုသေချာပါစေ။ fileကလေးအပိုင်းခွဲများအတွက် s တွင် ဒီဇိုင်းအပိုင်းပိုင်း၊ pin assignments သို့မဟုတ် Logic Lock မပါဝင်ပါ။

ဒေသတာဝန်များ။ ပေါင်းစပ်ပြင်ဆင်မှုလည်းဖြစ်သည်။ fileparent partitions များအတွက် s တွင် သက်ဆိုင်ရာ child partitions များအတွက် design partition assignments များသာ ပါဝင်ရပါမည်။ blinking_led_default.qsf၊ blinking_led_child_slow.qsf၊ blinking_led_child_empty.qsf၊ blinking_led_parent.qsf နှင့် blinking_led_parent_slow.pdf တွင်ရှိပါက ဤတာဝန်များကို ဖယ်ရှားပါ files

- blinking_led_parent.qsf နှင့် blinking_led_parent_slow.qsf တွင် အောက်ပါတာဝန်များကို ထည့်သွင်းပါ files:

- blinking_led.qpf ကို စစ်ဆေးပါ။ file အထူးအစီအစဥ်အရ အောက်ပါတည်းဖြတ်မှုများပါရှိသည်။

- မှတ်ချက် - တည်းဖြတ်မှု ကူးယူခြင်းဖြစ်ပါက files ကို hpr ဖိုင်တွဲမှ၊ blinking_led.qpf ကို ကိုယ်တိုင် အပ်ဒိတ်လုပ်ပါ။ file အထက်ပါ ကုဒ်လိုင်းများဖြင့်

ပြန်လည်ပြင်ဆင်မှု အမျိုးအစား သတ်မှတ်ခြင်း။

သင်၏ တည်းဖြတ်မှု တစ်ခုစီအတွက် တည်းဖြတ်မှု အမျိုးအစားကို သတ်မှတ်ရပါမည်။ ပြန်လည်ပြင်ဆင်မှု အမျိုးအစားသုံးမျိုး ရှိပါသည်။

- တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – အခြေခံ

- တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာပေါင်းစပ်မှု

- တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာ အကောင်အထည်ဖော်မှု

- အောက်ပါဇယားသည် တည်းဖြတ်မှုတစ်ခုစီအတွက် ပြန်လည်ပြင်ဆင်မှုအမျိုးအစားတာဝန်များကို စာရင်းပြုစုထားသည်။

ဇယား 4. ပြန်လည်ပြင်ဆင်မှု အမျိုးအစားများ

| တည်းဖြတ်မှုအမည် | ပြန်လည်ပြင်ဆင်မှု အမျိုးအစား |

| blinking_led.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – အခြေခံ |

| blinking_led_default.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာပေါင်းစပ်မှု |

| blinking_led_child_empty.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာပေါင်းစပ်မှု |

| blinking_led_child_slow.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာပေါင်းစပ်မှု |

| blinking_led_parent.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာပေါင်းစပ်မှု |

| blinking_led_parent_slow.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာပေါင်းစပ်မှု |

| blinking_led_pr_alpha.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာ အကောင်အထည်ဖော်မှု |

| blinking_led_pr_bravo.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာ အကောင်အထည်ဖော်မှု |

| blinking_led_pr_charlie.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာ အကောင်အထည်ဖော်မှု |

| blinking_led_pr_delta.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာ အကောင်အထည်ဖော်မှု |

| blinking_led_pr_emma.qsf | တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း – ပုဂ္ဂိုလ်ရေးဆိုင်ရာ အကောင်အထည်ဖော်မှု |

- ပရောဂျက် ➤ ပြန်လည်ပြင်ဆင်မှုများကို နှိပ်ပါ။ Revisions dialog box ပေါ်လာပါမယ်။

- ပြန်လည်ပြင်ဆင်မှုအမည်ကော်လံတွင် blinking_led ကိုရွေးချယ်ပြီး လက်ရှိသတ်မှတ်မည်ကို နှိပ်ပါ။

- Apply ကိုနှိပ်ပါ။ blinking_led တည်းဖြတ်မှု ဖွင့်သည်။

- blinking_led အတွက် ပြန်လည်ပြင်ဆင်မှု အမျိုးအစားကို သတ်မှတ်ရန်၊ Assignments ➤ ဆက်တင်များ ➤ အထွေထွေကို နှိပ်ပါ။

- Partial Reconfiguration – Base အဖြစ် ပြန်လည်ပြင်ဆင်မှု အမျိုးအစားကို ရွေးချယ်ပါ။

- အလားတူ၊ အထက်ဇယားတွင်ဖော်ပြထားသည့်အတိုင်း အခြားပြန်လည်ပြင်ဆင်မှုဆယ်ခုအတွက် ပြန်လည်ပြင်ဆင်မှုအမျိုးအစားများကို သတ်မှတ်ပါ။

- မှတ်ချက် - တည်းဖြတ်မှု အမျိုးအစားကို မသတ်မှတ်မီ တည်းဖြတ်မှုတစ်ခုစီကို လက်ရှိတည်းဖြတ်မှုအဖြစ် သတ်မှတ်ရပါမည်။ .qsf တစ်ခုစီကို စစ်ဆေးပါ။ file အောက်ပါတာဝန်ပါရှိသည်-

- မှတ်ချက် - PR အကောင်အထည်ဖော်မှုတွင် သင်အသုံးပြုလိုသည့် Fitter သီးသန့်ဆက်တင်များကို ပေါင်းထည့်ပါ။ Fitter သီးသန့်ဆက်တင်များသည် လူပုဂ္ဂိုလ်၏ အံဝင်ခွင်ကျမှုကို သက်ရောက်မှုရှိသော်လည်း တင်သွင်းထားသော အငြိမ်ဒေသကို မထိခိုက်စေပါ။ ပေါင်းစပ်ဖွဲ့စည်းမှုဆိုင်ရာ သီးခြားဆက်တင်များကို လူတစ်ဦးချင်းစီ၏ ပေါင်းစပ်မှုဆိုင်ရာ ပြန်လည်ပြင်ဆင်မှုများကိုလည်း ထည့်သွင်းနိုင်သည်။

Personas အတွက် ပြင်ဆင်မှုများ ပြုလုပ်ပါ။

အဆင့် 8- Hierarchical Partial Reconfiguration Flow Script ကို ထုတ်လုပ်ခြင်း။

အထက်အောက် တစ်စိတ်တစ်ပိုင်း ပြန်လည်ဖွဲ့စည်းမှု စီးဆင်းမှု script ကို ထုတ်လုပ်ရန်-

- Intel Quartus Prime command shell မှ၊ အောက်ပါ command ကို run ခြင်းဖြင့် flow template ကိုဖန်တီးပါ။

- Intel Quartus Prime သည် a10_hier_partial_reconfig/flow.tcl ကို ထုတ်ပေးသည်။ file.

- ထုတ်လုပ်ထားသော a10_hier_partial_reconfig/setup.tcl.ex ကို အမည်ပြောင်းပါ။ampa10_hier_partial_reconfig/setup.tcl သို့သွား၍ သင်၏ တစ်စိတ်တစ်ပိုင်း ပြန်လည်ဖွဲ့စည်းမှု ပရောဂျက်အသေးစိတ်များကို သတ်မှတ်ရန် script ကို ပြင်ဆင်ပါ-

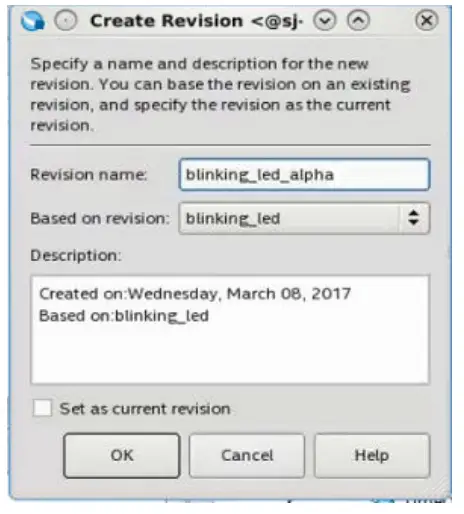

a. ပရောဂျက်၏အမည်ကို သတ်မှတ်ရန်၊ အောက်ပါစာကြောင်းကို အပ်ဒိတ်လုပ်ပါ။ b. အခြေခံပြင်ဆင်ချက်ကို သတ်မှတ်ရန်၊ အောက်ပါစာကြောင်းကို အပ်ဒိတ်လုပ်ပါ။

b. အခြေခံပြင်ဆင်ချက်ကို သတ်မှတ်ရန်၊ အောက်ပါစာကြောင်းကို အပ်ဒိတ်လုပ်ပါ။

- တစ်စိတ်တစ်ပိုင်း ပြန်လည်ဖွဲ့စည်းမှု အကောင်အထည်ဖော်မှု တည်းဖြတ်မှုတစ်ခုစီကို သတ်မှတ်ရန်၊ PR အခန်းကန့်အမည်များနှင့် တည်းဖြတ်မှုများကို အကောင်အထည်ဖော်သည့် အရင်းအမြစ်တည်းဖြတ်မှုနှင့်အတူ၊ အောက်ပါလိုင်းများကို အပ်ဒိတ်လုပ်ပါ။

မှတ်ချက် - ပြန်လည်ပြင်ဆင်မှု ပရောဂျက်အားလုံးသည် blinking_led.qpf ကဲ့သို့ တူညီသောလမ်းညွှန်တွင် ရှိရပါမည်။ မဟုတ်ပါက flow script ကို အလိုက်သင့် အပ်ဒိတ်လုပ်ပါ။

အဆင့် 9- Hierarchical Partial Reconfiguration Flow Script ကို လုပ်ဆောင်ခြင်း။

အထက်အောက် တစ်စိတ်တစ်ပိုင်း ပြန်လည်ဖွဲ့စည်းမှု စီးဆင်းမှု script ကို လုပ်ဆောင်ရန်-

- Tools ➤ Tcl Scripts ကိုနှိပ်ပါ။ Tcl Scripts dialog box ပေါ်လာသည်။

- Add to Project ကိုနှိပ်ပါ၊ ရှာဖွေပြီး a10_hier_partial_reconfig/flow.tcl ကို ရွေးပါ။

- Libraries pane ရှိ a10_hier_partial_reconfig/flow.tcl ကို ရွေးပြီး Run ကို နှိပ်ပါ။

ဤဇာတ်ညွှန်းသည် လူသုံးဦးအတွက် ပေါင်းစပ်မှုကို လုပ်ဆောင်သည်။ Intel Quartus Prime သည် SRAM Object ကိုထုတ်ပေးသည်။ File (.sof)၊ Partial-Masked SRAM Object တစ်ခု File (.pmsf) နှင့် Raw Binary တစ်ခု File ပုဂ္ဂိုလ်တစ်ဦးစီအတွက် (.rbf)။

မှတ်ချက်- Intel Quartus Prime command shell မှ script ကို run ရန်၊ အောက်ပါ command ကို ရိုက်ထည့်ပါ။

- Partial Reconfiguration Design ကို စုစည်းပါ။

- Partial Reconfiguration Flow Script ကို အသုံးပြုခြင်း။

- Partial Reconfiguration Flow Script ကို ပြင်ဆင်ခြင်း

- Programming ကို ဖန်တီးပါ။ Files

အဆင့် 10- ပရိုဂရမ်ရေးဆွဲခြင်း။

သင်မစတင်မီ-

- ပါဝါထောက်ပံ့မှုကို Intel Arria 10 SoC ဖွံ့ဖြိုးတိုးတက်မှုဘုတ်အဖွဲ့သို့ ချိတ်ဆက်ပါ။

- သင့် PC USB ပေါက်နှင့် USB Blaster အပေါက်ကြားရှိ USB Blaster ကြိုးကို ဖွံ့ဖြိုးတိုးတက်မှုဘုတ်အဖွဲ့တွင် ချိတ်ဆက်ပါ။

Intel Arria 10 SoC ဖွံ့ဖြိုးတိုးတက်မှုဘုတ်အဖွဲ့တွင် ဒီဇိုင်းကို လုပ်ဆောင်ရန်-

- Intel Quartus Prime ဆော့ဖ်ဝဲကိုဖွင့်ပြီး ကိရိယာများ ➤ ပရိုဂရမ်မာကို နှိပ်ပါ။

- Programmer တွင် Hardware Setup ကိုနှိပ်ပြီး USB-Blaster ကိုရွေးချယ်ပါ။

- Auto Detect ကိုနှိပ်ပြီး 10AS066N3 စက်ပစ္စည်းကို ရွေးချယ်ပါ။

- OK ကိုနှိပ်ပါ။ Intel Quartus Prime ဆော့ဖ်ဝဲလ်သည် ပရိုဂရမ်မာအား ဘုတ်ပေါ်ရှိ FPGA ချစ်ပ်သုံးခုဖြင့် ရှာဖွေပြီး အပ်ဒိတ်လုပ်သည်။

- 10AS066N3 စက်ပစ္စည်းကို ရွေးပါ၊ Change ကိုနှိပ်ပါ။ File blinking_led_pr_alpha.sof ကိုဖွင့်ပါ။ file.

- blinking_led_pr_alpha.sof အတွက် ပရိုဂရမ်/Configure ကိုဖွင့်ပါ။ file.

- Start ကိုနှိပ်ပြီး 100% ရောက်ရန် တိုးတက်မှုဘားကို စောင့်ပါ။

- မူလပြားချပ်ချပ်ဒီဇိုင်းနှင့် တူညီသောကြိမ်နှုန်းဖြင့် ဘုတ်ပေါ်ရှိ LED မီးများကို သတိပြုပါ။

- ကလေး PR ဒေသအတွက်သာ အစီအစဉ်ဆွဲရန်၊ blinking_led_pr_alpha.sof ကို ညာဖက်ကလစ်နှိပ်ပါ။ file Programmer တွင် Add PR Programming ကိုနှိပ်ပါ။ File.

- blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf ကို ရွေးပါ file.

- blinking_led_pr_alpha.sof အတွက် ပရိုဂရမ်/Configure ကို ပိတ်ပါ။ file.

- blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf အတွက် ပရိုဂရမ်ကိုဖွင့်ပါ/Configure file Start ကိုနှိပ်ပါ။ ဘုတ်ပေါ်တွင်၊ LED[0] နှင့် LED[1] ကို မျက်တောင်ခတ်နေသည် ကို သတိပြုပါ။ တိုးတက်မှုဘားသည် 100% သို့ရောက်ရှိသောအခါ LED[2] သည် တူညီသောနှုန်းဖြင့် မျက်တောင်ခတ်ပြီး LED[3] သည် ပိုမိုနှေးကွေးသွားပါသည်။

- မိဘနှင့်ကလေး PR ဒေသကို အစီအစဉ်ဆွဲရန်၊ .rbf ကို ညာကလစ်နှိပ်ပါ။ file Programmer တွင် Change PR Programing ကို နှိပ်ပါ။ File.

- blinking_led_pr_delta.pr_parent_partition.rbf ကို ရွေးပါ။ file.

- Start ကိုနှိပ်ပါ။ ဘုတ်ပေါ်တွင်၊ LED[0] နှင့် LED[1] သည် ဆက်လက် မှိတ်တုတ်မှိတ်တုတ် ဖြစ်နေသည်ကို သတိပြုပါ။ တိုးတက်မှုဘားသည် 100% ရောက်သောအခါ LED[2] နှင့် LED[3] နှစ်ခုစလုံးသည် မျက်တောင်ခတ်ခြင်းကို နှေးကွေးစေသည်။

- ကလေး PR ဒေသ သို့မဟုတ် မိဘနှင့် ကလေး PR ဒေသ နှစ်ခုလုံးကို တပြိုင်နက် ပြန်လည် အစီအစဉ်ချရန် အထက်ဖော်ပြပါ အဆင့်များကို ပြန်လုပ်ပါ။

ပုံ 10။ Intel Arria 10 SoC ဖွံ့ဖြိုးတိုးတက်ရေးဘုတ်အဖွဲ့ကို ပရိုဂရမ်ရေးဆွဲခြင်း။

ရှိပြီးသားပုဂ္ဂိုလ်ကို ပြုပြင်မွမ်းမံခြင်း။

- အခြေခံတည်းဖြတ်မှုကို အပြည့်အ၀ ပြုစုပြီးသည့်တိုင် ရှိပြီးသား ပုဂ္ဂိုလ်ကို ပြောင်းလဲနိုင်သည်။

- ဟောင်းအတွက်ample၊ မှိတ်တုတ်မှိတ်တုတ်_led_child_slow persona ကို ပို၍ပင် နှေးကွေးအောင် မျက်တောင်ခတ်စေသည်-

- blinking_led_child_slow.sv file၊ COUNTER_TAP ဘောင်ကို ၂၇ မှ ၂၈ အထိ မွမ်းမံပါ။

- ဤပုဂ္ဂိုလ်ကို ပြန်လည်ပေါင်းစပ်ပြီး ပြန်လည်အကောင်အထည်ဖော်ရန်၊ ပြောင်းလဲမှုကြောင့် သက်ရောက်မှုရှိသော ပေါင်းစပ်မှုသီးသန့်တည်းဖြတ်မှုများနှင့် အကောင်အထည်ဖော်မှုဆိုင်ရာ ပြင်ဆင်မှုများအားလုံးကို ပြန်လည်စုစည်းရပါမည်။ အောက်ပါစာကြောင်းများပါဝင်ရန် setup.tcl script ကိုမွမ်းမံပါ။

မှတ်ချက် - blinking_led_pr_delta တည်းဖြတ်မှုအတွက် pr_parent_parition ကို သတ်မှတ်သောအခါ၊ အကောင်အထည်ဖော်ရန်အတွက် သင်သည် ထိုပုဂ္ဂိုလ်၏ နောက်ဆုံးလျှပ်တစ်ပြက်ဓာတ်ပုံကို တင်သွင်းသည်။ ရလဒ်အနေဖြင့်၊ သက်ဆိုင်ရာကလေးအပိုင်းခွဲကို ပြင်ဆင်ခြင်းနှင့် အကောင်အထည်ဖော်နေစဉ်တွင် parent partition logic ကို အကောင်အထည်ဖော်ခြင်းသည် အတူတူပင်ဖြစ်ပါသည်။

မှတ်ချက် - blinking_led_pr_delta တည်းဖြတ်မှုအတွက် pr_parent_parition ကို သတ်မှတ်သောအခါ၊ အကောင်အထည်ဖော်ရန်အတွက် သင်သည် ထိုပုဂ္ဂိုလ်၏ နောက်ဆုံးလျှပ်တစ်ပြက်ဓာတ်ပုံကို တင်သွင်းသည်။ ရလဒ်အနေဖြင့်၊ သက်ဆိုင်ရာကလေးအပိုင်းခွဲကို ပြင်ဆင်ခြင်းနှင့် အကောင်အထည်ဖော်နေစဉ်တွင် parent partition logic ကို အကောင်အထည်ဖော်ခြင်းသည် အတူတူပင်ဖြစ်ပါသည်။ ဤ command သည် blinking_led_child_slow synthesis တည်းဖြတ်မှုကို ပြန်လည်ပေါင်းစပ်ပြီး blinking_led_pr_bravo ကို အသုံးပြု၍ PR အကောင်အထည်ဖော်မှုစုစည်းမှုကို လုပ်ဆောင်သည်။

ဤ command သည် blinking_led_child_slow synthesis တည်းဖြတ်မှုကို ပြန်လည်ပေါင်းစပ်ပြီး blinking_led_pr_bravo ကို အသုံးပြု၍ PR အကောင်အထည်ဖော်မှုစုစည်းမှုကို လုပ်ဆောင်သည်။ - ပေါင်းစပ်ဖွဲ့စည်းမှု-သီးသန့်ပြန်လည်ပြင်ဆင်မှုများကို လုပ်ဆောင်ရန် အောက်ပါ command ကို run ပါ- ဤ command သည် base recompile ကို မလုပ်ဆောင်ပါ။

- အကောင်အထည်ဖော်မှု ပြန်လည်ပြင်ဆင်မှုများကို စုစည်းလုပ်ဆောင်ရန်၊ အောက်ပါ command ကို run ပါ။

- ဤအမိန့်တော်သည် အခြေခံတည်းဖြတ်မှုကို ပြန်လည်ပေါင်းစည်းခြင်းမပြုပါ။

- အဆင့် 10 ရှိ အဆင့်များကို လိုက်နာပါ- ရလဒ် RBF ကို အစီအစဉ်ဆွဲရန် စာမျက်နှာ 22 တွင် ဘုတ်အဖွဲ့ကို ပရိုဂရမ်ပြုလုပ်ပါ။ file FPGA သို့။

မှတ်ချက် - တည်းဖြတ်မှုတိုင်းအတွက် စီးဆင်းမှုတစ်ခုလုံးကို လုပ်ဆောင်ခြင်းမှ ရှောင်ကြဉ်ရန်၊ setup.tcl script တွင် ပေါင်းစပ်သီးသန့်တည်းဖြတ်မှုများနှင့် အကောင်အထည်ဖော်မှုဆိုင်ရာ ပြင်ဆင်မှုများကို သတ်မှတ်ပြီး script ကို run ပါ။

ဒီဇိုင်းတွင် လူသစ်တစ်ဦးကို ထည့်သွင်းခြင်း။

သင်၏အခြေခံပြန်လည်ပြင်ဆင်မှုများကို အပြည့်အဝစုစည်းပြီးနောက်၊ သင်သည် လူသစ်များကိုထည့်သွင်းနိုင်ပြီး အဆိုပါပုဂ္ဂိုလ်များကို တစ်ဦးချင်းစုစည်းနိုင်သေးသည်။

ဟောင်းအတွက်ample၊ blinking_led_parent_slow အတွက် ကလေးပုဂ္ဂိုလ်အသစ်ကို သတ်မှတ်ရန်၊

- blinking_led_child_empty.sv ကို blinking_led_chdild_off.sv သို့ ကူးယူပါ။

- blinking_led_child_off.sv file, တာဝန်ကို ပြင်ဆင်ပါ၊ led_three_on = 1'b0 ကို သတ်မှတ်ပါ။ led_three_on = 1'b1; သတ်မှတ်ပေးရန်။ blinking_led_child_empty မှ blinking_led_child_off သို့ မော်ဂျူးအမည်ကို ပြောင်းလဲကြောင်း သေချာပါစေ။

- စာမျက်နှာ 16 ရှိ Synthesis-Only Revisions ဖန်တီးခြင်းတွင် အဆင့်များကို လိုက်နာခြင်းဖြင့် ပေါင်းစပ်ပြင်ဆင်မှုအသစ်၊ blinking_led_child_off ဖန်တီးပါ။

မှတ်ချက် - blinking_led_child_off ပြန်လည်ပြင်ဆင်မှုသည် blinking_led_child_off.sv ကို အသုံးပြုရမည် file. - စာမျက်နှာ 15 ရှိ အကောင်အထည်ဖော်မှု တည်းဖြတ်မှုများ ဖန်တီးခြင်းတွင် အဆင့်များကို လိုက်နာခြင်းဖြင့် blinking_led_pr_foxtrot အကောင်အထည်ဖော်မှု တည်းဖြတ်မှုအသစ်ကို ဖန်တီးပါ။

- a10_hier_partial_reconfig/setup.tcl ကို အပ်ဒိတ်လုပ်ပါ။ file PR အကောင်အထည်ဖော်မှုအသစ်ကို သတ်မှတ်ရန်-

- အောက်ပါ command ကို run ခြင်းဖြင့် ဤပေါင်းစပ်မှုအသစ်နှင့် အကောင်အထည်ဖော်မှု ပြန်လည်ပြင်ဆင်ချက်ကို စုစည်းပါ။

Intel Arria 10 စက်ပစ္စည်းများအတွက် အထက်အောက် တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်းဆိုင်ရာ အချက်အလက်အပြည့်အစုံအတွက်၊ Intel Quartus Prime Pro Edition Handbook အတွဲ 1 တွင် တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်မှုဒီဇိုင်းဖန်တီးခြင်းကို ကိုးကားပါ။

ဆက်စပ်အချက်အလက်

- Partial Reconfiguration Design ဖန်တီးခြင်း။

- Partial Reconfiguration အွန်လိုင်းသင်တန်း

စာရွက်စာတမ်း ပြန်လည်ပြင်ဆင်မှုမှတ်တမ်း

ဇယား ၂၆။ စာရွက်စာတမ်းပြန်လှန်မှတ်တမ်း

| စာရွက်စာတမ်းဗားရှင်း | software ဗားရှင်း | အပြောင်းအလဲများ |

| 2017.11.06 | 17.1.0 | • အပ်ဒိတ်လုပ်ထားသည်။ အကိုးအကား ဒီဇိုင်းလိုအပ်ချက်များ ဆော့ဖ်ဝဲဗားရှင်းနှင့်အတူအပိုင်း

• အပ်ဒိတ်လုပ်ထားသည်။ PR Partitioning မပါဘဲ Flat Reference Design ဒီဇိုင်းဘလောက်ပြောင်းလဲမှုနှင့်အတူပုံ • အပ်ဒိတ်လုပ်ထားသည်။ ရည်ညွှန်းဒီဇိုင်း Files ဇယားတွင် အချက်အလက်ပါရှိသည်။ Top_counter.sv မော်ဂျူး • အပ်ဒိတ်လုပ်ထားသည်။ Partial Reconfiguration IP Core ပေါင်းစပ်မှု ဒီဇိုင်းဘလောက်ပြောင်းလဲမှုနှင့်အတူပုံ • ကိန်းဂဏန်းများကို အပ်ဒိတ်လုပ်ခဲ့သည်- Design Partitions Window နှင့် Logic Lock Regions Window GUI အသစ်ကို ရောင်ပြန်ဟပ်ရန် • File အမည်ပြောင်းလဲခြင်း။ • စာသားတည်းဖြတ်မှုများ |

| 2017.05.08 | 17.0.0 | စာတမ်း၏ ကနဦးထုတ်ပြန်ချက် |

စာရွက်စာတမ်းများ / အရင်းအမြစ်များ

|

intel AN 805 Arria 10 SoC ဖွံ့ဖြိုးတိုးတက်ရေးဘုတ်အဖွဲ့တွင် ဒီဇိုင်းတစ်ခု၏ အထက်အောက် တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း [pdf] အသုံးပြုသူလမ်းညွှန် Arria 805 SoC ဖွံ့ဖြိုးတိုးတက်ရေးဘုတ်အဖွဲ့တွင် ဒီဇိုင်းတစ်ခု၏ 10 အထက်အောက် တစ်စိတ်တစ်ပိုင်း ပြန်လည်ပြင်ဆင်ခြင်း ဖွံ့ဖြိုးတိုးတက်ရေးအဖွဲ့ |