intel AN 805 Դիզայնի հիերարխիկ մասնակի վերակազմավորում Arria 10 SoC Development Board-ում

Hierarchical Partal Reconfiguration Tutorial Intel® Arria® 10 SoC Development Board-ի համար

Այս հավելվածի նշումը ցույց է տալիս պարզ դիզայնի վերափոխումը հիերարխիկ մասամբ վերակազմավորվող դիզայնի և դիզայնի ներդրումը Intel® Arria® 10 SoC մշակման տախտակի վրա: Հիերարխիկ մասնակի վերակազմավորումը (HPR) մասնակի վերակազմավորման հատուկ տեսակ է (PR), որտեղ դուք պարունակում եք PR տարածաշրջան մեկ այլ PR տարածաշրջանում: Դուք կարող եք ստեղծել մի քանի անձնավորություններ ինչպես երեխայի, այնպես էլ ծնողի բաժանման համար: Դուք տեղադրում եք երեխայի միջնորմները նրանց մայր բաժանմունքներում: Երեխայի բաժանման վերակազմավորումը չի ազդում ծնողի կամ ստատիկ շրջաններում գործողության վրա: Ծնող բաժանման վերակազմավորումը չի ազդում ստատիկ շրջանում գործողության վրա, այլ փոխարինում է մայր շրջանի զավակ բաժանմունքները լռելյայն մանկական բաժանման անձնավորություններով: Այս մեթոդաբանությունը արդյունավետ է համակարգերում, որտեղ մի քանի գործառույթներ ժամանակային համօգտագործում են FPGA սարքի նույն ռեսուրսները:

Մասնակի վերակազմավորումը ապահովում է հարթ դիզայնի հետևյալ առաջընթացները.

- Թույլ է տալիս գործարկման ժամանակի դիզայնի վերակազմավորումը

- Բարձրացնում է դիզայնի մասշտաբայնությունը

- Նվազեցնում է համակարգի խափանումների ժամանակը

- Աջակցում է ժամանակի մուլտիպլեքսավորման դինամիկ գործառույթներին դիզայնում

- Նվազեցնում է ծախսերը և էներգիայի սպառումը տախտակի տարածքի արդյունավետ օգտագործման շնորհիվ

- Նշում.

- Այս հղման դիզայնի իրականացումը պահանջում է հիմնական ծանոթություն Intel Quartus® Prime FPGA-ի իրականացման հոսքին և առաջնային Intel Quartus Prime նախագծի իմացությանը: files.

Առնչվող տեղեկատվություն

- Intel Arria 10 SoC Development Kit Օգտագործողի ուղեցույց

- Մասնակի վերակազմակերպման հայեցակարգեր

- Մասնակի վերակազմակերպման նախագծման հոսք

- Մասնակի վերակազմակերպման նախագծման առաջարկություններ

- Մասնակի վերակազմակերպման նախագծման նկատառումներ

Հղումների նախագծման պահանջներ

Այս հղման դիզայնը պահանջում է հետևյալը.

- Intel Quartus Prime Pro Edition ծրագրաշարի տարբերակը 17.1 դիզայնի իրականացման համար:

- Intel Arria 10 SoC մշակման հավաքածու FPGA-ի իրականացման համար:

Intel կորպորացիա. Բոլոր իրավունքները պաշտպանված են. Intel-ը, Intel-ի պատկերանշանը և Intel այլ նշանները Intel Corporation-ի կամ նրա դուստր ձեռնարկությունների ապրանքանիշերն են: Intel-ը երաշխավորում է իր FPGA-ի և կիսահաղորդչային արտադրանքների կատարումը ընթացիկ բնութագրերի համաձայն՝ համաձայն Intel-ի ստանդարտ երաշխիքի, սակայն իրեն իրավունք է վերապահում փոփոխություններ կատարել ցանկացած ապրանքի և ծառայությունների մեջ ցանկացած պահի առանց նախազգուշացման: Intel-ը չի ստանձնում ոչ մի պատասխանատվություն կամ պատասխանատվություն, որը բխում է սույն հոդվածում նկարագրված որևէ տեղեկատվության, արտադրանքի կամ ծառայության կիրառումից կամ օգտագործումից, բացառությամբ այն դեպքերի, որոնց մասին հստակ գրավոր համաձայնեցված է Intel-ի կողմից: Intel-ի հաճախորդներին խորհուրդ է տրվում ձեռք բերել սարքի տեխնիկական բնութագրերի վերջին տարբերակը՝ նախքան որևէ հրապարակված տեղեկատվության վրա հիմնվելը և ապրանքների կամ ծառայությունների պատվերներ կատարելը:

- Այլ անուններ և ապրանքանիշեր կարող են պահանջվել որպես ուրիշների սեփականություն:

Տեղեկատվության ձևավորում ավարտված էview

- Այս հղման դիզայնը բաղկացած է մեկ 32-բիթանոց հաշվիչից: Տախտակի մակարդակում դիզայնը միացնում է ժամացույցը 50 ՄՀց աղբյուրին և ելքը միացնում է FPGA-ի չորս LED-ներին: Հաշվիչի բիթերից ելքի ընտրությունը որոշակի հաջորդականությամբ հանգեցնում է նրան, որ LED-ները թարթում են որոշակի հաճախականությամբ:

Նկար 1. Flat Reference Design առանց PR բաժանման

Հղման դիզայն Files

Մասնակի վերակազմավորման ձեռնարկը հասանելի է հետևյալ վայրում. https://github.com/intel/fpga-partial-reconfig

Ձեռնարկը ներբեռնելու համար՝

- Սեղմեք Clone կամ ներբեռնեք:

- Սեղմեք Ներբեռնել ZIP. Անջատեք FPGA-partial-config-master.zip-ը file.

- Նավարկեք դեպի ձեռնարկներ/a10_soc_devkit_blinking_led_hpr ենթաթղթապանակ՝ հղումների դիզայնին մուտք գործելու համար:

Հարթ թղթապանակը բաղկացած է հետևյալից files:

Աղյուսակ 1. Հղման ձևավորում Files

| File Անուն | Նկարագրություն |

| վերեւ. Ս.Վ | Վերին մակարդակ file պարունակում է դիզայնի հարթ իրականացում։ Այս մոդուլը ներկայացնում է blinking_led ենթաբաժինը և top_counter մոդուլը: |

| top_counter.sv | Վերին մակարդակի 32-բիթանոց հաշվիչ, որն ուղղակիորեն կառավարում է LED[1]-ը: Հաշվիչի գրանցված ելքը վերահսկում է LED[0]-ը, ինչպես նաև միացնում է LED[2] և LED[3]-ը blinking_led մոդուլի միջոցով: |

| blinking_led.sdc | Սահմանում է ծրագրի ժամանակային սահմանափակումները: |

| շարունակել… | |

| File Անուն | Նկարագրություն |

| blinking_led.SV | Այս ձեռնարկում դուք այս մոդուլը վերածում եք մայր PR բաժանման: Մոդուլը ստանում է top_counter մոդուլի գրանցված ելքը, որը կառավարում է LED[2] և LED[3]: |

| blinking_led.qpf | Intel Quartus Prime նախագիծ file որը պարունակում է նախագծի բոլոր վերանայումների ցանկը: |

| blinking_led.qsf | Intel Quartus Prime կարգավորումներ file պարունակող առաջադրանքներ և պարամետրեր նախագծի համար: |

Նշում. hpr թղթապանակը պարունակում է ամբողջական փաթեթ fileԴուք ստեղծում եք՝ օգտագործելով այս հավելվածի նշումը: Հղում սրանք files քայլարշավի ընթացքում ցանկացած պահի:

Նկար 2. Հղման ձևավորում Files

Հղումների նախագծման ուղեցույց

Հետևյալ քայլերը նկարագրում են մասնակի վերակազմավորման կիրառումը հարթ դիզայնի վրա: Ուսուցումն օգտագործում է Intel Quartus Prime Pro Edition ծրագրակազմը Intel Arria 10 SoC մշակման տախտակի համար.

- Քայլ 1: Ինչպես սկսել էջ 6-ում

- Քայլ 2: Ստեղծեք երեխայի մակարդակի ենթամոդուլ 6-րդ էջում

- Քայլ 3: Դիզայնի միջնորմների ստեղծում 7-րդ էջում

- Քայլ 4: Տեղաբաշխման և երթուղային շրջանի հատկացում PR միջնորմների համար 9-րդ էջում

- Քայլ 5: Intel Arria 10 մասնակի վերակազմակերպման վերահսկիչի IP միջուկի ավելացում 10-րդ էջում

- Քայլ 6: Անձերի սահմանում 13-րդ էջում

- Քայլ 7: Վերանայումների ստեղծում 15-րդ էջում

- Քայլ 8: Հիերարխիկ մասնակի վերակազմակերպման հոսքի սցենարի ստեղծում 20-րդ էջում

- Քայլ 9: Հիերարխիկ մասնակի վերակազմավորման հոսքի սկրիպտի գործարկում 21-րդ էջում

- Քայլ 10: Խորհրդի ծրագրավորում 22-րդ էջում

Քայլ 1. Սկսել

Հղման դիզայնը պատճենելու համար files ձեր աշխատանքային միջավայրին և կազմեք blinking_led հարթ դիզայնը.

- Ստեղծեք գրացուցակ ձեր աշխատանքային միջավայրում՝ a10_soc_devkit_blinking_led_hpr:

- Պատճենեք ներբեռնված ձեռնարկները/a10_soc_devkit_blinking_led_hpr/հարթ ենթաթղթապանակը գրացուցակում, a10_soc_devkit_blinking_led_hpr:

- Intel Quartus Prime Pro Edition ծրագրաշարում սեղմեք File ➤ Բացեք Project-ը և ընտրեք blinking_led.qpf:

- Հարթ դիզայնը կազմելու համար սեղմեք Processing ➤ Start Compilation:

Քայլ 2. Երեխայի մակարդակի ենթամոդուլի ստեղծում

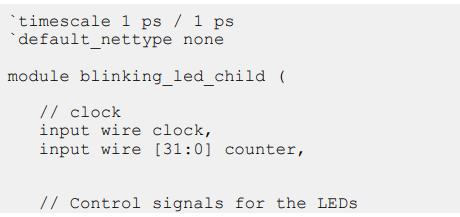

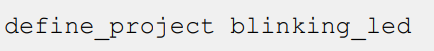

Այս հարթ դիզայնը հիերարխիկ PR դիզայնի վերածելու համար դուք պետք է ստեղծեք մանկական ենթամոդուլ (blinking_led_child. SV), որը տեղադրված է մայր ենթամոդուլում (blinking_led.sv):

- Ստեղծեք նոր դիզայն file, blinking_led_child.sv և դրան ավելացրեք կոդի հետևյալ տողերը fileժամանակի սանդղակ 1 ps / 1 ps `default_nettype none մոդուլ blinking_led_child ( // ժամացույցի մուտքային լարերի ժամացույց, մուտքային լար [31:0] հաշվիչ, // Կառավարման ազդանշաններ LED-ների համար

- Փոփոխեք blinking_led.sv file led_two_on-ը միացնելու համար ստատիկ շրջանից հաշվիչի 23-րդ բիթին և օրինականացնել blinking_led_child մոդուլը: Փոփոխություններից հետո ձեր blinking_led.sv file պետք է հայտնվի հետևյալ կերպ.

- Ամբողջ դիզայնը փոփոխելու մասին files, նորից կազմեք նախագիծը՝ սեղմելով Processing ➤ Start Compilation

Քայլ 3. Դիզայնի միջնորմների ստեղծում

Դուք պետք է ստեղծեք դիզայնի միջնորմներ յուրաքանչյուր PR տարածաշրջանի համար, որը ցանկանում եք մասնակիորեն վերակազմավորել: Դուք կարող եք ստեղծել ցանկացած թվով անկախ միջնորմներ կամ PR շրջաններ ձեր դիզայնում: Այս ձեռնարկը ստեղծում է երկու դիզայնի միջնորմ u_blinking_led_child և u_blinking_led օրինակների համար:

Հիերարխիկ մասնակի վերակազմավորման համար դիզայնի միջնորմներ ստեղծելու համար.

- Աջ սեղմեք u_blinking_led_child օրինակի վրա Project Navigator-ում և սեղմեք Design Partition ➤ Set as Design Partition: Դիզայնի բաժանման պատկերակը հայտնվում է յուրաքանչյուր օրինակի կողքին, որը սահմանված է որպես բաժանում:

Նկար 3. Նախագծային միջնորմների ստեղծում Project Navigator-ից

- Բաժանման տեսակը սահմանելու համար աջ սեղմեք u_blinking_led_child օրինակի վրա Հիերարխիա ներդիրում, սեղմեք Դիզայնի միջնորմ ➤ Reconfigurable: Դուք կարող եք սահմանել բաժանման տեսակը միայն այն բանից հետո, երբ օրինակը որպես միջնորմ սահմանեք: Դիզայնի բաժանումը հայտնվում է հանձնարարությունների վրա View Դիզայնի միջնորմների պատուհանի ներդիրը:

Նկար 4. Նախագծման միջնորմների պատուհան

- Խմբագրեք բաժանման անունը Design Partitions պատուհանում՝ կրկնակի սեղմելով անվան վրա: Այս տեղեկանքի ձևավորման համար բաժանման անունը վերանվանեք pr_partition:

Նշում. Երբ դուք ստեղծում եք միջնորմ, Intel Quartus Prime ծրագրաշարը ավտոմատ կերպով ստեղծում է բաժանման անուն՝ հիմնվելով օրինակի անվան և հիերարխիայի ուղու վրա: Այս լռելյայն բաժանման անունը կարող է տարբեր լինել յուրաքանչյուր օրինակից: - Կրկնեք 1-ին և 2-րդ քայլերը՝ u_blinking_led օրինակին վերակազմավորվող դիզայնի միջնորմներ նշանակելու համար: Վերանվանել այս բաժանումը pr_parent_partition:

Ստուգեք, որ blinking_led.qsf-ը պարունակում է հետևյալ առաջադրանքները, որոնք համապատասխանում են ձեր վերակազմավորվող դիզայնի միջնորմներին.

Ստեղծեք դիզայնի միջնորմներ մասնակի վերակազմավորման համար

Քայլ 4: Տեղաբաշխման և երթուղային շրջանի հատկացում PR միջնորմների համար

Երբ ստեղծում եք բազային վերանայումը, PR դիզայնի հոսքը օգտագործում է ձեր PR բաժանման տարածաշրջանի հատկացումը՝ համապատասխան անձի միջուկը վերապահված տարածաշրջանում տեղադրելու համար: Ձեր բազային վերանայման համար սարքի հատակագծում PR տարածաշրջանը գտնելու և նշանակելու համար.

- Աջ սեղմեք u_blinking_led_child օրինակի վրա Project Navigator-ում և սեղմեք Logic Lock Region ➤ Create New Logic Lock Region: Տարածաշրջանը հայտնվում է Logic Lock Regions պատուհանում:

- Ձեր տեղադրման տարածաշրջանը պետք է ներառի blinking_led_child տրամաբանությունը: Ընտրեք տեղաբաշխման շրջանը՝ տեղադրելով հանգույցը Chip Planner-ում: Աջ սեղմեք u_blinking_led_child տարածաշրջանի անվան վրա Project Navigator-ում և սեղմեք Locate Node ➤ Locate in Chip Planner:

Նկար 5. Chip Planner Node Location-ը blinking_led-ի համար

- Logic Lock Regions պատուհանում նշեք տեղադրման շրջանի կոորդինատները Ծագման սյունակում: Ծագումը համապատասխանում է շրջանի ստորին ձախ անկյունին։ Նախample, տեղադրման շրջան (X1 Y1) կոորդինատներով սահմանելու համար որպես (69 10), նշեք ծագումը որպես X69_Y10: Intel Quartus Prime ծրագրաշարը ավտոմատ կերպով հաշվարկում է (X2 Y2) կոորդինատները (վերևից աջ) տեղաբաշխման շրջանի համար՝ հիմնվելով ձեր նշած բարձրության և լայնության վրա:

Նշում. Այս ձեռնարկը օգտագործում է (X1 Y1) կոորդինատները – (69 10) և 20 բարձրությունն ու լայնությունը տեղաբաշխման շրջանի համար: Սահմանեք ցանկացած արժեք տեղաբաշխման տարածաշրջանի համար, պայմանով, որ տարածաշրջանը ծածկում է blinking_led_child տրամաբանությունը: - Միացնել Reserved և Core-Only տարբերակները:

- Կրկնակի սեղմեք Routing Region տարբերակը: Հայտնվում է Logic Lock Routing Region Settings երկխոսության տուփը:

- Ընտրեք Fixed with expansion-ը Routing տեսակի համար: Ընտրելով այս տարբերակը ավտոմատ կերպով նշանակում է 1 ընդլայնման երկարություն:

Նշում. Երթուղային շրջանը պետք է ավելի մեծ լինի, քան տեղադրման շրջանը, որպեսզի լրացուցիչ ճկունություն ապահովի Սարքավորողի համար, երբ շարժիչը ուղղորդում է տարբեր անձնավորությունների: - Կրկնեք 1-6 քայլերը u_blinking_led օրինակի համար: Ծնողի մակարդակի տեղադրում Կրկնեք 1-6 քայլերը u_blinking_led օրինակի համար: Ծնողի մակարդակի տեղաբաշխման շրջանը պետք է ամբողջությամբ ներառի երեխայի մակարդակի համապատասխան տեղաբաշխման և երթուղիների շրջանները՝ միաժամանակ բավարար տարածք թողնելով ծնողի մակարդակի տրամաբանական տեղադրման համար: Այս ձեռնարկը օգտագործում է (X1 Y1) կոորդինատները – (66 7), բարձրությունը 47 և լայնությունը 26 u_blinking_led օրինակի տեղադրման շրջանի համար:

Նկար 6. Logic Lock Regions պատուհան

Հաստատեք, որ blinking_led.qsf-ը պարունակում է հետևյալ առաջադրանքները, որոնք համապատասխանում են ձեր հատակագծին.

- Հատակի պլանավորում մասնակի վերակազմակերպման դիզայնը

- Մասնակի վերակազմավորման աստիճանական իրականացում

Քայլ 5. Intel Arria 10 մասնակի վերակազմակերպման վերահսկիչի IP միջուկի ավելացում

- Օգտագործեք Intel Arria 10 Partal Reconfiguration Controller IP միջուկը՝ PR բաժինը վերակազմավորելու համար: Այս IP միջուկը օգտագործում է JTAG PR բաժինը վերակազմավորելու համար: Intel Arria 10 Partal Reconfiguration Controller IP միջուկը ձեր Intel Quartus Prime նախագծին ավելացնելու համար.

- IP-ի կատալոգում մուտքագրեք Partal Reconfiguration:

- IP Parameter Editor Pro պատուհանը գործարկելու համար IP գրադարանից ընտրեք Intel Arria 10 Partal Reconfiguration Controller IP միջուկը և սեղմեք Ավելացնել:

- Նոր IP տարբերակ երկխոսության վանդակում մուտքագրեք pr_ip որպես file անունը և սեղմեք Ստեղծել: Օգտագործեք լռելյայն պարամետրիզացիան pr_ip-ի համար: Համոզվեք, որ Enable JTAG վրիպազերծման ռեժիմը և Միացնել սառեցման ինտերֆեյսի ընտրանքները միացված են, իսկ Enable Avalon-MM slave ինտերֆեյսի ընտրանքն անջատված է:

Նկար 7. Intel Arria 10 մասնակի վերակազմակերպման վերահսկիչի IP հիմնական պարամետրերը

- Սեղմեք Finish և դուրս եկեք պարամետրերի խմբագրիչից՝ առանց համակարգը ստեղծելու: Intel Quartus Prime ծրագիրը ստեղծում է pr_ip.ip IP տարբերակ file, և ավելացնում է file blinking_led նախագծին:

Նշում.

- Եթե դուք պատճենում եք pr_ip.ip-ը file hpr թղթապանակից, ձեռքով խմբագրեք blinking_led.qsf file ներառել հետևյալ տողը. set_global_assignment -name IP_FILE pr_ip.ip

- Տեղադրեք IP_FILE հանձնարարություն SDC_-ից հետոFILE հանձնարարություններ (ժtag.sdc և blinking_led.sdc) ձեր blinking_led.qsf-ում file. Այս պատվերը ապահովում է մասնակի վերակազմակերպման IP միջուկի համապատասխան սահմանափակում:

Նշում. Ժամացույցները հայտնաբերելու համար SDC-ն file քանի որ PR IP-ն պետք է հետևի ցանկացած SDC-ին, որը ստեղծում է ժամացույցներ, որոնք օգտագործում է IP միջուկը: Դուք հեշտացնում եք այս պատվերը՝ ապահովելով .ip-ը file քանի որ PR IP միջուկը գալիս է ցանկացած .ip-ից հետո files կամ SDC files-ն օգտագործվում է QSF-ում այս ժամացույցները ստեղծելու համար file ձեր Intel Quartus Prime նախագծի վերանայման համար: Լրացուցիչ տեղեկությունների համար տես Ժամկետային սահմանափակումներ բաժինը Մասնակի վերակազմակերպման IP Core Օգտագործողի ուղեցույցում:

Առնչվող տեղեկատվություն

- Մասնակի վերակազմակերպման IP լուծումների Օգտագործողի ուղեցույց

- Մասնակի վերակազմակերպման տարածաշրջանի վերահսկիչի IP միջուկի մասին տեղեկությունների համար:

- Մասնակի վերակազմակերպման IP Core Օգտագործողի ուղեցույց

- Ժամկետային սահմանափակումների մասին տեղեկությունների համար:

Վերին մակարդակի դիզայնի թարմացում

Վերևը թարմացնելու համար.SV file PR_IP օրինակով.

- PR_IP օրինակը վերին մակարդակի դիզայնին ավելացնելու համար վերևում հանեք հետևյալ կոդի բլոկը: SV file:

- Վերակազմավորման ընթացքում ելքային պորտերը տրամաբանական 1-ին ստիպելու համար օգտագործեք սառեցման կառավարման ազդանշանի ելքը PR_IP-ից: Այնուամենայնիվ, դիտելու համար, որ LED-ը շարունակում է թարթել մայր PR միջնորմից, մինչ PR-ը ծրագրավորում է երեխայի բաժանումը, սառեցման կառավարման ազդանշանը չի անջատում led_two_on-ը: Համոզվեք, որ pr_led_two_on ուղղակիորեն է

- Լռելյայն ծնող անձի (blinking_led) օրինակ նշանակելու համար թարմացրեք վերև.SV file հետևյալ կոդի բլոկով.

Նկար 8. Մասնակի վերակազմավորում IP Core ինտեգրում

Քայլ 6. Անձերի սահմանում

Այս հղման ձևավորումը սահմանում է հինգ առանձին անձնավորություններ ծնողի և երեխայի PR բաժինների համար: Անձերին ձեր նախագծում սահմանելու և ներառելու համար.

- Ստեղծեք չորս SystemVerilog files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv և blinking_led_slow.sv հինգ անձերի աշխատանքային գրացուցակում:

Նշում. Եթե ստեղծեք SystemVerilog files Intel Quartus Prime Text Editor-ից, անջատեք Ավելացնել file ընթացիկ նախագծի տարբերակին, երբ պահպանում եք files.

Աղյուսակ 2. Reference Design Personas

| File Անուն | Նկարագրություն | Կոդ |

| blinking_led_child.sv | Երեխայի մակարդակի դիզայնի կանխադրված անձը |

«ժամկետը 1 վրկ / 1 վրկ `default_nettype none մոդուլ blinking_led_child ( // ժամացույց մուտքային մետաղալար ժամացույց, մուտքային մետաղալար [31:0] հաշվիչ,

// Կառավարման ազդանշաններ LED-ների ելքային լարերի համար led_three_on

); localparam COUNTER_TAP = 23; reg led_three_on_r;

նշանակել led_three_on = led_three_on_r; միշտ_ff @(posge ժամացույց) սկսվում է led_three_on_r <= հաշվիչ[COUNTER_TAP]; վերջ

էնդմոդուլ |

| շարունակել… | ||

| File Անուն | Նկարագրություն | Կոդ |

| blinking_led_child_slow.sv | Այն

LED_THREE թարթում է ավելի դանդաղ |

«ժամկետը 1 վրկ / 1 վրկ `default_nettype none

մոդուլ blinking_led_child_slow (

// ժամացույց մուտքային մետաղալար ժամացույց, մուտքային մետաղալար [31:0] հաշվիչ,

// Կառավարման ազդանշաններ LED-ների ելքային լարերի համար led_three_on );

localparam COUNTER_TAP = 27; reg led_three_on_r;

նշանակել led_three_on = led_three_on_r; միշտ_ff @(posge ժամացույց) սկսվում է led_three_on_r <= հաշվիչ[COUNTER_TAP]; վերջ

էնդմոդուլ |

| blinking_led_child_empty.sv | Այն

LED_THREE մնում է ON |

«ժամկետը 1 վրկ / 1 վրկ `default_nettype none

մոդուլ blinking_led_child_empty (

// ժամացույց մուտքային մետաղալար ժամացույց, մուտքային մետաղալար [31:0] հաշվիչ,

// Կառավարման ազդանշաններ LED-ների ելքային լարերի համար led_three_on

);

// LED-ն ակտիվ է ցածր նշանակել led_three_on = 1'b0;

էնդմոդուլ |

| blinking_led_slow.sv | LED_TWO-ը

թարթում է ավելի դանդաղ: |

«ժամկետը 1 վրկ / 1 վրկ `default_nettype none մոդուլ blinking_led_slow( // ժամացույց մուտքային մետաղալար ժամացույց, մուտքային մետաղալար [31:0] հաշվիչ,

// LED-ների ելքային լարերի կառավարման ազդանշաններ led_two_on, ելքային մետաղալար led_three_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; նշանակել led_two_on = led_two_on_r;

// Հաշվիչ: always_ff @(posedge clock) start led_two_on_r <= հաշվիչ[COUNTER_TAP]; վերջ

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .counter (counter), .ժամացույց (ժամացույց) |

| File Անուն | Նկարագրություն | Կոդ |

| );nd մոդուլ |

Քայլ 3. Դիզայնի միջնորմների ստեղծում 7-րդ էջում

Քայլ 7. Վերանայումների ստեղծում

Հասարակայնության հետ կապերի նախագծման հոսքը օգտագործում է նախագծի վերանայման առանձնահատկությունը Intel Quartus Prime ծրագրաշարում: Ձեր նախնական դիզայնը բազային վերանայումն է, որտեղ դուք սահմանում եք ստատիկ շրջանի սահմանները և վերակազմավորվող շրջանները FPGA-ում: Բազային վերանայումից դուք ստեղծում եք բազմաթիվ վերանայումներ: Այս վերանայումները պարունակում են տարբեր իրականացումներ PR տարածաշրջանների համար: Այնուամենայնիվ, հասարակայնության հետ կապերի իրականացման բոլոր վերանայումներն օգտագործում են նույն վերին մակարդակի տեղաբաշխման և երթուղային արդյունքները բազային վերանայումից: PR դիզայն կազմելու համար դուք պետք է ստեղծեք PR իրականացման վերանայում և սինթեզի վերանայում յուրաքանչյուր անձի համար: Այս հղման նախագծում, բացի հիմնական վերանայումից (blinking_led), երեք երեխայի մակարդակի անձնավորությունները և երկու ծնողի մակարդակի անձերը պարունակում են հինգ առանձին սինթեզի վերանայումներ և հինգ առանձին իրականացման վերանայումներ.

Աղյուսակ 3. Վերանայումներ երկու ծնողների և երեք երեխաների անձնավորությունների համար

| Սինթեզի վերանայում | Իրականացման վերանայում |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_empty | blinking_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | blinking_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_empty | blinking_led_pr_emma |

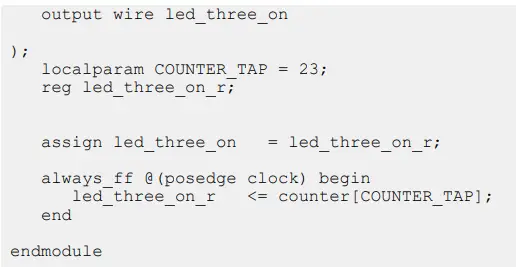

Իրականացման վերանայումների ստեղծում

PR-ի իրականացման վերանայումներ ստեղծելու համար.

- Revisions երկխոսության տուփը բացելու համար սեղմեք Project ➤ Revisions:

- Նոր վերանայում ստեղծելու համար կրկնակի սեղմեք < >.

- Նշեք Վերանայման անունը որպես blinking_led_pr_alpha և ընտրեք blinking_led համար «Վերանայման հիման վրա»:

- Անջատեք Սահմանել որպես ընթացիկ վերանայման տարբերակը և սեղմեք OK:

- Նմանապես, ստեղծեք blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta և blinking_led_pr_emma վերանայումները՝ հիմնված blinking_led վերանայման վրա:

Նշում. Մի սահմանեք վերը նշված վերանայումները որպես ընթացիկ վերանայում:

Նկար 9. Վերանայումների ստեղծում

Միայն սինթեզի վերանայումների ստեղծում

Անձերի համար միայն սինթեզի վերանայումներ ստեղծելու համար դուք պետք է նշանակեք վերին մակարդակի միավորը և համապատասխան SystemVerilog file անձերից յուրաքանչյուրի համար.

- Intel Quartus Prime ծրագրաշարում սեղմեք Project ➤ Revisions:

- Ստեղծեք blinking_led_default տարբերակ՝ հիմնված blinking_led վերանայման վրա: Մի սահմանեք այս վերանայումը որպես ընթացիկ տարբերակ:

- Փոփոխեք blinking_led_default.qsf-ը file ներառել հետևյալ առաջադրանքները.

set_global_assignment -name TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -name SYSTEMVERILOG_FILE - Նմանապես, ստեղծեք blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent և blinking_led_parent_slow վերանայումները՝ հիմնված blinking_led վերանայման վրա: Մի սահմանեք այս վերանայումները որպես ընթացիկ վերանայումներ:

- Թարմացրեք blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf և blinking_led_parent_slow.qsf: fileներ իրենց համապատասխան

TOP_LEVEL_ENTITY և SYSTEMVERILOG_FILE հանձնարարություններ:

- Սինթեզի սխալներից խուսափելու համար համոզվեք, որ սինթեզի վերանայումը fileՄանկական միջնորմների համար s-ը չի պարունակում որևէ դիզայնի միջնորմ, փին հանձնարարություններ կամ Logic Lock

մարզային առաջադրանքներ. Նաև սինթեզի վերանայումը files-ը մայր բաժանմունքների համար պետք է պարունակի միայն նախագծային բաժանման հանձնարարություններ համապատասխան զավակների համար: Հեռացրեք այս հանձնարարությունները, եթե այդպիսիք կան, blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf և blinking_led_parent_slow.pdf: files

- Ներառեք հետևյալ առաջադրանքները blinking_led_parent.qsf և blinking_led_parent_slow.qsf files:

- Ստուգեք, որ blinking_led.qpf file պարունակում է հետևյալ վերանայումները՝ առանց հատուկ հերթականության.

- Նշում. Եթե դուք կրկնօրինակում եք վերանայումը files hpr թղթապանակից, ձեռքով թարմացրեք blinking_led.qpf file վերը նշված կոդի տողերով:

Նշելով վերանայման տեսակը

Դուք պետք է նշանակեք վերանայման տեսակ ձեր յուրաքանչյուր վերանայման համար: Վերանայման երեք տեսակ կա.

- Մասնակի վերակազմավորում – Հիմք

- Մասնակի վերակազմավորում – Անձնական սինթեզ

- Մասնակի վերակազմավորում – Անձնակազմի իրականացում

- Հետևյալ աղյուսակը թվարկում է վերանայման տիպի հանձնարարությունները յուրաքանչյուր վերանայման համար.

Աղյուսակ 4. Վերանայման տեսակները

| Վերանայման անվանումը | Վերանայման տեսակը |

| blinking_led.qsf | Մասնակի վերակազմավորում – Հիմք |

| blinking_led_default.qsf | Մասնակի վերակազմավորում – Անձնական սինթեզ |

| blinking_led_child_empty.qsf | Մասնակի վերակազմավորում – Անձնական սինթեզ |

| blinking_led_child_slow.qsf | Մասնակի վերակազմավորում – Անձնական սինթեզ |

| blinking_led_parent.qsf | Մասնակի վերակազմավորում – Անձնական սինթեզ |

| blinking_led_parent_slow.qsf | Մասնակի վերակազմավորում – Անձնական սինթեզ |

| blinking_led_pr_alpha.qsf | Մասնակի վերակազմավորում – Անձնակազմի իրականացում |

| blinking_led_pr_bravo.qsf | Մասնակի վերակազմավորում – Անձնակազմի իրականացում |

| blinking_led_pr_charlie.qsf | Մասնակի վերակազմավորում – Անձնակազմի իրականացում |

| blinking_led_pr_delta.qsf | Մասնակի վերակազմավորում – Անձնակազմի իրականացում |

| blinking_led_pr_emma.qsf | Մասնակի վերակազմավորում – Անձնակազմի իրականացում |

- Սեղմեք Project ➤ Revisions: Հայտնվում է Revisions երկխոսության տուփը:

- Ընտրեք blinking_led Revision Name սյունակում և սեղմեք Set Current:

- Սեղմեք Դիմել: Բացվում է blinking_led վերանայումը:

- Blinking_led-ի վերանայման տեսակը սահմանելու համար սեղմեք Հանձնարարություններ ➤ Կարգավորումներ ➤ Ընդհանուր:

- Ընտրեք վերանայման տեսակը որպես մասնակի վերակազմավորում – բազա:

- Նմանապես, սահմանեք վերանայման տեսակները մյուս տասը վերանայումների համար, ինչպես նշված է վերը նշված աղյուսակում:

- Նշում. Նախքան վերանայման տեսակը նշանակելը, դուք պետք է յուրաքանչյուր վերանայում սահմանեք որպես ընթացիկ տարբերակ: Ստուգեք, որ յուրաքանչյուր .qsf file պարունակում է հետևյալ առաջադրանքը.

- Նշում. Ավելացրեք Fitter-ի համար նախատեսված ցանկացած կարգավորում, որը ցանկանում եք օգտագործել PR-ի իրականացման կոմպիլիայում՝ անձերի իրականացման վերանայումներին: Fitter-ի հատուկ կարգավորումները ազդում են անձի համապատասխանության վրա, բայց չեն ազդում ներմուծված ստատիկ շրջանի վրա: Դուք կարող եք նաև ավելացնել սինթեզի հատուկ կարգավորումներ անհատական սինթեզի վերանայումներին:

Ստեղծեք վերանայումներ անձերի համար

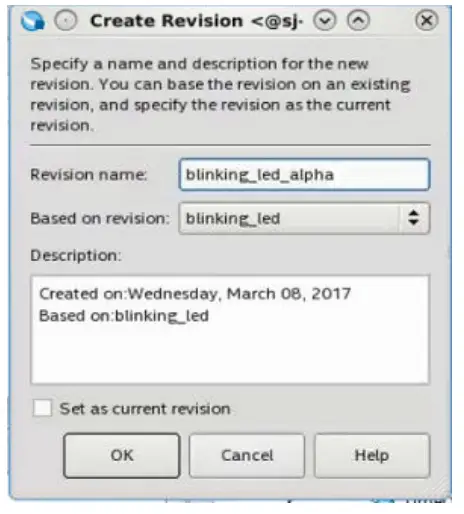

Քայլ 8: Հիերարխիկ մասնակի վերակազմակերպման հոսքի սցենարի ստեղծում

Հիերարխիկ մասնակի վերակազմավորման հոսքի սցենար ստեղծելու համար.

- Intel Quartus Prime հրամանի վահանակից ստեղծեք հոսքի ձևանմուշ՝ գործարկելով հետևյալ հրամանը.

- Intel Quartus Prime-ը ստեղծում է a10_hier_partial_reconfig/flow.tcl file.

- Վերանվանեք ստեղծված a10_hier_partial_reconfig/setup.tcl.exampանցեք a10_hier_partial_reconfig/setup.tcl և փոփոխեք սկրիպտը՝ ձեր մասնակի վերակազմակերպման նախագծի մանրամասները նշելու համար.

a. Նախագծի անվանումը սահմանելու համար թարմացրեք հետևյալ տողը. b. Բազային վերանայումը սահմանելու համար թարմացրեք հետևյալ տողը.

b. Բազային վերանայումը սահմանելու համար թարմացրեք հետևյալ տողը.

- Մասնակի վերակազմակերպման իրականացման վերանայումներից յուրաքանչյուրը սահմանելու համար PR բաժնի անվանումների և սկզբնաղբյուրի վերանայման հետ մեկտեղ, որն իրականացնում է վերանայումները, թարմացրեք հետևյալ տողերը.

Նշում. Բոլոր վերանայման նախագծերը պետք է լինեն նույն գրացուցակում, ինչ blinking_led.qpf: Հակառակ դեպքում, համապատասխանաբար թարմացրեք հոսքի սցենարը:

Քայլ 9: Հիերարխիկ մասնակի վերակազմակերպման հոսքի սցենարի գործարկում

Հիերարխիկ մասնակի վերակազմավորման հոսքի սկրիպտը գործարկելու համար՝

- Սեղմեք Գործիքներ ➤ Tcl Սկրիպտներ: Հայտնվում է Tcl Scripts երկխոսության տուփը:

- Կտտացրեք «Ավելացնել նախագծին», թերթեք և ընտրեք a10_hier_partial_reconfig/flow.tcl:

- Գրադարանների վահանակում ընտրեք a10_hier_partial_reconfig/flow.tcl և սեղմեք «Գործարկել»:

Այս սցենարը սինթեզում է երեք անձերի համար: Intel Quartus Prime-ը ստեղծում է SRAM օբյեկտ File (.sof), մասնակի դիմակավորված SRAM օբյեկտ File (.pmsf) և հում երկուական File (.rbf) անձերից յուրաքանչյուրի համար:

Նշում. Intel Quartus Prime հրամանի վահանակից սկրիպտը գործարկելու համար մուտքագրեք հետևյալ հրամանը.

- Կազմեք մասնակի վերակազմավորման դիզայնը

- Օգտագործելով մասնակի վերակազմակերպման հոսքի սցենար

- Մասնակի վերակազմակերպման հոսքի սցենարի կարգավորում

- Ստեղծեք ծրագրավորում Files

Քայլ 10: Խորհրդի ծրագրավորում

Նախքան սկսելը.

- Միացրեք սնուցման աղբյուրը Intel Arria 10 SoC մշակման տախտակին:

- Միացրեք USB Blaster մալուխը ձեր համակարգչի USB պորտի և մշակման տախտակի վրա գտնվող USB Blaster պորտի միջև:

Դիզայնը Intel Arria 10 SoC մշակման տախտակի վրա գործարկելու համար.

- Բացեք Intel Quartus Prime ծրագիրը և սեղմեք Գործիքներ ➤ Ծրագրավորող:

- Ծրագրավորողում սեղմեք Hardware Setup և ընտրեք USB-Blaster:

- Սեղմեք Auto Detect և ընտրեք սարքը՝ 10AS066N3:

- Սեղմեք OK: Intel Quartus Prime ծրագրաշարը հայտնաբերում և թարմացնում է Ծրագրավորողին տախտակի վրա գտնվող երեք FPGA չիպերով:

- Ընտրեք 10AS066N3 սարքը, սեղմեք Փոխել File և բեռնել blinking_led_pr_alpha.sof file.

- Միացնել ծրագիրը/Կարգավորել blinking_led_pr_alpha.sof-ի համար file.

- Կտտացրեք «Սկսել» և սպասեք, որ առաջընթացի բարը հասնի 100%-ի:

- Դիտեք, թե ինչպես են տախտակի վրա գտնվող LED-ները թարթում նույն հաճախականությամբ, ինչ բնօրինակ հարթ դիզայնը:

- Միայն մանկական PR տարածաշրջանը ծրագրավորելու համար աջ սեղմեք blinking_led_pr_alpha.sof. file Ծրագրավորողում և սեղմեք Ավելացնել PR ծրագրավորում File.

- Ընտրեք blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file.

- Անջատել ծրագիրը/Կարգավորել blinking_led_pr_alpha.sof-ի համար file.

- Միացնել ծրագիրը/Կարգավորել blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf-ի համար file և սեղմեք Սկսել: Տախտակի վրա դիտեք LED[0] և LED[1]-ը, որոնք շարունակում են թարթել: Երբ առաջընթացի սանդղակը հասնում է 100%-ի, LED[2]-ը թարթում է նույն արագությամբ, իսկ LED[3]-ը՝ ավելի դանդաղ:

- Ծնողի և երեխայի PR տարածաշրջանը ծրագրավորելու համար աջ սեղմեք .rbf file Ծրագրավորողում և սեղմեք «Փոխել PR ծրագրավորումը»: File.

- Ընտրեք blinking_led_pr_delta.pr_parent_partition.rbf file.

- Սեղմեք Սկսել: Տախտակի վրա դիտեք, որ LED[0] և LED[1] շարունակում են թարթել: Երբ առաջընթացի սանդղակը հասնում է 100%-ի, և՛ լուսադիոդը[2], և՛ լուսադիոդը[3] ավելի դանդաղ են թարթում:

- Կրկնեք վերը նշված քայլերը՝ դինամիկ կերպով վերածրագրավորելու միայն մանկական PR տարածաշրջանը կամ ծնողական և մանկական PR տարածաշրջանները միաժամանակ:

Նկար 10. Intel Arria 10 SoC զարգացման խորհրդի ծրագրավորում

Փոփոխել գոյություն ունեցող անձը

- Դուք կարող եք փոխել գոյություն ունեցող անձին, նույնիսկ բազային վերանայումն ամբողջությամբ կազմելուց հետո:

- Նախample, որպեսզի blinking_led_child_slow անձը էլ ավելի դանդաղ թարթվի.

- blinking_led_child_slow.sv-ում file, փոփոխեք COUNTER_TAP պարամետրը 27-ից 28:

- Այս անձը նորից սինթեզելու և գործադրելու համար դուք պետք է նորից կազմեք միայն սինթեզի համար նախատեսված բոլոր վերանայումները և կատարման վերանայումները, որոնք ազդում են փոփոխության վրա: Փոփոխեք setup.tcl սկրիպտը՝ ներառելով հետևյալ տողերը.

Նշում. blinking_led_pr_delta վերանայման համար pr_parent_parition սահմանելիս դուք ներմուծում եք այդ անձի վերջնական նկարը իրականացման համար: Արդյունքում, ծնողական բաժանման տրամաբանության իրականացումը մնում է նույնը, մինչդեռ փոփոխվում և ներդրվում է համապատասխան երեխա բաժանումը:

Նշում. blinking_led_pr_delta վերանայման համար pr_parent_parition սահմանելիս դուք ներմուծում եք այդ անձի վերջնական նկարը իրականացման համար: Արդյունքում, ծնողական բաժանման տրամաբանության իրականացումը մնում է նույնը, մինչդեռ փոփոխվում և ներդրվում է համապատասխան երեխա բաժանումը: Այս հրամանը վերասինթեզում է blinking_led_child_slow սինթեզի վերանայումը, այնուհետև գործարկում է PR իրականացման կոմպիլը՝ օգտագործելով blinking_led_pr_bravo:

Այս հրամանը վերասինթեզում է blinking_led_child_slow սինթեզի վերանայումը, այնուհետև գործարկում է PR իրականացման կոմպիլը՝ օգտագործելով blinking_led_pr_bravo: - Միայն սինթեզի համար նախատեսված վերանայումների կոմպիլյացիան կատարելու համար գործարկեք հետևյալ հրամանը.

- Իրականացման վերանայումների կոմպիլյացիան կատարելու համար գործարկեք հետևյալ հրամանը.

- Այս հրամանը չի վերակազմավորում բազային վերանայումը:

- Հետևեք 10-րդ քայլի քայլերին. 22-րդ էջի տախտակի ծրագրավորում՝ ստացված RBF-ը ծրագրավորելու համար file FPGA-ի մեջ:

Նշում. Յուրաքանչյուր վերանայման համար ամբողջ հոսքի գործարկումից խուսափելու համար սահմանեք setup.tcl սկրիպտում միայն սինթեզի համար նախատեսված վերանայումները և կատարման վերանայումները և գործարկեք սկրիպտը:

Դիզայնին նոր անձնավորություն ավելացնելը

Ձեր բազային վերանայումները ամբողջությամբ կազմելուց հետո դուք դեռ կարող եք ավելացնել նոր անձեր և անհատապես կազմել այդ անձերը:

Նախample, blinking_led_parent_slow-ի համար նոր երեխայի պերսոնա սահմանելու համար, որն անջատում է led_three-ը.

- Պատճենել blinking_led_child_empty.sv-ը blinking_led_chdild_off.sv-ում:

- blinking_led_child_off.sv-ում file, փոփոխել հանձնարարությունը, նշանակել led_three_on = 1'b0; նշանակել led_three_on = 1'b1;. Համոզվեք, որ փոխել եք մոդուլի անունը blinking_led_child_empty-ից blinking_led_child_off:

- Ստեղծեք նոր սինթեզի վերանայում՝ blinking_led_child_off, հետևելով 16-րդ էջի «Միայն սինթեզի համար վերանայումներ ստեղծելու» քայլերին:

Նշում. Blinking_led_child_off վերանայումը պետք է օգտագործի blinking_led_child_off.sv file. - Ստեղծեք նոր կատարման վերանայում, blinking_led_pr_foxtrot, հետևելով 15-րդ էջի կատարման վերանայումների ստեղծման քայլերին:

- Թարմացրեք a10_hier_partial_reconfig/setup.tcl file սահմանել նոր PR իրականացումը.

- Կազմեք հենց այս նոր սինթեզը և իրականացման վերանայումը` գործարկելով հետևյալ հրամանը.

Intel Arria 10 սարքերի հիերարխիկ մասնակի վերակազմավորման վերաբերյալ ամբողջական տեղեկատվության համար տե՛ս Intel Quartus Prime Pro Edition ձեռնարկի 1-ին հատորում մասնակի վերակազմակերպման դիզայնի ստեղծում:

Առնչվող տեղեկատվություն

- Մասնակի վերակազմակերպման դիզայնի ստեղծում

- Մասնակի վերակազմակերպման առցանց ուսուցում

Փաստաթղթերի վերանայման պատմություն

Աղյուսակ 5. Փաստաթղթերի վերանայման պատմություն

| Փաստաթղթի տարբերակը | Ծրագրային տարբերակ | Փոփոխություններ |

| 2017.11.06 | 17.1.0 | • Թարմացվել է Հղումների նախագծման պահանջներ բաժինը ծրագրաշարի տարբերակով

• Թարմացվել է Flat Reference Design առանց PR բաժանման գործիչ դիզայնի բլոկի փոփոխություններով • Թարմացվել է Հղման դիզայն Files աղյուսակի վերաբերյալ տեղեկություններով Top_counter.sv մոդուլ • Թարմացվել է Մասնակի վերակազմակերպում IP Core ինտեգրում գործիչ դիզայնի բլոկի փոփոխություններով • Թարմացվել է թվերը – Նախագծման միջնորմների պատուհան և Տրամաբանական կողպեք տարածաշրջանների պատուհան արտացոլելու նոր GUI-ը • File անվանափոխություն • Տեքստային խմբագրումներ |

| 2017.05.08 | 17.0.0 | Փաստաթղթի նախնական հրապարակումը |

Փաստաթղթեր / ռեսուրսներ

|

intel AN 805 Դիզայնի հիերարխիկ մասնակի վերակազմավորում Arria 10 SoC Development Board-ում [pdf] Օգտագործողի ուղեցույց AN 805 Դիզայնի հիերարխիկ մասնակի վերակազմավորում Arria 10 SoC զարգացման տախտակի վրա, AN 805, դիզայնի հիերարխիկ մասնակի վերակազմավորում Arria 10 SoC զարգացման տախտակի վրա, դիզայնի վերակազմավորում Arria 10 SoC զարգացման տախտակում, Arria 10 SoC զարգացման տախտակ, 10 SoC Զարգացման խորհուրդ |