intel AN 805 Hierarchická částečná rekonfigurace designu na Arria 10 SoC Development Board

Výukový program pro hierarchickou částečnou rekonfiguraci pro vývojovou desku Intel® Arria® 10 SoC

Tato aplikační poznámka demonstruje transformaci jednoduchého návrhu do hierarchicky částečně rekonfigurovatelného návrhu a implementaci návrhu na vývojové desce Intel® Arria® 10 SoC. Hierarchická částečná rekonfigurace (HPR) je speciální typ částečné rekonfigurace (PR), kdy obsahuje PR region v rámci jiného PR regionu. Můžete vytvořit více personas pro podřízený i nadřazený oddíl. Podřízené oddíly vnoříte do jejich nadřazených oddílů. Překonfigurování podřízeného oddílu neovlivní provoz v nadřazené nebo statické oblasti. Překonfigurování nadřazeného oddílu neovlivní operaci ve statické oblasti, ale nahradí podřízené oddíly nadřazené oblasti výchozími personami podřízeného oddílu. Tato metodika je účinná v systémech, kde více funkcí časově sdílí stejné prostředky zařízení FPGA.

Částečná rekonfigurace poskytuje následující vylepšení plochého designu:

- Umožňuje změnu konfigurace návrhu za běhu

- Zvyšuje škálovatelnost návrhu

- Snižuje prostoje systému

- Podporuje dynamické funkce time-multiplexingu v návrhu

- Snižuje náklady a spotřebu energie díky efektivnímu využití místa na desce

- Poznámka:

- Implementace tohoto referenčního návrhu vyžaduje základní znalost implementačního toku Intel Quartus® Prime FPGA a znalost primárního projektu Intel Quartus Prime. files.

Související informace

- Uživatelská příručka Intel Arria 10 SoC Development Kit

- Koncepty částečné rekonfigurace

- Návrhový tok částečné rekonfigurace

- Doporučení návrhu částečné rekonfigurace

- Úvahy o návrhu částečné rekonfigurace

Požadavky na referenční design

Tento referenční návrh vyžaduje následující:

- Software Intel Quartus Prime Pro Edition verze 17.1 pro implementaci návrhu.

- Vývojový kit Intel Arria 10 SoC pro implementaci FPGA.

Intel Corporation. Všechna práva vyhrazena. Intel, logo Intel a další značky Intel jsou ochranné známky společnosti Intel Corporation nebo jejích dceřiných společností. Společnost Intel zaručuje výkon svých FPGA a polovodičových produktů podle aktuálních specifikací v souladu se standardní zárukou společnosti Intel, ale vyhrazuje si právo provádět změny jakýchkoli produktů a služeb kdykoli bez upozornění. Společnost Intel nepřebírá žádnou odpovědnost nebo závazky vyplývající z aplikace nebo použití jakýchkoli informací, produktů nebo služeb zde popsaných, s výjimkou případů, kdy je společnost Intel výslovně písemně odsouhlasena. Zákazníkům společnosti Intel se doporučuje získat nejnovější verzi specifikací zařízení předtím, než se budou spoléhat na jakékoli zveřejněné informace a než zadají objednávky na produkty nebo služby.

- Jiná jména a značky mohou být nárokovány jako vlastnictví jiných.

Referenční design skončilview

- Tento referenční návrh se skládá z jednoho 32bitového čítače. Na úrovni desky návrh připojuje hodiny k 50MHz zdroji a výstup připojuje ke čtyřem LED na FPGA. Výběr výstupu z bitů čítače ve specifické sekvenci způsobí, že LED diody budou blikat specifickou frekvencí.

Obrázek 1. Plochý referenční design bez PR dělení

Referenční design Files

Výukový program částečné rekonfigurace je k dispozici v následujícím umístění: https://github.com/intel/fpga-partial-reconfig

Chcete-li stáhnout tutoriál:

- Klikněte na Klonovat nebo stáhnout.

- Klikněte na Stáhnout ZIP. Rozbalte soubor FPGA-partial-config-master.zip file.

- Chcete-li získat přístup k referenčnímu návrhu, přejděte do podsložky tutorials/a10_soc_devkit_blinking_led_hpr.

Plochá složka se skládá z následujícího files:

Tabulka 1. Referenční design Files

| File Jméno | Popis |

| horní. SV | Nejvyšší úroveň file obsahuje plošnou realizaci návrhu. Tento modul vytváří instanci pododdílu blinking_led a modulu top_counter. |

| top_counter.sv | 32bitový čítač nejvyšší úrovně, který přímo ovládá LED[1]. Registrovaný výstup čítače ovládá LED[0] a také napájí LED[2] a LED[3] přes modul blikající_led. |

| blikající_led.sdc | Definuje časová omezení pro projekt. |

| pokračování… | |

| File Jméno | Popis |

| blikající_led.SV | V tomto kurzu převedete tento modul na nadřazený oddíl PR. Modul přijímá registrovaný výstup modulu top_counter, který ovládá LED[2] a LED[3]. |

| blikající_led.qpf | Projekt Intel Quartus Prime file obsahující seznam všech revizí v projektu. |

| blikající_led.qsf | Nastavení Intel Quartus Prime file obsahující přiřazení a nastavení pro projekt. |

Poznámka: Složka hpr obsahuje kompletní sadu files pomocí této poznámky k aplikaci. Odkaz na tyto files kdykoli během průchodu.

Obrázek 2. Referenční návrh Files

Návod k referenčnímu designu

Následující kroky popisují aplikaci částečné rekonfigurace na plochý design. Výukový program používá software Intel Quartus Prime Pro Edition pro vývojovou desku Intel Arria 10 SoC:

- Krok 1: Začínáme na straně 6

- Krok 2: Vytvořte podmodul Child Level na straně 6

- Krok 3: Vytváření návrhových oddílů na straně 7

- Krok 4: Přidělení oblasti umístění a směrování pro PR oddíly na straně 9

- Krok 5: Přidání Intel Arria 10 Partial Reconfiguration Controller IP Core na straně 10

- Krok 6: Definování Personas na straně 13

- Krok 7: Vytváření revizí na straně 15

- Krok 8: Generování skriptu toku hierarchické částečné rekonfigurace na straně 20

- Krok 9: Spuštění skriptu toku hierarchické částečné rekonfigurace na straně 21

- Krok 10: Programování desky na straně 22

Krok 1: Začínáme

Chcete-li zkopírovat referenční návrh files vaším pracovním prostředím a zkompilujte si plochý design s blikajícím osvětlením:

- Vytvořte si ve svém pracovním prostředí adresář a10_soc_devkit_blinking_led_hpr.

- Zkopírujte staženou podsložku tutorials/a10_soc_devkit_blinking_led_hpr/flat do adresáře a10_soc_devkit_blinking_led_hpr.

- V softwaru Intel Quartus Prime Pro Edition klepněte na File ➤ Otevřete projekt a vyberte blinking_led.qpf.

- Chcete-li zkompilovat plochý návrh, klepněte na Zpracování ➤ Spustit kompilaci.

Krok 2: Vytvoření podmodulu Child Level

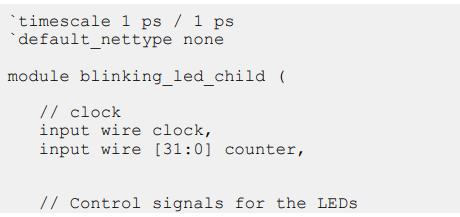

Chcete-li tento plochý design převést na hierarchický návrh PR, musíte vytvořit podřízený podmodul (blinking_led_child. SV), který je vnořen do nadřazeného podmodulu (blinking_led.sv).

- Vytvořte nový design file, blinking_led_child.sv a přidejte k tomu následující řádky kódu file: časová osa 1 ps / 1 ps `default_nettype žádný modul blinking_led_child ( // hodiny vstupního vodiče hodiny, vstupní vodič [31:0] čítač, // řídicí signály pro LED diody

- Upravte soubor blinking_led.sv file pro připojení led_two_on k bitu 23 čítače ze statické oblasti a vytvoření instance modulu blinking_led_child. Po úpravách bude vaše blinking_led.sv file musí vypadat následovně:

- O úpravě celého designu files, znovu zkompilujte projekt kliknutím na Zpracování ➤ Spustit kompilaci

Krok 3: Vytvoření návrhových oddílů

Musíte vytvořit návrhové oddíly pro každou oblast PR, kterou chcete částečně překonfigurovat. Ve svém návrhu můžete vytvořit libovolný počet nezávislých oddílů nebo PR regionů. Tento výukový program vytvoří dva návrhové oddíly pro instance u_blinking_led_child a u_blinking_led.

Chcete-li vytvořit návrhové oddíly pro hierarchickou částečnou rekonfiguraci:

- Klikněte pravým tlačítkem na instanci u_blinking_led_child v Navigátoru projektu a klikněte na Návrhový oddíl ➤ Nastavit jako návrhový oddíl. Vedle každé instance, která je nastavena jako oddíl, se zobrazí ikona návrhového oddílu.

Obrázek 3. Vytváření návrhových oddílů z Project Navigatoru

- Chcete-li definovat typ oddílu, klepněte pravým tlačítkem na instanci u_blinking_led_child na kartě Hierarchie a klepněte na Návrh oddílu ➤ Rekonfigurovatelné. Typ oddílu můžete definovat až po nastavení instance jako oddílu. Oddíl návrhu se zobrazí v Úkolech View v okně Návrh oddílů.

Obrázek 4. Okno Návrh oddílů

- Upravte název oddílu v okně Design Partitions poklepáním na název. Pro tento referenční návrh přejmenujte název oddílu na pr_partition.

Poznámka: Když vytvoříte oddíl, software Intel Quartus Prime automaticky vygeneruje název oddílu na základě názvu instance a cesty hierarchie. Tento výchozí název oddílu se může u každé instance lišit. - Opakováním kroků 1 a 2 přiřaďte instanci u_blinking_led přestavitelné designové oddíly. Přejmenujte tento oddíl na pr_parent_partition.

Ověřte, že soubor blinking_led.qsf obsahuje následující přiřazení odpovídající vašim rekonfigurovatelným návrhovým oddílům:

Vytvořte návrhové oddíly pro částečnou rekonfiguraci

Krok 4: Přidělení oblasti umístění a směrování pro PR oddíly

Když vytvoříte základní revizi, tok návrhu PR použije přidělení oblasti oddílu PR k umístění odpovídajícího osobního jádra do vyhrazené oblasti. Chcete-li najít a přiřadit oblast PR v půdorysu zařízení pro vaši základní revizi:

- Klepněte pravým tlačítkem na instanci u_blinking_led_child v Navigátoru projektu a klepněte na Oblast logického zámku ➤ Vytvořit novou oblast logického zámku. Oblast se objeví v okně Logic Lock Regions Window.

- Oblast umístění musí zahrnovat logiku blinking_led_child. Vyberte oblast umístění umístěním uzlu v Chip Planner. Klepněte pravým tlačítkem na název oblasti u_blinking_led_child v Navigátoru projektu a klepněte na Vyhledat uzel ➤ Vyhledat v Plánovači čipů.

Obrázek 5. Umístění uzlu plánovače čipů pro blinking_led

- V okně Logic Lock Regions určete souřadnice oblasti umístění ve sloupci Origin. Počátek odpovídá levému dolnímu rohu oblasti. Napřample, chcete-li nastavit oblast umístění se souřadnicemi (X1 Y1) jako (69 10), zadejte Počátek jako X69_Y10. Software Intel Quartus Prime automaticky vypočítá souřadnice (X2 Y2) (vpravo nahoře) pro oblast umístění na základě vámi určené výšky a šířky.

Poznámka: Tento výukový program používá souřadnice (X1 Y1) – (69 10) a výšku a šířku 20 pro oblast umístění. Definujte libovolnou hodnotu pro oblast umístění za předpokladu, že oblast pokrývá logiku blinking_led_child. - Povolte možnosti Reserved a Core-Only.

- Poklepejte na možnost Oblast směrování. Zobrazí se dialogové okno Logic Lock Routing Region Settings.

- Pro typ routování vyberte Pevné s rozšířením. Výběrem této možnosti se automaticky přiřadí délka rozšíření 1.

Poznámka: Oblast směrování musí být větší než oblast umístění, aby byla montérovi poskytnuta dodatečná flexibilita, když motor směruje různé osoby. - Opakujte kroky 1-6 pro instanci u_blinking_led. Umístění na nadřazené úrovni Opakujte kroky 1-6 pro instanci u_blinking_led. Oblast umístění na nadřazené úrovni musí plně obklopovat odpovídající umístění na podřízené úrovni a oblasti směrování a zároveň povolit dostatečný prostor pro umístění logiky na nadřazené úrovni. Tento výukový program používá souřadnice (X1 Y1) – (66 7), výšku 47 a šířku 26 pro oblast umístění instance u_blinking_led.

Obrázek 6. Okno Logic Lock Regions

Ověřte, že soubor blinking_led.qsf obsahuje následující přiřazení odpovídající vašemu plánování podlaží:

- Půdorys návrhu částečné přestavby

- Postupná implementace částečné rekonfigurace

Krok 5: Přidání Intel Arria 10 Partial Reconfiguration Controller IP Core

- K překonfigurování oddílu PR použijte jádro IP řadiče Intel Arria 10 Partial Reconfiguration Controller. Toto jádro IP používá JTAG překonfigurujte PR oddíl. Přidání jádra IP řadiče Intel Arria 10 Partial Reconfiguration Controller do vašeho projektu Intel Quartus Prime:

- Zadejte částečná rekonfigurace v katalogu IP.

- Chcete-li spustit okno IP Parameter Editor Pro, vyberte jádro IP řadiče Intel Arria 10 Partial Reconfiguration Controller z knihovny IP a klikněte na Přidat.

- V dialogovém okně Nová varianta IP zadejte jako pr_ip file jméno a klikněte na Vytvořit. Použijte výchozí parametrizaci pro pr_ip. Ujistěte se, že Povolit JTAG režim ladění a možnosti rozhraní Enable freeze jsou zapnuty a možnost Enable Avalon-MM slave interface je vypnutá.

Obrázek 7. Parametry jádra IP řadiče Intel Arria 10 Partial Reconfiguration

- Klikněte na Finish a ukončete editor parametrů bez generování systému. Software Intel Quartus Prime vytváří variaci IP pr_ip.ip filea dodává file do projektu blinking_led.

Poznámka:

- Pokud kopírujete soubor pr_ip.ip file ze složky hpr ručně upravte soubor blinking_led.qsf file zahrnout následující řádek: set_global_assignment -name IP_FILE pr_ip.ip

- Umístěte IP_FILE úkol po SDC_FILE úkoly (jtag.sdc a blinking_led.sdc) ve vašem blinking_led.qsf file. Toto řazení zajišťuje vhodné omezení jádra IP částečné rekonfigurace.

Poznámka: Chcete-li zjistit hodiny, SDC file pro PR IP musí následovat jakýkoli SDC, který vytváří hodiny, které používá jádro IP. Usnadníte tuto objednávku tím, že zajistíte .ip file pro PR jádro IP přichází za jakoukoli .ip files nebo SDC filese používá k vytvoření těchto hodin v QSF file pro revizi vašeho projektu Intel Quartus Prime. Další informace naleznete v části Časová omezení v uživatelské příručce částečné rekonfigurace IP Core.

Související informace

- Částečná rekonfigurace IP řešení Uživatelská příručka

- Informace o jádru IP řadiče oblasti částečné rekonfigurace.

- Částečná rekonfigurace IP Core Uživatelská příručka

- Informace o časových omezeních.

Aktualizace designu nejvyšší úrovně

Chcete-li aktualizovat top.SV file s instancí PR_IP:

- Chcete-li přidat instanci PR_IP do návrhu nejvyšší úrovně, vložte následující blok kódu na začátek.SV file:

- Chcete-li během rekonfigurace přinutit výstupní porty k logické 1, použijte výstup řídicího signálu zmrazení z PR_IP. Aby však bylo možné pozorovat, že kontrolka LED stále bliká z nadřazeného oddílu PR při programování PR podřízeného oddílu, řídicí signál zmrazení nevypne LED_two_on. Ujistěte se, že pr_led_two_on je přímo

- Chcete-li přiřadit instanci výchozí nadřazené osoby (blinking_led), aktualizujte soubor top.SV file s následujícím blokem kódu:

Obrázek 8. Částečná rekonfigurace Integrace jádra IP

Krok 6: Definování osob

Tento referenční návrh definuje pět samostatných osob pro nadřazený a podřízený oddíl PR. Chcete-li definovat a zahrnout persony do vašeho projektu:

- Vytvořte čtyři SystemVerilog files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv a blinking_led_slow.sv ve vašem pracovním adresáři pro pět osob.

Poznámka: Pokud vytvoříte SystemVerilog filez textového editoru Intel Quartus Prime, vypněte možnost Přidat file na aktuální možnost projektu, při ukládání files.

Tabulka 2. Reference Design Personas

| File Jméno | Popis | Kód |

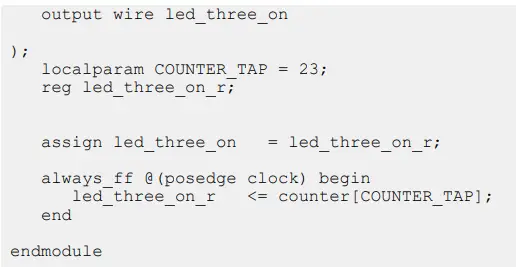

| blikající_led_child.sv | Výchozí persona pro návrh na dětské úrovni |

`časové měřítko 1 ps / 1 ps `default_nettype žádný modul blinking_led_child ( // hodiny vstupní drátové hodiny, vstupní vodič [31:0] čítač,

// Řídicí signály pro výstupní vodič LED diod led_three_on

); localparam COUNTER_TAP = 23; reg led_three_on_r;

přiřadit led_three_on = led_three_on_r; always_ff @(posedge clock) začít led_three_on_r <= čítač[COUNTER_TAP]; konec

koncový modul |

| pokračování… | ||

| File Jméno | Popis | Kód |

| blinking_led_child_slow.sv | The

LED_THREE bliká pomaleji |

`časové měřítko 1 ps / 1 ps `default_nettype žádný

modul blinking_led_child_slow (

// hodiny vstupní drátové hodiny, vstupní vodič [31:0] čítač,

// Řídicí signály pro výstupní vodič LED diod led_three_on );

localparam COUNTER_TAP = 27; reg led_three_on_r;

přiřadit led_three_on = led_three_on_r; always_ff @(posedge clock) začít led_three_on_r <= čítač[COUNTER_TAP]; konec

koncový modul |

| blikající_led_child_empty.sv | The

LED_THREE zůstane ON |

`časové měřítko 1 ps / 1 ps `default_nettype žádný

modul blinking_led_child_empty (

// hodiny vstupní drátové hodiny, vstupní vodič [31:0] čítač,

// Řídicí signály pro výstupní vodič LED diod led_three_on

);

// LED je aktivní nízko přiřadit led_three_on = 1'b0;

koncový modul |

| blikající_led_slow.sv | LED_TWO

bliká pomaleji. |

`časové měřítko 1 ps / 1 ps `default_nettype žádný modul blinking_led_slow( // hodiny vstupní drátové hodiny, vstupní vodič [31:0] čítač,

// Řídicí signály pro výstupní vodič LED led_two_on, výstupní vodič led_three_on

);

localparam COUNTER_TAP = 27; reg led_dva_on_r; přiřadit led_two_on = led_dwo_on_r;

// Pult: always_ff @(posedge clock) begin led_two_on_r <= counter[COUNTER_TAP]; konec

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .counter (counter), .hodiny (hodiny) |

| File Jméno | Popis | Kód |

| );ndmodul |

Krok 3: Vytvoření návrhových oddílů na straně 7

Krok 7: Vytvoření revizí

Průběh návrhu PR využívá funkci revizí projektu v softwaru Intel Quartus Prime. Váš počáteční návrh je základní revize, kde definujete hranice statického regionu a rekonfigurovatelné regiony na FPGA. Ze základní revize vytvoříte více revizí. Tyto revize obsahují různé implementace pro PR regiony. Všechny revize implementace PR však používají stejné výsledky umístění a směrování na nejvyšší úrovni ze základní revize. Chcete-li sestavit návrh PR, musíte vytvořit revizi implementace PR a revizi syntézy pro každou osobu. V tomto referenčním návrhu kromě základní revize (blinking_led) obsahují tři osoby na podřízené úrovni a dvě osoby na rodičovské úrovni pět samostatných revizí syntézy a pět samostatných revizí implementace:

Tabulka 3. Revize pro osoby dvou rodičů a osoby tří dětí

| Revize syntézy | Revize implementace |

| blinking_led_parent, blinking_led_default | blikající_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blikající_led_pr_bravo |

| blinking_led_parent, blinking_led_child_empty | blikající_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | blikající_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_empty | blikající_led_pr_emma |

Vytváření revizí implementace

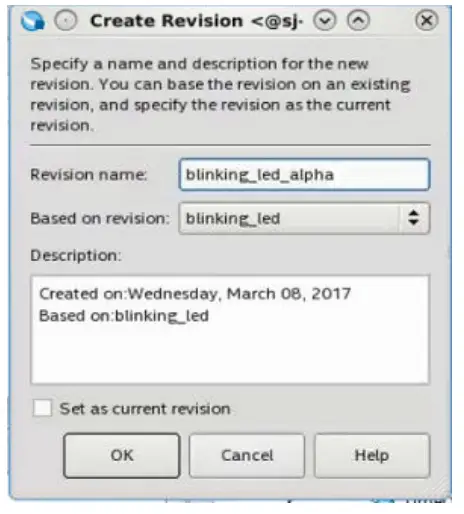

Chcete-li vytvořit revize implementace PR:

- Chcete-li otevřít dialogové okno Revize, klepněte na Projekt ➤ Revize.

- Chcete-li vytvořit novou revizi, poklepejte na < >.

- Zadejte název revize jako blinking_led_pr_alpha a vyberte blinking_led pro Based on Revision.

- Vypněte možnost Nastavit jako aktuální revizi a klepněte na OK.

- Podobně vytvořte revize blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta a blinking_led_pr_emma na základě revize blinking_led.

Poznámka: Nenastavujte výše uvedené revize jako aktuální revize.

Obrázek 9. Vytváření revizí

Vytváření revizí pouze pro syntézu

Chcete-li pro persony vytvořit revize pouze pro syntézu, musíte přiřadit entitu nejvyšší úrovně a odpovídající SystemVerilog file pro každou z osob:

- V softwaru Intel Quartus Prime klikněte na Projekt ➤ Revize.

- Vytvořte revizi blinking_led_default na základě revize blinking_led. Nenastavujte tuto revizi jako aktuální revizi.

- Upravte soubor blinking_led_default.qsf file zahrnout následující úkoly:

set_global_assignment -name TOP_LEVEL_ENTITY blikající_led_child

set_global_assignment -name SYSTEMVERILOG_FILE - Podobně vytvořte revize blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent a blinking_led_parent_slow založené na revizi blinking_led. Nenastavujte tyto revize jako aktuální revize.

- Aktualizujte soubory blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf a blinking_led_parent_slow.qsf files s jejich odpovídajícími

TOP_LEVEL_ENTITY a SYSTEMVERILOG_FILE úkoly:

- Abyste se vyhnuli chybám při syntéze, zajistěte, aby byla provedena revize syntézy files pro podřízené oddíly neobsahují žádný návrhový oddíl, přiřazení pinů ani logický zámek

krajské úkoly. Také revize syntézy files pro nadřazené oddíly musí obsahovat pouze přiřazení návrhových oddílů pro odpovídající podřízené oddíly. Odstraňte tato přiřazení, pokud existují, v souborech blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf a blinking_led_parent_slow.pdf files

- Zahrňte následující úkoly do blinking_led_parent.qsf a blinking_led_parent_slow.qsf files:

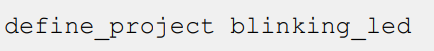

- Ověřte, že soubor blinking_led.qpf file obsahuje následující revize bez konkrétního pořadí:

- Poznámka: Pokud kopírujete revizi files ze složky hpr, ručně aktualizujte soubor blinking_led.qpf file s výše uvedenými řádky kódu.

Určení typu revize

Pro každou z vašich revizí musíte přiřadit typ revize. Existují tři typy revizí:

- Částečná rekonfigurace – základ

- Částečná rekonfigurace – Syntéza osobnosti

- Částečná rekonfigurace – Implementace persony

- Následující tabulka uvádí přiřazení typu revize pro každou z revizí:

Tabulka 4. Typy revizí

| Název revize | Typ revize |

| blikající_led.qsf | Částečná rekonfigurace – základ |

| blinking_led_default.qsf | Částečná rekonfigurace – Syntéza osobnosti |

| blinking_led_child_empty.qsf | Částečná rekonfigurace – Syntéza osobnosti |

| blinking_led_child_slow.qsf | Částečná rekonfigurace – Syntéza osobnosti |

| blinking_led_parent.qsf | Částečná rekonfigurace – Syntéza osobnosti |

| blinking_led_parent_slow.qsf | Částečná rekonfigurace – Syntéza osobnosti |

| blikající_led_pr_alpha.qsf | Částečná rekonfigurace – Implementace persony |

| blikající_led_pr_bravo.qsf | Částečná rekonfigurace – Implementace persony |

| blikající_led_pr_charlie.qsf | Částečná rekonfigurace – Implementace persony |

| blikající_led_pr_delta.qsf | Částečná rekonfigurace – Implementace persony |

| blikající_led_pr_emma.qsf | Částečná rekonfigurace – Implementace persony |

- Klepněte na Projekt ➤ Revize. Zobrazí se dialogové okno Revize.

- Ve sloupci Název revize vyberte blinking_led a klikněte na Nastavit aktuální.

- Klepněte na tlačítko Použít. Otevře se revize blinking_led.

- Chcete-li nastavit typ revize pro blinking_led, klepněte na Přiřazení ➤ Nastavení ➤ Obecné.

- Vyberte Typ revize jako Částečná rekonfigurace – Základní.

- Podobně nastavte typy revizí pro dalších deset revizí, jak je uvedeno v tabulce výše.

- Poznámka: Před přiřazením typu revize musíte každou revizi nastavit jako aktuální. Ověřte, že každý .qsf file obsahuje následující zadání:

- Poznámka: Přidejte jakákoli nastavení specifická pro Fitter, která chcete použít při kompilaci implementace PR, do revizí implementace persona. Nastavení specifická pro Fitter ovlivní přizpůsobení osobnosti, ale neovlivní importovanou statickou oblast. Můžete také přidat jakákoli nastavení specifická pro syntézu k jednotlivým revizím persona syntézy.

Vytvářejte revize pro Personas

Krok 8: Generování skriptu toku hierarchické částečné rekonfigurace

Chcete-li vygenerovat skript toku hierarchické částečné rekonfigurace:

- Z příkazového prostředí Intel Quartus Prime vytvořte šablonu toku spuštěním následujícího příkazu:

- Intel Quartus Prime generuje soubor a10_hier_partial_reconfig/flow.tcl file.

- Přejmenujte vygenerovaný a10_hier_partial_reconfig/setup.tcl.exampsoubor a10_hier_partial_reconfig/setup.tcl a upravte skript tak, aby specifikoval podrobnosti vašeho projektu částečné rekonfigurace:

a. Chcete-li definovat název projektu, aktualizujte následující řádek: b. Chcete-li definovat základní revizi, aktualizujte následující řádek:

b. Chcete-li definovat základní revizi, aktualizujte následující řádek:

- Chcete-li definovat každou z revizí implementace částečné rekonfigurace, spolu s názvy oddílů PR a revizí zdroje, která implementuje revize, aktualizujte následující řádky:

Poznámka: Všechny projekty revizí musí být ve stejném adresáři jako blinking_led.qpf. V opačném případě aktualizujte odpovídajícím způsobem skript toku.

Krok 9: Spuštění skriptu toku hierarchické částečné rekonfigurace

Chcete-li spustit skript toku hierarchické částečné rekonfigurace:

- Klepněte na Nástroje ➤ Skripty Tcl. Zobrazí se dialogové okno Skripty Tcl.

- Klikněte na Přidat do projektu, procházejte a vyberte soubor a10_hier_partial_reconfig/flow.tcl.

- V podokně Knihovny vyberte soubor a10_hier_partial_reconfig/flow.tcl a klepněte na Spustit.

Tento skript spustí syntézu pro tři osoby. Intel Quartus Prime generuje objekt SRAM File (.sof), částečně maskovaný objekt SRAM File (.pmsf) a nezpracovaný binární soubor File (.rbf) pro každou z person.

Poznámka: Chcete-li spustit skript z příkazového prostředí Intel Quartus Prime, zadejte následující příkaz:

- Zkompilujte návrh částečné rekonfigurace

- Použití skriptu toku částečné rekonfigurace

- Konfigurace skriptu toku částečné rekonfigurace

- Generovat programování Files

Krok 10: Programování desky

Než začnete:

- Připojte napájecí zdroj k vývojové desce Intel Arria 10 SoC.

- Připojte kabel USB Blaster mezi port USB počítače a port USB Blaster na vývojové desce.

Spuštění návrhu na vývojové desce Intel Arria 10 SoC:

- Otevřete software Intel Quartus Prime a klepněte na Nástroje ➤ Programátor.

- V Programátoru klikněte na Nastavení hardwaru a vyberte USB-Blaster.

- Klikněte na Auto Detect a vyberte zařízení, 10AS066N3.

- Klepněte na tlačítko OK. Software Intel Quartus Prime detekuje a aktualizuje programátor pomocí tří čipů FPGA na desce.

- Vyberte zařízení 10AS066N3 a klikněte na Změnit File a načtěte soubor blinking_led_pr_alpha.sof file.

- Povolit Program/Konfigurovat pro blinking_led_pr_alpha.sof file.

- Klikněte na Start a počkejte, až ukazatel průběhu dosáhne 100 %.

- Sledujte, jak LED diody na desce blikají stejnou frekvencí jako původní plochý design.

- Chcete-li naprogramovat pouze podřízenou oblast PR, klepněte pravým tlačítkem na soubor blinking_led_pr_alpha.sof file v Programátoru a klikněte na Přidat programování PR File.

- Vyberte soubor blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file.

- Zakázat Program/Konfigurovat pro blinking_led_pr_alpha.sof file.

- Povolit Program/Konfigurovat pro blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file a klepněte na tlačítko Start. Na desce sledujte, jak LED[0] a LED[1] dále blikají. Když ukazatel průběhu dosáhne 100 %, LED[2] bliká stejnou rychlostí a LED[3] bliká pomaleji.

- Chcete-li naprogramovat nadřazenou i podřízenou oblast PR, klepněte pravým tlačítkem na soubor .rbf file v Programátoru a klikněte na Změnit programování PR File.

- Vyberte soubor blinking_led_pr_delta.pr_parent_partition.rbf file.

- Klepněte na tlačítko Start. Pozorujte na desce, že LED[0] a LED[1] stále blikají. Když ukazatel průběhu dosáhne 100 %, LED[2] i LED[3] blikají pomaleji.

- Opakujte výše uvedené kroky pro dynamické přeprogramování pouze podřízené PR oblasti nebo obou rodičovských a podřízených PR oblastí současně.

Obrázek 10. Programování vývojové desky Intel Arria 10 SoC

Úprava existující persony

- Stávající personu můžete změnit i po úplném zkompilování základní revize.

- Napřample, aby persona blinking_led_child_slow blikala ještě pomaleji:

- V souboru blinking_led_child_slow.sv file, upravte parametr COUNTER_TAP z 27 na 28.

- Chcete-li znovu syntetizovat a znovu implementovat tuto personu, musíte znovu zkompilovat všechny revize pouze pro syntézu a revize implementace ovlivněné změnou. Upravte skript setup.tcl tak, aby obsahoval následující řádky:

Poznámka: Při definování pr_parent_parition pro revizi blinking_led_pr_delta importujete konečný snímek této persony pro implementaci. Výsledkem je, že implementace logiky nadřazeného oddílu zůstává stejná, zatímco se upravuje a implementuje odpovídající podřízený oddíl.

Poznámka: Při definování pr_parent_parition pro revizi blinking_led_pr_delta importujete konečný snímek této persony pro implementaci. Výsledkem je, že implementace logiky nadřazeného oddílu zůstává stejná, zatímco se upravuje a implementuje odpovídající podřízený oddíl. Tento příkaz znovu syntetizuje revizi syntézy blinking_led_child_slow a poté spustí kompilaci implementace PR pomocí blinking_led_pr_bravo.

Tento příkaz znovu syntetizuje revizi syntézy blinking_led_child_slow a poté spustí kompilaci implementace PR pomocí blinking_led_pr_bravo. - Chcete-li provést kompilaci revizí pouze pro syntézu, spusťte následující příkaz: Tento příkaz znovu nezkompiluje základní revizi.

- Chcete-li provést kompilaci revizí implementace, spusťte následující příkaz:

- Tento příkaz znovu nezkompiluje základní revizi.

- Pro naprogramování výsledného RBF postupujte podle kroků v Kroku 10: Programování desky na straně 22 file do FPGA.

Poznámka: Chcete-li se vyhnout spouštění celého toku pro každou revizi, definujte revize pouze pro syntézu a revize implementace ve skriptu setup.tcl a spusťte skript.

Přidání nové persony do designu

Po úplné kompilaci vašich základních revizí můžete stále přidávat nové persony a jednotlivě je sestavovat.

Napřample, k definování nové podřízené persony pro blinking_led_parent_slow, která vypne led_three:

- Zkopírujte soubor blinking_led_child_empty.sv do souboru blinking_led_chdild_off.sv.

- V souboru blinking_led_child_off.sv file, upravit přiřazení, přiřadit led_three_on = 1'b0; pro přiřazení led_three_on = 1'b1;. Ujistěte se, že jste změnili název modulu z blinking_led_child_empty na blinking_led_child_off.

- Vytvořte novou revizi syntézy, blinking_led_child_off, podle kroků v části Vytváření revizí pouze pro syntézu na stránce 16.

Poznámka: Revize blinking_led_child_off musí používat soubor blinking_led_child_off.sv file. - Vytvořte novou revizi implementace, blinking_led_pr_foxtrot, podle kroků v části Vytvoření revizí implementace na stránce 15.

- Aktualizujte soubor a10_hier_partial_reconfig/setup.tcl file definovat novou implementaci PR:

- Zkompilujte pouze tuto novou revizi syntézy a implementace spuštěním následujícího příkazu:

Úplné informace o hierarchické částečné rekonfiguraci pro zařízení Intel Arria 10 naleznete v části Vytvoření návrhu částečné rekonfigurace ve svazku 1 příručky Intel Quartus Prime Pro Edition.

Související informace

- Vytvoření návrhu částečné rekonfigurace

- Online školení částečné rekonfigurace

Historie revizí dokumentu

Tabulka 5. Historie revizí dokumentu

| Verze dokumentu | Verze softwaru | Změny |

| 2017.11.06 | 17.1.0 | • Aktualizováno Požadavky na referenční design část s verzí softwaru

• Aktualizováno Plochý referenční design bez PR dělení obrázek se změnami konstrukčního bloku • Aktualizováno Referenční design Files tabulka s informacemi o Modul Top_counter.sv • Aktualizováno Částečná rekonfigurace Integrace jádra IP obrázek se změnami konstrukčního bloku • Aktualizace čísel – Okno návrhových oddílů a Okno oblastí logického zámku odrážet nové GUI • File změny názvů • Úpravy textu |

| 2017.05.08 | 17.0.0 | První vydání dokumentu |

Dokumenty / zdroje

|

intel AN 805 Hierarchická částečná rekonfigurace designu na Arria 10 SoC Development Board [pdfUživatelská příručka AN 805 Hierarchická částečná rekonfigurace designu na Arria 10 SoC Development Board, AN 805, Hierarchická částečná rekonfigurace designu na Arria 10 SoC Development Board, Rekonfigurace designu na Arria 10 SoC Development Board, Arria 10 SoC Development Board, 10 SoC rozvojová rada |