intel AN 805 stigskipt endurstilling að hluta til hönnunar á Arria 10 SoC þróunarborði

Kennsla um stigskipting að hluta til endurstillingar fyrir Intel® Arria® 10 SoC þróunarborð

Þessi umsóknarskýring sýnir að umbreyta einfaldri hönnun í stigveldislega endurstillanlega hönnun og útfæra hönnunina á Intel® Arria® 10 SoC þróunarborðinu. Hierarchical partial reconfiguration (HPR) er sérstök tegund af partial reconfiguration (PR), þar sem þú inniheldur PR svæði innan annars PR svæði. Þú getur búið til margar persónur fyrir bæði barna- og foreldri skiptinguna. Þú hreiður undirsneiðina innan foreldrasneiðanna þeirra. Endurstilla undirsneið hefur ekki áhrif á aðgerð á yfir- eða kyrrstæðum svæðum. Endurstilla foreldrasneið hefur ekki áhrif á aðgerðina á kyrrstæða svæðinu, heldur kemur í stað undirsneiða móðursvæðisins fyrir sjálfgefna undirsneiðarpersónur. Þessi aðferðafræði er áhrifarík í kerfum þar sem margar aðgerðir deila sama FPGA tækinu í tíma.

Endurstilling að hluta veitir eftirfarandi framfarir í flatri hönnun:

- Leyfir endurstillingu hönnunar í keyrslutíma

- Eykur sveigjanleika hönnunarinnar

- Dregur úr kerfistíma

- Styður kraftmikla tíma-multiplexing aðgerðir í hönnuninni

- Lækkar kostnað og orkunotkun með hagkvæmri nýtingu borðpláss

- Athugið:

- Innleiðing þessarar tilvísunarhönnunar krefst grunnþekkingar á Intel Quartus® Prime FPGA útfærsluflæðinu og þekkingu á aðal Intel Quartus Prime verkefninu. files.

Tengdar upplýsingar

- Intel Arria 10 SoC þróunarsett notendahandbók

- Hugmyndir um endurstillingar að hluta

- Hönnunarflæði fyrir endurstillingu að hluta

- Hönnunarráðleggingar um endurstillingar að hluta

- Athugasemdir við hönnun að hluta til endurstillingar

Tilvísunarkröfur um hönnun

Þessi tilvísunarhönnun krefst eftirfarandi:

- Intel Quartus Prime Pro Edition hugbúnaðarútgáfa 17.1 fyrir hönnunarútfærsluna.

- Intel Arria 10 SoC þróunarsett fyrir FPGA útfærsluna.

Intel Corporation. Allur réttur áskilinn. Intel, Intel lógóið og önnur Intel merki eru vörumerki Intel Corporation eða dótturfélaga þess. Intel ábyrgist frammistöðu FPGA- og hálfleiðaravara sinna samkvæmt gildandi forskriftum í samræmi við staðlaða ábyrgð Intel, en áskilur sér rétt til að gera breytingar á hvaða vörum og þjónustu sem er hvenær sem er án fyrirvara. Intel tekur enga ábyrgð eða skaðabótaábyrgð sem stafar af notkun eða notkun á neinum upplýsingum, vöru eða þjónustu sem lýst er hér nema sérstaklega hafi verið samið skriflega af Intel. Viðskiptavinum Intel er bent á að fá nýjustu útgáfuna af tækjaforskriftum áður en þeir treysta á birtar upplýsingar og áður en pantað er fyrir vörur eða þjónustu.

- Önnur nöfn og vörumerki má gera tilkall til sem eign annarra.

Reference Design Overview

- Þessi viðmiðunarhönnun samanstendur af einum 32 bita teljara. Á borðinu tengir hönnunin klukkuna við 50MHz uppsprettu og tengir úttakið við fjóra LED á FPGA. Val á úttakinu úr teljarabitunum í ákveðinni röð veldur því að LED-ljósin blikka á ákveðinni tíðni.

Mynd 1. Flat tilvísunarhönnun án PR skiptingar

Tilvísunarhönnun Files

Kennsla um endurstillingu að hluta er fáanleg á eftirfarandi stað: https://github.com/intel/fpga-partial-reconfig

Til að hlaða niður kennsluefninu:

- Smelltu á Clone eða niðurhal.

- Smelltu á Download ZIP. Taktu upp FPGA-partial-config-master.zip file.

- Farðu í tutorials/a10_soc_devkit_blinking_led_hpr undirmöppuna til að fá aðgang að tilvísunarhönnuninni.

Flatmöppan samanstendur af eftirfarandi files:

Tafla 1. Tilvísunarhönnun Files

| File Nafn | Lýsing |

| efst. SV | Efsta stigið file inniheldur flata útfærslu hönnunarinnar. Þessi eining sýnir blinking_led undirskiptinguna og top_counter eininguna. |

| top_counter.sv | 32-bita teljari á efstu stigi sem stjórnar LED[1] beint. Skráð framleiðsla teljarans stjórnar LED[0] og knýr einnig LED[2] og LED[3] í gegnum blinking_led eininguna. |

| blinking_led.sdc | Skilgreinir tímatakmarkanir fyrir verkefnið. |

| áfram… | |

| File Nafn | Lýsing |

| blinking_led.SV | Í þessari kennslu breytir þú þessari einingu í foreldra PR skipting. Einingin fær skráð úttak af top_counter einingunni, sem stjórnar LED[2] og LED[3]. |

| blinking_led.qpf | Intel Quartus Prime verkefni file inniheldur lista yfir allar endurskoðanir í verkefninu. |

| blinking_led.qsf | Intel Quartus Prime stillingar file sem inniheldur verkefni og stillingar fyrir verkefnið. |

Athugið: Hpr mappan inniheldur allt sett af files þú býrð til með því að nota þessa forritaskýringu. Vísa til þessara files hvenær sem er á meðan á göngunni stendur.

Mynd 2. Tilvísunarhönnun Files

Tilvísun Hönnun Walkthrough

Eftirfarandi skref lýsa beitingu endurstillingar að hluta á flata hönnun. Kennslan notar Intel Quartus Prime Pro Edition hugbúnaðinn fyrir Intel Arria 10 SoC þróunarborðið:

- Skref 1: Byrjað á síðu 6

- Skref 2: Búðu til undireiningu barnastigs á síðu 6

- Skref 3: Að búa til hönnunarskiptingu á síðu 7

- Skref 4: Úthlutun staðsetningar og leiðarsvæðis fyrir PR skipting á síðu 9

- Skref 5: Bæta við Intel Arria 10 Partial Reconfiguration Controller IP Core á síðu 10

- Skref 6: Að skilgreina persónur á síðu 13

- Skref 7: Búa til endurskoðun á síðu 15

- Skref 8: Að búa til flæðisskrift fyrir stigveldisbreytingar að hluta á síðu 20

- Skref 9: Að keyra stigveldisforskrift um endurstillingarflæði á síðu 21

- Skref 10: Forritun stjórnarinnar á síðu 22

Skref 1: Að byrja

Til að afrita tilvísunarhönnun files að vinnuumhverfi þínu og settu saman blinking_led flata hönnunina:

- Búðu til möppu í vinnuumhverfi þínu, a10_soc_devkit_blinking_led_hpr.

- Afritaðu niðurhalaða kennsluefni/a10_soc_devkit_blinking_led_hpr/flat undirmöppu yfir í möppuna, a10_soc_devkit_blinking_led_hpr.

- Í Intel Quartus Prime Pro Edition hugbúnaðinum, smelltu á File ➤ Opnaðu Project og veldu blinking_led.qpf.

- Til að setja saman flata hönnunina, smelltu á Vinnsla ➤ Byrjaðu samantekt.

Skref 2: Að búa til undireiningu barnastigs

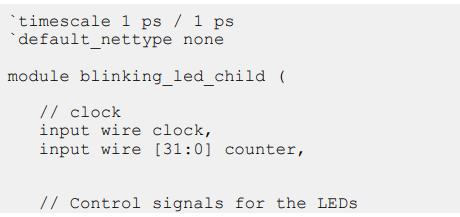

Til að breyta þessari flatu hönnun í stigveldi PR hönnun, verður þú að búa til undireiningu (blinking_led_child. SV) sem er hreiður inn í móður undireininguna (blinking_led.sv).

- Búðu til nýja hönnun file, blinking_led_child.sv, og bættu eftirfarandi kóðalínum við þetta file: tímakvarði 1 ps / 1 ps `default_nettype engin eining blinking_led_child ( // klukka inntaksvír klukka, inntaksvír [31:0] teljari, // Stýrimerki fyrir ljósdíóða

- Breyttu á blinking_led.sv file til að tengja led_two_on við bita 23 af teljaranum frá kyrrstöðusvæðinu og sýna blinking_led_child eininguna. Eftir breytingar mun blinking_led.sv file verður að birtast sem hér segir:

- Um að breyta allri hönnuninni files, settu verkefnið saman aftur með því að smella á Vinnsla ➤ Byrjaðu samantekt

Skref 3: Að búa til hönnunarskiptingu

Þú verður að búa til hönnunarskiptingar fyrir hvert PR svæði sem þú vilt endurstilla að hluta. Þú getur búið til hvaða fjölda óháðra skiptinga eða PR-svæða sem er í hönnun þinni. Þessi kennsla býr til tvær hönnunarskiptingar fyrir tilvikin u_blinking_led_child og u_blinking_led.

Til að búa til hönnunarsneiðar fyrir stigveldislega endurstillingu að hluta:

- Hægrismelltu á u_blinking_led_child tilvikið í Project Navigator og smelltu á Design Partition ➤ Set as Design Partition. Tákn fyrir hönnunarskiptingu birtist við hlið hvers tilviks sem er stillt sem skipting.

Mynd 3. Að búa til hönnunarþiljur frá Project Navigator

- Til að skilgreina tegund skiptingarinnar skaltu hægrismella á u_blinking_led_child tilvikið í stigveldisflipanum, smella á Hönnun skipting ➤ Endurstillanleg. Þú getur aðeins skilgreint skiptingargerðina eftir að tilvikið hefur verið stillt sem skipting. Hönnunarskiptingin birtist á Verkefnum View flipanum í Hönnunarskilaglugganum.

Mynd 4. Hönnunar skiptingargluggi

- Breyttu heiti skiptingarinnar í Design Partitions glugganum með því að tvísmella á nafnið. Fyrir þessa tilvísunarhönnun, endurnefna skiptingarheitið í pr_partition.

Athugið: Þegar þú býrð til skipting býr Intel Quartus Prime hugbúnaðurinn sjálfkrafa til skiptingarheiti, byggt á nafni tilviks og stigveldisleið. Þetta sjálfgefna skiptingarheiti getur verið breytilegt með hverju tilviki. - Endurtaktu skref 1 og 2 til að úthluta endurstillanlegum hönnunarsneiðum á u_blinking_led tilvikið. Endurnefna þessa skipting í pr_parent_partition.

Staðfestu að blinking_led.qsf innihaldi eftirfarandi verkefni, sem samsvara endurstillanlegum hönnunarhlutunum þínum:

Búðu til hönnunarskiptingar fyrir endurstillingu að hluta

Skref 4: Úthlutun staðsetningar og leiðarsvæðis fyrir PR skipting

Þegar þú býrð til grunnendurskoðunina notar PR hönnunarflæðið úthlutun PR skiptingarsvæðisins til að setja samsvarandi persónukjarna á frátekna svæðinu. Til að finna og úthluta PR-svæðinu í grunnplani tækisins fyrir grunnendurskoðunina þína:

- Hægrismelltu á u_blinking_led_child tilvikið í Project Navigator og smelltu á Logic Lock Region ➤ Create New Logic Lock Region. Svæðið birtist á Logic Lock Regions glugganum.

- Staðsetningarsvæðið þitt verður að innihalda blinking_led_child rökfræðina. Veldu staðsetningarsvæðið með því að finna hnútinn í Chip Planner. Hægrismelltu á u_blinking_led_child svæðisheitið í Project Navigator og smelltu á Locate Node ➤ Finndu í Chip Planner.

Mynd 5. Staðsetning Chip Planner Node fyrir blinking_led

- Í glugganum Röklæsingarsvæði skaltu tilgreina hnit staðsetningarsvæðisins í dálkinum Uppruni. Uppruni samsvarar neðra vinstra horni svæðisins. Til dæmisample, til að stilla staðsetningarsvæði með (X1 Y1) hnitum sem (69 10), tilgreinið uppruna sem X69_Y10. Intel Quartus Prime hugbúnaðurinn reiknar sjálfkrafa út (X2 Y2) hnitin (efst til hægri) fyrir staðsetningarsvæðið, byggt á hæð og breidd sem þú tilgreinir.

Athugið: Þessi kennsla notar (X1 Y1) hnitin – (69 10) og hæð og breidd 20 fyrir staðsetningarsvæðið. Skilgreindu hvaða gildi sem er fyrir staðsetningarsvæðið, að því tilskildu að svæðið nái yfir blinking_led_child rökfræði. - Virkjaðu valkostina frátekið og eingöngu kjarna.

- Tvísmelltu á valkostinn Routing Region. Glugginn Logic Lock Routing Region Settings gluggann birtist.

- Veldu Fast með stækkun fyrir leiðargerðina. Með því að velja þennan valkost er stækkunarlengd 1 sjálfkrafa úthlutað.

Athugið: Leiðbeiningasvæðið verður að vera stærra en staðsetningarsvæðið, til að veita búnaðinum aukinn sveigjanleika þegar vélin stýrir mismunandi persónum. - Endurtaktu skref 1 -6 fyrir u_blinking_led tilvikið. Staðsetning á foreldrastigi Endurtaktu skref 1 -6 fyrir u_blinking_led tilvikið. Staðsetningarsvæði foreldrastigs verður að fullu umlykja samsvarandi staðsetningar- og leiðarsvæði á barnastigi en leyfa nægilegt pláss fyrir rökfræðistaðsetningu foreldrastigsins. Þessi kennsla notar (X1 Y1) hnitin - (66 7), hæð 47 og breidd 26 fyrir staðsetningarsvæði u_blinking_led tilviksins.

Mynd 6.Logic Lock Regions Gluggi

Staðfestu að blinking_led.qsf innihaldi eftirfarandi verkefni, sem samsvara gólfskipulagi þínu:

- Gólfskipuleggja hönnunina að hluta til endurstillingar

- Innleiðir smám saman endurstillingu að hluta

Skref 5: Bæta við IP Core Intel Arria 10 Partial Reconfiguration Controller

- Notaðu Intel Arria 10 Partial Reconfiguration Controller IP kjarna til að endurstilla PR skiptinguna. Þessi IP kjarni notar JTAG til að endurstilla PR skiptinguna. Til að bæta Intel Arria 10 Partial Reconfiguration Controller IP kjarna við Intel Quartus Prime verkefnið þitt:

- Sláðu inn hluta endurstillingar í IP vörulista.

- Til að opna IP Parameter Editor Pro gluggann skaltu velja Intel Arria 10 Partial Reconfiguration Controller IP kjarna úr IP bókasafninu og smella á Bæta við.

- Í New IP Variant svarglugganum skaltu slá inn pr_ip sem file heiti og smelltu á Búa til. Notaðu sjálfgefna breytustillingu fyrir pr_ip. Gakktu úr skugga um að Enable JTAG kveikt er á kembistillingu og Virkja frystingu viðmótsvalkosta og slökkt er á Virkja Avalon-MM þrælviðmótsvalkosti.

Mynd 7. Intel Arria 10 Partial Reconfiguration Controller IP Core Parameters

- Smelltu á Ljúka og farðu úr færibreyturitlinum án þess að búa til kerfið. Intel Quartus Prime hugbúnaður býr til pr_ip.ip IP afbrigðið file, og bætir við file að blinking_led verkefninu.

Athugið:

- Ef þú ert að afrita pr_ip.ip file úr hpr möppunni, breyttu handvirkt blinking_led.qsf file að innihalda eftirfarandi línu: set_global_assignment -nafn IP_FILE pr_ip.ip

- Settu IP_FILE verkefni eftir SDC_FILE verkefni (jtag.sdc og blinking_led.sdc) í blinking_led.qsf file. Þessi röðun tryggir viðeigandi takmörkun á hluta endurstillingar IP kjarna.

Athugið: Til að greina klukkurnar, SDC file fyrir PR IP verður að fylgja hvaða SDC sem er sem býr til klukkur sem IP kjarninn notar. Þú auðveldar þessa pöntun með því að tryggja .ip file fyrir PR IP kjarna kemur á eftir hvaða .ip sem er files eða SDC files notað til að búa til þessar klukkur í QSF file fyrir endurskoðun Intel Quartus Prime verkefnisins. Nánari upplýsingar er að finna í kaflanum Tímatakmarkanir í Notendahandbók um IP Core fyrir hluta endurstillingar.

Tengdar upplýsingar

- Notendahandbók fyrir IP lausnir fyrir hluta endurstillingar

- Fyrir upplýsingar um IP-kjarna fyrir hluta endurstillingar svæðisstýringar.

- Notendahandbók um IP Core endurstilling að hluta

- Til að fá upplýsingar um tímatakmarkanir.

Uppfærsla á topphönnuninni

Til að uppfæra toppinn.SV file með PR_IP tilvikinu:

- Til að bæta PR_IP tilvikinu við hönnunina á efsta stigi skaltu afskrifa eftirfarandi kóðablokk efst.SV file:

- Til að þvinga úttakstengin í rökfræði 1 við endurstillingu, notaðu fryststýringarmerkið frá PR_IP. Hins vegar, til að fylgjast með því að ljósdíóðan haldi áfram að blikka frá foreldra PR skiptingunni á meðan PR forritar barnadeilið, slekkur frystistjórnunarmerkið ekki á led_two_on. Gakktu úr skugga um að pr_led_two_on sé beint

- Til að úthluta tilviki af sjálfgefna foreldrapersónu (blinking_led), uppfærðu toppinn.SV file með eftirfarandi kóðablokk:

Mynd 8. Endurstilling að hluta til IP Core Integration

Skref 6: Skilgreina persónur

Þessi tilvísunarhönnun skilgreinir fimm aðskildar persónur fyrir foreldra- og barn PR skiptinguna. Til að skilgreina og hafa persónurnar með í verkefninu þínu:

- Búðu til fjögur SystemVerilog files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv og blinking_led_slow.sv í vinnuskránni þinni fyrir persónurnar fimm.

Athugið: Ef þú býrð til SystemVerilog files frá Intel Quartus Prime Text Editor, slökktu á Add file að núverandi verkefnisvalkosti, þegar vistun er files.

Tafla 2. Tilvísunarhönnunarpersónur

| File Nafn | Lýsing | Kóði |

| blinking_led_child.sv | Sjálfgefin persóna fyrir hönnun á barnastigi |

`Tímakvarði 1 ps / 1 ps `default_nettype engin eining blinking_led_child ( // klukka inntaksvírklukka, inntaksvír [31:0] teljari,

// Stýrimerki fyrir LED úttaksvír led_three_on

); staðbundin param COUNTER_TAP = 23; reg leiddi_þrjú_á_r;

úthluta led_three_on = led_three_on_r; alltaf_ff @(posedge klukka) byrja led_three_on_r <= teljari[COUNTER_TAP]; enda

endaeining |

| áfram… | ||

| File Nafn | Lýsing | Kóði |

| blinking_led_child_slow.sv | The

LED_THREE blikkar hægar |

`Tímakvarði 1 ps / 1 ps `default_nettype engin

eining blinking_led_child_slow (

// klukka inntaksvírklukka, inntaksvír [31:0] teljari,

// Stýrimerki fyrir LED úttaksvír led_three_on );

staðbundin param COUNTER_TAP = 27; reg leiddi_þrjú_á_r;

úthluta led_three_on = led_three_on_r; alltaf_ff @(posedge klukka) byrja led_three_on_r <= teljari[COUNTER_TAP]; enda

endaeining |

| blinking_led_child_empty.sv | The

LED_THREE helst ON |

`Tímakvarði 1 ps / 1 ps `default_nettype engin

eining blinking_led_child_empty (

// klukka inntaksvírklukka, inntaksvír [31:0] teljari,

// Stýrimerki fyrir LED úttaksvír led_three_on

);

// LED er virk lágt úthluta led_three_on = 1'b0;

endaeining |

| blinking_led_slow.sv | LED_TWO

blikkar hægar. |

`Tímakvarði 1 ps / 1 ps `default_nettype engin eining blinking_led_slow( // klukka inntaksvírklukka, inntaksvír [31:0] teljari,

// Stýrimerki fyrir úttaksvír ljósdíóða led_two_on, úttaksvír led_three_on

);

staðbundin param COUNTER_TAP = 27; reg led_two_on_r; úthluta led_two_on = led_two_on_r;

// Teljarinn: alltaf_ff @(posedge klukka) byrja led_two_on_r <= teljari[COUNTER_TAP]; enda

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .teljari (teljari), .klukka (klukka) |

| File Nafn | Lýsing | Kóði |

| );ndmodule |

Skref 3: Að búa til hönnunarskiptingu á síðu 7

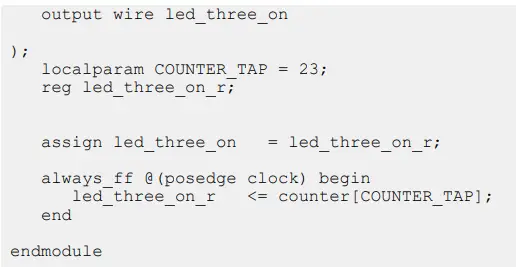

Skref 7: Búa til endurskoðun

PR hönnunarflæðið notar endurskoðunaraðgerðina í Intel Quartus Prime hugbúnaðinum. Upphafleg hönnun þín er grunnútgáfan, þar sem þú skilgreinir mörk kyrrstæðra svæðis og endurstillanleg svæði á FPGA. Frá grunnútgáfunni býrðu til margar endurskoðanir. Þessar endurskoðanir innihalda mismunandi útfærslur fyrir PR svæðin. Hins vegar nota allar útfærslur á PR innleiðingu sömu staðsetningar- og leiðarniðurstöður á efstu stigi frá grunnendurskoðuninni. Til að setja saman PR hönnun, verður þú að búa til PR útfærslu endurskoðun og samruna endurskoðun fyrir hverja persónu. Í þessari tilvísunarhönnun, auk grunnendurskoðunarinnar (blinking_led), innihalda persónurnar þrjár á barnastigi og tvær persónugerðir á foreldrastigi fimm aðskildar endurskoðunarendurskoðun og fimm aðskildar útfærsluendurskoðanir:

Tafla 3. Endurskoðun á persónupersónum tveggja foreldra og þriggja barna persónu

| Synthesis Endurskoðun | Framkvæmd endurskoðun |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_empty | blinking_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | blinking_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_tómt | blinking_led_pr_emma |

Að búa til innleiðingarendurskoðanir

Til að búa til endurskoðun á PR innleiðingu:

- Til að opna endurskoðunargluggann, smelltu á Verkefni ➤ Endurskoðun.

- Til að búa til nýja útgáfu skaltu tvísmella á < >.

- Tilgreindu endurskoðunarheitið sem blinking_led_pr_alpha og veldu blinking_led fyrir Byggt á endurskoðun.

- Slökktu á Stilla sem núverandi endurskoðun valkostinn og smelltu á OK.

- Á sama hátt, búðu til blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta og blinking_led_pr_emma endurskoðun, byggt á blinking_led endurskoðuninni.

Athugið: Ekki stilla ofangreindar breytingar sem núverandi endurskoðun.

Mynd 9. Búa til endurskoðun

Að búa til endurskoðanir sem eingöngu eru til samans

Til að búa til endurskoðun eingöngu fyrir persónurnar verður þú að úthluta efstu einingunni og samsvarandi SystemVerilog file fyrir hverja persónu:

- Í Intel Quartus Prime hugbúnaðinum, smelltu á Project ➤ Revisions.

- Búðu til blinking_led_default endurskoðun byggt á blinking_led endurskoðun. Ekki stilla þessa endurskoðun sem núverandi endurskoðun.

- Breyttu blinking_led_default.qsf file að innihalda eftirfarandi verkefni:

set_global_assignment -nafn TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -heiti SYSTEMVERILOG_FILE - Á sama hátt, búðu til blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent og blinking_led_parent_slow útgáfur byggðar á blinking_led endurskoðun. Ekki stilla þessar breytingar sem núverandi endurskoðun.

- Uppfæra blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf og blinking_led_parent_slow.qsf files með samsvarandi þeirra

TOP_LEVEL_ENTITY og SYSTEMVERILOG_FILE verkefni:

- Til að forðast myndun villur, tryggja að myndun endurskoðun files fyrir barn skiptingin innihalda enga hönnunarsneið, pinnaúthlutun eða Logic Lock

svæðisverkefni. Einnig samantekt endurskoðun files fyrir foreldri skiptingin verður aðeins að innihalda hönnun skipting verkefni fyrir samsvarandi barn skipting. Fjarlægðu þessi verkefni, ef einhver eru, í blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf og blinking_led_parent_slow.pdf files

- Láttu eftirfarandi verkefni fylgja með í blinking_led_parent.qsf og blinking_led_parent_slow.qsf files:

- Staðfestu að blinking_led.qpf file inniheldur eftirfarandi breytingar, í engri sérstakri röð:

- Athugið: Ef þú ert að afrita endurskoðunina files úr hpr möppunni, uppfærðu handvirkt blinking_led.qpf file með ofangreindum kóðalínum.

Tilgreinir endurskoðunartegund

Þú verður að úthluta endurskoðunargerð fyrir hverja endurskoðun þína. Það eru þrjár endurskoðunargerðir:

- Endurstilling að hluta - Grunnur

- Endurstilling að hluta - Persónumyndun

- Endurstilling að hluta - Persónuútfærsla

- Eftirfarandi tafla sýnir endurskoðunargerð verkefna fyrir hverja endurskoðun:

Tafla 4. Tegundir endurskoðunar

| Nafn endurskoðunar | Tegund endurskoðunar |

| blinking_led.qsf | Endurstilling að hluta - Grunnur |

| blinking_led_default.qsf | Endurstilling að hluta - Persónumyndun |

| blinking_led_child_empty.qsf | Endurstilling að hluta - Persónumyndun |

| blinking_led_child_slow.qsf | Endurstilling að hluta - Persónumyndun |

| blinking_led_parent.qsf | Endurstilling að hluta - Persónumyndun |

| blinking_led_parent_slow.qsf | Endurstilling að hluta - Persónumyndun |

| blinking_led_pr_alpha.qsf | Endurstilling að hluta - Persónuútfærsla |

| blinking_led_pr_bravo.qsf | Endurstilling að hluta - Persónuútfærsla |

| blinking_led_pr_charlie.qsf | Endurstilling að hluta - Persónuútfærsla |

| blinking_led_pr_delta.qsf | Endurstilling að hluta - Persónuútfærsla |

| blinking_led_pr_emma.qsf | Endurstilling að hluta - Persónuútfærsla |

- Smelltu á Verkefni ➤ Endurskoðun. Endurskoðun svarglugginn birtist.

- Veldu blinking_led í Revision Name dálknum og smelltu á Stilla núverandi.

- Smelltu á Apply. Blinking_led endurskoðunin opnast.

- Til að stilla endurskoðunargerðina fyrir blinking_led, smelltu á Verkefni ➤ Stillingar ➤ Almennt.

- Veldu endurskoðunartegund sem endurstilling að hluta – grunnur.

- Á sama hátt skaltu stilla endurskoðunargerðirnar fyrir hinar tíu endurskoðunirnar, eins og skráð er í töflunni hér að ofan.

- Athugið: Þú verður að stilla hverja útgáfu sem núverandi útgáfu áður en þú úthlutar endurskoðunargerðinni. Staðfestu að hver .qsf file inniheldur eftirfarandi verkefni:

- Athugið: Bættu öllum Fitter-sértækum stillingum sem þú vilt nota í PR-útfærslusamsetningunni við persónuútfærsluútfærslurnar. Sértækar stillingar fyrir Fitter hafa áhrif á passa persónunnar, en hafa ekki áhrif á innflutt kyrrstæða svæðið. Þú getur líka bætt hvaða stillingum sem er sértækar fyrir myndun við einstakar endurskoðanir á persónumyndun.

Búðu til endurskoðun fyrir persónur

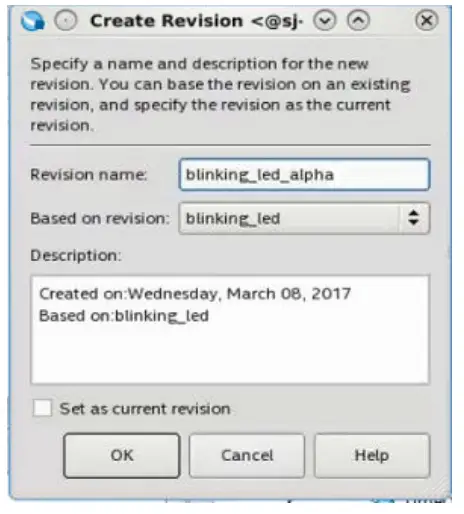

Skref 8: Búa til stigveldisforskrift um endurstillingarflæði að hluta

Til að búa til stigveldisforskrift fyrir endurstillingarflæði að hluta:

- Búðu til flæðisniðmát úr Intel Quartus Prime skipanaskelinni með því að keyra eftirfarandi skipun:

- Intel Quartus Prime býr til a10_hier_partial_reconfig/flow.tcl file.

- Endurnefna myndaða a10_hier_partial_reconfig/setup.tcl.example til a10_hier_partial_reconfig/setup.tcl, og breyttu handritinu til að tilgreina upplýsingar um hluta endurstillingarverkefnisins:

a. Til að skilgreina heiti verkefnisins skaltu uppfæra eftirfarandi línu: b. Til að skilgreina grunnútgáfuna skaltu uppfæra eftirfarandi línu:

b. Til að skilgreina grunnútgáfuna skaltu uppfæra eftirfarandi línu:

- Til að skilgreina hverja útfærsluútfærslu endurstillingar að hluta, ásamt nöfnum PR-sneiða og upprunaútgáfu sem útfærir breytingarnar, uppfærðu eftirfarandi línur:

Athugið: Öll endurskoðunarverkefnin verða að vera í sömu möppu og blinking_led.qpf. Annars skaltu uppfæra flæðishandritið í samræmi við það.

Skref 9: Að keyra stigveldisforskrift um endurstillingarflæði að hluta

Til að keyra stigveldisforskrift um endurstillingarflæði að hluta:

- Smelltu á Tools ➤ Tcl Scripts. Tcl Scripts svarglugginn birtist.

- Smelltu á Bæta við verkefni, flettu og veldu a10_hier_partial_reconfig/flow.tcl.

- Veldu a10_hier_partial_reconfig/flow.tcl í Libraries glugganum og smelltu á Run.

Þetta handrit keyrir samantektina fyrir persónurnar þrjár. Intel Quartus Prime býr til SRAM hlut File (.sof), SRAM hlutur með hluta grímu File (.pmsf), og óunnið tvíundir File (.rbf) fyrir hverja persónu.

Athugið: Til að keyra skriftuna frá Intel Quartus Prime skipanaskelinni skaltu slá inn eftirfarandi skipun:

- Settu saman hönnunina fyrir endurstillingu að hluta

- Notkun hluta endurstillingar flæðisskriftar

- Stilling á hluta endurstillingar flæðisskriftu

- Búðu til forritun Files

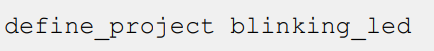

Skref 10: Forritun stjórnar

Áður en þú byrjar:

- Tengdu aflgjafann við Intel Arria 10 SoC þróunarspjaldið.

- Tengdu USB Blaster snúruna á milli USB USB tengis tölvunnar og USB Blaster tengisins á þróunarborðinu.

Til að keyra hönnunina á Intel Arria 10 SoC þróunarborðinu:

- Opnaðu Intel Quartus Prime hugbúnaðinn og smelltu á Verkfæri ➤ Forritari.

- Í forritaranum, smelltu á Hardware Setup og veldu USB-Blaster.

- Smelltu á Auto Detect og veldu tækið, 10AS066N3.

- Smelltu á OK. Intel Quartus Prime hugbúnaðurinn skynjar og uppfærir forritarann með þremur FPGA flögum á borðinu.

- Veldu 10AS066N3 tækið, smelltu á Breyta File og hlaðið blikkandi_led_pr_alpha.sof file.

- Virkja forrit/stillingu fyrir blinking_led_pr_alpha.sof file.

- Smelltu á Start og bíddu þar til framvindustikan nær 100%.

- Fylgstu með ljósdíóðunum á borðinu blikka á sömu tíðni og upprunalega flata hönnunin.

- Til að forrita aðeins barn PR svæði, hægrismelltu á blinking_led_pr_alpha.sof file í Forritaranum og smelltu á Bæta við PR-forritun File.

- Veldu blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file.

- Slökktu á forriti/stillingu fyrir blinking_led_pr_alpha.sof file.

- Virkja forrit/stillinga fyrir blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file og smelltu á Start. Á töflunni skaltu fylgjast með LED[0] og LED[1] halda áfram að blikka. Þegar framvindustikan nær 100% blikkar LED[2] á sama hraða og LED[3] blikkar hægar.

- Til að forrita bæði foreldra- og barn PR svæði, hægrismelltu á .rbf file í Forritaranum og smelltu á Breyta PR forritun File.

- Veldu blinking_led_pr_delta.pr_parent_partition.rbf file.

- Smelltu á Start. Á töflunni, athugaðu að LED[0] og LED[1] halda áfram að blikka. Þegar framvindustikan nær 100% blikka bæði LED[2] og LED[3] hægar.

- Endurtaktu skrefin hér að ofan til að endurforrita aðeins barn PR svæði, eða bæði foreldra og barn PR svæði samtímis.

Mynd 10. Forritun á Intel Arria 10 SoC Development Board

Breyting á núverandi persónu

- Þú getur breytt persónu sem fyrir er, jafnvel eftir að grunnúttektin hefur verið tekin að fullu saman.

- Til dæmisample, til að láta blinking_led_child_slow persónuna blikka enn hægar:

- Í blinking_led_child_slow.sv file, breyttu COUNTER_TAP færibreytunni úr 27 í 28.

- Til að endurgera og innleiða þessa persónu aftur, verður þú að setja saman allar endurskoðanir sem eingöngu eru til samansöfnunar og útfærslubreytingar sem breytingin hefur áhrif á. Breyttu setup.tcl forskriftinni til að innihalda eftirfarandi línur:

Athugið: Þegar þú skilgreinir pr_parent_parition fyrir blinking_led_pr_delta endurskoðun flytur þú inn lokamynd af þeirri persónu til innleiðingar. Afleiðingin er sú að útfærsla móðurskiptingsrökfræðinnar er óbreytt á meðan samsvarandi undirsneiðing er breytt og útfærð.

Athugið: Þegar þú skilgreinir pr_parent_parition fyrir blinking_led_pr_delta endurskoðun flytur þú inn lokamynd af þeirri persónu til innleiðingar. Afleiðingin er sú að útfærsla móðurskiptingsrökfræðinnar er óbreytt á meðan samsvarandi undirsneiðing er breytt og útfærð. Þessi skipun endurgerir endurskoðun blinking_led_child_slow nýmyndunar og keyrir síðan PR útfærslusamsetningu með því að nota blinking_led_pr_bravo.

Þessi skipun endurgerir endurskoðun blinking_led_child_slow nýmyndunar og keyrir síðan PR útfærslusamsetningu með því að nota blinking_led_pr_bravo. - Til að framkvæma samantekt á endurskoðunum sem eingöngu eru til samantektar, keyrðu eftirfarandi skipun: Þessi skipun setur ekki saman grunnútgáfuna aftur.

- Til að framkvæma samantekt á útfærslubreytingum skaltu keyra eftirfarandi skipun:

- Þessi skipun setur ekki saman grunnútgáfuna aftur.

- Fylgdu skrefunum í skrefi 10: Forritun borðsins á síðu 22 til að forrita RBF sem myndast file inn í FPGA.

Athugið: Til að forðast að keyra allt flæðið fyrir hverja endurskoðun, skilgreinið endurskoðanir og útfærsluendurskoðanir sem eingöngu eru notaðar til samsetningar í setup.tcl forskriftinni og keyrið handritið.

Bætir nýrri persónu við hönnunina

Eftir að þú hefur tekið saman grunnútgáfurnar þínar geturðu samt bætt við nýjum persónum og sett þessar persónur saman hver fyrir sig.

Til dæmisample, til að skilgreina nýja barnapersónu fyrir blinking_led_parent_slow, sem slekkur á led_three:

- Afritaðu blinking_led_child_empty.sv yfir á blinking_led_chdild_off.sv.

- Í blinking_led_child_off.sv file, breyta úthlutuninni, úthluta led_three_on = 1'b0; að úthluta led_three_on = 1'b1;. Gakktu úr skugga um að þú breytir heiti einingarinnar úr blinking_led_child_empty í blinking_led_child_off.

- Búðu til nýja myndun endurskoðunar, blinking_led_child_off, með því að fylgja skrefunum í Að búa til endurskoðun eingöngu á síðu 16.

Athugið: Blinking_led_child_off endurskoðunin verður að nota blinking_led_child_off.sv file. - Búðu til nýja útfærsluendurskoðun, blinking_led_pr_foxtrot, með því að fylgja skrefunum í Búa til útfærsluendurskoðun á síðu 15.

- Uppfærðu a10_hier_partial_reconfig/setup.tcl file til að skilgreina nýju PR útfærsluna:

- Safnaðu bara saman þessari nýju samsetningu og útfærslu endurskoðun með því að keyra eftirfarandi skipun:

Fyrir ítarlegar upplýsingar um stigveldislega endurstillingu að hluta fyrir Intel Arria 10 tæki, sjáðu að búa til hluta endurstillingarhönnun í bindi 1 í handbók Intel Quartus Prime Pro Edition.

Tengdar upplýsingar

- Að búa til endurstillingarhönnun að hluta

- Netþjálfun fyrir endurstillingu að hluta

Endurskoðunarsaga skjala

Tafla 5. Endurskoðunarferill skjala

| Skjalaútgáfa | Hugbúnaðarútgáfa | Breytingar |

| 2017.11.06 | 17.1.0 | • Uppfærði Tilvísunarkröfur um hönnun kafla með hugbúnaðarútgáfunni

• Uppfærði Flat tilvísunarhönnun án PR skiptingar mynd með breytingum á hönnunarblokk • Uppfærði Tilvísunarhönnun Files töflu með upplýsingum um Top_counter.sv eining • Uppfærði Endurstilling að hluta til IP Core Integration mynd með breytingum á hönnunarblokk • Uppfærði tölurnar – Hönnunar skiptingargluggi og Logic Lock Regions Gluggi til að endurspegla nýja GUI • File nafnbreytingar • Textabreytingar |

| 2017.05.08 | 17.0.0 | Upphafleg útgáfa skjalsins |

Skjöl / auðlindir

|

intel AN 805 stigskipt endurstilling að hluta til hönnunar á Arria 10 SoC þróunarborði [pdfNotendahandbók AN 805 Stigveldisbreyting að hluta til hönnunar á Arria 10 SoC þróunarborði, AN 805, stigveldisbreyting á hönnun á Arria 10 SoC þróunarráði, endurstilling hönnunar á Arria 10 SoC þróunarráði, Arria 10 SoC þróunarráði, 10 SoC Þróunarráð |