Arria 805 SoC ഡെവലപ്മെന്റ് ബോർഡിലെ ഒരു ഡിസൈനിന്റെ intel AN 10 ഹൈറാർക്കിക്കൽ ഭാഗിക പുനർക്രമീകരണം

Intel® Arria® 10 SoC ഡെവലപ്മെന്റ് ബോർഡിനായുള്ള ഹൈറാർക്കിക്കൽ ഭാഗിക പുനഃക്രമീകരണ ട്യൂട്ടോറിയൽ

ഈ ആപ്ലിക്കേഷൻ കുറിപ്പ് ഒരു ലളിതമായ രൂപകൽപ്പനയെ ശ്രേണിപരമായി ഭാഗികമായി പുനഃക്രമീകരിക്കാവുന്ന ഡിസൈനാക്കി മാറ്റുന്നതും Intel® Arria® 10 SoC ഡെവലപ്മെന്റ് ബോർഡിൽ ഡിസൈൻ നടപ്പിലാക്കുന്നതും പ്രകടമാക്കുന്നു. ഹൈറാർക്കിക്കൽ പാർഷ്യൽ റീകോൺഫിഗറേഷൻ (HPR) എന്നത് ഒരു പ്രത്യേക തരം ഭാഗിക റീകോൺഫിഗറേഷനാണ് (PR), അവിടെ നിങ്ങൾ മറ്റൊരു PR മേഖലയ്ക്കുള്ളിൽ ഒരു PR മേഖല ഉൾക്കൊള്ളുന്നു. കുട്ടിക്കും രക്ഷാകർതൃ പാർട്ടീഷനുകൾക്കുമായി നിങ്ങൾക്ക് ഒന്നിലധികം വ്യക്തിത്വങ്ങൾ സൃഷ്ടിക്കാൻ കഴിയും. ചൈൽഡ് പാർട്ടീഷനുകൾ അവരുടെ പാരന്റ് പാർട്ടീഷനുകളിൽ നിങ്ങൾ നെസ്റ്റ് ചെയ്യുക. ഒരു ചൈൽഡ് പാർട്ടീഷൻ പുനഃക്രമീകരിക്കുന്നത് പാരന്റ് അല്ലെങ്കിൽ സ്റ്റാറ്റിക് പ്രദേശങ്ങളിലെ പ്രവർത്തനത്തെ ബാധിക്കില്ല. ഒരു രക്ഷാകർതൃ പാർട്ടീഷൻ പുനഃക്രമീകരിക്കുന്നത് സ്റ്റാറ്റിക് റീജിയണിലെ പ്രവർത്തനത്തെ ബാധിക്കില്ല, പക്ഷേ മാതൃമേഖലയിലെ ചൈൽഡ് പാർട്ടീഷനുകളെ ഡിഫോൾട്ട് ചൈൽഡ് പാർട്ടീഷൻ പേഴ്സണുകൾ ഉപയോഗിച്ച് മാറ്റിസ്ഥാപിക്കുന്നു. ഒരേ എഫ്പിജിഎ ഉപകരണ ഉറവിടങ്ങൾ ഒന്നിലധികം ഫംഗ്ഷനുകൾ സമയം പങ്കിടുന്ന സിസ്റ്റങ്ങളിൽ ഈ രീതി ഫലപ്രദമാണ്.

ഭാഗികമായ പുനർക്രമീകരണം ഒരു ഫ്ലാറ്റ് ഡിസൈനിന് ഇനിപ്പറയുന്ന പുരോഗതി നൽകുന്നു:

- റൺ-ടൈം ഡിസൈൻ റീകോൺഫിഗറേഷൻ അനുവദിക്കുന്നു

- ഡിസൈനിന്റെ സ്കേലബിളിറ്റി വർദ്ധിപ്പിക്കുന്നു

- സിസ്റ്റം പ്രവർത്തനരഹിതമായ സമയം കുറയ്ക്കുന്നു

- ഡിസൈനിലെ ഡൈനാമിക് ടൈം-മൾട്ടിപ്ലക്സിംഗ് ഫംഗ്ഷനുകളെ പിന്തുണയ്ക്കുന്നു

- ബോർഡ് സ്ഥലത്തിന്റെ കാര്യക്ഷമമായ ഉപയോഗത്തിലൂടെ ചെലവും വൈദ്യുതി ഉപഭോഗവും കുറയ്ക്കുന്നു

- കുറിപ്പ്:

- ഈ റഫറൻസ് ഡിസൈൻ നടപ്പിലാക്കുന്നതിന് Intel Quartus® Prime FPGA ഇംപ്ലിമെന്റേഷൻ ഫ്ലോയുമായി അടിസ്ഥാന പരിചയവും പ്രാഥമിക ഇന്റൽ ക്വാർട്ടസ് പ്രൈം പ്രോജക്റ്റിനെക്കുറിച്ചുള്ള അറിവും ആവശ്യമാണ്. files.

ബന്ധപ്പെട്ട വിവരങ്ങൾ

- Intel Arria 10 SoC വികസന കിറ്റ് ഉപയോക്തൃ ഗൈഡ്

- ഭാഗിക പുനഃക്രമീകരണ ആശയങ്ങൾ

- ഭാഗിക പുനർക്രമീകരണ ഡിസൈൻ ഫ്ലോ

- ഭാഗിക പുനർക്രമീകരണ ഡിസൈൻ ശുപാർശകൾ

- ഭാഗിക പുനർക്രമീകരണ ഡിസൈൻ പരിഗണനകൾ

റഫറൻസ് ഡിസൈൻ ആവശ്യകതകൾ

ഈ റഫറൻസ് ഡിസൈനിന് ഇനിപ്പറയുന്നവ ആവശ്യമാണ്:

- ഡിസൈൻ നടപ്പാക്കലിനായി ഇന്റൽ ക്വാർട്ടസ് പ്രൈം പ്രോ എഡിഷൻ സോഫ്റ്റ്വെയർ പതിപ്പ് 17.1.

- FPGA നടപ്പിലാക്കുന്നതിനുള്ള Intel Arria 10 SoC വികസന കിറ്റ്.

ഇന്റൽ കോർപ്പറേഷൻ. എല്ലാ അവകാശങ്ങളും നിക്ഷിപ്തം. ഇന്റൽ, ഇന്റൽ ലോഗോ, മറ്റ് ഇന്റൽ മാർക്കുകൾ എന്നിവ ഇന്റൽ കോർപ്പറേഷന്റെയോ അതിന്റെ അനുബന്ധ സ്ഥാപനങ്ങളുടെയോ വ്യാപാരമുദ്രകളാണ്. ഇന്റലിന്റെ സ്റ്റാൻഡേർഡ് വാറന്റിക്ക് അനുസൃതമായി അതിന്റെ FPGA, അർദ്ധചാലക ഉൽപ്പന്നങ്ങളുടെ പ്രകടനം നിലവിലെ സ്പെസിഫിക്കേഷനുകളിലേക്ക് Intel വാറന്റ് ചെയ്യുന്നു, എന്നാൽ അറിയിപ്പ് കൂടാതെ ഏത് സമയത്തും ഏത് ഉൽപ്പന്നങ്ങളിലും സേവനങ്ങളിലും മാറ്റങ്ങൾ വരുത്താനുള്ള അവകാശം നിക്ഷിപ്തമാണ്. Intel രേഖാമൂലം രേഖാമൂലം സമ്മതിച്ചതല്ലാതെ ഇവിടെ വിവരിച്ചിരിക്കുന്ന ഏതെങ്കിലും വിവരങ്ങളുടെയോ ഉൽപ്പന്നത്തിന്റെയോ സേവനത്തിന്റെയോ ആപ്ലിക്കേഷനിൽ നിന്നോ ഉപയോഗത്തിൽ നിന്നോ ഉണ്ടാകുന്ന ഉത്തരവാദിത്തമോ ബാധ്യതയോ Intel ഏറ്റെടുക്കുന്നില്ല. ഏതെങ്കിലും പ്രസിദ്ധീകരിച്ച വിവരങ്ങളെ ആശ്രയിക്കുന്നതിന് മുമ്പും ഉൽപ്പന്നങ്ങൾക്കോ സേവനങ്ങൾക്കോ ഓർഡറുകൾ നൽകുന്നതിനുമുമ്പ് ഉപകരണ സവിശേഷതകളുടെ ഏറ്റവും പുതിയ പതിപ്പ് നേടുന്നതിന് ഇന്റൽ ഉപഭോക്താക്കളോട് നിർദ്ദേശിക്കുന്നു.

- മറ്റ് പേരുകളും ബ്രാൻഡുകളും മറ്റുള്ളവരുടെ സ്വത്തായി അവകാശപ്പെടാം.

റഫറൻസ് ഡിസൈൻ കഴിഞ്ഞുview

- ഈ റഫറൻസ് ഡിസൈനിൽ ഒരു 32-ബിറ്റ് കൗണ്ടർ അടങ്ങിയിരിക്കുന്നു. ബോർഡ് തലത്തിൽ, ഡിസൈൻ ക്ലോക്കിനെ 50MHz ഉറവിടത്തിലേക്ക് ബന്ധിപ്പിക്കുകയും ഔട്ട്പുട്ട് FPGA-യിലെ നാല് LED-കളുമായി ബന്ധിപ്പിക്കുകയും ചെയ്യുന്നു. കൌണ്ടർ ബിറ്റുകളിൽ നിന്നുള്ള ഔട്ട്പുട്ട് ഒരു പ്രത്യേക ശ്രേണിയിൽ തിരഞ്ഞെടുക്കുന്നത് LED- കൾ ഒരു പ്രത്യേക ആവൃത്തിയിൽ മിന്നിമറയുന്നതിന് കാരണമാകുന്നു.

ചിത്രം 1. പിആർ പാർട്ടീഷനിംഗ് ഇല്ലാതെ ഫ്ലാറ്റ് റഫറൻസ് ഡിസൈൻ

റഫറൻസ് ഡിസൈൻ Files

ഭാഗിക പുനഃക്രമീകരണ ട്യൂട്ടോറിയൽ ഇനിപ്പറയുന്ന സ്ഥലത്ത് ലഭ്യമാണ്: https://github.com/intel/fpga-partial-reconfig

ട്യൂട്ടോറിയൽ ഡൗൺലോഡ് ചെയ്യാൻ:

- ക്ലോൺ ക്ലിക്ക് ചെയ്യുക അല്ലെങ്കിൽ ഡൗൺലോഡ് ചെയ്യുക.

- ZIP ഡൗൺലോഡ് ക്ലിക്ക് ചെയ്യുക. FPGA-partial-config-master.zip അൺസിപ്പ് ചെയ്യുക file.

- റഫറൻസ് ഡിസൈൻ ആക്സസ് ചെയ്യാൻ ട്യൂട്ടോറിയലുകൾ/a10_soc_devkit_blinking_led_hpr സബ് ഫോൾഡറിലേക്ക് നാവിഗേറ്റ് ചെയ്യുക.

ഫ്ലാറ്റ് ഫോൾഡറിൽ ഇനിപ്പറയുന്നവ അടങ്ങിയിരിക്കുന്നു files:

പട്ടിക 1. റഫറൻസ് ഡിസൈൻ Files

| File പേര് | വിവരണം |

| മുകളിൽ. എസ്.വി | ഉയർന്ന തലം file ഡിസൈനിന്റെ ഫ്ലാറ്റ് നടപ്പിലാക്കൽ അടങ്ങിയിരിക്കുന്നു. ഈ മൊഡ്യൂൾ ബ്ലിങ്കിംഗ്_ലെഡ് സബ്-പാർട്ടീഷനെയും ടോപ്പ്_കൗണ്ടർ മൊഡ്യൂളിനെയും തൽക്ഷണം ചെയ്യുന്നു. |

| top_counter.sv | LED[32] നേരിട്ട് നിയന്ത്രിക്കുന്ന ടോപ്പ്-ലെവൽ 1-ബിറ്റ് കൗണ്ടർ. കൗണ്ടറിന്റെ രജിസ്റ്റർ ചെയ്ത ഔട്ട്പുട്ട് LED[0] നിയന്ത്രിക്കുന്നു, കൂടാതെ blinking_led മൊഡ്യൂൾ വഴി LED[2], LED[3] എന്നിവയ്ക്ക് ശക്തി നൽകുന്നു. |

| blinking_led.sdc | പ്രോജക്റ്റിനുള്ള സമയ നിയന്ത്രണങ്ങൾ നിർവചിക്കുന്നു. |

| തുടർന്നു… | |

| File പേര് | വിവരണം |

| ബ്ലിങ്കിംഗ്_ലെഡ്.എസ്.വി | ഈ ട്യൂട്ടോറിയലിൽ, നിങ്ങൾ ഈ മൊഡ്യൂളിനെ ഒരു പാരന്റ് പിആർ പാർട്ടീഷനാക്കി മാറ്റുന്നു. LED[2], LED[3] എന്നിവ നിയന്ത്രിക്കുന്ന top_counter മൊഡ്യൂളിന്റെ രജിസ്റ്റർ ചെയ്ത ഔട്ട്പുട്ട് മൊഡ്യൂളിന് ലഭിക്കുന്നു. |

| blinking_led.qpf | ഇന്റൽ ക്വാർട്ടസ് പ്രൈം പ്രോജക്റ്റ് file പ്രോജക്റ്റിലെ എല്ലാ പുനരവലോകനങ്ങളുടെയും ലിസ്റ്റ് അടങ്ങിയിരിക്കുന്നു. |

| blinking_led.qsf | ഇന്റൽ ക്വാർട്ടസ് പ്രൈം ക്രമീകരണങ്ങൾ file പ്രോജക്റ്റിനായുള്ള അസൈൻമെന്റുകളും ക്രമീകരണങ്ങളും അടങ്ങിയിരിക്കുന്നു. |

കുറിപ്പ്: hpr ഫോൾഡറിൽ പൂർണ്ണമായ സെറ്റ് അടങ്ങിയിരിക്കുന്നു fileഈ ആപ്ലിക്കേഷൻ കുറിപ്പ് ഉപയോഗിച്ചാണ് നിങ്ങൾ സൃഷ്ടിക്കുന്നത്. ഇവ പരാമർശിക്കുക fileനടപ്പാതയിൽ ഏത് സമയത്തും എസ്.

ചിത്രം 2. റഫറൻസ് ഡിസൈൻ Files

റഫറൻസ് ഡിസൈൻ വാക്ക്ത്രൂ

ഇനിപ്പറയുന്ന ഘട്ടങ്ങൾ ഒരു ഫ്ലാറ്റ് ഡിസൈനിലേക്ക് ഭാഗിക പുനർക്രമീകരണത്തിന്റെ പ്രയോഗത്തെ വിവരിക്കുന്നു. ട്യൂട്ടോറിയൽ Intel Arria 10 SoC ഡെവലപ്മെന്റ് ബോർഡിനായി ഇന്റൽ ക്വാർട്ടസ് പ്രൈം പ്രോ എഡിഷൻ സോഫ്റ്റ്വെയർ ഉപയോഗിക്കുന്നു:

- ഘട്ടം 1: പേജ് 6-ൽ ആരംഭിക്കുന്നു

- ഘട്ടം 2: പേജ് 6-ൽ ഒരു ചൈൽഡ് ലെവൽ സബ്-മൊഡ്യൂൾ സൃഷ്ടിക്കുക

- ഘട്ടം 3: പേജ് 7-ൽ ഡിസൈൻ പാർട്ടീഷനുകൾ സൃഷ്ടിക്കുന്നു

- ഘട്ടം 4: പേജ് 9-ൽ PR പാർട്ടീഷനുകൾക്കായി പ്ലേസ്മെന്റും റൂട്ടിംഗ് മേഖലയും അനുവദിക്കുന്നു

- ഘട്ടം 5: പേജ് 10-ൽ Intel Arria 10 ഭാഗിക റീകോൺഫിഗറേഷൻ കൺട്രോളർ IP കോർ ചേർക്കുന്നു

- ഘട്ടം 6: പേജ് 13-ൽ വ്യക്തികളെ നിർവചിക്കുന്നു

- ഘട്ടം 7: പേജ് 15-ൽ പുനരവലോകനങ്ങൾ സൃഷ്ടിക്കുന്നു

- ഘട്ടം 8: പേജ് 20-ൽ ഹൈറാർക്കിക്കൽ ഭാഗിക റീകോൺഫിഗറേഷൻ ഫ്ലോ സ്ക്രിപ്റ്റ് സൃഷ്ടിക്കുന്നു

- ഘട്ടം 9: പേജ് 21-ൽ ഹൈറാർക്കിക്കൽ ഭാഗിക റീകോൺഫിഗറേഷൻ ഫ്ലോ സ്ക്രിപ്റ്റ് പ്രവർത്തിപ്പിക്കുന്നു

- ഘട്ടം 10: പേജ് 22-ൽ ബോർഡ് പ്രോഗ്രാമിംഗ്

ഘട്ടം 1: ആരംഭിക്കുന്നു

റഫറൻസ് ഡിസൈൻ പകർത്താൻ fileനിങ്ങളുടെ പ്രവർത്തന പരിതസ്ഥിതിയിലേക്ക് പോയി ബ്ലിങ്കിംഗ്_ലെഡ് ഫ്ലാറ്റ് ഡിസൈൻ കംപൈൽ ചെയ്യുക:

- നിങ്ങളുടെ പ്രവർത്തന പരിതസ്ഥിതിയിൽ ഒരു ഡയറക്ടറി സൃഷ്ടിക്കുക, a10_soc_devkit_blinking_led_hpr.

- ഡൗൺലോഡ് ചെയ്ത ട്യൂട്ടോറിയലുകൾ/a10_soc_devkit_blinking_led_hpr/flat സബ് ഫോൾഡർ, a10_soc_devkit_blinking_led_hpr എന്ന ഡയറക്ടറിയിലേക്ക് പകർത്തുക.

- Intel Quartus Prime Pro Edition സോഫ്റ്റ്വെയറിൽ ക്ലിക്ക് ചെയ്യുക File ➤ Project തുറന്ന് blinking_led.qpf തിരഞ്ഞെടുക്കുക.

- ഫ്ലാറ്റ് ഡിസൈൻ കംപൈൽ ചെയ്യാൻ, പ്രോസസ്സിംഗ് ➤ കംപൈലേഷൻ ആരംഭിക്കുക ക്ലിക്കുചെയ്യുക.

ഘട്ടം 2: ഒരു ചൈൽഡ് ലെവൽ സബ്-മൊഡ്യൂൾ സൃഷ്ടിക്കുന്നു

ഈ ഫ്ലാറ്റ് ഡിസൈനിനെ ഒരു ശ്രേണിപരമായ PR ഡിസൈനാക്കി മാറ്റാൻ, നിങ്ങൾ ഒരു ചൈൽഡ് സബ്-മൊഡ്യൂൾ (blinking_led_child. SV) സൃഷ്ടിക്കണം, അത് പാരന്റ് സബ്-മൊഡ്യൂളിനുള്ളിൽ (blinking_led.sv) നെസ്റ്റഡ് ചെയ്തിരിക്കുന്നു.

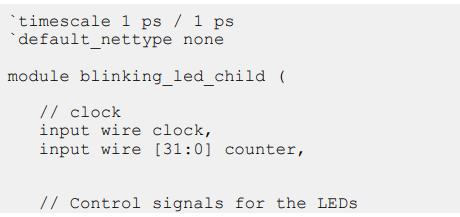

- ഒരു പുതിയ ഡിസൈൻ സൃഷ്ടിക്കുക file, blinking_led_child.sv, ഇതിലേക്ക് കോഡിന്റെ ഇനിപ്പറയുന്ന വരികൾ ചേർക്കുക file: ടൈംസ്കെയിൽ 1 ps / 1 ps `default_nettype none module blinking_led_child ( // ക്ലോക്ക് ഇൻപുട്ട് വയർ ക്ലോക്ക്, ഇൻപുട്ട് വയർ [31:0] കൗണ്ടർ, // LED-കൾക്കുള്ള നിയന്ത്രണ സിഗ്നലുകൾ

- blinking_led.sv പരിഷ്ക്കരിക്കുക file സ്റ്റാറ്റിക് റീജിയനിൽ നിന്ന് കൗണ്ടറിന്റെ ബിറ്റ് 23-ലേക്ക് led_two_on കണക്റ്റുചെയ്യാനും ബ്ലിങ്കിംഗ്_ലെഡ്_ചൈൽഡ് മൊഡ്യൂൾ തൽക്ഷണം ചെയ്യാനും. പരിഷ്ക്കരണങ്ങൾക്ക് ശേഷം, നിങ്ങളുടെ blinking_led.sv file ഇനിപ്പറയുന്ന രീതിയിൽ ദൃശ്യമാകണം:

- എല്ലാ ഡിസൈനും പരിഷ്കരിക്കുമ്പോൾ files, പ്രോസസ്സിംഗ് ➤ കംപൈലേഷൻ ആരംഭിക്കുക ക്ലിക്ക് ചെയ്ത് പ്രോജക്റ്റ് വീണ്ടും കംപൈൽ ചെയ്യുക

ഘട്ടം 3: ഡിസൈൻ പാർട്ടീഷനുകൾ സൃഷ്ടിക്കുന്നു

നിങ്ങൾ ഭാഗികമായി പുനഃക്രമീകരിക്കാൻ ആഗ്രഹിക്കുന്ന ഓരോ PR മേഖലയ്ക്കും നിങ്ങൾ ഡിസൈൻ പാർട്ടീഷനുകൾ ഉണ്ടാക്കണം. നിങ്ങളുടെ ഡിസൈനിൽ നിങ്ങൾക്ക് സ്വതന്ത്ര പാർട്ടീഷനുകളോ പിആർ മേഖലകളോ സൃഷ്ടിക്കാൻ കഴിയും. ഈ ട്യൂട്ടോറിയൽ u_blinking_led_child, u_blinking_led ഇൻസ്റ്റൻസുകൾക്കായി രണ്ട് ഡിസൈൻ പാർട്ടീഷനുകൾ സൃഷ്ടിക്കുന്നു.

ഹൈരാർക്കിക്കൽ ഭാഗിക പുനർക്രമീകരണത്തിനായി ഡിസൈൻ പാർട്ടീഷനുകൾ സൃഷ്ടിക്കുന്നതിന്:

- പ്രോജക്റ്റ് നാവിഗേറ്ററിലെ u_blinking_led_child സംഭവത്തിൽ വലത്-ക്ലിക്കുചെയ്ത് ഡിസൈൻ പാർട്ടീഷൻ ➤ ഡിസൈൻ പാർട്ടീഷനായി സജ്ജമാക്കുക ക്ലിക്കുചെയ്യുക. ഒരു പാർട്ടീഷനായി സജ്ജീകരിച്ചിരിക്കുന്ന ഓരോ സന്ദർഭത്തിനും അടുത്തായി ഒരു ഡിസൈൻ പാർട്ടീഷൻ ഐക്കൺ ദൃശ്യമാകുന്നു.

ചിത്രം 3. പ്രോജക്റ്റ് നാവിഗേറ്ററിൽ നിന്ന് ഡിസൈൻ പാർട്ടീഷനുകൾ സൃഷ്ടിക്കുന്നു

- പാർട്ടീഷൻ തരം നിർവചിക്കുന്നതിന്, ശ്രേണി ടാബിലെ u_blinking_led_child സന്ദർഭത്തിൽ വലത്-ക്ലിക്കുചെയ്യുക, ഡിസൈൻ പാർട്ടീഷൻ ➤ റീകോൺഫിഗർ ചെയ്യാവുന്നത് ക്ലിക്കുചെയ്യുക. ഇൻസ്റ്റൻസ് ഒരു പാർട്ടീഷനായി സജ്ജീകരിച്ചതിനുശേഷം മാത്രമേ നിങ്ങൾക്ക് പാർട്ടീഷൻ തരം നിർവചിക്കാൻ കഴിയൂ. അസൈൻമെന്റുകളിൽ ഡിസൈൻ പാർട്ടീഷൻ ദൃശ്യമാകുന്നു View ഡിസൈൻ പാർട്ടീഷനുകളുടെ ജാലകത്തിന്റെ ടാബ്.

ചിത്രം 4. ഡിസൈൻ പാർട്ടീഷനുകളുടെ വിൻഡോ

- പേര് ഡബിൾ ക്ലിക്ക് ചെയ്ത് ഡിസൈൻ പാർട്ടീഷനുകൾ വിൻഡോയിൽ പാർട്ടീഷൻ പേര് എഡിറ്റ് ചെയ്യുക. ഈ റഫറൻസ് ഡിസൈനിനായി, പാർട്ടീഷന്റെ പേര് pr_partition എന്ന് പുനർനാമകരണം ചെയ്യുക.

കുറിപ്പ്: നിങ്ങൾ ഒരു പാർട്ടീഷൻ സൃഷ്ടിക്കുമ്പോൾ, ഇന്റൽ ക്വാർട്ടസ് പ്രൈം സോഫ്റ്റ്വെയർ സ്വയമേവ ഒരു പാർട്ടീഷൻ നാമം സൃഷ്ടിക്കുന്നു, ഉദാഹരണ നാമവും ശ്രേണി പാതയും അടിസ്ഥാനമാക്കി. ഈ ഡിഫോൾട്ട് പാർട്ടീഷൻ നാമം ഓരോ സന്ദർഭത്തിലും വ്യത്യാസപ്പെടാം. - u_blinking_led ഇൻസ്റ്റൻസിലേക്ക് വീണ്ടും ക്രമീകരിക്കാവുന്ന ഡിസൈൻ പാർട്ടീഷനുകൾ നൽകുന്നതിന് 1, 2 ഘട്ടങ്ങൾ ആവർത്തിക്കുക. ഈ പാർട്ടീഷൻ pr_parent_partition എന്ന് പുനർനാമകരണം ചെയ്യുക.

നിങ്ങളുടെ പുനഃക്രമീകരിക്കാവുന്ന ഡിസൈൻ പാർട്ടീഷനുകൾക്ക് അനുയോജ്യമായ, blinking_led.qsf-ൽ ഇനിപ്പറയുന്ന അസൈൻമെന്റുകൾ അടങ്ങിയിട്ടുണ്ടെന്ന് പരിശോധിക്കുക:

ഭാഗിക പുനർക്രമീകരണത്തിനായി ഡിസൈൻ പാർട്ടീഷനുകൾ സൃഷ്ടിക്കുക

ഘട്ടം 4: പിആർ പാർട്ടീഷനുകൾക്കായി പ്ലെയ്സ്മെന്റും റൂട്ടിംഗ് മേഖലയും അനുവദിക്കുന്നു

നിങ്ങൾ അടിസ്ഥാന പുനരവലോകനം സൃഷ്ടിക്കുമ്പോൾ, പിആർ ഡിസൈൻ ഫ്ലോ നിങ്ങളുടെ പിആർ പാർട്ടീഷൻ റീജിയൻ അലോക്കേഷൻ ഉപയോഗിച്ച് റിസർവ് ചെയ്ത പ്രദേശത്ത് അനുബന്ധ പേഴ്സണ കോർ സ്ഥാപിക്കുന്നു. നിങ്ങളുടെ അടിസ്ഥാന പുനരവലോകനത്തിനായി ഉപകരണ ഫ്ലോർപ്ലാനിലെ PR മേഖല കണ്ടെത്തുന്നതിനും അസൈൻ ചെയ്യുന്നതിനും:

- പ്രോജക്റ്റ് നാവിഗേറ്ററിലെ u_blinking_led_child സംഭവത്തിൽ വലത്-ക്ലിക്കുചെയ്ത് ലോജിക് ലോക്ക് റീജിയൻ ക്ലിക്ക് ചെയ്യുക ➤ പുതിയ ലോജിക് ലോക്ക് റീജിയൺ സൃഷ്ടിക്കുക. പ്രദേശം ലോജിക് ലോക്ക് റീജിയൻസ് വിൻഡോയിൽ ദൃശ്യമാകുന്നു.

- നിങ്ങളുടെ പ്ലെയ്സ്മെന്റ് മേഖല ബ്ലിങ്കിംഗ്_ലെഡ്_ചൈൽഡ് ലോജിക് ഉൾപ്പെടുത്തണം. ചിപ്പ് പ്ലാനറിൽ നോഡ് കണ്ടെത്തി പ്ലെയ്സ്മെന്റ് മേഖല തിരഞ്ഞെടുക്കുക. പ്രോജക്റ്റ് നാവിഗേറ്ററിലെ u_blinking_led_child പ്രദേശത്തിന്റെ പേരിൽ വലത്-ക്ലിക്കുചെയ്ത് നോഡ് കണ്ടെത്തുക ➤ ചിപ്പ് പ്ലാനറിൽ കണ്ടെത്തുക ക്ലിക്കുചെയ്യുക.

ചിത്രം 5. blinking_led-നുള്ള ചിപ്പ് പ്ലാനർ നോഡ് ലൊക്കേഷൻ

- ലോജിക് ലോക്ക് റീജിയൻസ് വിൻഡോയിൽ, ഒറിജിൻ കോളത്തിൽ പ്ലേസ്മെന്റ് റീജിയൻ കോർഡിനേറ്റുകൾ വ്യക്തമാക്കുക. ഉത്ഭവം പ്രദേശത്തിന്റെ താഴെ ഇടത് കോണുമായി യോജിക്കുന്നു. ഉദാample, (X1 Y1) കോർഡിനേറ്റുകളുള്ള ഒരു പ്ലെയ്സ്മെന്റ് മേഖല (69 10) ആയി സജ്ജീകരിക്കാൻ, ഉത്ഭവം X69_Y10 ആയി വ്യക്തമാക്കുക. നിങ്ങൾ വ്യക്തമാക്കുന്ന ഉയരവും വീതിയും അടിസ്ഥാനമാക്കി, പ്ലെയ്സ്മെന്റ് മേഖലയ്ക്കായുള്ള (X2 Y2) കോർഡിനേറ്റുകൾ (മുകളിൽ-വലത്) Intel Quartus Prime സോഫ്റ്റ്വെയർ സ്വയമേവ കണക്കാക്കുന്നു.

കുറിപ്പ്: ഈ ട്യൂട്ടോറിയൽ (X1 Y1) കോർഡിനേറ്റുകൾ ഉപയോഗിക്കുന്നു - (69 10), കൂടാതെ പ്ലെയ്സ്മെന്റ് മേഖലയ്ക്ക് 20 ഉയരവും വീതിയും. പ്ലെയ്സ്മെന്റ് മേഖലയ്ക്കായി ഏത് മൂല്യവും നിർവചിക്കുക, മേഖല ബ്ലിങ്കിംഗ്_ലെഡ്_ചൈൽഡ് ലോജിക്ക് ഉൾക്കൊള്ളുന്നു. - റിസർവ് ചെയ്തതും കോർ-ഒൺലി ഓപ്ഷനുകളും പ്രവർത്തനക്ഷമമാക്കുക.

- റൂട്ടിംഗ് റീജിയൻ ഓപ്ഷനിൽ ഡബിൾ ക്ലിക്ക് ചെയ്യുക. Logic Lock Routing Region Settings ഡയലോഗ് ബോക്സ് ദൃശ്യമാകുന്നു.

- റൂട്ടിംഗ് തരത്തിനായുള്ള വിപുലീകരണത്തോടുകൂടിയ ഫിക്സ്ഡ് തിരഞ്ഞെടുക്കുക. ഈ ഓപ്ഷൻ തിരഞ്ഞെടുക്കുന്നത് സ്വയമേവ 1 ന്റെ വിപുലീകരണ ദൈർഘ്യം നൽകുന്നു.

കുറിപ്പ്: വ്യത്യസ്ത വ്യക്തികളെ എഞ്ചിൻ റൂട്ട് ചെയ്യുമ്പോൾ ഫിറ്ററിന് അധിക ഫ്ലെക്സിബിലിറ്റി നൽകുന്നതിന് റൂട്ടിംഗ് മേഖല പ്ലേസ്മെന്റ് മേഖലയേക്കാൾ വലുതായിരിക്കണം. - u_blinking_led ഉദാഹരണത്തിനായി 1 -6 ഘട്ടങ്ങൾ ആവർത്തിക്കുക. u_blinking_led ഉദാഹരണത്തിനായി പാരന്റ് ലെവൽ പ്ലേസ്മെന്റ് 1 -6 ഘട്ടങ്ങൾ ആവർത്തിക്കുക. പാരന്റ്-ലെവൽ പ്ലെയ്സ്മെന്റ് മേഖല, പാരന്റ് ലെവൽ ലോജിക് പ്ലെയ്സ്മെന്റിന് മതിയായ ഇടം അനുവദിക്കുമ്പോൾ, അനുബന്ധ ചൈൽഡ്-ലെവൽ പ്ലേസ്മെന്റും റൂട്ടിംഗ് മേഖലകളും പൂർണ്ണമായും ഉൾപ്പെടുത്തണം. ഈ ട്യൂട്ടോറിയൽ (X1 Y1) കോർഡിനേറ്റുകൾ ഉപയോഗിക്കുന്നു - (66 7), 47 ഉയരവും 26 വീതിയും u_blinking_led ഇൻസ്റ്റൻസിന്റെ പ്ലേസ്മെന്റ് മേഖലയ്ക്കായി.

ചിത്രം 6.ലോജിക് ലോക്ക് റീജിയൻസ് വിൻഡോ

blinking_led.qsf-ൽ നിങ്ങളുടെ ഫ്ലോർ പ്ലാനിംഗുമായി ബന്ധപ്പെട്ട ഇനിപ്പറയുന്ന അസൈൻമെന്റുകൾ അടങ്ങിയിട്ടുണ്ടെന്ന് പരിശോധിക്കുക:

- ഭാഗിക പുനർക്രമീകരണ ഡിസൈൻ ഫ്ലോർപ്ലാൻ ചെയ്യുക

- ഭാഗികമായ പുനർക്രമീകരണം വർദ്ധിപ്പിച്ച് നടപ്പിലാക്കുന്നു

ഘട്ടം 5: Intel Arria 10 ഭാഗിക റീകോൺഫിഗറേഷൻ കൺട്രോളർ IP കോർ ചേർക്കുന്നു

- PR പാർട്ടീഷൻ പുനഃക്രമീകരിക്കാൻ Intel Arria 10 Partial Reconfiguration Controller IP കോർ ഉപയോഗിക്കുക. ഈ ഐപി കോർ ജെ ഉപയോഗിക്കുന്നുTAG പിആർ പാർട്ടീഷൻ പുനഃക്രമീകരിക്കാൻ. നിങ്ങളുടെ ഇന്റൽ ക്വാർട്ടസ് പ്രൈം പ്രോജക്റ്റിലേക്ക് Intel Arria 10 ഭാഗിക റീകോൺഫിഗറേഷൻ കൺട്രോളർ IP കോർ ചേർക്കുന്നതിന്:

- ഐപി കാറ്റലോഗിൽ ഭാഗിക പുനർക്രമീകരണം എന്ന് ടൈപ്പ് ചെയ്യുക.

- IP പാരാമീറ്റർ എഡിറ്റർ പ്രോ വിൻഡോ സമാരംഭിക്കുന്നതിന്, IP ലൈബ്രറിയിൽ നിന്ന് Intel Arria 10 Partial Reconfiguration Controller IP കോർ തിരഞ്ഞെടുത്ത് ചേർക്കുക ക്ലിക്ക് ചെയ്യുക.

- പുതിയ IP വേരിയന്റ് ഡയലോഗ് ബോക്സിൽ pr_ip എന്ന് ടൈപ്പ് ചെയ്യുക file പേര് നൽകി സൃഷ്ടിക്കുക ക്ലിക്കുചെയ്യുക. pr_ip-ന് ഡിഫോൾട്ട് പാരാമീറ്ററൈസേഷൻ ഉപയോഗിക്കുക. ജെ പ്രവർത്തനക്ഷമമാക്കുന്നുവെന്ന് ഉറപ്പാക്കുകTAG ഡീബഗ് മോഡ്, ഫ്രീസ് ഇന്റർഫേസ് ഓപ്ഷനുകൾ പ്രവർത്തനക്ഷമമാക്കുക എന്നിവ ഓണാക്കി, Avalon-MM സ്ലേവ് ഇന്റർഫേസ് ഓപ്ഷൻ പ്രവർത്തനക്ഷമമാക്കുക ഓഫാക്കി.

ചിത്രം 7. Intel Arria 10 ഭാഗിക പുനഃക്രമീകരണ കൺട്രോളർ IP കോർ പാരാമീറ്ററുകൾ

- പൂർത്തിയാക്കുക ക്ലിക്ക് ചെയ്യുക, സിസ്റ്റം ജനറേറ്റ് ചെയ്യാതെ പാരാമീറ്റർ എഡിറ്ററിൽ നിന്ന് പുറത്തുകടക്കുക. ഇന്റൽ ക്വാർട്ടസ് പ്രൈം സോഫ്റ്റ്വെയർ pr_ip.ip IP വ്യതിയാനം സൃഷ്ടിക്കുന്നു file, ഒപ്പം ചേർക്കുന്നു file blinking_led പ്രോജക്റ്റിലേക്ക്.

കുറിപ്പ്:

- നിങ്ങൾ pr_ip.ip പകർത്തുകയാണെങ്കിൽ file hpr ഫോൾഡറിൽ നിന്ന്, blinking_led.qsf സ്വമേധയാ എഡിറ്റ് ചെയ്യുക file ഇനിപ്പറയുന്ന വരി ഉൾപ്പെടുത്താൻ: set_global_assignment -name IP_FILE pr_ip.ip (പ്രിന്റ്_ഐപി)

- IP_ സ്ഥാപിക്കുകFILE SDC_ ന് ശേഷമുള്ള അസൈൻമെന്റ്FILE നിയമനങ്ങൾ (ജെtag.sdc, blinking_led.sdc) നിങ്ങളുടെ blinking_led.qsf-ൽ file. ഈ ഓർഡറിംഗ് ഭാഗിക റീകോൺഫിഗറേഷൻ ഐപി കോറിന്റെ ഉചിതമായ നിയന്ത്രണം ഉറപ്പാക്കുന്നു.

കുറിപ്പ്: ക്ലോക്കുകൾ കണ്ടെത്തുന്നതിന്, എസ്.ഡി.സി file PR IP, IP കോർ ഉപയോഗിക്കുന്ന ക്ലോക്കുകൾ സൃഷ്ടിക്കുന്ന ഏതെങ്കിലും SDC പിന്തുടരേണ്ടതാണ്. .ip ഉറപ്പാക്കിക്കൊണ്ട് നിങ്ങൾ ഈ ഓർഡർ സുഗമമാക്കുന്നു file PR IP കോർ ഏതെങ്കിലും .ip-ന് ശേഷം വരുന്നു files അല്ലെങ്കിൽ SDC fileQSF-ൽ ഈ ക്ലോക്കുകൾ സൃഷ്ടിക്കാൻ s ഉപയോഗിക്കുന്നു file നിങ്ങളുടെ ഇന്റൽ ക്വാർട്ടസ് പ്രൈം പ്രോജക്റ്റ് പുനരവലോകനത്തിനായി. കൂടുതൽ വിവരങ്ങൾക്ക്, ഭാഗിക റീകോൺഫിഗറേഷൻ ഐപി കോർ ഉപയോക്തൃ ഗൈഡിലെ സമയ നിയന്ത്രണ വിഭാഗം കാണുക.

ബന്ധപ്പെട്ട വിവരങ്ങൾ

- ഭാഗിക പുനർക്രമീകരണം IP സൊല്യൂഷൻസ് ഉപയോക്തൃ ഗൈഡ്

- ഭാഗിക റീകോൺഫിഗറേഷൻ റീജിയൻ കൺട്രോളർ ഐപി കോർ സംബന്ധിച്ച വിവരങ്ങൾക്ക്.

- ഭാഗിക പുനർക്രമീകരണം IP കോർ ഉപയോക്തൃ ഗൈഡ്

- സമയ നിയന്ത്രണങ്ങളെക്കുറിച്ചുള്ള വിവരങ്ങൾക്ക്.

ഉയർന്ന തലത്തിലുള്ള ഡിസൈൻ അപ്ഡേറ്റ് ചെയ്യുന്നു

മുകളിൽ അപ്ഡേറ്റ് ചെയ്യാൻ.എസ്.വി file PR_IP ഉദാഹരണം ഉപയോഗിച്ച്:

- ഉയർന്ന തലത്തിലുള്ള ഡിസൈനിലേക്ക് PR_IP ഇൻസ്റ്റൻസ് ചേർക്കുന്നതിന്, മുകളിൽ താഴെ പറയുന്ന കോഡ് ബ്ലോക്ക് അൺകമന്റ് ചെയ്യുക.SV file:

- റീകോൺഫിഗറേഷൻ സമയത്ത് ഔട്ട്പുട്ട് പോർട്ടുകളെ ലോജിക് 1-ലേക്ക് നിർബന്ധിക്കാൻ, PR_IP-ൽ നിന്നുള്ള ഫ്രീസ് കൺട്രോൾ സിഗ്നൽ ഔട്ട്പുട്ട് ഉപയോഗിക്കുക. എന്നിരുന്നാലും, ചൈൽഡ് പാർട്ടീഷൻ പിആർ പ്രോഗ്രാം ചെയ്യുമ്പോൾ പാരന്റ് പിആർ പാർട്ടീഷനിൽ നിന്ന് എൽഇഡി മിന്നുന്നത് തുടരുന്നത് നിരീക്ഷിക്കാൻ, ഫ്രീസ് കൺട്രോൾ സിഗ്നൽ led_two_on ഓഫ് ചെയ്യുന്നില്ല. pr_led_two_on നേരിട്ട് ആണെന്ന് ഉറപ്പാക്കുക

- സ്ഥിരസ്ഥിതി രക്ഷാകർതൃ വ്യക്തിത്വത്തിന്റെ (blinking_led) ഒരു ഉദാഹരണം നൽകുന്നതിന്, മുകളിൽ.SV അപ്ഡേറ്റ് ചെയ്യുക file ഇനിപ്പറയുന്ന കോഡ് ബ്ലോക്ക് ഉപയോഗിച്ച്:

ചിത്രം 8. ഭാഗിക പുനർക്രമീകരണം IP കോർ ഇന്റഗ്രേഷൻ

ഘട്ടം 6: വ്യക്തികളെ നിർവചിക്കുന്നു

ഈ റഫറൻസ് ഡിസൈൻ പാരന്റ് ആൻഡ് ചൈൽഡ് പിആർ പാർട്ടീഷനുകൾക്കായി അഞ്ച് വ്യത്യസ്ത വ്യക്തികളെ നിർവചിക്കുന്നു. നിങ്ങളുടെ പ്രോജക്റ്റിലെ വ്യക്തികളെ നിർവചിക്കാനും ഉൾപ്പെടുത്താനും:

- നാല് SystemVerilog സൃഷ്ടിക്കുക files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv, blinking_led_slow.sv എന്നീ അഞ്ച് വ്യക്തികൾക്കായി നിങ്ങളുടെ വർക്കിംഗ് ഡയറക്ടറിയിൽ.

കുറിപ്പ്: നിങ്ങൾ SystemVerilog സൃഷ്ടിക്കുകയാണെങ്കിൽ fileഇന്റൽ ക്വാർട്ടസ് പ്രൈം ടെക്സ്റ്റ് എഡിറ്ററിൽ നിന്ന്, ആഡ് പ്രവർത്തനരഹിതമാക്കുക file സംരക്ഷിക്കുമ്പോൾ നിലവിലെ പ്രോജക്റ്റ് ഓപ്ഷനിലേക്ക് files.

പട്ടിക 2. റഫറൻസ് ഡിസൈൻ വ്യക്തികൾ

| File പേര് | വിവരണം | കോഡ് |

| blinking_led_child.sv | ചൈൽഡ് ലെവൽ ഡിസൈനിനുള്ള ഡിഫോൾട്ട് വ്യക്തിത്വം |

`ടൈംസ്കെയിൽ 1 ps / 1 ps `default_nettype none module blinking_led_child ( // ക്ലോക്ക് ഇൻപുട്ട് വയർ ക്ലോക്ക്, ഇൻപുട്ട് വയർ [31:0] കൌണ്ടർ,

// LED-കളുടെ ഔട്ട്പുട്ട് വയർ led_three_on-നുള്ള നിയന്ത്രണ സിഗ്നലുകൾ

); ലോക്കൽപരം COUNTER_TAP = 23; reg led_three_on_r;

അസൈൻ led_three_on = led_three_on_r; എപ്പോഴും_ff @(പോസ്ഡ്ജ് ക്ലോക്ക്) ആരംഭിക്കുക led_three_on_r <= കൗണ്ടർ[COUNTER_TAP]; അവസാനിക്കുന്നു

എൻഡ്മൊഡ്യൂൾ |

| തുടർന്നു… | ||

| File പേര് | വിവരണം | കോഡ് |

| blinking_led_child_slow.sv | ദി

LED_THREE പതുക്കെ മിന്നിമറയുന്നു |

`ടൈംസ്കെയിൽ 1 ps / 1 ps `default_nettype none' എന്ന് ടൈപ്പ് ചെയ്യുക

മൊഡ്യൂൾ blinking_led_child_slow (

// ക്ലോക്ക് ഇൻപുട്ട് വയർ ക്ലോക്ക്, ഇൻപുട്ട് വയർ [31:0] കൌണ്ടർ,

// LED-കളുടെ ഔട്ട്പുട്ട് വയർ led_three_on-നുള്ള നിയന്ത്രണ സിഗ്നലുകൾ );

ലോക്കൽപരം COUNTER_TAP = 27; reg led_three_on_r;

അസൈൻ led_three_on = led_three_on_r; എപ്പോഴും_ff @(പോസ്ഡ്ജ് ക്ലോക്ക്) ആരംഭിക്കുക led_three_on_r <= കൗണ്ടർ[COUNTER_TAP]; അവസാനിക്കുന്നു

എൻഡ്മൊഡ്യൂൾ |

| blinking_led_child_empty.sv | ദി

LED_THREE തുടരുന്നു |

`ടൈംസ്കെയിൽ 1 ps / 1 ps `default_nettype none' എന്ന് ടൈപ്പ് ചെയ്യുക

മൊഡ്യൂൾ blinking_led_child_empty (

// ക്ലോക്ക് ഇൻപുട്ട് വയർ ക്ലോക്ക്, ഇൻപുട്ട് വയർ [31:0] കൌണ്ടർ,

// LED-കളുടെ ഔട്ട്പുട്ട് വയർ led_three_on-നുള്ള നിയന്ത്രണ സിഗ്നലുകൾ

);

// LED സജീവമാണ് led_three_on = 1'b0 അസൈൻ ചെയ്യുക;

എൻഡ്മൊഡ്യൂൾ |

| blinking_led_slow.sv | LED_TWO

പതുക്കെ മിന്നിമറയുന്നു. |

`ടൈംസ്കെയിൽ 1 ps / 1 ps `default_nettype none module blinking_led_slow( // ക്ലോക്ക് ഇൻപുട്ട് വയർ ക്ലോക്ക്, ഇൻപുട്ട് വയർ [31:0] കൌണ്ടർ,

// LED-കളുടെ ഔട്ട്പുട്ട് വയർ led_two_on-നുള്ള നിയന്ത്രണ സിഗ്നലുകൾ, ഔട്ട്പുട്ട് വയർ led_three_on

);

ലോക്കൽപരം COUNTER_TAP = 27; റെജി led_two_on_r; അസൈൻ led_two_on = led_two_on_r;

// കൗണ്ടർ: always_ff @(posedge clock) led_two_on_r <= counter[COUNTER_TAP] ആരംഭിക്കുന്നു; അവസാനിക്കുന്നു

മിന്നുന്ന_led_child u_blinking_led_child( .led_three_on (led_three_on), .കൗണ്ടർ (കൗണ്ടർ), .ക്ലോക്ക് (ക്ലോക്ക്) |

| File പേര് | വിവരണം | കോഡ് |

| );ndmodule |

ഘട്ടം 3: പേജ് 7-ൽ ഡിസൈൻ പാർട്ടീഷനുകൾ സൃഷ്ടിക്കുന്നു

ഘട്ടം 7: പുനരവലോകനങ്ങൾ സൃഷ്ടിക്കുന്നു

PR ഡിസൈൻ ഫ്ലോ ഇന്റൽ ക്വാർട്ടസ് പ്രൈം സോഫ്റ്റ്വെയറിലെ പ്രോജക്റ്റ് റിവിഷൻ ഫീച്ചർ ഉപയോഗിക്കുന്നു. നിങ്ങളുടെ പ്രാരംഭ രൂപകൽപ്പന അടിസ്ഥാന പുനരവലോകനമാണ്, അവിടെ നിങ്ങൾ എഫ്പിജിഎയിലെ സ്റ്റാറ്റിക് റീജിയൻ അതിരുകളും വീണ്ടും ക്രമീകരിക്കാവുന്ന പ്രദേശങ്ങളും നിർവചിക്കുന്നു. അടിസ്ഥാന പുനരവലോകനത്തിൽ നിന്ന്, നിങ്ങൾ ഒന്നിലധികം പുനരവലോകനങ്ങൾ സൃഷ്ടിക്കുന്നു. ഈ പുനരവലോകനങ്ങളിൽ പിആർ മേഖലകൾക്കായുള്ള വ്യത്യസ്ത നിർവ്വഹണങ്ങൾ അടങ്ങിയിരിക്കുന്നു. എന്നിരുന്നാലും, എല്ലാ PR നടപ്പിലാക്കൽ പുനരവലോകനങ്ങളും അടിസ്ഥാന പുനരവലോകനത്തിൽ നിന്നുള്ള ഉയർന്ന തലത്തിലുള്ള പ്ലെയ്സ്മെന്റും റൂട്ടിംഗ് ഫലങ്ങളും ഉപയോഗിക്കുന്നു. ഒരു PR ഡിസൈൻ കംപൈൽ ചെയ്യുന്നതിന്, നിങ്ങൾ ഓരോ വ്യക്തിക്കും വേണ്ടി ഒരു PR നടപ്പിലാക്കൽ പുനരവലോകനവും സിന്തസിസ് പുനരവലോകനവും സൃഷ്ടിക്കണം. ഈ റഫറൻസ് ഡിസൈനിൽ, അടിസ്ഥാന പുനരവലോകനത്തിന് (blinking_led) പുറമേ, മൂന്ന് ചൈൽഡ്-ലെവൽ വ്യക്തികളും രണ്ട് പേരന്റ്-ലെവൽ വ്യക്തികളും അഞ്ച് വ്യത്യസ്ത സിന്തസിസ് റിവിഷനുകളും അഞ്ച് വ്യത്യസ്ത നിർവ്വഹണ പുനരവലോകനങ്ങളും ഉൾക്കൊള്ളുന്നു:

പട്ടിക 3. രണ്ട് പേരന്റ് വ്യക്തികൾക്കും മൂന്ന്-കുട്ടികൾക്കുള്ള വ്യക്തികൾക്കും വേണ്ടിയുള്ള പുനരവലോകനങ്ങൾ

| സിന്തസിസ് റിവിഷൻ | നടപ്പാക്കൽ പുനരവലോകനം |

| blinking_led_parent, blinking_led_default | മിന്നുന്ന_led_pr_alpha |

| ബ്ലിങ്കിംഗ്_ലെഡ്_പാരന്റ്, മിന്നുന്ന_കുട്ടി_സ്ലോ | blinking_led_pr_bravo |

| ബ്ലിങ്കിംഗ്_ലെഡ്_പാരന്റ്, മിന്നുന്ന_കുട്ടി_ശൂന്യം | blinking_led_pr_charlie |

| ബ്ലിങ്കിംഗ്_ലെഡ്_പാരന്റ്_സ്ലോ, ബ്ലിങ്കിംഗ്_ലെഡ്_ചൈൽഡ്_സ്ലോ | blinking_led_pr_delta |

| ബ്ലിങ്കിംഗ്_ലെഡ്_പാരന്റ്_സ്ലോ, മിന്നുന്ന_കുട്ടി_ശൂന്യം | blinking_led_pr_emma |

നടപ്പാക്കൽ പുനരവലോകനങ്ങൾ സൃഷ്ടിക്കുന്നു

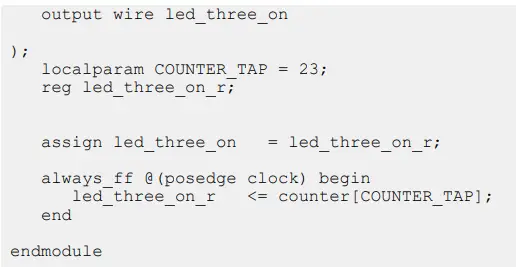

PR നടപ്പിലാക്കൽ പുനരവലോകനങ്ങൾ സൃഷ്ടിക്കുന്നതിന്:

- പുനരവലോകന ഡയലോഗ് ബോക്സ് തുറക്കാൻ, Project ➤ Revisions ക്ലിക്ക് ചെയ്യുക.

- ഒരു പുതിയ പുനരവലോകനം സൃഷ്ടിക്കാൻ, < ഡബിൾ ക്ലിക്ക് ചെയ്യുക >.

- റിവിഷൻ പേര് blinking_led_pr_alpha എന്ന് വ്യക്തമാക്കുകയും റിവിഷൻ അടിസ്ഥാനമാക്കിയുള്ളതിന് blinking_led തിരഞ്ഞെടുക്കുക.

- നിലവിലെ പുനരവലോകന ഓപ്ഷനായി സജ്ജമാക്കുക എന്നത് പ്രവർത്തനരഹിതമാക്കി ശരി ക്ലിക്കുചെയ്യുക.

- അതുപോലെ, blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta, blinking_led_pr_emma റിവിഷനുകൾ എന്നിവ ബ്ലിങ്കിംഗ്_ലെഡ് റിവിഷനെ അടിസ്ഥാനമാക്കി സൃഷ്ടിക്കുക.

കുറിപ്പ്: മുകളിലുള്ള പുനരവലോകനങ്ങൾ നിലവിലെ പുനരവലോകനമായി സജ്ജീകരിക്കരുത്.

ചിത്രം 9. പുനരവലോകനങ്ങൾ സൃഷ്ടിക്കുന്നു

സിന്തസിസ്-ഒൺലി റിവിഷനുകൾ സൃഷ്ടിക്കുന്നു

വ്യക്തികൾക്കായി സിന്തസിസ് മാത്രമുള്ള പുനരവലോകനങ്ങൾ സൃഷ്ടിക്കുന്നതിന്, നിങ്ങൾ ഉയർന്ന തലത്തിലുള്ള എന്റിറ്റിയും അനുബന്ധ SystemVerilog-ഉം നൽകണം file ഓരോ വ്യക്തികൾക്കും:

- Intel Quartus Prime സോഫ്റ്റ്വെയറിൽ Project ➤ Revisions ക്ലിക്ക് ചെയ്യുക.

- Blinking_led റിവിഷൻ അടിസ്ഥാനമാക്കി blinking_led_default റിവിഷൻ സൃഷ്ടിക്കുക. ഈ പുനരവലോകനം നിലവിലെ പുനരവലോകനമായി സജ്ജീകരിക്കരുത്.

- blinking_led_default.qsf പരിഷ്ക്കരിക്കുക file ഇനിപ്പറയുന്ന അസൈൻമെന്റുകൾ ഉൾപ്പെടുത്താൻ:

set_global_assignment -name TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -നാമം SYSTEMVERILOG_FILE - അതുപോലെ, blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent, blinking_led_parent_slow റിവിഷനുകൾ ബ്ലിങ്കിംഗ്_ലെഡ് റിവിഷൻ അടിസ്ഥാനമാക്കി സൃഷ്ടിക്കുക. ഈ പുനരവലോകനങ്ങളെ നിലവിലെ പുനരവലോകനങ്ങളായി സജ്ജീകരിക്കരുത്.

- blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, blinking_led_parent_slow.qsf എന്നിവ അപ്ഡേറ്റ് ചെയ്യുക fileകൾ അവരുടെ അനുബന്ധവുമായി

TOP_LEVEL_ENTITY കൂടാതെ SYSTEMVERILOG_FILE അസൈൻമെന്റുകൾ:

- സിന്തസിസ് പിശകുകൾ ഒഴിവാക്കാൻ, സിന്തസിസ് റിവിഷൻ ഉറപ്പാക്കുക fileചൈൽഡ് പാർട്ടീഷനുകളിൽ ഡിസൈൻ പാർട്ടീഷനോ പിൻ അസൈൻമെന്റുകളോ ലോജിക് ലോക്കോ അടങ്ങിയിട്ടില്ല.

മേഖല അസൈൻമെന്റുകൾ. കൂടാതെ, സിന്തസിസ് റിവിഷൻ fileപാരന്റ് പാർട്ടീഷനുകൾക്കുള്ള s-ൽ അനുബന്ധ ചൈൽഡ് പാർട്ടീഷനുകൾക്കുള്ള ഡിസൈൻ പാർട്ടീഷൻ അസൈൻമെന്റുകൾ മാത്രമേ അടങ്ങിയിരിക്കാവൂ. blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, blinking_led_parent_slow.pdf എന്നിവയിൽ എന്തെങ്കിലും ഉണ്ടെങ്കിൽ ഈ അസൈൻമെന്റുകൾ നീക്കം ചെയ്യുക files

- blinking_led_parent.qsf, blinking_led_parent_slow.qsf എന്നിവയിൽ ഇനിപ്പറയുന്ന അസൈൻമെന്റുകൾ ഉൾപ്പെടുത്തുക files:

- blinking_led.qpf എന്ന് പരിശോധിക്കുക file പ്രത്യേക ക്രമമൊന്നുമില്ലാതെ, ഇനിപ്പറയുന്ന പുനരവലോകനങ്ങൾ അടങ്ങിയിരിക്കുന്നു:

- കുറിപ്പ്: നിങ്ങൾ റിവിഷൻ പകർത്തുകയാണെങ്കിൽ filehpr ഫോൾഡറിൽ നിന്ന്, blinking_led.qpf സ്വമേധയാ അപ്ഡേറ്റ് ചെയ്യുക file കോഡിന്റെ മുകളിലെ വരികൾക്കൊപ്പം.

റിവിഷൻ തരം വ്യക്തമാക്കുന്നു

നിങ്ങളുടെ ഓരോ പുനരവലോകനത്തിനും നിങ്ങൾ പുനരവലോകന തരം നൽകണം. മൂന്ന് പുനരവലോകന തരങ്ങളുണ്ട്:

- ഭാഗിക പുനർക്രമീകരണം - അടിസ്ഥാനം

- ഭാഗിക പുനഃക്രമീകരണം - വ്യക്തി സമന്വയം

- ഭാഗികമായ പുനർക്രമീകരണം - വ്യക്തിത്വം നടപ്പിലാക്കൽ

- ഓരോ പുനരവലോകനത്തിനും വേണ്ടിയുള്ള റിവിഷൻ-ടൈപ്പ് അസൈൻമെന്റുകൾ ഇനിപ്പറയുന്ന പട്ടിക പട്ടികപ്പെടുത്തുന്നു:

പട്ടിക 4. റിവിഷൻ തരങ്ങൾ

| പുനരവലോകന നാമം | റിവിഷൻ തരം |

| blinking_led.qsf | ഭാഗിക പുനർക്രമീകരണം - അടിസ്ഥാനം |

| blinking_led_default.qsf | ഭാഗിക പുനഃക്രമീകരണം - വ്യക്തി സമന്വയം |

| blinking_led_child_empty.qsf | ഭാഗിക പുനഃക്രമീകരണം - വ്യക്തി സമന്വയം |

| blinking_led_child_slow.qsf | ഭാഗിക പുനഃക്രമീകരണം - വ്യക്തി സമന്വയം |

| blinking_led_parent.qsf | ഭാഗിക പുനഃക്രമീകരണം - വ്യക്തി സമന്വയം |

| blinking_led_parent_slow.qsf | ഭാഗിക പുനഃക്രമീകരണം - വ്യക്തി സമന്വയം |

| blinking_led_pr_alpha.qsf | ഭാഗികമായ പുനർക്രമീകരണം - വ്യക്തിത്വം നടപ്പിലാക്കൽ |

| blinking_led_pr_bravo.qsf | ഭാഗികമായ പുനർക്രമീകരണം - വ്യക്തിത്വം നടപ്പിലാക്കൽ |

| blinking_led_pr_charlie.qsf | ഭാഗികമായ പുനർക്രമീകരണം - വ്യക്തിത്വം നടപ്പിലാക്കൽ |

| blinking_led_pr_delta.qsf | ഭാഗികമായ പുനർക്രമീകരണം - വ്യക്തിത്വം നടപ്പിലാക്കൽ |

| blinking_led_pr_emma.qsf | ഭാഗികമായ പുനർക്രമീകരണം - വ്യക്തിത്വം നടപ്പിലാക്കൽ |

- പ്രൊജക്റ്റ് ➤ റിവിഷനുകൾ ക്ലിക്ക് ചെയ്യുക. പുനരവലോകന ഡയലോഗ് ബോക്സ് ദൃശ്യമാകുന്നു.

- റിവിഷൻ നെയിം കോളത്തിൽ blinking_led തിരഞ്ഞെടുത്ത് നിലവിലെ സെറ്റ് ക്ലിക്ക് ചെയ്യുക.

- പ്രയോഗിക്കുക ക്ലിക്ക് ചെയ്യുക. blinking_led റിവിഷൻ തുറക്കുന്നു.

- Blinking_led എന്നതിനായി പുനരവലോകന തരം സജ്ജീകരിക്കാൻ, അസൈൻമെന്റുകൾ ➤ ക്രമീകരണങ്ങൾ ➤ പൊതുവായത് ക്ലിക്കുചെയ്യുക.

- ഭാഗിക പുനർക്രമീകരണം - അടിസ്ഥാനമായി റിവിഷൻ തരം തിരഞ്ഞെടുക്കുക.

- അതുപോലെ, മുകളിലെ പട്ടികയിൽ പട്ടികപ്പെടുത്തിയിരിക്കുന്നതുപോലെ മറ്റ് പത്ത് പുനരവലോകനങ്ങൾക്കായി പുനരവലോകന തരങ്ങൾ സജ്ജമാക്കുക.

- കുറിപ്പ്: പുനരവലോകന തരം നൽകുന്നതിന് മുമ്പ് നിങ്ങൾ ഓരോ പുനരവലോകനവും നിലവിലെ പുനരവലോകനമായി സജ്ജീകരിക്കണം. ഓരോ .qsf എന്ന് പരിശോധിക്കുക file ഇനിപ്പറയുന്ന അസൈൻമെന്റ് അടങ്ങിയിരിക്കുന്നു:

- കുറിപ്പ്: PR നടപ്പിലാക്കൽ കംപൈലിൽ നിങ്ങൾ ഉപയോഗിക്കാൻ ആഗ്രഹിക്കുന്ന ഏതെങ്കിലും ഫിറ്റർ-നിർദ്ദിഷ്ട ക്രമീകരണങ്ങൾ വ്യക്തിഗത നിർവ്വഹണ പുനരവലോകനങ്ങളിലേക്ക് ചേർക്കുക. ഫിറ്റർ-നിർദ്ദിഷ്ട ക്രമീകരണങ്ങൾ വ്യക്തിയുടെ ഫിറ്റിനെ ബാധിക്കുന്നു, എന്നാൽ ഇറക്കുമതി ചെയ്ത സ്റ്റാറ്റിക് മേഖലയെ ബാധിക്കില്ല. വ്യക്തിഗത വ്യക്തിഗത സിന്തസിസ് പുനരവലോകനങ്ങളിലേക്ക് നിങ്ങൾക്ക് ഏതെങ്കിലും സിന്തസിസ്-നിർദ്ദിഷ്ട ക്രമീകരണങ്ങൾ ചേർക്കാനും കഴിയും.

വ്യക്തികൾക്കായി പുനരവലോകനങ്ങൾ സൃഷ്ടിക്കുക

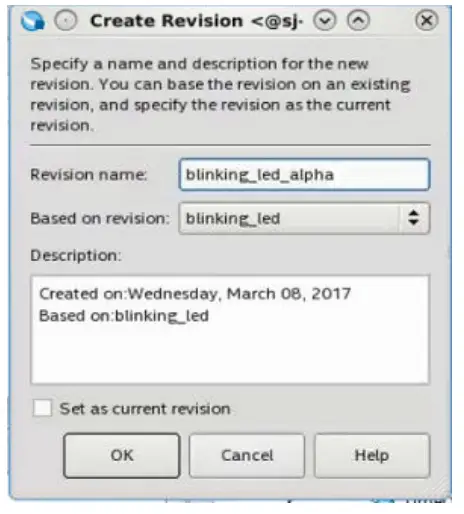

ഘട്ടം 8: ഹൈറാർക്കിക്കൽ ഭാഗിക റീകോൺഫിഗറേഷൻ ഫ്ലോ സ്ക്രിപ്റ്റ് ജനറേറ്റുചെയ്യുന്നു

ഹൈറാർക്കിക്കൽ ഭാഗിക പുനർക്രമീകരണ ഫ്ലോ സ്ക്രിപ്റ്റ് സൃഷ്ടിക്കുന്നതിന്:

- ഇന്റൽ ക്വാർട്ടസ് പ്രൈം കമാൻഡ് ഷെല്ലിൽ നിന്ന്, ഇനിപ്പറയുന്ന കമാൻഡ് പ്രവർത്തിപ്പിച്ച് ഒരു ഫ്ലോ ടെംപ്ലേറ്റ് സൃഷ്ടിക്കുക:

- ഇന്റൽ ക്വാർട്ടസ് പ്രൈം a10_hier_partial_reconfig/flow.tcl ജനറേറ്റുചെയ്യുന്നു file.

- ജനറേറ്റുചെയ്ത a10_hier_partial_reconfig/setup.tcl.ex എന്നതിന്റെ പേര് മാറ്റുകample to a10_hier_partial_reconfig/setup.tcl, നിങ്ങളുടെ ഭാഗിക പുനർക്രമീകരണ പ്രോജക്റ്റ് വിശദാംശങ്ങൾ വ്യക്തമാക്കുന്നതിന് സ്ക്രിപ്റ്റ് പരിഷ്ക്കരിക്കുക:

a. പ്രോജക്റ്റിന്റെ പേര് നിർവചിക്കുന്നതിന്, ഇനിപ്പറയുന്ന വരി അപ്ഡേറ്റ് ചെയ്യുക: b. അടിസ്ഥാന പുനരവലോകനം നിർവചിക്കുന്നതിന്, ഇനിപ്പറയുന്ന വരി അപ്ഡേറ്റ് ചെയ്യുക:

b. അടിസ്ഥാന പുനരവലോകനം നിർവചിക്കുന്നതിന്, ഇനിപ്പറയുന്ന വരി അപ്ഡേറ്റ് ചെയ്യുക:

- പിആർ പാർട്ടീഷൻ നാമങ്ങളും പുനരവലോകനങ്ങൾ നടപ്പിലാക്കുന്ന ഉറവിട പുനരവലോകനവും സഹിതം ഭാഗികമായ പുനർക്രമീകരണം നടപ്പിലാക്കൽ പുനരവലോകനങ്ങൾ ഓരോന്നും നിർവചിക്കുന്നതിന്, ഇനിപ്പറയുന്ന വരികൾ അപ്ഡേറ്റ് ചെയ്യുക:

കുറിപ്പ്: എല്ലാ റിവിഷൻ പ്രോജക്റ്റുകളും blinking_led.qpf-ന്റെ അതേ ഡയറക്ടറിയിലായിരിക്കണം. അല്ലെങ്കിൽ, അതിനനുസരിച്ച് ഫ്ലോ സ്ക്രിപ്റ്റ് അപ്ഡേറ്റ് ചെയ്യുക.

ഘട്ടം 9: ഹൈറാർക്കിക്കൽ ഭാഗിക റീകോൺഫിഗറേഷൻ ഫ്ലോ സ്ക്രിപ്റ്റ് പ്രവർത്തിപ്പിക്കുന്നു

ഹൈറാർക്കിക്കൽ ഭാഗിക പുനർക്രമീകരണ ഫ്ലോ സ്ക്രിപ്റ്റ് പ്രവർത്തിപ്പിക്കുന്നതിന്:

- ടൂളുകൾ ➤ Tcl സ്ക്രിപ്റ്റുകൾ ക്ലിക്ക് ചെയ്യുക. Tcl Scripts ഡയലോഗ് ബോക്സ് ദൃശ്യമാകുന്നു.

- പ്രോജക്റ്റിലേക്ക് ചേർക്കുക ക്ലിക്കുചെയ്യുക, ബ്രൗസ് ചെയ്ത് a10_hier_partial_reconfig/flow.tcl തിരഞ്ഞെടുക്കുക.

- ലൈബ്രറി പാളിയിൽ a10_hier_partial_reconfig/flow.tcl തിരഞ്ഞെടുത്ത് റൺ ക്ലിക്ക് ചെയ്യുക.

ഈ സ്ക്രിപ്റ്റ് മൂന്ന് വ്യക്തികളുടെ സമന്വയം പ്രവർത്തിപ്പിക്കുന്നു. ഇന്റൽ ക്വാർട്ടസ് പ്രൈം ഒരു SRAM ഒബ്ജക്റ്റ് സൃഷ്ടിക്കുന്നു File (.sof), ഒരു ഭാഗിക മുഖംമൂടിയുള്ള SRAM ഒബ്ജക്റ്റ് File (.pmsf), ഒരു റോ ബൈനറിയും File (.rbf) ഓരോ വ്യക്തികൾക്കും.

ശ്രദ്ധിക്കുക: ഇന്റൽ ക്വാർട്ടസ് പ്രൈം കമാൻഡ് ഷെല്ലിൽ നിന്ന് സ്ക്രിപ്റ്റ് പ്രവർത്തിപ്പിക്കുന്നതിന്, ഇനിപ്പറയുന്ന കമാൻഡ് ടൈപ്പ് ചെയ്യുക:

- ഭാഗിക പുനർക്രമീകരണ ഡിസൈൻ കംപൈൽ ചെയ്യുക

- ഭാഗിക റീകോൺഫിഗറേഷൻ ഫ്ലോ സ്ക്രിപ്റ്റ് ഉപയോഗിക്കുന്നു

- ഭാഗിക റീകോൺഫിഗറേഷൻ ഫ്ലോ സ്ക്രിപ്റ്റ് കോൺഫിഗർ ചെയ്യുന്നു

- പ്രോഗ്രാമിംഗ് സൃഷ്ടിക്കുക Files

ഘട്ടം 10: ബോർഡ് പ്രോഗ്രാമിംഗ്

നിങ്ങൾ ആരംഭിക്കുന്നതിന് മുമ്പ്:

- Intel Arria 10 SoC ഡെവലപ്മെന്റ് ബോർഡിലേക്ക് വൈദ്യുതി വിതരണം ബന്ധിപ്പിക്കുക.

- നിങ്ങളുടെ PC USB പോർട്ടിനും വികസന ബോർഡിലെ USB Blaster പോർട്ടിനും ഇടയിൽ USB Blaster കേബിൾ ബന്ധിപ്പിക്കുക.

Intel Arria 10 SoC ഡെവലപ്മെന്റ് ബോർഡിൽ ഡിസൈൻ പ്രവർത്തിപ്പിക്കുന്നതിന്:

- ഇന്റൽ ക്വാർട്ടസ് പ്രൈം സോഫ്റ്റ്വെയർ തുറന്ന് ടൂൾസ് ➤ പ്രോഗ്രാമർ ക്ലിക്ക് ചെയ്യുക.

- പ്രോഗ്രാമറിൽ, ഹാർഡ്വെയർ സെറ്റപ്പ് ക്ലിക്ക് ചെയ്ത് USB-Blaster തിരഞ്ഞെടുക്കുക.

- ഓട്ടോ ഡിറ്റക്റ്റ് ക്ലിക്ക് ചെയ്ത് ഉപകരണം തിരഞ്ഞെടുക്കുക, 10AS066N3.

- ശരി ക്ലിക്ക് ചെയ്യുക. ഇന്റൽ ക്വാർട്ടസ് പ്രൈം സോഫ്റ്റ്വെയർ ബോർഡിലെ മൂന്ന് എഫ്പിജിഎ ചിപ്പുകൾ ഉപയോഗിച്ച് പ്രോഗ്രാമറെ കണ്ടെത്തുകയും അപ്ഡേറ്റ് ചെയ്യുകയും ചെയ്യുന്നു.

- 10AS066N3 ഉപകരണം തിരഞ്ഞെടുക്കുക, മാറ്റുക ക്ലിക്കുചെയ്യുക File ഒപ്പം blinking_led_pr_alpha.sof ലോഡുചെയ്യുക file.

- Blinking_led_pr_alpha.sof-നുള്ള പ്രോഗ്രാം/കോൺഫിഗർ പ്രവർത്തനക്ഷമമാക്കുക file.

- ആരംഭിക്കുക ക്ലിക്കുചെയ്യുക, പുരോഗതി ബാർ 100% എത്തുന്നതുവരെ കാത്തിരിക്കുക.

- യഥാർത്ഥ ഫ്ലാറ്റ് ഡിസൈനിന്റെ അതേ ആവൃത്തിയിൽ ബോർഡിലെ LED-കൾ മിന്നിമറയുന്നത് നിരീക്ഷിക്കുക.

- ചൈൽഡ് പിആർ മേഖല മാത്രം പ്രോഗ്രാം ചെയ്യാൻ, blinking_led_pr_alpha.sof-ൽ വലത് ക്ലിക്ക് ചെയ്യുക file പ്രോഗ്രാമറിൽ, ആഡ് പിആർ പ്രോഗ്രാമിംഗ് ക്ലിക്ക് ചെയ്യുക File.

- blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf തിരഞ്ഞെടുക്കുക file.

- Blinking_led_pr_alpha.sof-നുള്ള പ്രോഗ്രാം/കോൺഫിഗർ പ്രവർത്തനരഹിതമാക്കുക file.

- Blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf-നായി പ്രോഗ്രാം/കോൺഫിഗർ ചെയ്യുക file ആരംഭിക്കുക ക്ലിക്ക് ചെയ്യുക. ബോർഡിൽ, LED[0], LED[1] മിന്നുന്നത് തുടരുന്നത് നിരീക്ഷിക്കുക. പ്രോഗ്രസ് ബാർ 100% എത്തുമ്പോൾ, LED[2] അതേ നിരക്കിൽ മിന്നുന്നു, LED[3] മന്ദഗതിയിൽ മിന്നുന്നു.

- മാതാപിതാക്കളുടെയും കുട്ടികളുടെയും പിആർ മേഖല പ്രോഗ്രാം ചെയ്യുന്നതിന്, .rbf-ൽ റൈറ്റ് ക്ലിക്ക് ചെയ്യുക file പ്രോഗ്രാമറിൽ, PR പ്രോഗ്രാമിംഗ് മാറ്റുക ക്ലിക്കുചെയ്യുക File.

- blinking_led_pr_delta.pr_parent_partition.rbf തിരഞ്ഞെടുക്കുക file.

- ആരംഭിക്കുക ക്ലിക്ക് ചെയ്യുക. ബോർഡിൽ, LED[0], LED[1] മിന്നുന്നത് തുടരുന്നത് നിരീക്ഷിക്കുക. പ്രോഗ്രസ് ബാർ 100% എത്തുമ്പോൾ, LED[2] ഉം LED[3] ഉം പതുക്കെ മിന്നുന്നു.

- ചൈൽഡ് പിആർ മേഖലയോ മാതാപിതാക്കളുടെയും കുട്ടികളുടെയും പിആർ മേഖലകളോ ഒരേസമയം ചലനാത്മകമായി റീ-പ്രോഗ്രാം ചെയ്യാൻ മുകളിലുള്ള ഘട്ടങ്ങൾ ആവർത്തിക്കുക.

ചിത്രം 10. Intel Arria 10 SoC ഡെവലപ്മെന്റ് ബോർഡ് പ്രോഗ്രാമിംഗ്

നിലവിലുള്ള ഒരു വ്യക്തിയെ പരിഷ്ക്കരിക്കുന്നു

- അടിസ്ഥാന പുനരവലോകനം പൂർണ്ണമായി സമാഹരിച്ചതിന് ശേഷവും നിങ്ങൾക്ക് നിലവിലുള്ള ഒരു വ്യക്തിയെ മാറ്റാൻ കഴിയും.

- ഉദാample, blinking_led_child_slow വ്യക്തിത്വം കൂടുതൽ സാവധാനത്തിൽ മിന്നിമറയാൻ കാരണമാകുന്നു:

- Blinking_led_child_slow.sv-ൽ file, COUNTER_TAP പരാമീറ്റർ 27 മുതൽ 28 വരെ പരിഷ്ക്കരിക്കുക.

- ഈ വ്യക്തിത്വം വീണ്ടും സമന്വയിപ്പിക്കുന്നതിനും വീണ്ടും നടപ്പിലാക്കുന്നതിനും, മാറ്റം ബാധിച്ച എല്ലാ സിന്തസിസ്-ഒൺലി റിവിഷനുകളും ഇംപ്ലിമെന്റേഷൻ റിവിഷനുകളും നിങ്ങൾ വീണ്ടും കംപൈൽ ചെയ്യണം. ഇനിപ്പറയുന്ന വരികൾ ഉൾപ്പെടുത്തുന്നതിന് setup.tcl സ്ക്രിപ്റ്റ് പരിഷ്ക്കരിക്കുക:

കുറിപ്പ്: blinking_led_pr_delta പുനരവലോകനത്തിനായി pr_parent_parition നിർവചിക്കുമ്പോൾ, ആ വ്യക്തിത്വത്തിന്റെ അന്തിമ സ്നാപ്പ്ഷോട്ട് നടപ്പിലാക്കുന്നതിനായി നിങ്ങൾ ഇറക്കുമതി ചെയ്യുന്നു. തൽഫലമായി, അനുബന്ധ ചൈൽഡ് പാർട്ടീഷൻ പരിഷ്കരിക്കുകയും നടപ്പിലാക്കുകയും ചെയ്യുമ്പോൾ, പാരന്റ് പാർട്ടീഷൻ ലോജിക്കിന്റെ നടപ്പാക്കൽ അതേപടി തുടരുന്നു.

കുറിപ്പ്: blinking_led_pr_delta പുനരവലോകനത്തിനായി pr_parent_parition നിർവചിക്കുമ്പോൾ, ആ വ്യക്തിത്വത്തിന്റെ അന്തിമ സ്നാപ്പ്ഷോട്ട് നടപ്പിലാക്കുന്നതിനായി നിങ്ങൾ ഇറക്കുമതി ചെയ്യുന്നു. തൽഫലമായി, അനുബന്ധ ചൈൽഡ് പാർട്ടീഷൻ പരിഷ്കരിക്കുകയും നടപ്പിലാക്കുകയും ചെയ്യുമ്പോൾ, പാരന്റ് പാർട്ടീഷൻ ലോജിക്കിന്റെ നടപ്പാക്കൽ അതേപടി തുടരുന്നു. ഈ കമാൻഡ് blinking_led_child_slow സിന്തസിസ് റിവിഷൻ വീണ്ടും സമന്വയിപ്പിക്കുന്നു, തുടർന്ന് blinking_led_pr_bravo ഉപയോഗിച്ച് PR നടപ്പിലാക്കൽ കംപൈൽ പ്രവർത്തിപ്പിക്കുന്നു.

ഈ കമാൻഡ് blinking_led_child_slow സിന്തസിസ് റിവിഷൻ വീണ്ടും സമന്വയിപ്പിക്കുന്നു, തുടർന്ന് blinking_led_pr_bravo ഉപയോഗിച്ച് PR നടപ്പിലാക്കൽ കംപൈൽ പ്രവർത്തിപ്പിക്കുന്നു. - സിന്തസിസ്-ഒൺലി റിവിഷനുകളുടെ സമാഹാരം നടത്താൻ, ഇനിപ്പറയുന്ന കമാൻഡ് പ്രവർത്തിപ്പിക്കുക: ഈ കമാൻഡ് അടിസ്ഥാന പുനരവലോകനം പുനഃസംഘടിപ്പിക്കുന്നില്ല.

- നടപ്പാക്കൽ പുനരവലോകനങ്ങളുടെ സമാഹാരം നടത്താൻ, ഇനിപ്പറയുന്ന കമാൻഡ് പ്രവർത്തിപ്പിക്കുക:

- ഈ കമാൻഡ് ബേസ് റിവിഷൻ വീണ്ടും കംപൈൽ ചെയ്യുന്നില്ല.

- ഘട്ടം 10-ലെ ഘട്ടങ്ങൾ പിന്തുടരുക: തത്ഫലമായുണ്ടാകുന്ന RBF പ്രോഗ്രാം ചെയ്യുന്നതിന് പേജ് 22-ൽ ബോർഡ് പ്രോഗ്രാമിംഗ് ചെയ്യുക file FPGA-യിലേക്ക്.

കുറിപ്പ്: ഓരോ പുനരവലോകനത്തിനും മുഴുവൻ ഫ്ലോയും പ്രവർത്തിപ്പിക്കുന്നത് ഒഴിവാക്കാൻ, setup.tcl സ്ക്രിപ്റ്റിൽ സിന്തസിസ്-ഒൺലി റിവിഷനുകളും ഇംപ്ലിമെന്റേഷൻ റിവിഷനുകളും നിർവചിച്ച് സ്ക്രിപ്റ്റ് പ്രവർത്തിപ്പിക്കുക.

ഡിസൈനിലേക്ക് ഒരു പുതിയ വ്യക്തിത്വം ചേർക്കുന്നു

നിങ്ങളുടെ അടിസ്ഥാന പുനരവലോകനങ്ങൾ പൂർണ്ണമായി സമാഹരിച്ചതിന് ശേഷം, നിങ്ങൾക്ക് ഇപ്പോഴും പുതിയ വ്യക്തികളെ ചേർക്കാനും ഈ വ്യക്തിത്വങ്ങൾ വ്യക്തിഗതമായി കംപൈൽ ചെയ്യാനും കഴിയും.

ഉദാample, blinking_led_parent_slow എന്നതിനായി ഒരു പുതിയ ചൈൽഡ് വ്യക്തിത്വത്തെ നിർവചിക്കാൻ, അത് led_three ഓഫ് ചെയ്യുന്നു:

- blinking_led_child_empty.sv എന്നതിലേക്ക് blinking_led_chdild_off.sv എന്നതിലേക്ക് പകർത്തുക.

- മിന്നുന്ന_led_child_off.sv-ൽ file, അസൈൻമെന്റ് പരിഷ്ക്കരിക്കുക, led_three_on = 1'b0 അസൈൻ ചെയ്യുക; led_three_on = 1'b1 അസൈൻ ചെയ്യാൻ;. നിങ്ങൾ മൊഡ്യൂളിന്റെ പേര് blinking_led_child_empty എന്നതിൽ നിന്ന് blinking_led_child_off എന്നാക്കി മാറ്റുന്നുവെന്ന് ഉറപ്പാക്കുക.

- പേജ് 16-ലെ സിന്തസിസ്-ഒൺലി റിവിഷനുകൾ സൃഷ്ടിക്കുക എന്നതിലെ ഘട്ടങ്ങൾ പിന്തുടർന്ന് blinking_led_child_off എന്ന പുതിയ സിന്തസിസ് പുനരവലോകനം സൃഷ്ടിക്കുക.

കുറിപ്പ്: blinking_led_child_off റിവിഷൻ ബ്ലിങ്കിംഗ്_led_child_off.sv ഉപയോഗിക്കണം file. - പേജ് 15-ലെ ഇംപ്ലിമെന്റേഷൻ റിവിഷനുകൾ സൃഷ്ടിക്കുക എന്നതിലെ ഘട്ടങ്ങൾ പിന്തുടർന്ന് blinking_led_pr_foxtrot, ഒരു പുതിയ നിർവ്വഹണ പുനരവലോകനം സൃഷ്ടിക്കുക.

- a10_hier_partial_reconfig/setup.tcl അപ്ഡേറ്റ് ചെയ്യുക file പുതിയ PR നടപ്പിലാക്കൽ നിർവ്വചിക്കാൻ:

- ഇനിപ്പറയുന്ന കമാൻഡ് പ്രവർത്തിപ്പിച്ച് ഈ പുതിയ സമന്വയവും നടപ്പിലാക്കൽ പുനരവലോകനവും കംപൈൽ ചെയ്യുക:

Intel Arria 10 ഉപകരണങ്ങൾക്കായുള്ള ഹൈറാർക്കിക്കൽ ഭാഗികമായ പുനർക്രമീകരണത്തെക്കുറിച്ചുള്ള പൂർണ്ണമായ വിവരങ്ങൾക്ക്, Intel Quartus Prime Pro എഡിഷൻ ഹാൻഡ്ബുക്കിന്റെ വോളിയം 1-ൽ ഒരു ഭാഗിക റീകോൺഫിഗറേഷൻ ഡിസൈൻ സൃഷ്ടിക്കുന്നത് കാണുക.

ബന്ധപ്പെട്ട വിവരങ്ങൾ

- ഒരു ഭാഗിക റീകോൺഫിഗറേഷൻ ഡിസൈൻ സൃഷ്ടിക്കുന്നു

- ഭാഗിക പുനഃക്രമീകരണ ഓൺലൈൻ പരിശീലനം

ഡോക്യുമെൻ്റ് റിവിഷൻ ചരിത്രം

പട്ടിക 5. ഡോക്യുമെന്റ് റിവിഷൻ ചരിത്രം

| പ്രമാണ പതിപ്പ് | സോഫ്റ്റ്വെയർ പതിപ്പ് | മാറ്റങ്ങൾ |

| 2017.11.06 | 17.1.0 | • അപ്ഡേറ്റ് ചെയ്തു റഫറൻസ് ഡിസൈൻ ആവശ്യകതകൾ സോഫ്റ്റ്വെയർ പതിപ്പുള്ള വിഭാഗം

• അപ്ഡേറ്റ് ചെയ്തു പിആർ പാർട്ടീഷനിംഗ് ഇല്ലാതെ ഫ്ലാറ്റ് റഫറൻസ് ഡിസൈൻ ഡിസൈൻ ബ്ലോക്ക് മാറ്റങ്ങളുള്ള ചിത്രം • അപ്ഡേറ്റ് ചെയ്തു റഫറൻസ് ഡിസൈൻ Files എന്നതിനെക്കുറിച്ചുള്ള വിവരങ്ങളുള്ള പട്ടിക Top_counter.sv മൊഡ്യൂൾ • അപ്ഡേറ്റ് ചെയ്തു ഭാഗിക പുനഃക്രമീകരണം IP കോർ ഇന്റഗ്രേഷൻ ഡിസൈൻ ബ്ലോക്ക് മാറ്റങ്ങളുള്ള ചിത്രം • കണക്കുകൾ അപ്ഡേറ്റ് ചെയ്തു - പാർട്ടീഷനുകളുടെ വിൻഡോ ഡിസൈൻ ചെയ്യുക ഒപ്പം ലോജിക് ലോക്ക് റീജിയൻസ് വിൻഡോ പുതിയ GUI പ്രതിഫലിപ്പിക്കാൻ • File പേര് മാറ്റങ്ങൾ • ടെക്സ്റ്റ് എഡിറ്റുകൾ |

| 2017.05.08 | 17.0.0 | പ്രമാണത്തിന്റെ പ്രാരംഭ റിലീസ് |

പ്രമാണങ്ങൾ / വിഭവങ്ങൾ

|

Arria 805 SoC ഡെവലപ്മെന്റ് ബോർഡിലെ ഒരു ഡിസൈനിന്റെ intel AN 10 ഹൈറാർക്കിക്കൽ ഭാഗിക പുനർക്രമീകരണം [pdf] ഉപയോക്തൃ ഗൈഡ് AN 805 Arria 10 SoC ഡെവലപ്മെന്റ് ബോർഡിലെ ഒരു ഡിസൈനിന്റെ ഹൈറാർക്കിക്കൽ ഭാഗിക പുനർക്രമീകരണം, AN 805, Arria 10 SoC ഡവലപ്മെന്റ് ബോർഡിലെ ഒരു ഡിസൈനിന്റെ ഹൈറാർക്കിക്കൽ ഭാഗിക പുനർക്രമീകരണം, Arria 10 SoC ഡവലപ്മെന്റ് ബോർഡിലെ ഒരു ഡിസൈനിന്റെ പുനർക്രമീകരണം, Arria 10 SoC ഡവലപ്മെന്റ് ബോർഡ്, 10 SoC വികസന ബോർഡ് |