intel AN 805 Hierarchical Partial Reconfiguration of a Design on Arria 10 SoC Development Board

ການສອນການກຳນົດຄ່າບາງສ່ວນຕາມລຳດັບສຳລັບຄະນະພັດທະນາ Intel® Arria® 10 SoC

ບັນທຶກແອັບພລິເຄຊັນນີ້ສະແດງໃຫ້ເຫັນເຖິງການຫັນປ່ຽນການອອກແບບທີ່ງ່າຍດາຍໄປສູ່ການອອກແບບທີ່ປັບຕັ້ງຄ່າໄດ້ບາງສ່ວນຕາມລຳດັບ, ແລະການປະຕິບັດການອອກແບບໃນກະດານພັດທະນາ Intel® Arria® 10 SoC. Hierarchical partial reconfiguration (HPR) ແມ່ນປະເພດພິເສດຂອງການປັບຄ່າບາງສ່ວນ (PR), ບ່ອນທີ່ທ່ານມີພາກພື້ນ PR ພາຍໃນພາກພື້ນ PR ອື່ນ. ທ່ານສາມາດສ້າງ personas ຫຼາຍສໍາລັບການແບ່ງປັນທັງເດັກນ້ອຍແລະພໍ່ແມ່. ທ່ານວາງພາທິຊັນເດັກນ້ອຍພາຍໃນພາທິຊັນພໍ່ແມ່ຂອງພວກເຂົາ. ການຕັ້ງຄ່າການແບ່ງພາຕິຊັນເດັກນ້ອຍຄືນໃໝ່ບໍ່ສົ່ງຜົນກະທົບຕໍ່ການເຮັດວຽກຢູ່ໃນພາກພື້ນຫຼັກ ຫຼື ພື້ນທີ່ຄົງທີ່. ການກຳນົດຄ່າພາທິຊັນພໍ່ແມ່ຄືນໃໝ່ບໍ່ສົ່ງຜົນກະທົບຕໍ່ການດຳເນີນການໃນພາກພື້ນສະຖິດ, ແຕ່ປ່ຽນການແບ່ງພາທິຊັນລູກຂອງພາກພື້ນແມ່ດ້ວຍສ່ວນແບ່ງສ່ວນລູກເລີ່ມຕົ້ນ. ວິທີການນີ້ມີປະສິດຕິຜົນໃນລະບົບທີ່ຫຼາຍຫນ້າທີ່ໃຊ້ເວລາແບ່ງປັນຊັບພະຍາກອນອຸປະກອນ FPGA ດຽວກັນ.

ການປັບຄ່າບາງສ່ວນໃຫ້ຄວາມກ້າວໜ້າຕໍ່ໄປນີ້ຕໍ່ກັບການອອກແບບຮາບພຽງ:

- ອະນຸຍາດໃຫ້ການປັບຕັ້ງຄ່າການອອກແບບທີ່ໃຊ້ເວລາແລ່ນ

- ເພີ່ມທະວີການຂະຫຍາຍການອອກແບບ

- ຫຼຸດຜ່ອນການຢຸດລະບົບ

- ຮອງຮັບຟັງຊັນເວລາ multiplexing ແບບເຄື່ອນໄຫວໃນການອອກແບບ

- ຫຼຸດຜ່ອນຄ່າໃຊ້ຈ່າຍແລະການບໍລິໂພກພະລັງງານໂດຍຜ່ານການນໍາໃຊ້ທີ່ມີປະສິດທິພາບຂອງພື້ນທີ່ກະດານ

- ໝາຍເຫດ:

- ການປະຕິບັດການອອກແບບການອ້າງອິງນີ້ຮຽກຮ້ອງໃຫ້ມີຄວາມຄຸ້ນເຄີຍພື້ນຖານກັບຂະບວນການປະຕິບັດ Intel Quartus® Prime FPGA ແລະຄວາມຮູ້ຂອງໂຄງການ Intel Quartus Prime ຕົ້ນຕໍ. files.

ຂໍ້ມູນທີ່ກ່ຽວຂ້ອງ

- ຄູ່ມືຜູ້ໃຊ້ Intel Arria 10 SoC Development Kit

- ແນວຄວາມຄິດການປັບຄ່າບາງສ່ວນ

- ກະແສການອອກແບບການປັບຕັ້ງຄ່າຄືນໃໝ່ບາງສ່ວນ

- ການແນະນຳການອອກແບບການປັບຕັ້ງຄ່າຄືນໃໝ່ບາງສ່ວນ

- ການພິຈາລະນາການອອກແບບການປັບຄ່າບາງສ່ວນ

ຂໍ້ກໍານົດການອອກແບບອ້າງອີງ

ການອອກແບບກະສານອ້າງອີງນີ້ຮຽກຮ້ອງໃຫ້ມີດັ່ງຕໍ່ໄປນີ້:

- ຊອບແວ Intel Quartus Prime Pro Edition ເວີຊັ່ນ 17.1 ສຳລັບການຈັດຕັ້ງປະຕິບັດການອອກແບບ.

- ຊຸດພັດທະນາ Intel Arria 10 SoC ສໍາລັບການປະຕິບັດ FPGA.

ບໍລິສັດ Intel. ສະຫງວນລິຂະສິດທັງໝົດ. Intel, ໂລໂກ້ Intel, ແລະເຄື່ອງໝາຍ Intel ອື່ນໆແມ່ນເຄື່ອງໝາຍການຄ້າຂອງ Intel Corporation ຫຼືບໍລິສັດຍ່ອຍຂອງມັນ. Intel ຮັບປະກັນປະສິດທິພາບຂອງຜະລິດຕະພັນ FPGA ແລະ semiconductor ຂອງຕົນຕໍ່ກັບຂໍ້ມູນຈໍາເພາະໃນປະຈຸບັນໂດຍສອດຄ່ອງກັບການຮັບປະກັນມາດຕະຖານຂອງ Intel, ແຕ່ສະຫງວນສິດທີ່ຈະປ່ຽນແປງຜະລິດຕະພັນແລະການບໍລິການໄດ້ທຸກເວລາໂດຍບໍ່ມີການແຈ້ງການ. Intel ຖືວ່າບໍ່ມີຄວາມຮັບຜິດຊອບ ຫຼືຄວາມຮັບຜິດຊອບທີ່ເກີດຂຶ້ນຈາກແອັບພລິເຄຊັນ ຫຼືການນຳໃຊ້ຂໍ້ມູນ, ຜະລິດຕະພັນ, ຫຼືບໍລິການໃດໜຶ່ງທີ່ໄດ້ອະທິບາຍໄວ້ໃນນີ້ ຍົກເວັ້ນຕາມທີ່ໄດ້ຕົກລົງຢ່າງຈະແຈ້ງໃນລາຍລັກອັກສອນໂດຍ Intel. ລູກຄ້າ Intel ໄດ້ຮັບຄໍາແນະນໍາໃຫ້ໄດ້ຮັບສະບັບຫລ້າສຸດຂອງຂໍ້ມູນຈໍາເພາະຂອງອຸປະກອນກ່ອນທີ່ຈະອີງໃສ່ຂໍ້ມູນໃດໆທີ່ຈັດພີມມາແລະກ່ອນທີ່ຈະວາງຄໍາສັ່ງສໍາລັບຜະລິດຕະພັນຫຼືການບໍລິການ.

- ຊື່ ແລະຍີ່ຫໍ້ອື່ນໆອາດຈະຖືກອ້າງວ່າເປັນຊັບສິນຂອງຄົນອື່ນ.

Reference Design Overview

- ການອອກແບບການອ້າງອິງນີ້ປະກອບດ້ວຍຕົວນັບ 32-bit ຫນຶ່ງ. ໃນລະດັບກະດານ, ການອອກແບບເຊື່ອມຕໍ່ໂມງກັບແຫຼ່ງ 50MHz ແລະເຊື່ອມຕໍ່ຜົນຜະລິດກັບສີ່ LEDs ໃນ FPGA. ການເລືອກຜົນຜະລິດຈາກ counter bits ໃນລໍາດັບສະເພາະໃດຫນຶ່ງເຮັດໃຫ້ LEDs ກະພິບໃນຄວາມຖີ່ສະເພາະໃດຫນຶ່ງ.

ຮູບທີ 1. ການອອກແບບກະສານອ້າງອີງ Flat ໂດຍບໍ່ມີການແບ່ງປັນ PR

ການອອກແບບອ້າງອີງ Files

ການສອນການປັບຄ່າບາງສ່ວນແມ່ນມີຢູ່ໃນສະຖານທີ່ຕໍ່ໄປນີ້: https://github.com/intel/fpga-partial-reconfig

ເພື່ອດາວໂຫລດ tutorial ໄດ້:

- ກົດ Clone ຫຼືດາວໂຫລດ.

- ກົດດາວໂຫລດ ZIP. Unzip FPGA-partial-config-master.zip file.

- ໄປທີ່ໂຟນເດີຍ່ອຍ tutorials/a10_soc_devkit_blinking_led_hpr ເພື່ອເຂົ້າເຖິງການອອກແບບອ້າງອີງ.

ໂຟນເດີຮາບພຽງປະກອບດ້ວຍດັ່ງຕໍ່ໄປນີ້ files:

ຕາຕະລາງ 1. ການອອກແບບອ້າງອີງ Files

| File ຊື່ | ລາຍລະອຽດ |

| ເທິງ. SV | ລະດັບສູງສຸດ file ປະກອບດ້ວຍການປະຕິບັດຮາບພຽງຂອງການອອກແບບ. ໂມດູນນີ້ເຮັດໃຫ້ການແບ່ງສ່ວນຍ່ອຍຂອງ blinking_led ແລະໂມດູນ top_counter. |

| top_counter.sv | ເຄົາເຕີ 32-ບິດລະດັບສູງສຸດທີ່ຄວບຄຸມ LED[1] ໂດຍກົງ. ຜົນຜະລິດທີ່ລົງທະບຽນຂອງເຄົາເຕີຄວບຄຸມ LED[0], ແລະຍັງໃຫ້ພະລັງງານ LED[2] ແລະ LED[3] ຜ່ານໂມດູນ blinking_led. |

| blinking_led.sdc | ກໍານົດຂໍ້ຈໍາກັດໄລຍະເວລາສໍາລັບໂຄງການ. |

| ສືບຕໍ່… | |

| File ຊື່ | ລາຍລະອຽດ |

| blinking_led.SV | ໃນບົດສອນນີ້, ທ່ານປ່ຽນໂມດູນນີ້ເປັນພາທິຊັນ PR ຂອງພໍ່ແມ່. ໂມດູນໄດ້ຮັບຜົນຜະລິດທີ່ລົງທະບຽນຂອງໂມດູນ top_counter, ເຊິ່ງຄວບຄຸມ LED[2] ແລະ LED[3]. |

| blinking_led.qpf | ໂຄງການ Intel Quartus Prime file ປະກອບມີບັນຊີລາຍຊື່ຂອງການແກ້ໄຂທັງຫມົດໃນໂຄງການ. |

| blinking_led.qsf | ການຕັ້ງຄ່າ Intel Quartus Prime file ປະກອບດ້ວຍການມອບຫມາຍແລະການຕັ້ງຄ່າສໍາລັບໂຄງການ. |

ໝາຍເຫດ: ໂຟນເດີ hpr ມີຊຸດທີ່ສົມບູນ files ທ່ານສ້າງໂດຍໃຊ້ບັນທຶກຄໍາຮ້ອງສະຫມັກນີ້. ອ້າງອີງເຫຼົ່ານີ້ files ໃນຈຸດໃດຫນຶ່ງໃນລະຫວ່າງການ walkthrough.

ຮູບທີ 2. ການອອກແບບອ້າງອີງ Files

ການອ້າງອີງການອອກແບບ Walkthrough

ຂັ້ນຕອນຕໍ່ໄປນີ້ອະທິບາຍການນຳໃຊ້ການປັບຄ່າບາງສ່ວນໃຫ້ກັບການອອກແບບຮາບພຽງ. ການສອນການນຳໃຊ້ຊອບແວ Intel Quartus Prime Pro Edition ສໍາລັບກະດານພັດທະນາ Intel Arria 10 SoC:

- ຂັ້ນຕອນທີ 1: ການເລີ່ມຕົ້ນໃນຫນ້າ 6

- ຂັ້ນຕອນທີ 2: ສ້າງໂມດູນຍ່ອຍລະດັບລູກໃນໜ້າ 6

- ຂັ້ນຕອນທີ 3: ການສ້າງ Partitions ການອອກແບບໃນຫນ້າ 7

- ຂັ້ນຕອນທີ 4: ການຈັດສັນການຈັດວາງ ແລະເຂດເສັ້ນທາງສຳລັບ PR Partitions ໃນໜ້າ 9

- ຂັ້ນຕອນທີ 5: ການເພີ່ມ Intel Arria 10 Partial Reconfiguration Controller IP Core ຢູ່ໜ້າ 10

- ຂັ້ນຕອນທີ 6: ການກໍານົດ Personas ໃນຫນ້າ 13

- ຂັ້ນຕອນທີ 7: ການສ້າງສະບັບປັບປຸງໃນຫນ້າ 15

- ຂັ້ນຕອນທີ 8: ການສ້າງລະບົບ Hierarchical Partial Reconfiguration Flow Script ໃນໜ້າ 20

- ຂັ້ນຕອນທີ 9: ແລ່ນສະຄຣິບໂຟລການປັບຄ່າສ່ວນລຳດັບຊັ້ນສູງໃນໜ້າ 21

- ຂັ້ນຕອນທີ 10: ການຂຽນໂປລແກລມຄະນະບໍດີໃນຫນ້າ 22

ຂັ້ນຕອນທີ 1: ການເລີ່ມຕົ້ນ

ເພື່ອຄັດລອກການອອກແບບອ້າງອີງ files ກັບສະພາບແວດລ້ອມການເຮັດວຽກຂອງທ່ານແລະລວບລວມການອອກແບບຮາບພຽງ blinking_led:

- ສ້າງໄດເລກະທໍລີໃນສະພາບແວດລ້ອມການເຮັດວຽກຂອງທ່ານ, a10_soc_devkit_blinking_led_hpr.

- ສຳເນົາການສອນທີ່ດາວໂຫຼດມາ/a10_soc_devkit_blinking_led_hpr/ໂຟເດີຍ່ອຍແບບແປໄປໃສ່ໄດເຣັກທໍຣີ, a10_soc_devkit_blinking_led_hpr.

- ໃນຊອບແວ Intel Quartus Prime Pro Edition, ຄລິກ File ➤ ເປີດໂຄງການ ແລະເລືອກ blinking_led.qpf.

- ເພື່ອລວບລວມການອອກແບບຮາບພຽງ, ຄລິກ ການປະມວນຜົນ ➤ ເລີ່ມການລວບລວມ.

ຂັ້ນຕອນທີ 2: ການສ້າງໂມດູນຍ່ອຍລະດັບເດັກ

ເພື່ອປ່ຽນການອອກແບບແບບຮາບພຽງນີ້ໃຫ້ເປັນການອອກແບບ PR ແບບລຳດັບ, ທ່ານຕ້ອງສ້າງໂມດູນຍ່ອຍຍ່ອຍ (blinking_led_child. SV) ທີ່ຕິດຢູ່ພາຍໃນໂມດູນຍ່ອຍຂອງແມ່ (blinking_led.sv).

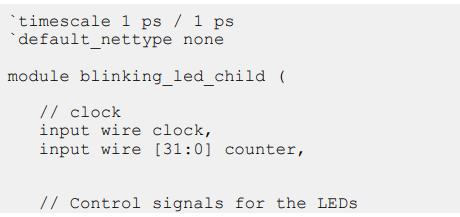

- ສ້າງການອອກແບບໃຫມ່ file, blinking_led_child.sv, ແລະເພີ່ມສາຍລະຫັດຕໍ່ໄປນີ້ໃສ່ນີ້ file: timescale 1 ps / 1 ps `default_nettype none module blinking_led_child ( // clock input wire clock, input wire [31:0] counter, // ການຄວບຄຸມສັນຍານສໍາລັບ LEDs

- ແກ້ໄຂ blinking_led.sv file ເພື່ອເຊື່ອມຕໍ່ led_two_on ກັບ bit 23 ຂອງ counter ຈາກພາກພື້ນ static, ແລະ instantiate blinking_led_child module. ຫຼັງຈາກການດັດແກ້, blinking_led.sv ຂອງທ່ານ file ຕ້ອງປະກົດວ່າດັ່ງຕໍ່ໄປນີ້:

- ກ່ຽວກັບການປັບປຸງການອອກແບບທັງຫມົດ files, ລວບລວມໂຄງການຄືນໃໝ່ໂດຍການຄລິກທີ່ Processing ➤ Start Compilation

ຂັ້ນຕອນທີ 3: ການສ້າງ Partitions ການອອກແບບ

ທ່ານຕ້ອງສ້າງການແບ່ງປັນການອອກແບບສໍາລັບແຕ່ລະພາກພື້ນ PR ທີ່ທ່ານຕ້ອງການທີ່ຈະ configure ບາງສ່ວນ. ທ່ານສາມາດສ້າງຈໍານວນສ່ວນທີ່ເປັນເອກະລາດຫຼືພາກພື້ນ PR ໃນການອອກແບບຂອງທ່ານ. ການສອນນີ້ສ້າງສອງພາທິຊັນການອອກແບບສໍາລັບ u_blinking_led_child ແລະ u_blinking_led instances.

ເພື່ອສ້າງການອອກແບບ partitions ສໍາລັບການ reconfiguration ບາງສ່ວນ hierarchical:

- ຄລິກຂວາໃສ່ຕົວຢ່າງ u_blinking_led_child ໃນ Project Navigator ແລະຄລິກ Design Partition ➤ ຕັ້ງເປັນ Design Partition. ໄອຄອນການແບ່ງປັນການອອກແບບຈະປາກົດຢູ່ຖັດຈາກແຕ່ລະຕົວຢ່າງທີ່ຕັ້ງເປັນພາທິຊັນ.

ຮູບທີ 3. ການສ້າງ Partitions ການອອກແບບຈາກ Project Navigator

- ເພື່ອກໍານົດປະເພດພາທິຊັນ, ໃຫ້ຄລິກຂວາໃສ່ຕົວຢ່າງ u_blinking_led_child ໃນແຖບລໍາດັບຊັ້ນ, ຄລິກ Design Partition ➤ ຕັ້ງຄ່າຄືນໃໝ່ໄດ້. ທ່ານພຽງແຕ່ສາມາດກໍານົດປະເພດພາທິຊັນຫຼັງຈາກຕັ້ງຕົວຢ່າງເປັນພາທິຊັນ. ການແບ່ງປັນການອອກແບບຈະປາກົດຢູ່ໃນ Assignments View ແຖບຂອງ Design Partitions Window.

ຮູບທີ 4. ການອອກແບບ Partitions Window

- ແກ້ໄຂຊື່ພາທິຊັນໃນປ່ອງຢ້ຽມການອອກແບບ Partitions ໂດຍການຄລິກສອງຄັ້ງຊື່. ສໍາລັບການອອກແບບອ້າງອີງນີ້, ປ່ຽນຊື່ພາທິຊັນເປັນ pr_partition.

ໝາຍເຫດ: ເມື່ອທ່ານສ້າງພາທິຊັນ, ຊອບແວ Intel Quartus Prime ຈະສ້າງຊື່ພາທິຊັນໂດຍອັດຕະໂນມັດ, ໂດຍອີງໃສ່ຊື່ຕົວຢ່າງແລະເສັ້ນທາງລໍາດັບຊັ້ນ. ຊື່ພາທິຊັນເລີ່ມຕົ້ນນີ້ສາມາດແຕກຕ່າງກັນກັບແຕ່ລະຕົວຢ່າງ. - ເຮັດຊ້ຳຂັ້ນຕອນທີ 1 ແລະ 2 ເພື່ອມອບໝາຍພາທິຊັນການອອກແບບທີ່ກຳນົດຄ່າຄືນໃໝ່ໃຫ້ກັບຕົວຢ່າງ u_blinking_led. ປ່ຽນຊື່ພາທິຊັນນີ້ເປັນ pr_parent_partition.

ກວດສອບວ່າ blinking_led.qsf ປະກອບດ້ວຍການມອບຫມາຍດັ່ງຕໍ່ໄປນີ້, ທີ່ສອດຄ້ອງກັນກັບການແບ່ງປັນການອອກແບບ reconfigurable ຂອງທ່ານ:

ສ້າງ Partitions ອອກແບບສໍາລັບ Reconfiguration ບາງສ່ວນ

ຂັ້ນຕອນທີ 4: ການຈັດສັນການຈັດວາງ ແລະເຂດເສັ້ນທາງສໍາລັບ PR Partitions

ເມື່ອທ່ານສ້າງການແກ້ໄຂພື້ນຖານ, ການອອກແບບ PR ໄຫຼໃຊ້ການຈັດສັນພາກພື້ນ PR ຂອງທ່ານເພື່ອຈັດວາງຫຼັກ persona ທີ່ສອດຄ້ອງກັນຢູ່ໃນພາກພື້ນທີ່ສະຫງວນໄວ້. ເພື່ອຊອກຫາ ແລະມອບໝາຍພາກພື້ນ PR ໃນແຜນພື້ນອຸປະກອນສຳລັບການປັບປຸງພື້ນຖານຂອງທ່ານ:

- ຄລິກຂວາໃສ່ຕົວຢ່າງ u_blinking_led_child ໃນ Project Navigator ແລະຄລິກ Logic Lock Region ➤ Create New Logic Lock Region. ພາກພື້ນຈະປາກົດຢູ່ໃນປ່ອງຢ້ຽມ Logic Lock Regions Window.

- ພາກພື້ນການຈັດວາງຂອງທ່ານຕ້ອງປິດລ້ອມດ້ວຍເຫດຜົນ blinking_led_child. ເລືອກພາກພື້ນການຈັດວາງໂດຍການຊອກຫາ node ໃນ Chip Planner. ຄລິກຂວາໃສ່ຊື່ພາກພື້ນ u_blinking_led_child ໃນ Project Navigator ແລະຄລິກ Locate Node ➤ Locate in Chip Planner.

ຮູບທີ 5. Chip Planner Node ສະຖານທີ່ສຳລັບ blinking_led

- ຢູ່ໃນປ່ອງຢ້ຽມ Logic Lock Regions, ລະບຸຈຸດພິກັດພາກພື້ນການຈັດວາງຢູ່ໃນຖັນຕົ້ນກຳເນີດ. ຕົ້ນກໍາເນີດແມ່ນກົງກັບມຸມຊ້າຍລຸ່ມຂອງພາກພື້ນ. ຕົວຢ່າງample, ເພື່ອກໍານົດພາກພື້ນການຈັດວາງທີ່ມີ (X1 Y1) ພິກັດເປັນ (69 10), ໃຫ້ລະບຸຕົ້ນກໍາເນີດເປັນ X69_Y10. ຊອບແວ Intel Quartus Prime ຈະຄິດໄລ່ພິກັດ (X2 Y2) ອັດຕະໂນມັດ (ເທິງຂວາ) ສໍາລັບພາກພື້ນການຈັດວາງ, ໂດຍອີງໃສ່ຄວາມສູງແລະຄວາມກວ້າງທີ່ທ່ານລະບຸ.

ໝາຍເຫດ: ການສອນນີ້ໃຊ້ຈຸດພິກັດ (X1 Y1) – (69 10), ແລະຄວາມສູງແລະຄວາມກວ້າງຂອງ 20 ສໍາລັບພາກພື້ນການຈັດວາງ. ກໍານົດຄ່າໃດໆສໍາລັບພາກພື້ນການຈັດວາງ, ສະຫນອງໃຫ້ວ່າພາກພື້ນກວມເອົາເຫດຜົນ blinking_led_child. - ເປີດໃຊ້ຕົວເລືອກທີ່ສະຫງວນໄວ້ ແລະ ຫຼັກເທົ່ານັ້ນ.

- ຄລິກສອງຄັ້ງທີ່ຕົວເລືອກ Routing Region. ກ່ອງໂຕ້ຕອບການຕັ້ງຄ່າພາກພື້ນ Logic Lock Routing Region ຈະປາກົດຂຶ້ນ.

- ເລືອກ Fixed with expansion for the Routing type. ການເລືອກທາງເລືອກນີ້ອັດຕະໂນມັດກໍານົດຄວາມຍາວການຂະຫຍາຍຂອງ 1.

ໝາຍເຫດ: ພາກພື້ນ routing ຈະຕ້ອງຂະຫນາດໃຫຍ່ກ່ວາພາກພື້ນການຈັດວາງ, ເພື່ອສະຫນອງຄວາມຍືດຫຍຸ່ນພິເສດສໍາລັບ Fitter ໃນເວລາທີ່ເຄື່ອງຈັກເສັ້ນທາງບຸກຄົນທີ່ແຕກຕ່າງກັນ. - ເຮັດຊ້ໍາຂັ້ນຕອນ 1 -6 ສໍາລັບຕົວຢ່າງ u_blinking_led. ການຈັດວາງລະດັບພໍ່ແມ່ ເຮັດຊ້ຳຂັ້ນຕອນ 1 -6 ສໍາລັບຕົວຢ່າງ u_blinking_led. ພາກພື້ນການຈັດວາງລະດັບພໍ່ແມ່ຕ້ອງກວມເອົາການຈັດວາງລະດັບເດັກນ້ອຍທີ່ສອດຄ້ອງກັນ ແລະ ພື້ນທີ່ກຳນົດທິດທາງ ໃນຂະນະທີ່ໃຫ້ພື້ນທີ່ພຽງພໍສຳລັບການຈັດວາງຕາມເຫດຜົນລະດັບພໍ່ແມ່. ການສອນນີ້ໃຊ້ຈຸດພິກັດ (X1 Y1) – (66 7), ຄວາມສູງ 47, ແລະຄວາມກວ້າງຂອງ 26 ສໍາລັບພື້ນທີ່ການຈັດວາງຂອງຕົວຢ່າງ u_blinking_led.

ຮູບ 6.Logic Lock Regions Window

ກວດສອບວ່າ blinking_led.qsf ມີວຽກງານດັ່ງຕໍ່ໄປນີ້, ທີ່ສອດຄ້ອງກັນກັບການວາງແຜນພື້ນເຮືອນຂອງທ່ານ:

- ວາງແຜນການອອກແບບການປັບຄ່າບາງສ່ວນ

- ເພີ່ມການຈັດຕັ້ງປະຕິບັດການປັບຄ່າບາງສ່ວນຄືນໃໝ່

ຂັ້ນຕອນທີ 5: ການເພີ່ມ Intel Arria 10 Partial Reconfiguration Controller IP Core

- ໃຊ້ Intel Arria 10 Partial Reconfiguration Controller IP core ເພື່ອ configure PR partition. ຫຼັກ IP ນີ້ໃຊ້ JTAG ເພື່ອ configure PR partition. ເພື່ອເພີ່ມ Intel Arria 10 Partial Reconfiguration Controller IP core ກັບໂຄງການ Intel Quartus Prime ຂອງທ່ານ:

- ພິມ Reconfiguration ບາງສ່ວນໃນລາຍການ IP.

- ເພື່ອເປີດໜ້າຕ່າງ IP Parameter Editor Pro, ເລືອກ Intel Arria 10 Partial Reconfiguration Controller IP core ຈາກຫໍສະໝຸດ IP, ແລະຄລິກ Add.

- ໃນກ່ອງໂຕ້ຕອບ New IP variant, ພິມ pr_ip ເປັນ file ຊື່ແລະຄລິກສ້າງ. ໃຊ້ຕົວກໍານົດຄ່າເລີ່ມຕົ້ນສໍາລັບ pr_ip. ຮັບປະກັນວ່າ Enable JTAG ໂໝດດີບັກ ແລະເປີດໃຊ້ຕົວເລືອກອິນເຕີເຟດຄ້າງໄວ້ແມ່ນເປີດຢູ່, ແລະເປີດໃຊ້ຕົວເລືອກອິນເຕີເຟດ slave Avalon-MM ປິດແລ້ວ.

ຮູບທີ 7. Intel Arria 10 Partial Reconfiguration Controller IP Core Parameters

- ກົດ Finish, ແລະອອກຈາກຕົວແກ້ໄຂພາລາມິເຕີໂດຍບໍ່ມີການສ້າງລະບົບ. ຊອບແວ Intel Quartus Prime ສ້າງການປ່ຽນແປງ IP pr_ip.ip file, ແລະເພີ່ມ file ກັບໂຄງການ blinking_led.

ໝາຍເຫດ:

- ຖ້າທ່ານກໍາລັງຄັດລອກ pr_ip.ip file ຈາກໂຟນເດີ hpr, ແກ້ໄຂ blinking_led.qsf ດ້ວຍຕົນເອງ file ເພື່ອປະກອບມີແຖວຕໍ່ໄປນີ້: set_global_assignment -name IP_FILE pr_ip.ip

- ວາງ IP_FILE ການມອບໝາຍຫຼັງຈາກ SDC_FILE ວຽກງານ (jtag.sdc ແລະ blinking_led.sdc) ໃນ blinking_led.qsf ຂອງທ່ານ file. ຄໍາສັ່ງນີ້ຮັບປະກັນການຈໍາກັດທີ່ເຫມາະສົມຂອງຫຼັກ IP ການຕັ້ງຄ່າບາງສ່ວນ.

ໝາຍເຫດ: ເພື່ອກວດຫາໂມງ, SDC file ສໍາລັບ PR IP ຕ້ອງປະຕິບັດຕາມ SDC ໃດໆທີ່ສ້າງໂມງທີ່ຫຼັກ IP ໃຊ້. ທ່ານສ້າງຄວາມສະດວກໃນຄໍາສັ່ງນີ້ໂດຍການຮັບປະກັນ .ip file ສໍາລັບຫຼັກ PR IP ມາຫຼັງຈາກໃດ .ip files ຫຼື SDC files ໃຊ້ເພື່ອສ້າງໂມງເຫຼົ່ານີ້ຢູ່ໃນ QSF file ສໍາລັບການປັບປຸງໂຄງການ Intel Quartus Prime ຂອງທ່ານ. ສໍາລັບຂໍ້ມູນເພີ່ມເຕີມ, ເບິ່ງພາກສ່ວນການຈໍາກັດເວລາໃນບາງສ່ວນ Reconfiguration IP Core User Guide.

ຂໍ້ມູນທີ່ກ່ຽວຂ້ອງ

- ຄູ່ມືການແກ້ໄຂ IP ການປັບຄ່າບາງສ່ວນ

- ສໍາລັບຂໍ້ມູນກ່ຽວກັບພາກສ່ວນ Reconfiguration Region Controller ຫຼັກ IP.

- ຄູ່ມືການປັບຄ່າບາງສ່ວນ IP Core ຜູ້ໃຊ້

- ສໍາລັບຂໍ້ມູນກ່ຽວກັບການຈໍາກັດເວລາ.

ການປັບປຸງການອອກແບບລະດັບສູງສຸດ

ເພື່ອອັບເດດ top.SV file ກັບຕົວຢ່າງ PR_IP:

- ເພື່ອເພີ່ມຕົວຢ່າງ PR_IP ໃຫ້ກັບການອອກແບບລະດັບສູງສຸດ, ຍົກເລີກການສະແດງລະຫັດບລັອກຕໍ່ໄປນີ້ຢູ່ເທິງສຸດ.SV file:

- ເພື່ອບັງຄັບຜອດຜົນຜະລິດເປັນ logic 1 ໃນລະຫວ່າງການປັບຄ່າຄືນໃໝ່, ໃຫ້ໃຊ້ສັນຍານຄວບຄຸມການຢຸດຄ້າງຈາກ PR_IP. ຢ່າງໃດກໍຕາມ, ເພື່ອສັງເກດເຫັນ LED ສືບຕໍ່ກະພິບຈາກພາທິຊັນ PR ຂອງພໍ່ແມ່ໃນຂະນະທີ່ PR ດໍາເນີນໂຄງການພາທິຊັນເດັກນ້ອຍ, ສັນຍານການຄວບຄຸມ freeze ບໍ່ໄດ້ປິດ led_two_on. ໃຫ້ແນ່ໃຈວ່າ pr_led_two_on ແມ່ນໂດຍກົງ

- ເພື່ອມອບໝາຍຕົວຢ່າງຂອງບຸກຄົນຫຼັກເລີ່ມຕົ້ນ (blinking_led), ອັບເດດ top.SV file ກັບບລັອກຂອງລະຫັດຕໍ່ໄປນີ້:

ຮູບທີ 8. ການເຊື່ອມໂຍງຫຼັກ IP ການຕັ້ງຄ່າບາງສ່ວນ

ຂັ້ນຕອນທີ 6: ການກໍານົດບຸກຄົນ

ການອອກແບບການອ້າງອິງນີ້ກໍານົດຫ້າບຸກຄົນແຍກຕ່າງຫາກສໍາລັບການແບ່ງສ່ວນ PR ຂອງພໍ່ແມ່ແລະເດັກ. ເພື່ອກໍານົດແລະລວມເອົາບຸກຄົນໃນໂຄງການຂອງທ່ານ:

- ສ້າງສີ່ SystemVerilog files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv, ແລະ blinking_led_slow.sv ໃນໄດເລກະທໍລີເຮັດວຽກຂອງເຈົ້າສໍາລັບຫ້າຄົນ.

ໝາຍເຫດ: ຖ້າທ່ານສ້າງ SystemVerilog files ຈາກ Intel Quartus Prime Text Editor, ປິດການໃຊ້ງານ Add file ທາງເລືອກໂຄງການໃນປະຈຸບັນ, ເມື່ອບັນທຶກ files.

ຕາຕະລາງ 2. Reference Design Personas

| File ຊື່ | ລາຍລະອຽດ | ລະຫັດ |

| blinking_led_child.sv | ບຸກຄົນເລີ່ມຕົ້ນສໍາລັບການອອກແບບລະດັບເດັກນ້ອຍ |

`ໄລຍະເວລາ 1 ps / 1 ps `default_nettype none module blinking_led_child ( // ໂມງ ໂມງສາຍເຂົ້າ, ສາຍ input [31:0] counter,

// ສັນຍານການຄວບຄຸມສໍາລັບສາຍໄຟ LEDs ອອກ led_three_on

); localparam COUNTER_TAP = 23; reg led_three_on_r;

ມອບໝາຍ led_three_on = led_three_on_r; always_ff @(ໂມງ posedge) ເລີ່ມຕົ້ນ led_three_on_r <= counter[COUNTER_TAP]; ສິ້ນສຸດ

ໂມດູນສຸດທ້າຍ |

| ສືບຕໍ່… | ||

| File ຊື່ | ລາຍລະອຽດ | ລະຫັດ |

| blinking_led_child_slow.sv | ໄດ້

LED_THREE ກະພິບຊ້າລົງ |

`ໄລຍະເວລາ 1 ps / 1 ps `default_nettype none

ໂມດູນ blinking_led_child_slow (

// ໂມງ ໂມງສາຍເຂົ້າ, ສາຍ input [31:0] counter,

// ສັນຍານການຄວບຄຸມສໍາລັບສາຍໄຟ LEDs ອອກ led_three_on );

localparam COUNTER_TAP = 27; reg led_three_on_r;

ມອບໝາຍ led_three_on = led_three_on_r; always_ff @(ໂມງ posedge) ເລີ່ມຕົ້ນ led_three_on_r <= counter[COUNTER_TAP]; ສິ້ນສຸດ

ໂມດູນສຸດທ້າຍ |

| blinking_led_child_empty.sv | ໄດ້

LED_THREE ຍັງເປີດຢູ່ |

`ໄລຍະເວລາ 1 ps / 1 ps `default_nettype none

ໂມດູນ blinking_led_child_empty (

// ໂມງ ໂມງສາຍເຂົ້າ, ສາຍ input [31:0] counter,

// ສັນຍານການຄວບຄຸມສໍາລັບສາຍໄຟ LEDs ອອກ led_three_on

);

// LED ມີການເຄື່ອນໄຫວຕໍ່າ ມອບໝາຍ led_three_on = 1'b0;

ໂມດູນສຸດທ້າຍ |

| blinking_led_slow.sv | LED_TWO

ກະພິບຊ້າລົງ. |

`ໄລຍະເວລາ 1 ps / 1 ps `default_nettype none module blinking_led_slow( // ໂມງ ໂມງສາຍເຂົ້າ, ສາຍ input [31:0] counter,

// ສັນຍານການຄວບຄຸມສໍາລັບສາຍໄຟ LEDs ອອກ led_two_on, ສາຍສົ່ງອອກ led_three_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; ມອບໝາຍ led_two_on = led_two_on_r;

// ເຄົາເຕີ້: always_ff @(ໂມງ posedge) ເລີ່ມ led_two_on_r <= counter[COUNTER_TAP]; ສິ້ນສຸດ

blinking_led_child u_blinking_led_child( .led_three_on (led_three_on), .counter (ເຄົາເຕີ), .ໂມງ (ໂມງ) |

| File ຊື່ | ລາຍລະອຽດ | ລະຫັດ |

| );ndmodule |

ຂັ້ນຕອນທີ 3: ການສ້າງການອອກແບບ Partitions ໃນຫນ້າ 7

ຂັ້ນຕອນທີ 7: ການສ້າງການແກ້ໄຂ

ກະແສການອອກແບບ PR ໃຊ້ຄຸນສົມບັດການແກ້ໄຂໂຄງການໃນຊອບແວ Intel Quartus Prime. ການອອກແບບເບື້ອງຕົ້ນຂອງທ່ານແມ່ນການແກ້ໄຂພື້ນຖານ, ບ່ອນທີ່ທ່ານກໍານົດຂອບເຂດຂອງພາກພື້ນທີ່ຄົງທີ່ແລະພາກພື້ນທີ່ສາມາດກໍານົດຄືນໃຫມ່ໃນ FPGA. ຈາກການປັບປຸງພື້ນຖານ, ທ່ານສ້າງການດັດແກ້ຫຼາຍຄັ້ງ. ການປັບປຸງເຫຼົ່ານີ້ປະກອບດ້ວຍການປະຕິບັດທີ່ແຕກຕ່າງກັນສໍາລັບພາກພື້ນ PR. ຢ່າງໃດກໍ່ຕາມ, ການແກ້ໄຂການປະຕິບັດ PR ທັງຫມົດນໍາໃຊ້ການຈັດວາງລະດັບເທິງດຽວກັນແລະຜົນການກໍານົດເສັ້ນທາງຈາກການປັບປຸງພື້ນຖານ. ເພື່ອລວບລວມການອອກແບບ PR, ທ່ານຕ້ອງສ້າງການປັບປຸງການປະຕິບັດ PR ແລະການປັບປຸງການສັງເຄາະສໍາລັບແຕ່ລະຄົນ. ໃນການອອກແບບການອ້າງອິງນີ້, ນອກເຫນືອຈາກການດັດແກ້ພື້ນຖານ (blinking_led), ສາມບຸກຄົນລະດັບເດັກແລະສອງບຸກຄົນລະດັບພໍ່ແມ່ມີຫ້າການປັບປຸງການສັງເຄາະແຍກຕ່າງຫາກແລະຫ້າການແກ້ໄຂການປະຕິບັດແຍກຕ່າງຫາກ:

ຕາຕະລາງ 3. ການປັບປຸງສໍາລັບບຸກຄົນສອງພໍ່ແມ່ ແລະບຸກຄົນສາມລູກ

| ການທົບທວນສັງເຄາະ | ການປັບປຸງການຈັດຕັ້ງປະຕິບັດ |

| blinking_led_parent, blinking_led_default | ກະພິບ_led_pr_alpha |

| blinking_led_parent, ກະພິບ_led_child_slow | ກະພິບ_led_pr_bravo |

| blinking_led_parent, ກະພິບ_led_child_ເປົ່າ | blinking_led_pr_charlie |

| blinking_led_parent_slow, ກະພິບ_led_child_slow | ກະພິບ_led_pr_delta |

| blinking_led_parent_slow, ກະພິບ_led_child_ເປົ່າ | ກະພິບ_led_pr_emma |

ການສ້າງການແກ້ໄຂການຈັດຕັ້ງປະຕິບັດ

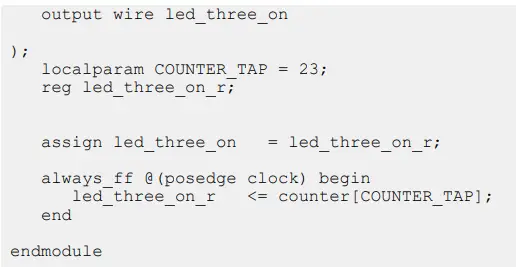

ເພື່ອສ້າງການແກ້ໄຂການປະຕິບັດ PR:

- ເພື່ອເປີດກ່ອງໂຕ້ຕອບ Revisions, ຄລິກ Project ➤ Revisions.

- ເພື່ອສ້າງການແກ້ໄຂໃຫມ່, ຄລິກສອງຄັ້ງ < >.

- ລະບຸຊື່ການແກ້ໄຂເປັນ blinking_led_pr_alpha ແລະເລືອກ blinking_led ໂດຍອີງໃສ່ການດັດແກ້.

- ປິດການທໍາງານການຕັ້ງເປັນທາງເລືອກການແກ້ໄຂໃນປະຈຸບັນແລະຄລິກ OK.

- ເຊັ່ນດຽວກັນ, ສ້າງ blinking_led_pr_bravo, blinking_led_pr_charlie, blinking_led_pr_delta, ແລະ blinking_led_pr_emma ດັດແກ້, ອີງໃສ່ການດັດແກ້ blinking_led.

ໝາຍເຫດ: ຢ່າຕັ້ງການດັດແກ້ຂ້າງເທິງເປັນການປັບປຸງປະຈຸບັນ.

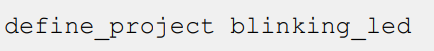

ຮູບ 9. ການສ້າງການດັດແກ້

ການສ້າງການແກ້ໄຂການສັງເຄາະເທົ່ານັ້ນ

ເພື່ອສ້າງການແກ້ໄຂການສັງເຄາະເທົ່ານັ້ນສໍາລັບ personas, ທ່ານຕ້ອງມອບຫມາຍຫນ່ວຍງານລະດັບສູງສຸດແລະ SystemVerilog ທີ່ສອດຄ້ອງກັນ. file ສໍາລັບແຕ່ລະບຸກຄົນ:

- ໃນຊອບແວ Intel Quartus Prime, ຄລິກ Project ➤ Revisions.

- ສ້າງການດັດແກ້ blinking_led_default ໂດຍອີງໃສ່ການດັດແກ້ blinking_led. ຢ່າຕັ້ງການດັດແກ້ນີ້ເປັນການປັບປຸງປະຈຸບັນ.

- ແກ້ໄຂ blinking_led_default.qsf file ເພື່ອລວມເອົາວຽກຕໍ່ໄປນີ້:

set_global_assignment -name TOP_LEVEL_ENTITY ກະພິບ_led_child

set_global_assignment -name SYSTEMVERILOG_FILE - ເຊັ່ນດຽວກັນ, ສ້າງ blinking_led_child_slow, blinking_led_child_empty, blinking_led_parent, ແລະ blinking_led_parent_slow ການແກ້ໄຂໂດຍອີງໃສ່ການທົບທວນ blinking_led. ຢ່າຕັ້ງການດັດແກ້ເຫຼົ່ານີ້ເປັນການແກ້ໄຂໃນປະຈຸບັນ.

- ອັບເດດ blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, ແລະ blinking_led_parent_slow.qsf files ກັບທີ່ສອດຄ້ອງກັນຂອງພວກເຂົາ

TOP_LEVEL_ENTITY ແລະ SYSTEMVERILOG_FILE ການມອບໝາຍ:

- ເພື່ອຫຼີກເວັ້ນການຜິດພາດການສັງເຄາະ, ໃຫ້ແນ່ໃຈວ່າການດັດແກ້ການສັງເຄາະ files ສໍາລັບການແບ່ງປັນເດັກບໍ່ມີການແບ່ງປັນການອອກແບບ, ການມອບຫມາຍ pin, ຫຼື Logic Lock

ການມອບຫມາຍພາກພື້ນ. ນອກຈາກນີ້, ການປັບປຸງການສັງເຄາະ files ສໍາລັບພາທິຊັນພໍ່ແມ່ຈະຕ້ອງມີພຽງແຕ່ການກໍານົດການແບ່ງປັນການອອກແບບສໍາລັບພາທິຊັນເດັກນ້ອຍທີ່ສອດຄ້ອງກັນ. ເອົາການມອບໝາຍເຫຼົ່ານີ້ອອກ, ຖ້າມີ, ໃນ blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, ແລະ blinking_led_parent_slow.pdf files

- ລວມເອົາວຽກຕໍ່ໄປນີ້ຢູ່ໃນ blinking_led_parent.qsf ແລະ blinking_led_parent_slow.qsf files:

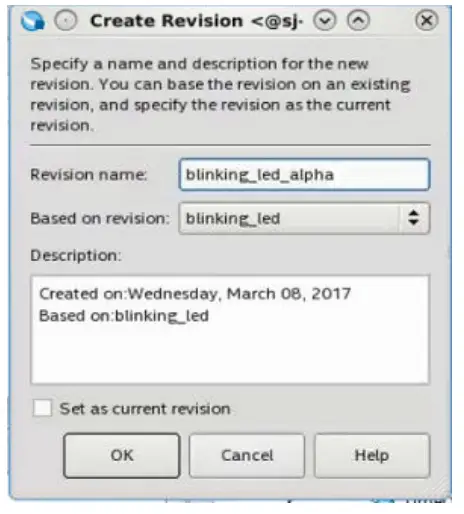

- ກວດສອບວ່າ blinking_led.qpf file ປະກອບມີການດັດແກ້ຕໍ່ໄປນີ້, ໂດຍບໍ່ມີຄໍາສັ່ງໂດຍສະເພາະ:

- ໝາຍເຫດ: ຖ້າທ່ານກໍາລັງຄັດລອກການດັດແກ້ files ຈາກໂຟນເດີ hpr, ປັບປຸງ blinking_led.qpf ດ້ວຍຕົນເອງ file ກັບເສັ້ນຂ້າງເທິງຂອງລະຫັດ.

ການກໍານົດປະເພດການແກ້ໄຂ

ທ່ານຕ້ອງກໍານົດປະເພດການແກ້ໄຂສໍາລັບແຕ່ລະສະບັບຂອງທ່ານ. ມີສາມປະເພດການແກ້ໄຂ:

- Reconfiguration ບາງສ່ວນ – ຖານ

- ການປັບຕັ້ງຄ່າບາງສ່ວນ – ການສັງເຄາະບຸກຄົນ

- ການປັບຕັ້ງຄ່າບາງສ່ວນ - ການຈັດຕັ້ງປະຕິບັດບຸກຄົນ

- ຕາຕະລາງຕໍ່ໄປນີ້ລາຍຊື່ການມອບຫມາຍປະເພດການແກ້ໄຂສໍາລັບແຕ່ລະການແກ້ໄຂ:

ຕາຕະລາງ 4. ປະເພດການແກ້ໄຂ

| ຊື່ການແກ້ໄຂ | ປະເພດການແກ້ໄຂ |

| blinking_led.qsf | Reconfiguration ບາງສ່ວນ – ຖານ |

| blinking_led_default.qsf | ການປັບຕັ້ງຄ່າບາງສ່ວນ – ການສັງເຄາະບຸກຄົນ |

| blinking_led_child_empty.qsf | ການປັບຕັ້ງຄ່າບາງສ່ວນ – ການສັງເຄາະບຸກຄົນ |

| blinking_led_child_slow.qsf | ການປັບຕັ້ງຄ່າບາງສ່ວນ – ການສັງເຄາະບຸກຄົນ |

| blinking_led_parent.qsf | ການປັບຕັ້ງຄ່າບາງສ່ວນ – ການສັງເຄາະບຸກຄົນ |

| blinking_led_parent_slow.qsf | ການປັບຕັ້ງຄ່າບາງສ່ວນ – ການສັງເຄາະບຸກຄົນ |

| blinking_led_pr_alpha.qsf | ການປັບຕັ້ງຄ່າບາງສ່ວນ - ການຈັດຕັ້ງປະຕິບັດບຸກຄົນ |

| blinking_led_pr_bravo.qsf | ການປັບຕັ້ງຄ່າບາງສ່ວນ - ການຈັດຕັ້ງປະຕິບັດບຸກຄົນ |

| blinking_led_pr_charlie.qsf | ການປັບຕັ້ງຄ່າບາງສ່ວນ - ການຈັດຕັ້ງປະຕິບັດບຸກຄົນ |

| blinking_led_pr_delta.qsf | ການປັບຕັ້ງຄ່າບາງສ່ວນ - ການຈັດຕັ້ງປະຕິບັດບຸກຄົນ |

| ກະພິບ_led_pr_emma.qsf | ການປັບຕັ້ງຄ່າບາງສ່ວນ - ການຈັດຕັ້ງປະຕິບັດບຸກຄົນ |

- ຄລິກໂຄງການ ➤ ການປັບປຸງ. ກ່ອງໂຕ້ຕອບການດັດແກ້ຈະປາກົດຂຶ້ນ.

- ເລືອກ blinking_led ໃນຖັນ Revision Name, ແລະຄລິກ Set Current.

- ກົດສະຫມັກ. ການດັດແກ້ blinking_led ເປີດ.

- ເພື່ອກໍານົດປະເພດການແກ້ໄຂສໍາລັບ blinking_led, ຄລິກ Assignments ➤ Settings ➤ General.

- ເລືອກປະເພດການແກ້ໄຂເປັນບາງສ່ວນການປັບຕັ້ງຄ່າ – ຖານ.

- ເຊັ່ນດຽວກັນ, ກໍານົດປະເພດການແກ້ໄຂສໍາລັບການດັດແກ້ອື່ນໆສິບ, ດັ່ງທີ່ໄດ້ລະບຸໄວ້ໃນຕາຕະລາງຂ້າງເທິງ.

- ໝາຍເຫດ: ທ່ານຕ້ອງຕັ້ງແຕ່ລະການແກ້ໄຂເປັນການແກ້ໄຂປະຈຸບັນກ່ອນທີ່ຈະກໍານົດປະເພດການແກ້ໄຂ. ກວດສອບວ່າແຕ່ລະ .qsf file ປະກອບດ້ວຍການມອບຫມາຍດັ່ງຕໍ່ໄປນີ້:

- ໝາຍເຫດ: ເພີ່ມການຕັ້ງຄ່າສະເພາະ Fitter ທີ່ທ່ານຕ້ອງການໃຊ້ໃນການປະຕິບັດ PR ລວບລວມກັບການແກ້ໄຂການປະຕິບັດ persona. ການຕັ້ງຄ່າສະເພາະ Fitter ມີຜົນກະທົບຕໍ່ຄວາມພໍດີຂອງບຸກຄົນ, ແຕ່ບໍ່ມີຜົນຕໍ່ພາກພື້ນທີ່ນໍາເຂົ້າມາ. ນອກນັ້ນທ່ານຍັງສາມາດເພີ່ມການຕັ້ງຄ່າການສັງເຄາະສະເພາະໃດນຶ່ງໃຫ້ກັບການແກ້ໄຂການສັງເຄາະສ່ວນບຸກຄົນ.

ສ້າງການດັດແກ້ສໍາລັບບຸກຄົນ

ຂັ້ນຕອນທີ 8: ກໍາລັງສ້າງ Script Flow Reconfiguration Partial Hierarchical

ເພື່ອສ້າງສະຄຣິບກະແສການກຳນົດຄ່າບາງສ່ວນຕາມລຳດັບ:

- ຈາກແກະຄໍາສັ່ງ Intel Quartus Prime, ສ້າງແມ່ແບບການໄຫຼໂດຍການແລ່ນຄໍາສັ່ງຕໍ່ໄປນີ້:

- Intel Quartus Prime ສ້າງ a10_hier_partial_reconfig/flow.tcl file.

- ປ່ຽນຊື່ທີ່ສ້າງຂຶ້ນ a10_hier_partial_reconfig/setup.tcl.exampໄປທີ່ a10_hier_partial_reconfig/setup.tcl, ແລະແກ້ໄຂສະຄຣິບເພື່ອລະບຸລາຍລະອຽດໂຄງການປັບຄ່າບາງສ່ວນຂອງທ່ານ:

a. ເພື່ອກໍານົດຊື່ຂອງໂຄງການ, ປັບປຸງແຖວຕໍ່ໄປນີ້: b. ເພື່ອກໍານົດການແກ້ໄຂພື້ນຖານ, ປັບປຸງເສັ້ນຕໍ່ໄປນີ້:

b. ເພື່ອກໍານົດການແກ້ໄຂພື້ນຖານ, ປັບປຸງເສັ້ນຕໍ່ໄປນີ້:

- ເພື່ອກໍານົດແຕ່ລະການແກ້ໄຂການປະຕິບັດການປັບຄ່າບາງສ່ວນ, ພ້ອມກັບຊື່ພາທິຊັນ PR ແລະການແກ້ໄຂແຫຼ່ງທີ່ປະຕິບັດການດັດແກ້, ປັບປຸງສາຍຕໍ່ໄປນີ້:

ໝາຍເຫດ: ໂຄງການດັດແກ້ທັງໝົດຕ້ອງຢູ່ໃນໄດເລກະທໍລີດຽວກັນກັບ blinking_led.qpf. ຖ້າບໍ່ດັ່ງນັ້ນ, ປັບປຸງສະຄິບໄຫຼຕາມຄວາມເຫມາະສົມ.

ຂັ້ນຕອນທີ 9: ແລ່ນສະຄຣິບໂຟລການປັບຕັ້ງຄ່າສ່ວນລຳດັບຊັ້ນສູງ

ເພື່ອແລ່ນສະຄຣິບກະແສການກຳນົດຄ່າບາງສ່ວນແບບລຳດັບ:

- ຄລິກເຄື່ອງມື ➤ Tcl Scripts. ກ່ອງໂຕ້ຕອບ Tcl Scripts ປາກົດຂຶ້ນ.

- ກົດ Add to Project, ຊອກຫາ ແລະເລືອກ a10_hier_partial_reconfig/flow.tcl.

- ເລືອກ a10_hier_partial_reconfig/flow.tcl ໃນແຖບຫ້ອງສະໝຸດ, ແລະຄລິກ Run.

script ນີ້ດໍາເນີນການສັງເຄາະສໍາລັບສາມ personas. Intel Quartus Prime ສ້າງ SRAM Object File (.sof), ວັດຖຸ SRAM ທີ່ໜ້າກາກບາງສ່ວນ File (.pmsf), ແລະໄບນາຣີດິບ File (.rbf) ສໍາລັບແຕ່ລະບຸກຄົນ.

ໝາຍເຫດ: ເພື່ອແລ່ນສະຄຣິບຈາກແຜ່ນຄຳສັ່ງ Intel Quartus Prime, ໃຫ້ພິມຄຳສັ່ງຕໍ່ໄປນີ້:

- ລວບລວມການອອກແບບການປັບຄ່າບາງສ່ວນ

- ການໃຊ້ Partial Reconfiguration Flow Script

- ການຕັ້ງຄ່າ Partial Reconfiguration Flow Script

- ສ້າງໂຄງການ Files

ຂັ້ນຕອນທີ 10: ການຂຽນໂປລແກລມຄະນະກໍາມະການ

ກ່ອນທີ່ທ່ານຈະເລີ່ມຕົ້ນ:

- ເຊື່ອມຕໍ່ການສະຫນອງພະລັງງານກັບກະດານພັດທະນາ Intel Arria 10 SoC.

- ເຊື່ອມຕໍ່ສາຍ USB Blaster ລະຫວ່າງພອດ USB ຂອງ PC ແລະພອດ USB Blaster ຢູ່ໃນກະດານພັດທະນາ.

ເພື່ອດໍາເນີນການອອກແບບໃນກະດານພັດທະນາ Intel Arria 10 SoC:

- ເປີດຊອບແວ Intel Quartus Prime ແລະຄລິກ Tools ➤ Programmer.

- ໃນ Programmer, ຄລິກ Hardware Setup ແລະເລືອກ USB-Blaster.

- ຄລິກ Auto Detect ແລະເລືອກອຸປະກອນ, 10AS066N3.

- ກົດ OK. ຊອບແວ Intel Quartus Prime ກວດພົບ ແລະອັບເດດ Programmer ດ້ວຍຊິບ FPGA ສາມຊິບຢູ່ໃນກະດານ.

- ເລືອກອຸປະກອນ 10AS066N3, ຄລິກປ່ຽນ File ແລະໂຫຼດ blinking_led_pr_alpha.sof file.

- ເປີດໃຊ້ Program/Configure ສໍາລັບ blinking_led_pr_alpha.sof file.

- ກົດ Start ແລະລໍຖ້າສໍາລັບແຖບຄວາມຄືບຫນ້າເພື່ອບັນລຸ 100%.

- ສັງເກດເຫັນໄຟ LEDs ໃນກະດານກະພິບໃນຄວາມຖີ່ດຽວກັນກັບການອອກແບບຮາບພຽງຢູ່ຕົ້ນສະບັບ.

- ເພື່ອດໍາເນີນໂຄງການພຽງແຕ່ພາກພື້ນ PR ຂອງເດັກນ້ອຍ, ຄລິກຂວາທີ່ blinking_led_pr_alpha.sof file ໃນ Programmer ແລະກົດ Add PR Programming File.

- ເລືອກ blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file.

- ປິດໃຊ້ງານໂປຣແກຣມ/ກຳນົດຄ່າສຳລັບ blinking_led_pr_alpha.sof file.

- ເປີດໃຊ້ Program/Configure ສໍາລັບ blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf file ແລະກົດ Start. ຢູ່ເທິງກະດານ, ໃຫ້ສັງເກດ LED[0] ແລະ LED[1] ສືບຕໍ່ກະພິບ. ເມື່ອແຖບຄວາມຄືບໜ້າຮອດ 100%, LED[2] ກະພິບໃນອັດຕາດຽວກັນ, ແລະ LED[3] ກະພິບຊ້າລົງ.

- ເພື່ອຂຽນໂປຣແກຣມທັງສອງພາກພື້ນ PR ຂອງພໍ່ແມ່ ແລະລູກ, ໃຫ້ຄລິກຂວາທີ່ .rbf file ໃນ Programmer ແລະກົດ Change PR Programing File.

- ເລືອກ blinking_led_pr_delta.pr_parent_partition.rbf file.

- ກົດເລີ່ມຕົ້ນ. ຢູ່ເທິງກະດານ, ສັງເກດເຫັນວ່າ LED[0] ແລະ LED[1] ສືບຕໍ່ກະພິບ. ເມື່ອແຖບຄວາມຄືບໜ້າໄປຮອດ 100%, ທັງ LED[2] ແລະ LED[3] ກະພິບຊ້າລົງ.

- ເຮັດຊ້ໍາຂັ້ນຕອນຂ້າງເທິງເພື່ອດໍາເນີນໂຄງການຄືນໃຫມ່ແບບເຄື່ອນໄຫວພຽງແຕ່ພາກພື້ນ PR ຂອງເດັກ, ຫຼືທັງສອງພາກພື້ນ PR ຂອງພໍ່ແມ່ແລະເດັກພ້ອມກັນ.

ຮູບທີ 10. ການຂຽນໂປຣແກຣມຂອງ Intel Arria 10 SoC Development Board

ການປັບປຸງບຸກຄົນທີ່ມີຢູ່ແລ້ວ

- ທ່ານສາມາດປ່ຽນແປງບຸກຄົນທີ່ມີຢູ່ແລ້ວ, ເຖິງແມ່ນວ່າຫຼັງຈາກການສັງລວມການແກ້ໄຂພື້ນຖານຢ່າງເຕັມທີ່.

- ຕົວຢ່າງample, ເພື່ອເຮັດໃຫ້ກະພິບ_led_child_slow persona ກະພິບຊ້າລົງ:

- ໃນ blinking_led_child_slow.sv file, ແກ້ໄຂພາລາມິເຕີ COUNTER_TAP ຈາກ 27 ຫາ 28.

- ເພື່ອສັງລວມຄືນໃຫມ່ແລະປະຕິບັດບຸກຄົນນີ້ຄືນໃຫມ່, ທ່ານຕ້ອງລວບລວມການດັດແກ້ທັງຫມົດທີ່ສັງເຄາະເທົ່ານັ້ນແລະການປັບປຸງການປະຕິບັດທີ່ໄດ້ຮັບຜົນກະທົບຈາກການປ່ຽນແປງ. ແກ້ໄຂສະຄຣິບ setup.tcl ເພື່ອປະກອບມີແຖວຕໍ່ໄປນີ້:

ໝາຍເຫດ: ເມື່ອກໍານົດ pr_parent_parition ສໍາລັບການດັດແກ້ blinking_led_pr_delta, ທ່ານນໍາເຂົ້າຮູບສຸດທ້າຍຂອງບຸກຄົນນັ້ນເພື່ອປະຕິບັດ. ດັ່ງນັ້ນ, ການປະຕິບັດເຫດຜົນຂອງການແບ່ງປັນພໍ່ແມ່ຍັງຄົງຢູ່ຄືກັນ, ໃນຂະນະທີ່ປັບປຸງແລະປະຕິບັດການແບ່ງສ່ວນລູກທີ່ສອດຄ້ອງກັນ.

ໝາຍເຫດ: ເມື່ອກໍານົດ pr_parent_parition ສໍາລັບການດັດແກ້ blinking_led_pr_delta, ທ່ານນໍາເຂົ້າຮູບສຸດທ້າຍຂອງບຸກຄົນນັ້ນເພື່ອປະຕິບັດ. ດັ່ງນັ້ນ, ການປະຕິບັດເຫດຜົນຂອງການແບ່ງປັນພໍ່ແມ່ຍັງຄົງຢູ່ຄືກັນ, ໃນຂະນະທີ່ປັບປຸງແລະປະຕິບັດການແບ່ງສ່ວນລູກທີ່ສອດຄ້ອງກັນ. ຄໍາສັ່ງນີ້ re-synthesizes blinking_led_child_slow synthesis revision, ແລະຫຼັງຈາກນັ້ນດໍາເນີນການ PR ປະຕິບັດ compile ໂດຍໃຊ້ blinking_led_pr_bravo.

ຄໍາສັ່ງນີ້ re-synthesizes blinking_led_child_slow synthesis revision, ແລະຫຼັງຈາກນັ້ນດໍາເນີນການ PR ປະຕິບັດ compile ໂດຍໃຊ້ blinking_led_pr_bravo. - ເພື່ອປະຕິບັດການລວບລວມການປັບປຸງການສັງເຄາະເທົ່ານັ້ນ, ດໍາເນີນການຄໍາສັ່ງຕໍ່ໄປນີ້: ຄໍາສັ່ງນີ້ບໍ່ໄດ້ລວບລວມການດັດແກ້ພື້ນຖານ.

- ເພື່ອປະຕິບັດການລວບລວມການແກ້ໄຂການປະຕິບັດ, ດໍາເນີນການຄໍາສັ່ງຕໍ່ໄປນີ້:

- ຄໍາສັ່ງນີ້ບໍ່ໄດ້ລວບລວມການດັດແກ້ພື້ນຖານ.

- ປະຕິບັດຕາມຂັ້ນຕອນໃນຂັ້ນຕອນທີ 10: ການຂຽນໂປຼແກຼມຄະນະກໍາມະການຢູ່ໃນຫນ້າ 22 ເພື່ອດໍາເນີນໂຄງການ RBF ຜົນໄດ້ຮັບ file ເຂົ້າໄປໃນ FPGA.

ໝາຍເຫດ: ເພື່ອຫຼີກເວັ້ນການດໍາເນີນການທັງຫມົດສໍາລັບການດັດແກ້ທຸກຄັ້ງ, ກໍານົດການແກ້ໄຂການສັງເຄາະເທົ່ານັ້ນແລະການແກ້ໄຂການປະຕິບັດໃນສະຄິບ setup.tcl, ແລະດໍາເນີນການສະຄິບ.

ເພີ່ມຄົນໃໝ່ໃສ່ການອອກແບບ

ຫຼັງຈາກລວບລວມການປັບປຸງພື້ນຖານຂອງທ່ານຢ່າງສົມບູນ, ທ່ານຍັງສາມາດເພີ່ມບຸກຄົນໃຫມ່ແລະລວບລວມບຸກຄົນເຫຼົ່ານີ້ເປັນສ່ວນບຸກຄົນ.

ຕົວຢ່າງample, ເພື່ອກໍານົດ persona ເດັກໃຫມ່ສໍາລັບການ blinking_led_parent_slow, ທີ່ປິດ led_three:

- ສຳເນົາ blinking_led_child_empty.sv ໄປໃສ່ blinking_led_chdild_off.sv.

- ໃນ blinking_led_child_off.sv file, ດັດແປງການມອບຫມາຍ, ມອບຫມາຍ led_three_on = 1'b0; ເພື່ອມອບໝາຍ led_three_on = 1'b1; ໃຫ້ແນ່ໃຈວ່າທ່ານປ່ຽນຊື່ໂມດູນຈາກ blinking_led_child_empty ເປັນ blinking_led_child_off.

- ສ້າງການດັດແກ້ສັງເຄາະໃໝ່, blinking_led_child_off, ໂດຍປະຕິບັດຕາມຂັ້ນຕອນໃນການສ້າງການສັງເຄາະເທົ່ານັ້ນໃນໜ້າ 16.

ໝາຍເຫດ: ການແກ້ໄຂ blinking_led_child_off ຈະຕ້ອງໃຊ້ blinking_led_child_off.sv. file. - ສ້າງການແກ້ໄຂການປະຕິບັດໃຫມ່, blinking_led_pr_foxtrot, ໂດຍປະຕິບັດຕາມຂັ້ນຕອນໃນການສ້າງການຈັດຕັ້ງປະຕິບັດການແກ້ໄຂໃນຫນ້າ 15.

- ອັບເດດ a10_hier_partial_reconfig/setup.tcl file ເພື່ອກໍານົດການປະຕິບັດ PR ໃຫມ່:

- ລວບລວມພຽງແຕ່ການສັງເຄາະໃຫມ່ນີ້ແລະການແກ້ໄຂການປະຕິບັດໂດຍການແລ່ນຄໍາສັ່ງຕໍ່ໄປນີ້:

ສໍາລັບຂໍ້ມູນຄົບຖ້ວນກ່ຽວກັບການປັບຕັ້ງຄ່າບາງສ່ວນຕາມລຳດັບສຳລັບອຸປະກອນ Intel Arria 10, ໃຫ້ອ້າງອີງເຖິງການສ້າງການອອກແບບການປັບຕັ້ງຄ່າບາງສ່ວນໃນສະບັບທີ 1 ຂອງປຶ້ມຄູ່ມື Intel Quartus Prime Pro Edition.

ຂໍ້ມູນທີ່ກ່ຽວຂ້ອງ

- ການສ້າງການອອກແບບການປັບຄ່າບາງສ່ວນ

- ການຝຶກອົບຮົມອອນໄລນ໌ Reconfiguration ບາງສ່ວນ

ປະຫວັດການແກ້ໄຂເອກະສານ

ຕາຕະລາງ 5. ປະຫວັດການທົບທວນເອກະສານ

| ສະບັບເອກະສານ | ເວີຊັນຊອບແວ | ການປ່ຽນແປງ |

| 2017.11.06 | 17.1.0 | • ອັບເດດ ຂໍ້ກໍານົດການອອກແບບອ້າງອີງ ພາກສ່ວນທີ່ມີສະບັບຊອບແວ

• ອັບເດດ ການອອກແບບກະສານອ້າງອີງ Flat ໂດຍບໍ່ມີການແບ່ງປັນ PR ຕົວເລກທີ່ມີການປ່ຽນແປງຕັນການອອກແບບ • ອັບເດດ ການອອກແບບອ້າງອີງ Files ຕາຕະລາງທີ່ມີຂໍ້ມູນກ່ຽວກັບ ໂມດູນ Top_counter.sv • ອັບເດດ ການເຊື່ອມໂຍງຫຼັກ IP ການຕັ້ງຄ່າບາງສ່ວນ ຕົວເລກທີ່ມີການປ່ຽນແປງຕັນການອອກແບບ • ອັບເດດຕົວເລກ – ປ່ອງຢ້ຽມແບ່ງສ່ວນອອກແບບ ແລະ Logic Lock Regions Window ເພື່ອສະທ້ອນໃຫ້ເຫັນ GUI ໃຫມ່ • File ການປ່ຽນແປງຊື່ • ແກ້ໄຂຂໍ້ຄວາມ |

| 2017.05.08 | 17.0.0 | ການປ່ອຍເອກະສານເບື້ອງຕົ້ນ |

ເອກະສານ / ຊັບພະຍາກອນ

|

intel AN 805 Hierarchical Partial Reconfiguration of a Design on Arria 10 SoC Development Board [pdf] ຄູ່ມືຜູ້ໃຊ້ AN 805 Hierarchical Reconfiguration ບາງສ່ວນຂອງການອອກແບບໃນ Arria 10 SoC Development Board, AN 805, Hierarchical Partial Reconfiguration of a Design on Arria 10 SoC Development Board, Reconfiguration of a Design on Arria 10 SoC Development Board, Arria 10 SoC Development Board, 10 SoC ຄະນະພັດທະນາ |