Atmel ATF15xx 複雜可程式邏輯元件

規格

- 產品名稱:Atmel ATF15xx 系統內編程

- 型號:ATF15xx

- 類型:複雜可程式邏輯元件(CPLD)

- 程式設計方式:在系統程式設計(ISP)

- 接口:JTAG ISP介面

- 製造商: 愛特梅爾

常見問題解答

Q:我可以將第三方程式設計軟體與 ATF15xx CPLD 一起使用嗎?

A:可以,只要軟體支援程式演算法和JTAG ATF15xx CPLD 所需的指令。

Q:是否可以同時對多個 ATF15xx CPLD 進行程式設計?

答:是的,JTAG ISP 介面支援多元件編程,可同時對多個 CPLD 進行高效編程。

介紹

- Atmel® ATF15xx 複雜可程式邏輯元件 (CPLD) 具有 Logic Doubling® 架構,支援透過 IEEE Std. 1149.1 標準的在系統程式設計 (ISP)。 XNUMX 聯合測試行動小組(JTAG) 介面.此功能增強了程式設計靈活性,並在各個階段提供了好處;產品開發、生產、現場使用。本使用者指南介紹了在支援 ISP 的 ATF15xx CPLD 上實現 ISP 的設計方法和要求,如下所示:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

特點和優點

系統內編程允許在將 ISP 設備安裝到印刷電路板 (PCB) 上後對其進行編程和重新編程。這消除了製造過程中在將裝置安裝到 PCB 上之前在外部裝置編程器上對裝置進行編程所需的額外處理步驟。消除此步驟可降低損壞高引腳數表面貼裝元件的精密引線或在編程流程期間因靜電放電 (ESD) 損壞裝置的可能性。 ISP 還允許用戶進行設計變更和現場升級,而無需從 PCB 上移除 ISP 設備。此外,它還允許使用嵌入式微控制器或線上測試儀對ISP元件進行在系統程式設計操作,並將這些程式設計操作整合到電路板的生產流程中。

系統內程式系統

ATF15xx CPLD 的 ISP 系統的三個基本組件是:

軟體

編程演算法的實作以及J的生成TAG 目標 ISP 設備的指令和資料。它可以是在 PC、嵌入式微控制器或線上測試設備上運行的軟體程式。

介面硬體

ISP 軟體與目標板上的 ISP 設備之間的通訊通道。這可以是 Atmel 或第三方供應商提供的 ISP 下載電纜或程式設計器、線上測試設備,或嵌入式微控制器與 PCB 上的 ISP 設備之間的連接

目標板

J 中包含 ISP 設備的電路板TAG 鏈。這可以是 Atmel 的 ATF15xx CPLD 開發/編程器板,也可以是具有適當 J 的客製化設計電路板。TAG 與介面硬體的連接。

除了這三個組件之外,JEDEC file 對 ATF15xx CPLD 進行編程是必需的。本次 JEDEC file 可以透過編譯設計來創建 file 使用支援 ATF15xx CPLD 的開發軟體,例如 Atmel WinCUPL 和 Atmel ProChip Designer。 Atmel 還提供了一個轉換器軟體實用程式 POF2JED.exe,用於轉換輸出 file 從競爭對手的程式設計格式到 JEDEC file 與 ATF15xx CPLD 相容。有關此實用程式的更多信息,請參閱 Atmel 應用說明“ATF15xx 產品系列轉換”(可在 Atmel 上找到) web地點。 JEDEC 之後 file是為所有 ATF15xx CPLD 創建的,它們可以在目標板上進行編程。 ATF15xx CPLD 可透過以下系統內程式系統進行程式設計:

- ATF15xx 在系統程式系統

- 嵌入式微控制器

- 線上測試儀

Atmel ATF15xx 系統內程式系統

對於 ATF15xx CPLD 的系統內編程,Atmel 提供 ISP 軟體、下載電纜和開發/編程器套件,以下各節將介紹此內容。

網路服務軟體

Atmel ATF15xx ISP 軟體 ATMISP 是實現 JTAG ATF15xx CPLD 上的系統內程式設計。 ATMISP 在基於 Windows 的主機 PC 上運行,並在目標 ISP 硬體系統上實現 ATF15xx CPLD 的系統內編程或產生串行向量格式 (.SVF) file 由自動測試設備 (ATE) 用於對目標系統上的 ATF15xx CPLD 進行程式設計。 ATMISP 首先從用戶處獲取有關 J 的所有必要信息TAG 目標系統中的設備鏈。然後它執行適當的 JTAG J 上的 ISP 指令TAG 根據 J 目標系統中的設備鏈TAG 使用者透過PC的USB或LPT連接埠指定的設備鏈資訊。有關 Atmel ATMISP 軟體的更多信息,請訪問: www.atmel.com/tools/ATMISP.aspx.

ISP下載線

Atmel ATF15xx 基於 USB 的 ISP 下載電纜 ATDH1150USB,一側連接至主機的標準 USB 端口,另一側連接至 JTAG 另一側目標電路板的標頭。它傳輸 JTAG 主機PC上執行的ATMISP所產生的指令和資料傳送到目標電路板上的ISP設備。有關 ATDH1150USB 電纜的更多信息,請訪問 www.atmel.com/tools/ATDH1150USB.aspx.

開發/程式設計師

Atmel ATF15xx 開發/程式設計器套件 ATF15xx-DK3-U 是一個完整的開發系統和 ATF15xx CPLD 的 ISP 程式設計器。該套件為設計人員提供了一種非常快速、簡單的方法來開發原型並使用 ATF15xx ISP CPLD 評估新設計。由於提供了不同的插座轉接器板來支援 ATF15xx CPLD 中提供的大多數封裝類型,因此該套件可用作 ISP 編程器,透過 J 介面對大多數可用封裝類型中的 ATF15xx ISP CPLD 進行編程。TAG 介面.有關 Atmel ATF15xx-DK3-U 套件的更多信息,請訪問: www.atmel.com/tools/ATF15XX-DK3-U.aspx.

嵌入式微控制器系統

編程演算法和JTAG ATF15xx CPLD 的指令可在微控制器或微處理器中實現,然後可用於對目標板上的 ATF15xx CPLD 進行程式設計。一種可能的方法是提取所有相關的 JTAG 協議資訊(即 JTAG 指令和資料)來自SVF file 由 ATMISP 軟體生成,然後使用此資訊來實現微控制器或微處理器的程式碼,以產生 JTAG J 中 ISP 設備的訊號TAG 鏈。這種方法最適合已經具有嵌入式微控制器或微處理器的系統,且無需使用外部系統內程式軟體和硬體工具。

線上測試系統

ATF15xx CPLD 可透過 J 在目標電路板上進行編程TAG 使用線上測試器測試電路板時的介面。一般來說,SVF file 由 ATMISP 產生的應包含所有相關的 JTAG 線上測試儀對目標電路板上的 ATF15xx CPLD 進行程式設計所需的系統內程式資訊。這種方法允許將程式設計步驟整合到測試中tage 生產流程。

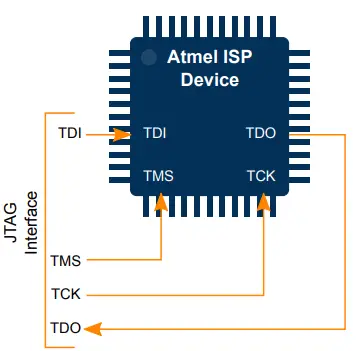

JTAG ISP介面

ATF15xx CPLD 的 ISP 使用 IEEE 1149.1 標準實作。 JTAG 介面.此介面可用於擦除、編程和驗證 ATF15xx CPLD。 JTAG 接口是一個串行接口,由 TCK、TMS、TDI 和 TDO 信號和 JTAG 測試存取連接埠 (TAP) 控制器。 TCK 腳位是 J 的時脈輸入TAG TAP 控制器並移入/移出 JTAG 指令和數據。 TDI 引腳是串列資料輸入。它用於將程式指令和資料轉移到 ISP 設備中。 TDO 引腳是串列資料輸出。它用於從 ISP 設備移出資料。 TMS 引腳是模式選擇引腳。它控制 J 的狀態TAG TAP 控制器。 JTAG ISP 目標板上 ATF15xx CPLD 的介面接腳必須通常透過 10 接腳接頭連接到 ISP 介面硬體(即 ISP 下載電纜)。 ISP 介面硬體也需要連接到執行 ISP 軟體的主機 PC。 ISP 介面硬體在 ISP 軟體和 ISP 設備之間建立通信,它允許 ISP 軟體將程式指令和資料從主機 PC 傳輸到 ATF15xx CPLD。帶有 J 的 ATF15xx CPLDTAG 啟用的功能完全 JTAG 相容並支援 J 中指定的所需邊界掃描測試 (BST) 操作TAG 標準。 ATF15xx CPLD 可配置為 J 的一部分TAG BST鏈與其他JTAG 用於系統板線上測試的設備。借助此功能,ATF15xx CPLD 可以與其他 J 一起在電路板上進行測試。TAG- 無需進行釘床測試即可支援的設備。

單設備程式設計

JTAG ISP 介面可設定為對單一 ATF15xx CPLD 進行程式設計。 JTAG 單一設備的配置如下圖所示。當 ATF15xx CPLD 以這種方式配置時,裝置的 TDI 和 TDO 引腳之間會出現一個暫存器。暫存器的大小取決於JTAG 指令寬度和該指令移入的資料。圖2-1 JTAG 裝置

多設備編程

ATF15xx CPLD 可配置為多個 J 菊花鏈的一部分TAG- 支援的設備如下所述,也如下圖所示。

- 連接 J 中每個裝置的 TMS 和 TCK 接腳TAG 連結到 J 的 TMS 和 TCK 引腳TAG 電路板上的介面接頭。

- 將第一個裝置的 TDI 接腳連接到 J 的 TDI 接腳TAG 接口標頭。

- 將第一個裝置的 TDO 接腳連接到下一個裝置的 TDI 接腳。繼續此過程,直到最後一個之外的所有其他都已連接。

- 將最後一個裝置的 TDO 接腳連接到 J 的 TDO 接腳TAG 接口標頭。

圖 2-2 多設備 JTAG 配置

對 J 中的多個裝置進行編程TAG 鏈,使用者必須使用支援此類功能的 ISP 軟體工具。在ISP軟體中,使用者需要指定:

- J 中的設備數量TAG 鏈。

- 設備的零件號碼以及 J 中的位置TAG 鏈。

- JTAG 每個設備的操作。

- 其他 JTAG- 相關信息,例如 JTAG 每個設備的指令寬度。

一旦JTAG 菊花鏈已在 ISP 目標板上和 ISP 軟體中正確設置,J 中的設備TAG 鏈可以同時編程。

設計考慮因素

要在 ATF15xx CPLD 上執行 ISP,J 的資源TAG 必須保留 ATF15xx 中的介面。因此,TMS、TDI、TDO 和 TCK 引腳的四個 I/O 引腳必須保留給 JTAG 且不能用作使用者 I/O。這些引腳的引腳編號取決於所使用的 ATF15xx CPLD 及其封裝類型。請參閱下表以了解引腳排列資訊。 JTAG 標準建議將 J 中每個裝置的 TMS 和 TDI 引腳上拉TAG 鏈。 ATF15xx CPLD 的這些接腳具有內部上拉功能,啟用此功能後,無需外部上拉電阻。此外,JTAG 必須啟用介面功能才能在 ATF15xx CPLD 上執行 ISP。啟用 JTAG 介面需要在編譯 ATF15xx 設計之前選擇特定的 Atmel 裝置類型或選項設定。本指南中概述了 WinCUPL、ProChip Designer 和 POF2JED 的這些過程。預設情況下,所有全新的 ATF15xx CPLD 均隨 JTAG 介面已啟用。一旦邏輯資源為JTAG 保留接口,使用者可以使用 ATMISP 軟體對目標板上的任何 ATF15xx CPLD 進行編程、驗證和擦除。

提示:雖然四JTAG 引腳保留給 JTAG 接口,使用者可以在與這些引腳關聯的巨集單元中實現隱藏邏輯功能。

表 3-1 ATF15xx CPLD JTAG 針號

| JTAG 別針 | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| 經顱磁刺激系統 | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

啟用 JTAG 與 WinCUPL 的介面

要啟用 JTAG 為了與 WinCUPL 接口,需要在編譯設計之前指定適當的 ATF15xx ISP 設備類型。成功編譯設計後,JEDEC file 與 JTAG 產生啟用的介面功能。當這個 JEDEC file 被編程到 ATF15xxCPLD 中,其 JTAG 介面已啟用。使用者還可以透過在 CUPL 設計中包含以下屬性語句來啟用 TDI 和 TMS 內部上拉電阻 file.

- 屬性 ATMEL {TDI_PULLUP = ON};

- 屬性 ATMEL {TMS_PULLUP = ON};

注意:如果 ATF15xx ISP 裝置類型用於使用 J 的設計TAG 介面引腳作為邏輯 I/O 引腳,WinCUPL 會產生錯誤。

以下步驟討論如何在 WinCUPL 中開啟現有設計、指定裝置類型並編譯設計。

- 在 WinCUPL 主選單上,選擇 File > 開啟。選擇 CUPL (.pld) 來源 file 從適當的工作目錄。

- 選擇「確定」開啟 PLD 來源 file.

- 在 WinCUPL 主選單上,選擇 File > 保存。這會保存對來源所做的更改 file.

- 在主選單上,選擇選項 > 裝置。這將開啟“裝置選擇”對話框。

- 選擇適當的 ATF15xx ISP 設備。請參閱下表,以了解 WinCUPL 支援的所有 ATF15xx 設備類型的清單。

- 選擇“確定”關閉設備選擇選單。

- 注意:另一種方法是從下表中選擇適當的 ATF15xx 設備類型並將其包含在 CUPL 原始碼的標頭部分中 file.

- 在 WinCUPL 主選單上,選擇「執行」>「裝置相關編譯」。

- WinCUPL 編譯設計並產生 Atmel 裝置組裝程式。如果設計合適,JEDEC file 是自動建立的。

- 當 JEDEC file 被編程到設備中,JTAG 介面、可選的內部 TMS 和 TDI 上拉電阻以及可選的引腳保持電路已啟用。

筆記:選擇 Atmel ISP 設備類型會自動啟用 JTAG Atmel WinCUPL 執行 Atmel 裝置組裝程式時預設使用的介面。

如果設計阻止為 J 保留資源TAG 如果選擇不使用介面或 ISP,則必須選擇 Atmel 非 ISP 設備類型。請參閱下表以了解設備清單。然後可以使用外部設備編程器對該設備進行重新編程。下表列出了 WinCUPL 的 Atmel ISP 和 Atmel 非 ISP 設備類型。

表 3-2 WinCUPL ATF15xx 設備類型

| 設備名稱 | 封裝類型 | WinCUPL 設備類型 | |

| JTAG 啟用 | JTAG 殘障人士 | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

啟用 JTAG 與 Atmel ProChip Designer 的接口

要啟用 JTAG 與 ProChip Designer 的介面:

- 開啟適當的 ProChip Designer 專案。

- 點選 Device Fitter 下的 Atmel Fitter 按鈕,開啟 Fitter Options 視窗。

- 選擇全域設備選項卡,然後選取 JTAG 連接埠盒。也可以透過勾選 TDI Pullup 和 TMS Pullup 方塊來啟用 TMS 和 TDI 內部上拉電阻。這些複選框如下圖所示。

圖 3-1 ProChip Designer 組裝選項使用者介面

啟用 JTAG 與 POF2JED 接口

在 POF2JED 中,JTAG 模式選項可以設定為自動,讓 POF2JED 確定 JTAG 應啟用或停用 ATF15xx 中的功能,這取決於 J 是否TAG 在競爭對手的 CPLD 中得到支援。打開 JTAG 在 ATF15xx CPLD 中,無論 JTAG 無論競爭對手的 CPLD 是否支持,JTAG 模式選項應設定為“開”。當 JTAG 在 ATF15xx 中啟用後,可以透過檢查 Enable 來啟用 TDI 和 TMS 內部上拉電阻。

POF2JED 中的 TDI_PULLUP 和啟用 TMS_PULLUP 框。見下圖。

圖 3-2 POF2JED 使用者介面

指南和建議

注意力:在 ATF15xx CPLD 上執行 ISP 操作時應特別注意本節。本節討論一些 JTAG 應充分注意的 ISP 指南、資訊和建議。

- 確保 JTAG J 中所有設備的端口TAG 鏈已啟用。

- 對於 ATF15xx CPLD,JTAG 如果裝置空白/擦除或用 J 編程,則連接埠啟用TAG 已啟用。

- 所有 Atmel ATF15xx 裝置出廠時均處於空白/已擦除狀態;因此,JTAG 連接埠已為所有全新設備啟用並準備好供 ISP 使用。

- 帶 J 的 ATF15xx 設備TAG 停用需要使用非 ISP 裝置程式設計器擦除以重新啟用 JTAG 港口。

- 確保正確的 VCC 卷tage 應用於 J 中的每個設備TAG 鏈。

- 採用15-PLCC、84-TQFP 和100-PQFP 封裝類型的ATF100xxAS/ASL CPLD:VCCINT 必須介於4.5V 和5.5V 之間,而VCCIO 可以介於3.0V 和3.6V 或4.5V 和5.5V 之間。

- 15-PLCC 和 44-TQFP 封裝類型的 ATF44xxAS/ASL CPLD:VCC 必須在 4.5V 至 5.5V 之間。

- ATF15xxASV/ASVL CPLD:VCC(VCCIO 和 VCCINT)必須介於 3.0V 至 3.6V 之間。

- J 中裝置的 VCCTAG 鏈條必須得到適當的調節和過濾。

- 對於大多數應用中使用的 ATF15xx CPLD,建議為每個 VCC/GND 對使用一個 0.22μF 去耦電容器。

- 建議 J 中的所有設備使用公共接地。TAG 鍊和 JTAG 介面硬體(即ATDH1150USB ISP 下載電纜)。

- 建議避免長(不超過五個設備)JTAG 鏈。

- 如果長JTAG 鍊是必要的,每五個設備後緩衝 TMS 和 TCK 訊號。優先使用施密特觸發器緩衝器。

- 緩衝器重塑 TMS 和 TCK 訊號的上升和下降時間。

- 需要考慮緩衝區產生的額外延遲。

- 建議在 J 端為 TMS 和 TDI 訊號使用上拉電阻(4.7KΩ 至 10KΩ),為 TCK 訊號使用下拉電阻。TAG 頭,以防止這些訊號在不由介面硬體驅動時浮動。

- TMS 和 TDI 上的選用內部上拉電阻可用於 ATF15xx CPLD。

- 建議終止JTAG J 處的訊號TAG 標頭。

- 有源和無源端接均可;然而,優選被動終止。

- 它減少了由於電纜/PCB 走線長度較長而產生的振鈴。

- 終止對於 TMS 和 TCK 來說最為關鍵。

- 建議 J 中設備的所有輸入和 I/OTAG 鏈,除了 JTAG 當對 ATF15xx CPLD 進行編程時,引腳應處於靜態,以最大限度地減少雜訊。

- 使用 Atmel ATF15xx 開發/編程器板之一時,當更改 VCC 選擇跳線的位置時,必須關閉該板的電源。

- 對於 ATF15xx CPLD,JTAG 當裝置處於引腳控制的掉電模式或「低功耗」裝置休眠時,ISP 可用。

- ISP中斷後設備狀態:

- 如果 ISP 中斷,則無論接腳固定器電路的狀態為何,所有 I/O 接腳都將處於三態。

- 防止部分編程的設備與電路板上的其他設備造成匯流排爭用。

- 在 ISP 編程期間,所有 I/O 引腳均處於以下狀態之一:

- 高阻狀態:

- 當對空白/擦除裝置進行編程時。

- 當裝置在引腳保持器電路停用的情況下重新編程時。

- 防止與電路板上 ATF15xx CPLD 連接的外部設備發生匯流排爭用。

- 弱鎖定到先前的狀態:

- 當已編程的裝置在引腳保持器電路啟用的情況下重新編程時。

- I/O 引腳在 ISP 之前保持先前的邏輯電平。

- 防止 ISP 影響主機板上其他設備的運作。

- 使用多個JTAG 不建議將鏈條放在一塊板上。

- 設備可以在不同的 J 之間交互TAG 鏈。

- 只有當所有設備都在 J 中時,該板才會起作用TAG 鏈已成功編程。

- 如果鏈中至少一個設備的程式設計失敗,而其他 JTAG 鏈已成功編程:

- 由於三態輸出可能有匯流排爭用問題,Atmel 或板上的其他裝置可能會被損壞。

- 系統板的運作狀態未定義;因此,可能會發生不正確的功能操作。

- 在 J 之間插入主動電路TAG 標頭和 JTAG 不建議使用鍊式設備。如果有源電路發生故障,可能會導致編程/驗證問題。

- 混合卷的使用tag設備JTAG 不建議使用鏈條。

- 這些是 JTAG 具有使用不同 VCC 卷的設備的鏈tages 和/或接口 voltages.

- 介面磁碟區tag5.0V 設備的電平(VIL、VIH、VOL、VOH)可能與介面 vol 不相容tag3.0V 裝置的 e 電平。

- 如果 ATMISP 與 J 通訊有問題TAG 設備硬體鏈,嘗試運行自校準或手動校準以降低 J 的頻率TAG 訊號.

- 在編程開始之前,請確保 ATDH1150USB 電纜上的 LED 已開啟且呈綠色。確保ISP下載線能夠與ATMISP軟體正常通訊。

- 確保正確的 VCC 卷tage 適用於 ATDH1150USB 電纜。

- J 中第一個設備使用的 VCCTAG 鏈條必須透過 1150 針 J 的針 4 提供給 ATDH10USB 電纜TAG 標頭。

- 對於具有獨立 VCCINT 和 VCCIO 的 ATF15xx CPLD,VCCIO 應用於 ATDH1150USB 電纜。

訂購資訊

| 訂購代號 | 描述 |

| ATF15xx-DK3-U | CPLD 開發/程式設計器套件(包括 ATF15xxDK3-SAA44 和 ATDH1150USB 或 ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | 用於 DK100 板的 3 針 TQFP 插座適配器板 |

| ATF15xxDK3-SAJ44 | 用於 DK44 板的 3 針 PLCC 插座適配器板 |

| ATF15xxDK3-SAJ84 | 用於 DK84 板的 3 針 PLCC 插座適配器板 |

| ATF15xxDK3-SAA44 | 用於 DK44 板的 3 針 TQFP 插座適配器板 |

| ATDH1150USB | Atmel ATF15xx CPLD 基於 USB 的 JTAG ISP下載線 |

修訂歷史

| 博士。 牧師 | 日期 | 評論 |

| A | 12/2015 | 初始文件發布。 |

聯絡資訊

愛特梅爾公司

- 1600 Technology Drive, 聖何塞, CA 95110 美國

- 電話:(+1)(408) 441.0311

- 女:(+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel 公司。 / 修訂版:Atmel-8968A-CPLD-ATF-ISP_使用者指南-12/2015

Atmel®、Atmel 標誌及其組合、Enabling Unlimited Possibilities® 等是 Atmel Corporation 在美國和其他國家的註冊商標或商標。其他術語和產品名稱可能是其他人的商標。

免責聲明:本文檔中的信息與 Atmel 產品有關。 本文檔或與愛特梅爾產品的銷售有關的任何知識產權均未通過禁止反言或其他方式授予任何明示或暗示的許可。 位於 ATMEL 上的銷售條款和條件中規定的除外 WEB網站、ATMEL 不承擔任何責任,並否認與其產品相關的任何明示、暗示或法定保證,包括但不限於適銷性、特定用途適用性或不侵權的暗示保證。在任何情況下,ATMEL 均不對因使用或無法使用而引起的任何直接、間接、後果性、懲罰性、特殊或附帶損害(包括但不限於損失和利潤損害、業務中斷或資訊遺失)承擔責任。即使ATMEL 已被告知可能發生此類損害,也請使用本文檔。 Atmel 不對本文檔內容的準確性或完整性做出任何陳述或保證,並保留隨時更改規格和產品描述的權利,恕不另行通知。 Atmel 不承諾更新此處包含的資訊。除非另有明確規定,Atmel 產品不適合且不得用於汽車應用。 Atmel 產品無意、授權或保證用作旨在支持或維持生命的應用中的組件。安全關鍵型、軍事和汽車應用免責聲明:Atmel 產品並非為任何應用而設計,也不會用於此類產品的故障將合理預期導致重大人身傷害或死亡的任何應用(「安全關鍵型應用」)應用程式」),未經Atmel 官員的具體書面同意。安全關鍵應用包括但不限於維生裝置和系統、用於核設施和武器系統操作的設備或系統。 Atmel 產品並非設計用於軍事或航空航天應用或環境,除非 Atmel 明確指定為軍用等級。 Atmel 產品並非專為汽車應用而設計或設計用於汽車應用,除非 Atmel 明確指定為汽車級產品。

文件/資源

|

Atmel ATF15xx 複雜可程式邏輯元件 [pdf] 使用者指南 ATF15xx、ATF15xx 複雜可程式邏輯元件、複雜可程式邏輯元件、可程式邏輯元件、邏輯元件、裝置 |