Atmel ATF15xx 복합 프로그래밍 논리 장치

명세서

- 제품 이름: Atmel ATF15xx 시스템 내 프로그래밍

- 모델: ATF15xx

- 유형: 복합 프로그래밍 논리 장치(CPLD)

- 프로그래밍 방식: 인시스템 프로그래밍(ISP)

- 인터페이스: JTAG ISP 인터페이스

- 제조사: Atmel

자주 묻는 질문

질문: ATF15xx CPLD와 함께 타사 프로그래밍 소프트웨어를 사용할 수 있나요?

A: 예, 소프트웨어가 프로그래밍 알고리즘과 J를 지원하는 한 가능합니다.TAG ATF15xx CPLD에 필요한 지침입니다.

질문: 여러 개의 ATF15xx CPLD를 동시에 프로그래밍할 수 있나요?

A: 네, JTAG ISP 인터페이스는 여러 CPLD를 동시에 효율적으로 프로그래밍할 수 있도록 다중 장치 프로그래밍을 지원합니다.

소개

- Logic Doubling® 아키텍처를 갖춘 Atmel® ATF15xx 복합 프로그래머블 논리 장치(CPLD)는 IEEE Std. 1149.1 공동 테스트 작업 그룹(J)을 통해 ISP(시스템 내 프로그래밍)를 지원합니다.TAG) 인터페이스. 이 기능은 프로그래밍 유연성을 향상시키고 다양한 단계(제품 개발, 생산 및 현장 사용)에서 이점을 제공합니다. 이 사용자 가이드는 아래에 나열된 ISP 지원이 있는 ATF15xx CPLD에서 ISP를 구현하기 위한 설계 방법과 요구 사항을 설명합니다.

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

특징 및 이점

시스템 내 프로그래밍은 ISP 장치를 인쇄 회로 기판(PCB)에 장착한 후 프로그래밍하고 재프로그래밍할 수 있게 해줍니다. 이를 통해 PCB에 장착하기 전에 외부 장치 프로그래머에서 장치를 프로그래밍하는 데 필요한 제조 공정의 추가 처리 단계가 없어집니다. 이 단계를 제거하면 프로그래밍 흐름 중에 고핀 카운트 표면 실장 장치의 섬세한 리드가 손상되거나 정전기 방전(ESD)으로 인해 장치가 손상될 가능성이 줄어듭니다. ISP를 사용하면 사용자가 PCB에서 ISP 장치를 제거하지 않고도 설계를 변경하고 현장 업그레이드할 수 있습니다. 또한 임베디드 마이크로컨트롤러나 인서킷 테스터를 사용하여 ISP 장치에서 시스템 내 프로그래밍 작업을 수행하고 이러한 프로그래밍 작업을 회로 기판의 생산 흐름에 통합할 수도 있습니다.

시스템 내 프로그래밍 시스템

ATF15xx CPLD를 위한 ISP 시스템의 세 가지 필수 구성 요소는 다음과 같습니다.

소프트웨어

프로그래밍 알고리즘의 구현 및 J 생성TAG 대상 ISP 장치에 대한 지침 및 데이터. 이는 PC에서 실행되는 소프트웨어 프로그램, 임베디드 마이크로컨트롤러 또는 회로 내 테스트 장비일 수 있습니다.

인터페이스 하드웨어

ISP 소프트웨어와 대상 보드의 ISP 장치 간의 통신 채널. 이는 Atmel 또는 타사 공급업체의 ISP 다운로드 케이블 또는 프로그래머, 회로 내 테스트 장비 또는 PCB의 임베디드 마이크로컨트롤러와 ISP 장치 간의 연결일 수 있습니다.

타겟 보드

J에 ISP 장치가 포함된 회로 기판TAG 체인. 이는 Atmel의 ATF15xx CPLD 개발/프로그래머 보드 또는 적절한 J를 갖춘 맞춤 설계 회로 보드일 수 있습니다.TAG 인터페이스 하드웨어에 대한 연결.

이 세 가지 구성 요소 외에도 JEDEC file ATF15xx CPLD를 프로그래밍하려면 이 JEDEC가 필요합니다. file 디자인을 컴파일하여 생성할 수 있습니다 file Atmel WinCUPL 및 Atmel ProChip Designer와 같은 ATF15xx CPLD를 지원하는 개발 소프트웨어를 사용합니다. Atmel은 또한 출력을 변환하는 POF2JED.exe라는 변환기 소프트웨어 유틸리티를 제공합니다. file 경쟁사의 프로그래밍 형식에서 JEDEC로 file ATF15xx CPLD와 호환됩니다. 이 유틸리티에 대한 자세한 내용은 Atmel에서 제공되는 Atmel 애플리케이션 노트 "ATF15xx 제품군 변환"을 참조하십시오. web사이트. JEDEC 이후 files는 모든 ATF15xx CPLD에 대해 생성되며 대상 보드에서 프로그래밍할 수 있습니다. ATF15xx CPLD는 다음 시스템 내 프로그래밍 시스템에서 프로그래밍할 수 있습니다.

- ATF15xx 시스템 내 프로그래밍 시스템

- 임베디드 마이크로 컨트롤러

- 인서킷 테스터

Atmel ATF15xx 시스템 내 프로그래밍 시스템

ATF15xx CPLD의 시스템 내 프로그래밍을 위해 ISP 소프트웨어, 다운로드 케이블 및 개발/프로그래머 키트를 Atmel에서 구입할 수 있으며, 아래 섹션에 이에 대한 설명이 나와 있습니다.

ISP 소프트웨어

Atmel ATF15xx ISP 소프트웨어인 ATMISP는 J를 구현하는 주요 수단입니다.TAG ATF15xx CPLD에 대한 시스템 내 프로그래밍. ATMISP는 Windows 기반 호스트 PC에서 실행되고 대상 ISP 하드웨어 시스템에서 ATF15xx CPLD의 시스템 내 프로그래밍을 구현하거나 직렬 벡터 형식(.SVF)을 생성합니다. file ATE(자동 테스트 장비)에서 대상 시스템의 ATF15xx CPLD를 프로그래밍하는 데 사용됩니다. ATMISP는 먼저 사용자로부터 J에 대한 모든 필요한 정보를 수집합니다.TAG 대상 시스템의 장치 체인입니다. 그런 다음 적절한 J를 실행합니다.TAG J에 대한 ISP 지침TAG J에 따른 대상 시스템의 장치 체인TAG 사용자가 PC의 USB 또는 LPT 포트를 통해 지정한 장치 체인 정보. Atmel ATMISP 소프트웨어에 대한 자세한 내용은 다음에서 제공됩니다. www.atmel.com/tools/ATMISP.aspx.

ISP 다운로드 케이블

Atmel ATF15xx USB 기반 ISP 다운로드 케이블, ATDH1150USB는 한 쪽은 호스트 컴퓨터의 표준 USB 포트에 연결되고 다른 쪽은 J에 연결됩니다.TAG 반대쪽에 있는 대상 회로 보드의 헤더입니다. J를 전송합니다.TAG 호스트 PC에서 실행되는 ATMISP가 생성한 지침 및 데이터를 대상 회로 보드의 ISP 장치로 전송합니다. ATDH1150USB 케이블에 대한 자세한 내용은 다음에서 확인할 수 있습니다. www.atmel.com/tools/ATDH1150USB.aspx.

개발/프로그래머

Atmel ATF15xx 개발/프로그래머 키트, ATF15xx-DK3-U는 ATF15xx CPLD를 위한 완전한 개발 시스템이자 ISP 프로그래머입니다. 이 키트는 설계자에게 ATF15xx ISP CPLD로 프로토타입을 개발하고 새로운 디자인을 평가하는 매우 빠르고 쉬운 방법을 제공합니다. ATF15xx CPLD에서 제공되는 대부분의 패키지 유형을 지원하는 다양한 소켓 어댑터 보드를 사용할 수 있으므로 이 키트는 J를 통해 사용 가능한 대부분의 패키지 유형에서 ATF15xx ISP CPLD를 프로그래밍하는 ISP 프로그래머로 사용할 수 있습니다.TAG 인터페이스. Atmel ATF15xx-DK3-U 키트에 대한 자세한 내용은 다음에서 제공됩니다. www.atmel.com/tools/ATF15XX-DK3-U.aspx.

임베디드 마이크로컨트롤러 시스템

프로그래밍 알고리즘과 JTAG ATF15xx CPLD에 대한 명령어는 마이크로컨트롤러 또는 마이크로프로세서에 구현할 수 있으며, 이를 사용하여 대상 보드에서 ATF15xx CPLD를 프로그래밍할 수 있습니다. 가능한 방법 중 하나는 모든 관련 J를 추출하는 것입니다.TAG 프로토콜 정보(예: JTAG SVF의 지침 및 데이터 file ATMISP 소프트웨어에서 생성된 다음 이 정보를 사용하여 J를 생성하는 마이크로컨트롤러 또는 마이크로프로세서에 대한 코드를 구현합니다.TAG J의 ISP 장치에 대한 신호TAG 체인. 이 접근 방식은 이미 내장된 마이크로컨트롤러나 마이크로프로세서를 갖춘 시스템에 가장 적합하며, 이를 통해 외부 시스템 내 프로그래밍 소프트웨어와 하드웨어 도구를 사용할 필요가 없습니다.

인서킷 테스트 시스템

ATF15xx CPLD는 J를 통해 대상 회로 기판에 프로그래밍될 수 있습니다.TAG 회로 기판을 인서킷 테스터를 사용하여 테스트하는 동안 인터페이스. 일반적으로 SVF file ATMISP에서 생성된 모든 관련 J를 포함해야 합니다.TAG 인서킷 테스터가 대상 회로 보드에서 ATF15xx CPLD를 프로그래밍하는 데 필요한 인시스템 프로그래밍 정보입니다. 이 접근 방식을 사용하면 프로그래밍 단계를 테스트 s에 통합할 수 있습니다.tag생산 흐름의 e.

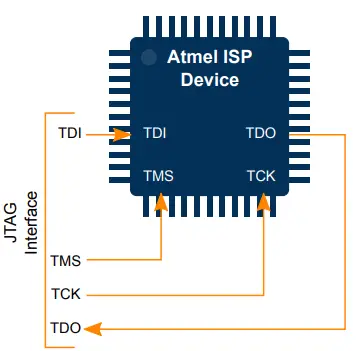

JTAG ISP 인터페이스

ATF15xx CPLD용 ISP는 IEEE 1149.1 Std. J를 사용하여 구현됩니다.TAG 인터페이스. 이 인터페이스는 ATF15xx CPLD를 지우고, 프로그래밍하고, 검증하는 데 사용할 수 있습니다. JTAG 인터페이스는 TCK, TMS, TDI 및 TDO 신호와 J로 구성된 직렬 인터페이스입니다.TAG 테스트 액세스 포트(TAP) 컨트롤러. TCK 핀은 J의 클록 입력입니다.TAG TAP 컨트롤러를 사용하여 J를 안쪽/바깥쪽으로 이동합니다.TAG 명령어 및 데이터. TDI 핀은 직렬 데이터 입력입니다. 프로그래밍 명령어 및 데이터를 ISP 장치로 옮기는 데 사용됩니다. TDO 핀은 직렬 데이터 출력입니다. ISP 장치에서 데이터를 옮기는 데 사용됩니다. TMS 핀은 모드 선택 핀입니다. J의 상태를 제어합니다.TAG TAP 컨트롤러. JTAG ISP 대상 보드의 ATF15xx CPLD의 인터페이스 핀은 일반적으로 10핀 헤더를 통해 ISP 인터페이스 하드웨어(예: ISP 다운로드 케이블)에 연결해야 합니다. ISP 인터페이스 하드웨어도 ISP 소프트웨어를 실행하는 호스트 PC에 연결해야 합니다. ISP 인터페이스 하드웨어는 ISP 소프트웨어와 ISP 장치 간의 통신을 설정하고 ISP 소프트웨어가 호스트 PC에서 ATF15xx CPLD로 프로그래밍 명령어와 데이터를 전송할 수 있도록 합니다. J가 있는 ATF15xx CPLDTAG 기능이 활성화되어 있으면 완전히 J입니다.TAG 호환되며 J에 명시된 필수 BST(경계 주사 테스트) 작업도 지원합니다.TAG 표준. ATF15xx CPLD는 J의 일부로 구성될 수 있습니다.TAG 다른 J와 함께하는 BST 체인TAG 시스템 보드의 회로 내 테스트를 위한 장치입니다. 이 기능을 사용하면 ATF15xx CPLD를 다른 J와 함께 회로 보드에서 테스트할 수 있습니다.TAG-실제 테스트에 의존하지 않고도 지원되는 장치가 있습니다.

단일 장치 프로그래밍

JTAG ISP 인터페이스는 단일 ATF15xx CPLD를 프로그래밍하도록 구성할 수 있습니다. JTAG 단일 장치에 대한 구성은 아래 그림에 나와 있습니다. ATF15xx CPLD가 이런 방식으로 구성되면 장치의 TDI와 TDO 핀 사이에 레지스터가 나타납니다. 레지스터의 크기는 J에 따라 달라집니다.TAG 명령어 폭과 해당 명령어에 대해 이동되는 데이터. 그림 2-1 JTAG 장치

다중 장치 프로그래밍

ATF15xx CPLD는 여러 개의 J 데이지 체인의 일부로 구성될 수 있습니다.TAG-아래에 설명되어 있고 다음 그림에도 표시된 지원 장치입니다.

- J의 각 장치에 대한 TMS 및 TCK 핀을 연결합니다.TAG J의 TMS 및 TCK 핀에 체인을 연결합니다.TAG 회로 기판의 인터페이스 헤더.

- 첫 번째 장치의 TDI 핀을 J의 TDI 핀에 연결합니다.TAG 인터페이스 헤더.

- 첫 번째 장치의 TDO 핀을 다음 장치의 TDI 핀에 연결합니다. 마지막 하나를 제외한 모든 것이 연결될 때까지 이 프로세스를 계속합니다.

- 마지막 장치의 TDO 핀을 J의 TDO 핀에 연결합니다.TAG 인터페이스 헤더.

그림 2-2 다중 장치 JTAG 구성

J에서 여러 장치를 프로그래밍하려면TAG 체인, 사용자는 이러한 기능을 지원하는 ISP 소프트웨어 도구를 사용해야 합니다. ISP 소프트웨어에서 사용자는 다음을 지정해야 합니다.

- J의 장치 수TAG 체인.

- 장치의 부품 번호 및 J 내의 위치TAG 체인.

- JTAG 각 장치에 대한 작업.

- 기타 JTAG-J와 같은 관련 정보TAG 각 장치에 대한 명령어 폭.

J가 한 번TAG ISP 대상 보드와 ISP 소프트웨어에서 데이지 체인이 제대로 설정되어 있으면 J의 장치가TAG 체인도 동시에 프로그래밍이 가능합니다.

디자인 고려 사항

ATF15xx CPLD에서 ISP를 수행하려면 J에 대한 리소스가 필요합니다.TAG ATF15xx의 인터페이스는 예약되어야 합니다. 따라서 TMS, TDI, TDO 및 TCK 핀의 XNUMX개 I/O 핀은 J에 예약되어야 합니다.TAG 사용자 I/O로 사용할 수 없습니다. 이러한 핀의 핀 번호는 사용되는 ATF15xx CPLD와 패키지 유형에 따라 달라집니다. 핀아웃 정보는 아래 표를 참조하십시오. JTAG 표준에서는 J의 각 장치에 대해 TMS 및 TDI 핀을 끌어올릴 것을 권장합니다.TAG 체인. ATF15xx CPLD는 이러한 핀에 대한 내부 풀업 기능을 가지고 있으며, 이를 활성화하면 외부 풀업 저항이 필요 없게 됩니다. 또한 JTAG ATF15xx CPLD에서 ISP를 수행하려면 인터페이스 기능을 활성화해야 합니다. J 활성화TAG 인터페이스는 ATF15xx 설계를 컴파일하기 전에 특정 Atmel 장치 유형이나 옵션 설정을 선택해야 합니다. 이러한 절차는 이 가이드에서 WinCUPL, ProChip Designer 및 POF2JED에 대해 설명합니다. 기본적으로 모든 새로운 ATF15xx CPLD는 JTAG 인터페이스가 활성화되었습니다. J에 대한 논리 리소스가 활성화되면TAG 인터페이스는 예약되어 있으므로 사용자는 ATMISP 소프트웨어를 사용하여 대상 보드의 모든 ATF15xx CPLD를 프로그래밍, 검증 및 지울 수 있습니다.

팁: 네 개의 JTAG 핀은 J에 예약되어 있습니다TAG 인터페이스를 통해 사용자는 이러한 핀과 관련된 매크로셀에 묻힌 논리 기능을 구현할 수 있습니다.

표 3-1 ATF15xx CPLD JTAG 핀 번호

| JTAG 핀 | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| 티디디 | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| 티엠에스 | 7 | 13 | 23 | 15 | 17 |

| 티씨씨 | 26 | 32 | 62 | 62 | 64 |

J 활성화TAG WinCUPL과의 인터페이스

J를 활성화하려면TAG WinCUPL과 인터페이스하려면 설계를 컴파일하기 전에 적절한 ATF15xx ISP 장치 유형을 지정해야 합니다. 설계가 성공적으로 컴파일되면 JEDEC file J와 함께TAG 인터페이스 기능이 활성화되어 생성됩니다. 이 JEDEC file ATF15xxCPLD에 프로그래밍되어 있으며 JTAG 인터페이스가 활성화되었습니다. 사용자는 CUPL 설계에 다음 속성 문을 포함하여 TDI 및 TMS 내부 풀업 저항을 활성화할 수도 있습니다. file.

- 속성 ATMEL {TDI_PULLUP = ON};

- 속성 ATMEL {TMS_PULLUP = ON};

알아채다: J를 사용하는 설계에 ATF15xx ISP 장치 유형이 사용되는 경우TAG 인터페이스 핀을 논리 I/O 핀으로 사용하면 WinCUPL에서 오류가 발생합니다.

다음 단계에서는 WinCUPL에서 기존 디자인을 열고, 장치 유형을 지정하고, 디자인을 컴파일하는 방법을 설명합니다.

- WinCUPL 메인 메뉴에서 다음을 선택하세요. File > 열기. CUPL(.pld) 소스를 선택하세요 file 해당 작업 디렉토리에서.

- PLD 소스를 열려면 확인을 선택하세요 file.

- WinCUPL 메인 메뉴에서 다음을 선택하세요. File > 저장. 이렇게 하면 소스에 대한 변경 사항이 저장됩니다. file.

- 메인 메뉴에서 옵션 > 장치를 선택합니다. 그러면 장치 선택 대화 상자가 열립니다.

- 적절한 ATF15xx ISP 장치를 선택하세요. WinCUPL에서 지원하는 모든 ATF15xx 장치 유형 목록은 다음 표를 참조하세요.

- 확인을 선택하여 장치 선택 메뉴를 닫습니다.

- 참고: 또 다른 방법은 다음 표에서 적절한 ATF15xx 장치 유형을 선택하여 CUPL 소스의 헤더 섹션에 포함하는 것입니다. file.

- WinCUPL 메인 메뉴에서 실행>장치 종속 컴파일을 선택합니다.

- WinCUPL은 설계를 컴파일하고 Atmel 장치 피터를 생성합니다. 설계가 맞으면 JEDEC file 자동으로 생성됩니다.

- JEDEC가 file 장치에 프로그래밍되어 있습니다, JTAG 인터페이스, 옵션 내부 TMS 및 TDI 풀업, 옵션 핀 키퍼 회로가 활성화됩니다.

메모: Atmel ISP 장치 유형을 선택하면 J가 자동으로 활성화됩니다.TAG Atmel WinCUPL이 Atmel 디바이스 피터를 실행할 때 기본적으로 사용되는 인터페이스입니다.

디자인이 J에 대한 리소스 예약을 방해하는 경우TAG 인터페이스 또는 ISP가 선택적으로 사용되지 않는 경우 Atmel 비 ISP 장치 유형을 선택해야 합니다. 장치 목록은 아래 표를 참조하세요. 그런 다음 외부 장치 프로그래머를 사용하여 장치를 다시 프로그래밍할 수 있습니다. 아래 표에는 WinCUPL에 대한 Atmel ISP 및 Atmel 비 ISP 장치 유형이 나열되어 있습니다.

표 3-2 WinCUPL ATF15xx 장치 유형

| 장치 이름 | 패키지 유형 | WinCUPL 장치 유형 | |

| JTAG 활성화됨 | JTAG 장애가 있는 | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

J 활성화TAG Atmel ProChip Designer와의 인터페이스

J를 활성화하려면TAG ProChip Designer와의 인터페이스:

- 적절한 ProChip Designer 프로젝트를 엽니다.

- Device Fitter 아래에 있는 Atmel Fitter 버튼을 클릭하여 Fitter 옵션 창을 엽니다.

- 글로벌 장치 탭을 선택한 다음 J를 확인하세요.TAG 포트 상자. TMS 및 TDI 내부 풀업 저항은 TDI 풀업 및 TMS 풀업 상자를 체크하여 활성화할 수도 있습니다. 이러한 체크 상자는 아래 그림에 나와 있습니다.

그림 3-1 ProChip Designer Fitter 옵션 사용자 인터페이스

J 활성화TAG POF2JED와의 인터페이스

POF2JED에서는 JTAG POF2JED가 J를 결정할 수 있도록 모드 옵션을 자동으로 설정할 수 있습니다.TAG ATF15xx의 기능을 활성화해야 하는지 여부는 J 여부에 따라 결정됩니다.TAG 경쟁사의 CPLD에서 지원됩니다. J를 켜려면TAG ATF15xx CPLD에서 J 여부에 관계없이TAG 경쟁사의 CPLD에서 지원되는지 여부에 관계없이 JTAG 모드 옵션은 켜짐으로 설정해야 합니다. JTAG ATF15xx에서 활성화된 경우 TDI 및 TMS 내부 풀업 저항은 Enable을 확인하여 활성화할 수 있습니다.

POF2JED의 TDI_PULLUP 및 Enable TMS_PULLUP 상자. 아래 그림을 참조하세요.

그림 3-2 POF2JED 사용자 인터페이스

지침 및 권장 사항

주목: ATF15xx CPLD에서 ISP 작업을 수행할 때 이 섹션에 특별히 주의해야 합니다. 이 섹션에서는 JTAG 잘 알아두어야 할 ISP 가이드라인, 정보 및 권장 사항.

- J를 확인하세요TAG J의 모든 장치에 대한 포트TAG 체인이 활성화되었습니다.

- ATF15xx CPLD의 경우 JTAG 장치가 비어 있거나 지워지거나 J로 프로그래밍된 경우 포트가 활성화됩니다.TAG 활성화됨.

- 모든 Atmel ATF15xx 장치는 비어 있는/지워진 상태로 배송됩니다. 따라서 JTAG 포트는 모든 신규 기기에 대해 활성화되어 있으며 ISP에 연결할 준비가 되었습니다.

- J가 있는 ATF15xx 장치TAG 비활성화된 항목은 ISP가 아닌 장치 프로그래머를 사용하여 지워야 J를 다시 활성화할 수 있습니다.TAG 포트.

- 적절한 VCC 볼륨을 확인하세요tage는 J의 각 장치에 적용됩니다.TAG 체인.

- 15-PLCC, 84-TQFP 및 100-PQFP 패키지 유형의 ATF100xxAS/ASL CPLD: VCCINT는 4.5V~5.5V여야 하고, VCCIO는 3.0V~3.6V 또는 4.5V~5.5V일 수 있습니다.

- 15-PLCC 및 44-TQFP 패키지 유형의 ATF44xxAS/ASL CPLD: VCC는 4.5V~5.5V 사이여야 합니다.

- ATF15xxASV/ASVL CPLD: VCC(VCCIO 및 VCCINT)는 3.0V~3.6V 사이여야 합니다.

- J의 장치에 대한 VCCTAG 체인은 적절하게 조절되고 여과되어야 합니다.

- 대부분의 애플리케이션에 사용되는 ATF15xx CPLD의 경우 각 VCC/GND 쌍에 대해 0.22µF 디커플링 커패시터를 하나씩 사용하는 것이 좋습니다.

- J의 모든 장치에 공통 접지를 사용하는 것이 좋습니다.TAG 체인과 JTAG 인터페이스 하드웨어(예: ATDH1150USB ISP 다운로드 케이블).

- 장시간(최대 5개 기기) 사용은 피하는 것이 좋습니다.TAG 쇠사슬.

- 긴 J라면TAG 체인이 필요하고, 5번째 장치마다 TMS 및 TCK 신호를 버퍼링합니다. 슈미트 트리거 버퍼를 사용하는 것이 좋습니다.

- 버퍼는 TMS와 TCK 신호의 상승 및 하강 시간을 재구성합니다.

- 버퍼로 인해 발생하는 추가적인 지연을 고려해야 합니다.

- TMS 및 TDI 신호에는 풀업 저항(4.7KΩ~10KΩ)을 사용하고 J에서 TCK 신호에는 풀다운 저항을 사용하는 것이 좋습니다.TAG 인터페이스 하드웨어에 의해 구동되지 않을 때 이러한 신호가 플로팅되는 것을 방지하기 위한 헤더입니다.

- ATF15xx CPLD에는 TMS 및 TDI의 옵션 내부 풀업이 사용 가능합니다.

- J를 종료하는 것이 좋습니다.TAG J에서의 신호TAG 헤더.

- 능동적 종료와 수동적 종료가 모두 허용되지만, 수동적 종료가 더 선호됩니다.

- 긴 케이블/PCB 트레이스 길이로 인한 울림 현상이 줄어듭니다.

- 종료는 TMS와 TCK에 가장 중요합니다.

- J의 모든 장치의 입력 및 I/O는 다음과 같습니다.TAG 체인, J 제외TAG ATF15xx CPLD를 프로그래밍할 때는 노이즈를 최소화하기 위해 핀이 정적 상태여야 합니다.

- Atmel ATF15xx 개발/프로그래머 보드 중 하나를 사용할 때 VCC 선택 점퍼 위치를 변경할 때는 보드의 전원을 꺼야 합니다.

- ATF15xx CPLD의 경우 JTAG ISP는 해당 부품이 핀 제어 전원 끄기 모드에 있거나 "저전력" 장치가 절전 모드에 있을 때 사용할 수 있습니다.

- ISP 중단 후 장치 상태:

- ISP가 중단되면 핀키퍼 회로의 상태와 관계없이 모든 I/O 핀은 3상태가 됩니다.

- 부분적으로 프로그래밍된 장치로 인해 회로 기판의 다른 장치와 버스 경합이 발생하는 것을 방지합니다.

- ISP 프로그래밍 중 모든 I/O 핀은 다음 조건 중 하나입니다.

- 고임피던스 상태:

- 빈/지워진 장치가 프로그래밍되는 경우.

- 핀키퍼 회로가 비활성화된 상태에서 장치를 다시 프로그래밍하는 경우.

- 회로 기판의 ATF15xx CPLD와 인터페이스하는 외부 장치와의 버스 경합을 방지합니다.

- 이전 상태에 약하게 고정됨:

- 프로그래밍된 장치가 핀키퍼 회로를 활성화하여 다시 프로그래밍되는 경우.

- I/O 핀은 ISP 이전의 이전 논리 레벨을 유지합니다.

- ISP가 시스템 보드의 다른 장치의 작동에 영향을 미치지 못하도록 방지합니다.

- 여러 개의 J 사용TAG 한 보드에 체인을 여러 개 사용하는 것은 권장되지 않습니다.

- 장치는 서로 다른 J 간에 상호 작용할 수 있습니다.TAG 쇠사슬.

- 이 보드는 모든 J의 모든 장치가 작동할 때만 작동합니다.TAG 체인이 성공적으로 프로그래밍되었습니다.

- 체인의 한 장치 이상에 대한 프로그래밍이 실패하는 경우 다른 JTAG 체인이 성공적으로 프로그래밍되었습니다:

- 3상태 출력의 경우 버스 경합 문제로 인해 Atmel이나 보드의 다른 장치가 손상될 수 있습니다.

- 시스템 보드의 작동 상태가 정의되지 않아 잘못된 기능 작동이 발생할 수 있습니다.

- J 사이에 활성 회로 삽입TAG 헤더와 JTAG 체인에 있는 장치는 권장되지 않습니다. 활성 회로가 오작동하면 프로그래밍/확인 문제가 발생할 수 있습니다.

- 혼합된 볼륨의 사용tage 장치 JTAG 체인은 권장되지 않습니다.

- 이것들은 J입니다TAG 다른 VCC 볼륨을 사용하는 장치가 있는 체인tages 및/또는 인터페이스 voltag에스.

- 인터페이스 볼륨tag5.0V 장치의 e 레벨(VIL, VIH, VOL, VOH)은 인터페이스 볼륨과 호환되지 않을 수 있습니다.tag3.0V 장치의 e 레벨.

- ATMISP가 J와 통신하는 데 문제가 있는 경우TAG 장치 하드웨어 체인, J의 주파수를 낮추기 위해 Self Calibrate 또는 Manually Calibrate를 실행해보세요.TAG 신호.

- 프로그래밍을 시작하기 전에 ATDH1150USB 케이블의 LED가 켜져 있고 녹색인지 확인하세요. ISP 다운로드 케이블이 ATMISP 소프트웨어와 제대로 통신할 수 있는지 확인하세요.

- 적절한 VCC 볼륨을 확인하세요tage는 ATDH1150USB 케이블에 적용됩니다.

- J의 첫 번째 장치에서 사용하는 VCCTAG 체인은 1150핀 J의 핀 4를 통해 ATDH10USB 케이블에 공급되어야 합니다.TAG 헤더.

- VCCINT와 VCCIO가 별도로 있는 ATF15xx CPLD의 경우, ATDH1150USB 케이블에는 VCCIO를 사용해야 합니다.

주문 정보

| 주문 코드 | 설명 |

| ATF15xx-DK3-U | CPLD 개발/프로그래머 키트(ATF15xxDK3-SAA44 및 ATDH1150USB 또는 ATDH1150USB-K 포함) |

| ATF15xxDK3-SAA100 | DK100 보드용 3핀 TQFP 소켓 어댑터 보드 |

| ATF15xxDK3-SAJ44 | DK44 보드용 3핀 PLCC 소켓 어댑터 보드 |

| ATF15xxDK3-SAJ84 | DK84 보드용 3핀 PLCC 소켓 어댑터 보드 |

| ATF15xxDK3-SAA44 | DK44 보드용 3핀 TQFP 소켓 어댑터 보드 |

| ATDH1150USB | Atmel ATF15xx CPLD USB 기반 JTAG ISP 다운로드 케이블 |

개정 내역

| 문서. 신부님. | 날짜 | 댓글 |

| A | 12/2015 | 초기 문서 릴리스. |

연락처 정보

아트멜 코퍼레이션

- 1600 Technology Drive, San Jose, CA 95110 USA

- 전화: (+1)(408) 441.0311

- 팩스: (+1)(408) 436.4200

- www.아트멜닷컴

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_사용자 가이드-12/2015

Atmel®, Atmel 로고 및 그 조합, Enabling Unlimited Possibilities® 및 기타는 미국 및 기타 국가에서 Atmel Corporation의 등록 상표 또는 상표입니다. 다른 용어 및 제품 이름은 다른 사람의 상표일 수 있습니다.

면책 조항: 이 문서의 정보는 Atmel 제품과 관련하여 제공됩니다. 이 문서에 의해 또는 Atmel 제품 판매와 관련하여 금반언 또는 기타 방식으로 지적 재산권에 대한 명시적 또는 묵시적 라이선스가 부여되지 않습니다. ATMEL에 위치한 ATMEL 판매 약관에 명시된 경우를 제외하고 WEB사이트에서 ATMEL은 어떠한 책임도 지지 않으며 상품성, 특정 목적에의 적합성 또는 비침해에 대한 묵시적 보증을 포함하되 이에 국한되지 않는 제품과 관련된 명시적, 묵시적 또는 법정적 보증에 대해 어떠한 책임도 지지 않습니다. 어떠한 경우에도 ATMEL은 이 문서의 사용 또는 사용 불능으로 인해 발생하는 직접적, 간접적, 결과적, 징벌적, 특별적 또는 우발적 손해(이에 국한되지 않음, 이익 손실, 사업 중단 또는 정보 손실에 대한 손해 포함)에 대해 책임을 지지 않습니다. ATMEL이 그러한 손해의 가능성을 통보받은 경우에도 마찬가지입니다. Atmel은 이 문서 내용의 정확성 또는 완전성과 관련하여 어떠한 진술이나 보증도 하지 않으며, 사전 통지 없이 언제든지 사양 및 제품 설명을 변경할 권리를 보유합니다. Atmel은 여기에 포함된 정보를 업데이트할 어떠한 약속도 하지 않습니다. 달리 구체적으로 명시되지 않는 한, Atmel 제품은 자동차 애플리케이션에 적합하지 않으며 사용해서는 안 됩니다. Atmel 제품은 생명을 유지하거나 지원하기 위한 응용 분야에서 구성 요소로 사용하도록 의도, 허가 또는 보증되지 않습니다. 안전이 중요한 군사 및 자동차 응용 분야 면책 조항: Atmel 제품은 Atmel 임원의 구체적인 서면 동의 없이 해당 제품의 고장으로 인해 상당한 개인 부상 또는 사망이 발생할 것으로 합리적으로 예상되는 응용 분야("안전이 중요한 응용 분야")에 사용하도록 설계되지 않았으며 이와 관련하여 사용되지 않습니다. 안전이 중요한 응용 분야에는 생명 유지 장치 및 시스템, 핵 시설 및 무기 시스템을 작동하기 위한 장비 또는 시스템이 포함되지만 이에 국한되지 않습니다. Atmel 제품은 Atmel에서 군용 등급으로 특별히 지정하지 않는 한 군사 또는 항공 우주 응용 분야 또는 환경에서 사용하도록 설계 또는 의도되지 않았습니다. Atmel 제품은 Atmel에서 자동차 등급으로 특별히 지정하지 않는 한 자동차 응용 분야에서 사용하도록 설계 또는 의도되지 않았습니다.

문서 / 리소스

|

Atmel ATF15xx 복합 프로그래밍 논리 장치 [PDF 파일] 사용자 가이드 ATF15xx, ATF15xx 복합 프로그래머블 논리 장치, 복합 프로그래머블 논리 장치, 프로그래머블 논리 장치, 논리 장치, 장치 |