Dispositivo lógico programável complexo Atmel ATF15xx

Especificações

- Nome do produto: Atmel ATF15xx Programação no sistema

- Modelo: ATF15xx

- Tipo: Dispositivo Lógico Programável Complexo (CPLD)

- Método de programação: Programação no sistema (ISP)

- Interface: JTAG Interface do ISP

- Fabricante: Atmel

Perguntas frequentes

P: Posso usar software de programação de terceiros com os CPLDs ATF15xx?

R: Sim, desde que o software suporte o algoritmo de programação e JTAG instruções necessárias para os CPLDs ATF15xx.

P: É possível programar vários CPLDs ATF15xx simultaneamente?

R: Sim, o JTAG A interface ISP suporta programação de múltiplos dispositivos para programação eficiente de vários CPLDs ao mesmo tempo.

Introdução

- Os dispositivos lógicos programáveis complexos (CPLDs) Atmel® ATF15xx com arquitetura Logic Doubling® oferecem suporte à programação no sistema (ISP) por meio do IEEE Std. 1149.1 Joint Test Action Group (JTAG). Esse recurso aumenta a flexibilidade da programação e fornece benefícios em várias fases; desenvolvimento do produto, produção e uso em campo. Este guia do usuário descreve os métodos de design e os requisitos para implementar ISP em CPLDs ATF15xx com suporte a ISP, conforme listado abaixo:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Características e benefícios

A programação no sistema permite a programação e reprogramação de dispositivos ISP depois que eles são montados nas Placas de Circuito Impresso (PCBs). Isso elimina a etapa de manuseio extra necessária no processo de fabricação para programar os dispositivos em um programador de dispositivo externo antes que eles sejam montados nas PCBs. A eliminação dessa etapa reduz a possibilidade de danificar os fios delicados de dispositivos de montagem em superfície com alta contagem de pinos ou danificar o dispositivo por descarga eletrostática (ESD) durante o fluxo de programação. O ISP também permite que os usuários façam alterações de design e atualizações de campo sem ter que remover os dispositivos ISP das PCBs. Além disso, ele também permite o uso de um microcontrolador incorporado ou testador no circuito para executar operações de programação no sistema nos dispositivos ISP e integrar essas operações de programação no fluxo de produção das placas de circuito.

Sistemas de programação no sistema

Os três componentes essenciais de um sistema ISP para os CPLDs ATF15xx são:

Programas

Implementação do algoritmo de programação, bem como a geração do JTAG instruções e dados para os dispositivos ISP alvo. Isso pode ser um programa de software rodando em um PC, um microcontrolador embarcado ou um equipamento de teste in-circuit.

Hardware de interface

Um canal de comunicação entre o software ISP e os dispositivos ISP na placa de destino. Pode ser um cabo de download ISP ou programador da Atmel ou de um fornecedor terceirizado, equipamento de teste em circuito ou as conexões entre um microcontrolador embarcado e dispositivos ISP no PCB

Quadro de alvos

Placa de circuito contendo os dispositivos ISP no JTAG cadeia. Esta pode ser a placa de desenvolvimento/programação ATF15xx CPLD da Atmel ou uma placa de circuito personalizada com o J apropriadoTAG conexões com o hardware da interface.

Além desses três componentes, um JEDEC file é necessário programar um CPLD ATF15xx. Este JEDEC file pode ser criado compilando um design file usando software de desenvolvimento que suporta os CPLDs ATF15xx, como Atmel WinCUPL e Atmel ProChip Designer. A Atmel também fornece um utilitário de software tradutor, POF2JED.exe, que converte saída file do formato de programação do concorrente para um JEDEC file compatível com o CPLD ATF15xx. Para obter mais informações sobre este utilitário, consulte a nota de aplicação Atmel, “ATF15xx Product Family Conversion”, disponível no site Atmel weblocal. Após o JEDEC files são criados para todos os CPLDs ATF15xx, eles podem ser programados na placa de destino. Os CPLDs ATF15xx podem ser programados pelos seguintes sistemas de programação no sistema:

- Sistema de programação ATF15xx In-System

- Microcontroladores embarcados

- Testadores em circuito

Sistema de programação no sistema Atmel ATF15xx

Para programação no sistema dos CPLDs ATF15xx, o software ISP, o cabo de download e o kit de desenvolvimento/programação estão disponíveis na Atmel e são descritos nas seções abaixo.

Software para ISP

O software Atmel ATF15xx ISP, ATMISP, é o principal meio de implementação do JTAG programação no sistema nos CPLDs ATF15xx. O ATMISP é executado em um PC host baseado em Windows e implementa a programação no sistema dos CPLDs ATF15xx no sistema de hardware do ISP de destino ou gera um Serial Vector Format (.SVF) file para ser usado pelo Equipamento de Teste Automático (ATE) para programar os CPLDs ATF15xx no sistema de destino. O ATMISP primeiro adquire todas as informações necessárias dos usuários sobre o JTAG cadeia de dispositivos no sistema de destino. Em seguida, ele executa o J apropriadoTAG Instruções do ISP para o JTAG cadeia de dispositivos no sistema de destino de acordo com o JTAG informações da cadeia de dispositivos especificadas pelos usuários por meio da porta USB ou LPT do PC. Mais informações sobre o software Atmel ATMISP estão disponíveis em www.atmel.com/tools/ATMISP.aspx.

Cabo de download do ISP

O cabo de download ISP baseado em USB Atmel ATF15xx, ATDH1150USB, conecta-se a uma porta USB padrão de um computador host de um lado e a uma porta JTAG cabeçalho da placa de circuito alvo no outro lado. Ele transfere o JTAG instruções e dados gerados pelo ATMISP em execução no PC host para os dispositivos ISP na placa de circuito de destino. Mais informações sobre o cabo ATDH1150USB estão disponíveis em www.atmel.com/tools/ATDH1150USB.aspx.

Desenvolvimento/Programador

O Atmel ATF15xx Development/Programmer Kit, ATF15xx-DK3-U, é um sistema de desenvolvimento completo e um programador ISP para os CPLDs ATF15xx. Este kit fornece aos designers uma maneira muito rápida e fácil de desenvolver protótipos e avaliar novos designs com um CPLD ATF15xx ISP. Com a disponibilidade de diferentes placas adaptadoras de soquete para suportar a maioria dos tipos de pacotes oferecidos nos CPLDs ATF15xx, este kit pode ser usado como um programador ISP para programar os CPLDs ATF15xx ISP na maioria dos tipos de pacotes disponíveis por meio do JTAG interface. Mais informações sobre o kit Atmel ATF15xx-DK3-U estão disponíveis em www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Sistema de microcontrolador embarcado

O algoritmo de programação e JTAG instruções para os CPLDs ATF15xx podem ser implementadas em um microcontrolador ou microprocessador, que pode então ser usado para programar os CPLDs ATF15xx na placa de destino. Um método possível é extrair todos os J pertinentesTAG informações de protocolo (ou seja, JTAG instruções e dados) do SVF file gerado pelo software ATMISP e, em seguida, usar essas informações para implementar o código para o microcontrolador ou microprocessador que geraria o JTAG sinais para os dispositivos ISP no JTAG cadeia. Essa abordagem é mais adequada para sistemas que já têm um microcontrolador ou microprocessador embarcado, e isso elimina o uso de software de programação e ferramentas de hardware externos no sistema.

Sistema de teste em circuito

Os CPLDs ATF15xx podem ser programados na placa de circuito alvo por meio do JTAG interface durante o teste da placa de circuito usando um testador no circuito. Geralmente, o SVF file gerado pelo ATMISP deve conter todos os J pertinentesTAG informações de programação no sistema que os testadores no circuito precisam para programar os CPLDs ATF15xx na placa de circuito alvo. Essa abordagem permite a integração da etapa de programação no teste stage do fluxo de produção.

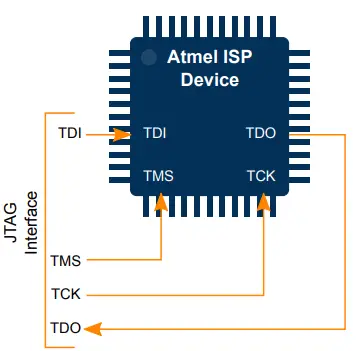

JTAG Interface do ISP

O ISP para CPLDs ATF15xx é implementado usando o IEEE 1149.1 Std. JTAG interface. Esta interface pode ser usada para apagar, programar e verificar os CPLDs ATF15xx. O JTAG interface é uma interface serial que consiste nos sinais TCK, TMS, TDI e TDO e um JTAG Controlador de porta de acesso de teste (TAP). O pino TCK é a entrada de relógio para o JTAG Controlador TAP e para mudar para dentro/fora do JTAG instruções e dados. O pino TDI é a entrada de dados seriais. Ele é usado para deslocar instruções de programação e dados para os dispositivos ISP. O pino TDO é a saída de dados seriais. Ele é usado para deslocar dados dos dispositivos ISP. O pino TMS é um pino de seleção de modo. Ele controla o estado do JTAG Controlador TAP. O JTAG os pinos de interface do CPLD ATF15xx na placa de destino do ISP devem ser conectados ao hardware de interface do ISP (ou seja, cabo de download do ISP) normalmente por meio de um cabeçalho de 10 pinos. O hardware de interface do ISP também precisa ser conectado ao PC host que executa o software do ISP. O hardware de interface do ISP estabelece comunicação entre o software do ISP e os dispositivos do ISP e permite que o software do ISP transfira as instruções de programação e os dados do PC host para os CPLDs ATF15xx. CPLDs ATF15xx com o JTAG os recursos habilitados são totalmente JTAG compatível e também suporta as operações necessárias do Boundary Scan Test (BST) especificadas no JTAG padrão. Os CPLDs ATF15xx podem ser configurados para fazer parte de um JTAG Cadeia BST com outros JTAG dispositivos para teste no circuito da placa do sistema. Com esse recurso, os CPLDs ATF15xx podem ser testados na placa de circuito junto com outros JTAG-dispositivos suportados sem recorrer a testes de laboratório.

Programação de dispositivo único

O JTAG A interface ISP pode ser configurada para programar um único CPLD ATF15xx. O JTAG configuração para um único dispositivo é mostrada na figura abaixo. Quando um CPLD ATF15xx é configurado dessa forma, um registro aparece entre os pinos TDI e TDO do dispositivo. O tamanho do registro depende do JTAG largura da instrução e os dados sendo deslocados para essa instrução. Figura 2-1 JTAG Dispositivo

Programação de múltiplos dispositivos

Os CPLDs ATF15xx podem ser configurados como parte de uma cadeia de vários JTAG- dispositivos suportados, conforme descrito abaixo e também mostrado na figura a seguir.

- Conecte os pinos TMS e TCK para cada dispositivo no JTAG corrente para os pinos TMS e TCK do JTAG cabeçalho de interface na placa de circuito.

- Conecte o pino TDI do primeiro dispositivo ao pino TDI do JTAG cabeçalho da interface.

- Conecte o pino TDO do primeiro dispositivo ao pino TDI do próximo dispositivo. Continue esse processo até que todos, exceto o último, estejam conectados.

- Conecte o pino TDO do último dispositivo ao pino TDO do JTAG cabeçalho da interface.

Figura 2-2 Dispositivo múltiplo JTAG Configuração

Para programar vários dispositivos em um JTAG chain, os usuários devem usar ferramentas de software do ISP que suportem tais recursos. No software do ISP, os usuários precisam especificar:

- Número de dispositivos no JTAG corrente.

- Números de peça dos dispositivos e as posições dentro do JTAG corrente.

- JTAG operações para cada um dos dispositivos.

- Outro JTAG-informações relacionadas, como o JTAG largura de instrução para cada um dos dispositivos.

Uma vez que o JTAG a cadeia de ligação em cadeia está devidamente configurada na placa de destino do ISP e no software do ISP, os dispositivos no JTAG a cadeia pode ser programada ao mesmo tempo.

Considerações de design

Para executar ISP em um CPLD ATF15xx, recursos para o JTAG interface no ATF15xx deve ser reservada. Portanto, os quatro pinos de E/S para os pinos TMS, TDI, TDO e TCK devem ser reservados para JTAG e não podem ser usados como E/Ss de usuário. Os números de pinos para esses pinos dependem de qual ATF15xx CPLD é usado e seu tipo de pacote. Consulte a tabela abaixo para obter informações sobre pinagem. O JTAG o padrão recomenda que os pinos TMS e TDI sejam puxados para cima para cada dispositivo no JTAG cadeia. Os CPLDs ATF15xx têm um recurso de pull-up interno para esses pinos que, quando habilitado, elimina a necessidade de resistores de pull-up externos. Além disso, o JTAG O recurso de interface deve ser habilitado para executar o ISP nos CPLDs ATF15xx. Habilitando o JTAG A interface requer a escolha de tipos específicos de dispositivos Atmel ou configurações de opções antes de compilar o design ATF15xx. Esses procedimentos são descritos para WinCUPL, ProChip Designer e POF2JED neste guia. Por padrão, todos os CPLDs ATF15xx novos são enviados com o JTAG interface habilitada. Uma vez que os recursos lógicos para o JTAG interface são reservadas, os usuários podem programar, verificar e apagar qualquer CPLD ATF15xx na placa de destino usando o software ATMISP.

Dica:Embora os quatro JTAG os pinos são reservados para um JTAG interface, os usuários podem implementar funções lógicas ocultas nas macrocélulas associadas a esses pinos.

Tabela 3-1 ATF15xx CPLD JTAG Números PIN

| JTAG Alfinete | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| EMT (Transmissão Transmissível) | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Habilitar JTAG Interface com WinCUPL

Para habilitar o JTAG interface com WinCUPL, o tipo de dispositivo ISP ATF15xx apropriado precisa ser especificado antes que um design seja compilado. Após um design ser compilado com sucesso, um JEDEC file com o JTAG recurso de interface habilitado é gerado. Quando este JEDEC file é programado em um ATF15xxCPLD, seu JTAG interface está habilitada. Os usuários também podem habilitar os resistores pull-up internos TDI e TMS incluindo as seguintes declarações de propriedade no projeto CUPL file.

- PROPRIEDADE ATMEL {TDI_PULLUP = ON};

- PROPRIEDADE ATMEL {TMS_PULLUP = ON};

Perceber: Se um tipo de dispositivo ISP ATF15xx for usado para um projeto que usa o JTAG pinos de interface como pinos de E/S lógica, o WinCUPL gera um erro.

As etapas a seguir discutem como abrir um design existente no WinCUPL, especificar o tipo de dispositivo e compilar o design.

- No menu principal do WinCUPL, selecione File > Abrir. Selecione a fonte CUPL (.pld) file do diretório de trabalho apropriado.

- Selecione OK para abrir a fonte PLD file.

- No menu principal do WinCUPL, selecione File > Salvar. Isso salva as alterações feitas na fonte file.

- No menu principal, selecione Opções > Dispositivos. Isso abre a caixa de diálogo Seleção de Dispositivo.

- Selecione o dispositivo ISP ATF15xx apropriado. Veja a tabela a seguir para uma listagem de todos os tipos de dispositivos ATF15xx suportados pelo WinCUPL.

- Selecione OK para fechar o menu de seleção de dispositivos.

- Nota: Um método alternativo é escolher um tipo de dispositivo ATF15xx apropriado na tabela a seguir e incluí-lo na seção de cabeçalho da fonte CUPL file.

- No menu principal do WinCUPL, selecione Executar > Compilação Dependente de Dispositivo.

- O WinCUPL compila o design e gera o Atmel device fitter. Se o design for adequado, um JEDEC file é criado automaticamente.

- Quando o JEDEC file é programado no dispositivo, o JTAG interface, os pull-ups internos opcionais TMS e TDI e os circuitos opcionais de proteção de pinos são habilitados.

Observação: Selecionar um tipo de dispositivo Atmel ISP habilita automaticamente o JTAG interface padrão quando o Atmel WinCUPL executa o instalador de dispositivos Atmel.

Se os projetos impedem a reserva de recursos para o JTAG interface ou um ISP não for usado opcionalmente, um tipo de dispositivo Atmel não ISP deve ser selecionado. Veja a tabela abaixo para uma lista de dispositivos. O dispositivo pode então ser reprogramado usando um programador de dispositivo externo. A tabela abaixo lista os tipos de dispositivos Atmel ISP e Atmel não ISP para WinCUPL.

Tabela 3-2 Tipo de dispositivo WinCUPL ATF15xx

| Nome do dispositivo | Tipo de pacote | Tipo de dispositivo WinCUPL | |

| JTAG Habilitado | JTAG Desabilitado | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Habilitar JTAG Interface com Atmel ProChip Designer

Para habilitar o JTAG interface com ProChip Designer:

- Abra o projeto apropriado do ProChip Designer.

- Abra a janela Opções do Fitter clicando no botão Atmel Fitter em Device Fitter.

- Selecione a aba Dispositivo Global e então marque a caixa JTAG Caixa de porta. Os resistores pull-up internos TMS e TDI também podem ser habilitados marcando as caixas TDI Pullup e TMS Pullup. Essas caixas de seleção são mostradas na figura abaixo.

Figura 3-1 Interface do usuário das opções do ProChip Designer Fitter

Habilitar JTAG Interface com POF2JED

No POF2JED, o JTAG A opção de modo pode ser definida como Automático para permitir que o POF2JED determine se o JTAG recurso no ATF15xx deve ser habilitado ou não, e é baseado em se JTAG é suportado no CPLD do concorrente. Para ligar o JTAG no CPLD ATF15xx independentemente de JTAG é suportado no CPLD do concorrente ou não, o JTAG A opção Modo deve ser definida como Ligado. Quando JTAG está habilitado no ATF15xx, os resistores pull-up internos TDI e TMS podem ser habilitados marcando a caixa de seleção Habilitar

Caixas TDI_PULLUP e Enable TMS_PULLUP em POF2JED. Veja a figura abaixo.

Figura 3-2 Interface do usuário do POF2JED

Diretrizes e recomendações

Atenção: Atenção extra a esta seção deve ser dada ao executar operações ISP em CPLDs ATF15xx. Esta seção discute alguns dos JTAG Diretrizes, informações e recomendações do ISP que devem ser bem observadas.

- Certifique-se de que o JTAG porta para todos os dispositivos no JTAG cadeia estão habilitados.

- Para os CPLDs ATF15xx, o JTAG a porta é habilitada se os dispositivos estiverem em branco/apagados ou programados com JTAG habilitado.

- Todos os dispositivos Atmel ATF15xx são enviados em estado em branco/apagado; portanto, o JTAG a porta está habilitada para todos os dispositivos novos e pronta para o ISP.

- Dispositivos ATF15xx com JTAG desabilitados precisam ser apagados usando um programador de dispositivo não ISP para reativar o JTAG porta.

- Certifique-se de que o volume VCC corretotage é aplicado a cada um dos dispositivos no JTAG corrente.

- CPLDs ATF15xxAS/ASL nos tipos de pacote 84-PLCC, 100-TQFP e 100-PQFP: VCCINT deve estar entre 4.5 V e 5.5 V, enquanto VCCIO pode estar entre 3.0 V e 3.6 V ou 4.5 V e 5.5 V.

- CPLDs ATF15xxAS/ASL em tipos de pacote 44-PLCC e 44-TQFP: VCC deve estar entre 4.5 V e 5.5 V.

- CPLDs ATF15xxASV/ASVL: VCC (VCCIO e VCCINT) deve estar entre 3.0 V e 3.6 V.

- O VCC para os dispositivos no JTAG a cadeia deve ser devidamente regulada e filtrada.

- Para os CPLDs ATF15xx usados na maioria das aplicações, é recomendado usar um capacitor de desacoplamento de 0.22 µF para cada um dos pares VCC/GND.

- É recomendável usar um aterramento comum para todos os dispositivos no JTAG corrente e o JTAG hardware de interface (por exemplo, cabo de download ISP ATDH1150USB).

- Recomenda-se evitar J longos (não mais que cinco dispositivos)TAG correntes.

- Se um J longoTAG cadeia é necessária, armazene em buffer os sinais TMS e TCK após cada quinto dispositivo. O uso do buffer de gatilho Schmitt é preferível.

- Os buffers remodelam os tempos de subida e descida dos sinais TMS e TCK.

- É preciso levar em consideração o atraso adicional causado pelos buffers.

- Recomenda-se a utilização de resistores pull-up (4.7 KΩ a 10 KΩ) para os sinais TMS e TDI e resistor pull-down para o sinal TCK no JTAG cabeçalho para evitar que esses sinais flutuem quando não estiverem sendo controlados pelo hardware da interface.

- Pull-ups internos opcionais no TMS e TDI estão disponíveis para os CPLDs ATF15xx.

- É recomendado encerrar JTAG sinais no JTAG cabeçalho.

- Terminações ativas e passivas são aceitáveis; no entanto, a terminação passiva é preferida.

- Reduz o zumbido causado por longos comprimentos de cabo/PCB.

- O término é mais crítico para TMS e TCK.

- É recomendado que todas as entradas e E/Ss dos dispositivos no JTAG cadeia, exceto o JTAG pinos, devem estar em estado estático quando os CPLDs ATF15xx estão sendo programados para minimizar o ruído.

- Ao usar uma das placas de desenvolvimento/programação Atmel ATF15xx, a alimentação da placa deve ser desligada quando as posições dos jumpers de seleção VCC estiverem sendo alteradas.

- Para os CPLDs ATF15xx, JTAG O ISP está disponível quando a peça está no modo de desligamento controlado por pino ou quando o dispositivo de “baixo consumo de energia” está em modo de espera.

- Estado do dispositivo após interrupção do ISP:

- Se o ISP for interrompido, todos os pinos de E/S serão tri-stateados, independentemente do estado dos circuitos Pin-keeper.

- Evita que dispositivos parcialmente programados causem contenção de barramento com outros dispositivos na placa de circuito.

- Durante a programação do ISP, todos os pinos de E/S estão em uma das seguintes condições:

- Estado de alta impedância:

- Quando um dispositivo em branco/apagado é programado.

- Quando um dispositivo é reprogramado com os circuitos Pin-keeper desabilitados.

- Evita contenção de barramento com dispositivos externos que fazem interface com os CPLDs ATF15xx na placa de circuito.

- Fracamente preso ao estado anterior:

- Quando um dispositivo programado é reprogramado com os circuitos Pin-keeper habilitados.

- Os pinos de E/S mantêm os níveis lógicos anteriores ao ISP.

- Evita que o ISP afete a operação de outros dispositivos na placa de sistema.

- O uso de múltiplos JTAG correntes em uma placa não são recomendadas.

- Os dispositivos podem interagir entre diferentes JTAG correntes.

- A placa é funcional somente quando todos os dispositivos em todos os JTAG as cadeias são programadas com sucesso.

- Se a programação falhar para pelo menos um dispositivo em uma cadeia enquanto outros JTAG as cadeias foram programadas com sucesso:

- Tanto o Atmel quanto outros dispositivos a bordo podem ser danificados devido a um possível problema de contenção de barramento para saídas tri-stateáveis.

- O estado operacional da placa do sistema é indefinido e, portanto, pode ocorrer operação funcional incorreta.

- Inserindo circuitos ativos entre JTAG cabeçalho e o JTAG dispositivos em cadeia não é recomendado. Se o circuito ativo apresentar mau funcionamento, pode causar problemas de programação/verificação.

- O uso de volume mistotage dispositivo JTAG correntes não são recomendadas.

- Estes são JTAG cadeias com dispositivos que usam diferentes volumes VCCtages e/ou interface voltage.

- Volume da interfacetagOs níveis (VIL, VIH, VOL, VOH) para dispositivos de 5.0 V podem não ser compatíveis com a interface voltage níveis para dispositivos de 3.0 V.

- Se o ATMISP tiver problemas para se comunicar com o JTAG cadeia de hardware do dispositivo, tente executar a autocalibração ou a calibração manual para diminuir as frequências do JTAG sinais.

- Certifique-se de que o LED no cabo ATDH1150USB esteja ligado e verde antes de iniciar a programação. Certifique-se de que o cabo de download do ISP seja capaz de se comunicar adequadamente com o software ATMISP.

- Certifique-se de que o volume VCC corretotage é aplicado ao cabo ATDH1150USB.

- O VCC usado pelo primeiro dispositivo no JTAG a corrente deve ser fornecida ao cabo ATDH1150USB através do pino 4 do J de 10 pinosTAG cabeçalho.

- Para CPLDs ATF15xx com VCCINT e VCCIO separados, o VCCIO deve ser usado para o cabo ATDH1150USB.

Informações para pedidos

| Código de pedido | Descrição |

| ATF15xx-DK3-U | Kit de desenvolvimento/programador CPLD (inclui ATF15xxDK3-SAA44 e ATDH1150USB ou ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | Placa adaptadora de soquete TQFP de 100 pinos para placa DK3 |

| ATF15xxDK3-SAJ44 | Placa adaptadora de soquete PLCC de 44 pinos para placa DK3 |

| ATF15xxDK3-SAJ84 | Placa adaptadora de soquete PLCC de 84 pinos para placa DK3 |

| ATF15xxDK3-SAA44 | Placa adaptadora de soquete TQFP de 44 pinos para placa DK3 |

| ATDH1150USB | Atmel ATF15xx CPLD USB baseado em JTAG Cabo de download do ISP |

Histórico de revisão

| Doutor. Rev. | Data | Comentários |

| A | 12/2015 | Liberação inicial do documento. |

INFORMAÇÕES DE CONTATO

Corporação Atmel

- 1600 Technology Drive, San Jose, CA 95110 EUA

- T: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_Guia do usuário-12/2015

Atmel®, logotipo Atmel e combinações destes, Enabling Unlimited Possibilities® e outros são marcas registradas ou marcas comerciais da Atmel Corporation nos EUA e outros países. Outros termos e nomes de produtos podem ser marcas comerciais de terceiros.

ISENÇÃO DE RESPONSABILIDADE: As informações neste documento são fornecidas em relação aos produtos Atmel. Nenhuma licença, expressa ou implícita, por preclusão ou de outra forma, para qualquer direito de propriedade intelectual é concedida por este documento ou em conexão com a venda de produtos Atmel. EXCETO CONFORME ESTABELECIDO NOS TERMOS E CONDIÇÕES DE VENDAS DO ATMEL LOCALIZADAS NO ATMEL WEBSITE, A ATMEL NÃO ASSUME NENHUMA RESPONSABILIDADE E SE ISENTA DE QUALQUER GARANTIA EXPRESSA, IMPLÍCITA OU ESTATUTÁRIA RELACIONADA A SEUS PRODUTOS, INCLUINDO, MAS NÃO SE LIMITANDO À GARANTIA IMPLÍCITA DE COMERCIALIZAÇÃO, ADEQUAÇÃO A UM DETERMINADO FIM OU NÃO VIOLAÇÃO. EM NENHUMA HIPÓTESE A ATMEL SERÁ RESPONSÁVEL POR QUAISQUER DANOS DIRETOS, INDIRETOS, CONSEQUENCIAIS, PUNITIVOS, ESPECIAIS OU INCIDENTAIS (INCLUINDO, MAS NÃO SE LIMITAÇÃO, DANOS POR PERDAS E LUCROS, INTERRUPÇÃO DE NEGÓCIOS OU PERDA DE INFORMAÇÕES) DECORRENTES DO USO OU INCAPACIDADE DE USAR ESTE DOCUMENTO, MESMO QUE A ATMEL TENHA SIDO AVISADA DA POSSIBILIDADE DE TAIS DANOS. A Atmel não faz representações ou garantias com relação à precisão ou integridade do conteúdo deste documento e reserva-se o direito de fazer alterações nas especificações e descrições de produtos a qualquer momento, sem aviso prévio. A Atmel não se compromete a atualizar as informações aqui contidas. A menos que especificamente disposto de outra forma, os produtos Atmel não são adequados e não devem ser usados em aplicações automotivas. Os produtos Atmel não são destinados, autorizados ou garantidos para uso como componentes em aplicações destinadas a dar suporte ou sustentar a vida. AVISO LEGAL DE APLICAÇÕES CRÍTICAS DE SEGURANÇA, MILITARES E AUTOMOTIVAS: Os produtos Atmel não são projetados e não serão usados em conexão com quaisquer aplicações onde a falha de tais produtos seria razoavelmente esperada para resultar em ferimentos pessoais significativos ou morte ("Aplicações Críticas de Segurança") sem o consentimento específico por escrito de um oficial da Atmel. As aplicações críticas de segurança incluem, sem limitação, dispositivos e sistemas de suporte de vida, equipamentos ou sistemas para a operação de instalações nucleares e sistemas de armas. Os produtos Atmel não são projetados nem destinados ao uso em aplicações ou ambientes militares ou aeroespaciais, a menos que especificamente designados pela Atmel como de nível militar. Os produtos Atmel não são projetados nem destinados ao uso em aplicações automotivas, a menos que sejam especificamente designados pela Atmel como de nível automotivo.

Documentos / Recursos

|

Dispositivo lógico programável complexo Atmel ATF15xx [pdf] Guia do Usuário ATF15xx, ATF15xx Dispositivo Lógico Programável Complexo, Dispositivo Lógico Programável Complexo, Dispositivo Lógico Programável, Dispositivo Lógico, Dispositivo |