Thiết bị logic lập trình phức hợp Atmel ATF15xx

Thông số kỹ thuật

- Tên sản phẩm: Lập trình trong hệ thống Atmel ATF15xx

- Mẫu: ATF15xx

- Loại: Thiết bị logic lập trình phức tạp (CPLD)

- Phương pháp lập trình: Lập trình trong hệ thống (ISP)

- Giao diện: JTAG Giao diện ISP

- Nhà sản xuất: Atmel

Câu hỏi thường gặp

H: Tôi có thể sử dụng phần mềm lập trình của bên thứ ba với CPLD ATF15xx không?

A: Có, miễn là phần mềm hỗ trợ thuật toán lập trình và JTAG hướng dẫn cần thiết cho CPLD ATF15xx.

H: Có thể lập trình nhiều CPLD ATF15xx cùng lúc không?

A: Vâng, JTAG Giao diện ISP hỗ trợ lập trình nhiều thiết bị để lập trình hiệu quả nhiều CPLD cùng một lúc.

Giới thiệu

- Thiết bị logic lập trình phức hợp Atmel® ATF15xx (CPLD) với kiến trúc Logic Doubling® hỗ trợ lập trình trong hệ thống (ISP) thông qua Nhóm hành động thử nghiệm chung IEEE Std. 1149.1 (JTAG) giao diện. Tính năng này tăng cường tính linh hoạt của lập trình và mang lại lợi ích trong nhiều giai đoạn khác nhau; phát triển sản phẩm, sản xuất và sử dụng tại hiện trường. Hướng dẫn sử dụng này mô tả các phương pháp thiết kế và yêu cầu để triển khai ISP trên CPLD ATF15xx có hỗ trợ ISP như được liệt kê dưới đây:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Tính năng và lợi ích

Lập trình trong hệ thống cho phép lập trình và lập trình lại các thiết bị ISP sau khi chúng được gắn vào Bảng mạch in (PCB). Điều này loại bỏ bước xử lý bổ sung cần thiết trong quy trình sản xuất để lập trình các thiết bị trên một bộ lập trình thiết bị bên ngoài trước khi chúng được gắn vào PCB. Việc loại bỏ bước này làm giảm khả năng làm hỏng các dây dẫn mỏng manh của các thiết bị gắn bề mặt có số lượng chân cắm cao hoặc làm hỏng thiết bị thông qua phóng tĩnh điện (ESD) trong quá trình lập trình. ISP cũng cho phép người dùng thực hiện các thay đổi thiết kế và nâng cấp tại hiện trường mà không cần phải tháo các thiết bị ISP khỏi PCB. Hơn nữa, nó cũng cho phép sử dụng bộ vi điều khiển nhúng hoặc bộ kiểm tra trong mạch để thực hiện các hoạt động lập trình trong hệ thống trên các thiết bị ISP và tích hợp các hoạt động lập trình này vào quy trình sản xuất của bảng mạch.

Hệ thống lập trình trong hệ thống

Ba thành phần thiết yếu của hệ thống ISP dành cho CPLD ATF15xx là:

Phần mềm

Việc triển khai thuật toán lập trình cũng như việc tạo ra JTAG hướng dẫn và dữ liệu cho các thiết bị ISP mục tiêu. Đây có thể là một chương trình phần mềm chạy trên PC, một bộ vi điều khiển nhúng hoặc một thiết bị kiểm tra trong mạch.

Phần cứng giao diện

Kênh truyền thông giữa phần mềm ISP và các thiết bị ISP trên bo mạch đích. Đây có thể là cáp tải xuống ISP hoặc bộ lập trình từ Atmel hoặc nhà cung cấp bên thứ ba, thiết bị kiểm tra trong mạch hoặc kết nối giữa bộ vi điều khiển nhúng và các thiết bị ISP trên PCB

Bảng mục tiêu

Bảng mạch chứa các thiết bị ISP trong JTAG chuỗi. Đây có thể là bo mạch phát triển/lập trình CPLD ATF15xx từ Atmel hoặc bo mạch được thiết kế riêng với J phù hợpTAG kết nối tới phần cứng giao diện.

Ngoài ba thành phần này, một JEDEC file là cần thiết để lập trình một CPLD ATF15xx. JEDEC này file có thể được tạo ra bằng cách biên soạn một thiết kế file sử dụng phần mềm phát triển hỗ trợ ATF15xx CPLD như Atmel WinCUPL và Atmel ProChip Designer. Atmel cũng cung cấp tiện ích phần mềm dịch, POF2JED.exe, chuyển đổi đầu ra file từ định dạng lập trình của đối thủ cạnh tranh đến JEDEC file tương thích với ATF15xx CPLD. Để biết thêm thông tin về tiện ích này, vui lòng tham khảo ghi chú ứng dụng Atmel, “Chuyển đổi họ sản phẩm ATF15xx”, có sẵn trên Atmel webtrang web. Sau JEDEC files được tạo cho tất cả các CPLD ATF15xx, chúng có thể được lập trình trên bảng mục tiêu. Các CPLD ATF15xx có thể được lập trình bằng các hệ thống lập trình trong hệ thống sau:

- Hệ thống lập trình trong hệ thống ATF15xx

- Bộ vi điều khiển nhúng

- Thiết bị kiểm tra trong mạch

Hệ thống lập trình trong hệ thống Atmel ATF15xx

Để lập trình trong hệ thống CPLD ATF15xx, phần mềm ISP, cáp tải xuống và bộ phát triển/lập trình viên có sẵn từ Atmel và được mô tả trong các phần bên dưới.

Phần mềm ISP

Phần mềm ISP Atmel ATF15xx, ATMISP, là phương tiện chính để triển khai JTAG lập trình trong hệ thống trên CPLD ATF15xx. ATMISP chạy trên PC chủ chạy Windows và triển khai lập trình trong hệ thống của CPLD ATF15xx trên hệ thống phần cứng ISP đích hoặc tạo Định dạng vectơ tuần tự (.SVF) file được sử dụng bởi Thiết bị kiểm tra tự động (ATE) để lập trình CPLD ATF15xx trên hệ thống mục tiêu. ATMISP đầu tiên thu thập tất cả thông tin cần thiết từ người dùng về JTAG chuỗi thiết bị trong hệ thống mục tiêu. Sau đó, nó thực hiện J thích hợpTAG Hướng dẫn của ISP vào JTAG chuỗi thiết bị trong hệ thống mục tiêu theo JTAG thông tin chuỗi thiết bị do người dùng chỉ định thông qua cổng USB hoặc LPT của PC. Thông tin thêm về phần mềm Atmel ATMISP có tại www.atmel.com/tools/ATMISP.aspx.

Cáp tải xuống ISP

Cáp tải xuống ISP dựa trên USB Atmel ATF15xx, ATDH1150USB, kết nối với cổng USB tiêu chuẩn của máy chủ ở một bên và với cổng JTAG đầu của bảng mạch mục tiêu ở phía bên kia. Nó chuyển JTAG hướng dẫn và dữ liệu được tạo ra bởi ATMISP chạy trên máy tính chủ đến các thiết bị ISP trên bảng mạch đích. Thông tin thêm về cáp ATDH1150USB có tại www.atmel.com/tools/ATDH1150USB.aspx.

Phát triển/Lập trình viên

Bộ công cụ lập trình/phát triển Atmel ATF15xx, ATF15xx-DK3-U, là một hệ thống phát triển hoàn chỉnh và là một bộ lập trình ISP cho CPLD ATF15xx. Bộ công cụ này cung cấp cho các nhà thiết kế một cách rất nhanh chóng và dễ dàng để phát triển các nguyên mẫu và đánh giá các thiết kế mới với CPLD ISP ATF15xx. Với sự sẵn có của các bo mạch bộ chuyển đổi ổ cắm khác nhau để hỗ trợ hầu hết các loại gói được cung cấp trong CPLD ATF15xx, bộ công cụ này có thể được sử dụng như một bộ lập trình ISP để lập trình CPLD ISP ATF15xx trong hầu hết các loại gói có sẵn thông qua JTAG giao diện. Thông tin thêm về bộ Atmel ATF15xx-DK3-U có sẵn tại www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Hệ thống vi điều khiển nhúng

Thuật toán lập trình và JTAG hướng dẫn cho ATF15xx CPLD có thể được triển khai trong bộ vi điều khiển hoặc bộ vi xử lý, sau đó có thể được sử dụng để lập trình ATF15xx CPLD trên bảng mục tiêu. Một phương pháp khả thi là trích xuất tất cả các J có liên quanTAG thông tin giao thức (tức là JTAG hướng dẫn và dữ liệu) từ SVF file được tạo ra bởi phần mềm ATMISP, sau đó sử dụng thông tin này để triển khai mã cho bộ vi điều khiển hoặc bộ vi xử lý sẽ tạo ra JTAG tín hiệu cho các thiết bị ISP trong JTAG chuỗi. Phương pháp này phù hợp nhất với các hệ thống đã có bộ vi điều khiển hoặc bộ vi xử lý nhúng và loại bỏ việc sử dụng phần mềm lập trình bên ngoài trong hệ thống và các công cụ phần cứng.

Hệ thống kiểm tra trong mạch

Các CPLD ATF15xx có thể được lập trình trên bảng mạch mục tiêu thông qua JTAG giao diện trong quá trình thử nghiệm bảng mạch bằng máy thử nghiệm trong mạch. Nói chung, SVF file được tạo ra bởi ATMISP phải chứa tất cả các J có liên quanTAG thông tin lập trình trong hệ thống mà các máy kiểm tra trong mạch cần để lập trình ATF15xx CPLD trên bảng mạch mục tiêu. Phương pháp này cho phép tích hợp bước lập trình vào các thử nghiệmtagcủa luồng sản xuất.

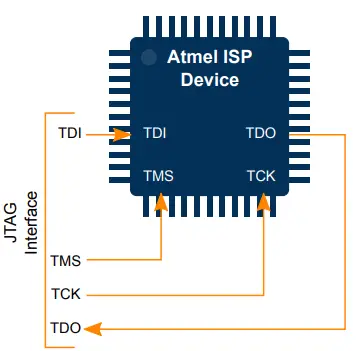

JTAG Giao diện ISP

ISP cho CPLD ATF15xx được triển khai bằng cách sử dụng IEEE 1149.1 Std. JTAG giao diện. Giao diện này có thể được sử dụng để xóa, lập trình và xác minh CPLD ATF15xx. JTAG giao diện là một giao diện nối tiếp bao gồm các tín hiệu TCK, TMS, TDI và TDO và một JTAG Bộ điều khiển Cổng truy cập thử nghiệm (TAP). Chân TCK là đầu vào xung nhịp cho JTAG Bộ điều khiển TAP và dịch chuyển vào/ra JTAG hướng dẫn và dữ liệu. Chân TDI là đầu vào dữ liệu nối tiếp. Nó được sử dụng để chuyển hướng dẫn lập trình và dữ liệu vào các thiết bị ISP. Chân TDO là đầu ra dữ liệu nối tiếp. Nó được sử dụng để chuyển dữ liệu ra khỏi các thiết bị ISP. Chân TMS là chân chọn chế độ. Nó điều khiển trạng thái của JTAG Bộ điều khiển TAP. JTAG chân giao diện của CPLD ATF15xx trên bo mạch đích ISP phải được kết nối với phần cứng giao diện ISP (tức là cáp tải xuống ISP) thông thường qua đầu cắm 10 chân. Phần cứng giao diện ISP cũng cần được kết nối với PC chủ chạy phần mềm ISP. Phần cứng giao diện ISP thiết lập giao tiếp giữa phần mềm ISP và các thiết bị ISP, và cho phép phần mềm ISP chuyển hướng dẫn lập trình và dữ liệu từ PC chủ đến CPLD ATF15xx. CPLD ATF15xx với JTAG tính năng được kích hoạt đầy đủ JTAG tương thích và cũng hỗ trợ các hoạt động Kiểm tra quét ranh giới (BST) bắt buộc được chỉ định trong JTAG tiêu chuẩn. CPLD ATF15xx có thể được cấu hình để trở thành một phần của JTAG Chuỗi BST với J khácTAG thiết bị để kiểm tra trong mạch của bo mạch hệ thống. Với tính năng này, CPLD ATF15xx có thể được kiểm tra trên bo mạch cùng với các J khácTAG- thiết bị được hỗ trợ mà không cần dùng đến phương pháp thử nghiệm bằng đinh.

Lập trình thiết bị đơn

Chữ JTAG Giao diện ISP có thể được cấu hình để lập trình một CPLD ATF15xx duy nhất. JTAG cấu hình cho một thiết bị duy nhất được hiển thị trong hình bên dưới. Khi CPLD ATF15xx được cấu hình theo cách này, một thanh ghi sẽ xuất hiện giữa các chân TDI và TDO của thiết bị. Kích thước của thanh ghi phụ thuộc vào JTAG chiều rộng lệnh và dữ liệu được chuyển vào cho lệnh đó. Hình 2-1 JTAG Thiết bị

Lập trình nhiều thiết bị

Các CPLD ATF15xx có thể được cấu hình như một phần của chuỗi liên kết nhiều JTAG- các thiết bị được hỗ trợ như mô tả bên dưới và cũng được hiển thị trong hình sau.

- Kết nối chân TMS và TCK cho mỗi thiết bị trong JTAG chuỗi đến các chân TMS và TCK của JTAG đầu cắm giao diện trên bảng mạch.

- Kết nối chân TDI từ thiết bị đầu tiên với chân TDI của JTAG tiêu đề giao diện.

- Kết nối chân TDO từ thiết bị đầu tiên với chân TDI của thiết bị tiếp theo. Tiếp tục quá trình này cho đến khi tất cả trừ thiết bị cuối cùng được kết nối.

- Kết nối chân TDO từ thiết bị cuối cùng với chân TDO của JTAG tiêu đề giao diện.

Hình 2-2 Nhiều thiết bị JTAG Cấu hình

Để lập trình nhiều thiết bị trong một JTAG chuỗi, người dùng phải sử dụng các công cụ phần mềm ISP hỗ trợ các tính năng như vậy. Trong phần mềm ISP, người dùng cần chỉ định:

- Số lượng thiết bị trong JTAG xích.

- Số bộ phận của các thiết bị và vị trí trong JTAG xích.

- JTAG hoạt động cho từng thiết bị.

- J khácTAG-thông tin liên quan như JTAG chiều rộng hướng dẫn cho từng thiết bị.

Một khi JTAG chuỗi hoa cúc được thiết lập đúng cách trên bảng mục tiêu ISP và trong phần mềm ISP, các thiết bị trong JTAG chuỗi có thể được lập trình cùng một lúc.

Những cân nhắc về thiết kế

Để thực hiện ISP trên CPLD ATF15xx, các tài nguyên cho JTAG giao diện trong ATF15xx phải được dành riêng. Do đó, bốn chân I/O cho các chân TMS, TDI, TDO và TCK phải được dành riêng cho JTAG và không thể được sử dụng làm I/O của người dùng. Số chân cho các chân này phụ thuộc vào CPLD ATF15xx nào được sử dụng và loại gói của nó. Tham khảo bảng bên dưới để biết thông tin về chân cắm. JTAG tiêu chuẩn khuyến nghị rằng các chân TMS và TDI được kéo lên cho mỗi thiết bị trong JTAG chuỗi. CPLD ATF15xx có tính năng kéo lên bên trong cho các chân này, khi được bật, sẽ tiết kiệm nhu cầu về điện trở kéo lên bên ngoài. Hơn nữa, JTAG tính năng giao diện phải được bật để thực hiện ISP trên CPLD ATF15xx. Bật JTAG giao diện yêu cầu chọn các loại thiết bị Atmel cụ thể hoặc cài đặt tùy chọn trước khi biên dịch thiết kế ATF15xx. Các quy trình này được phác thảo cho WinCUPL, ProChip Designer và POF2JED trong hướng dẫn này. Theo mặc định, tất cả các CPLD ATF15xx hoàn toàn mới đều được cung cấp cùng với JTAG giao diện được kích hoạt. Một khi tài nguyên logic cho JTAG Giao diện được bảo lưu, người dùng có thể lập trình, xác minh và xóa bất kỳ CPLD ATF15xx nào trên bo mạch mục tiêu bằng phần mềm ATMISP.

Mẹo: Mặc dù bốn JTAG chân được dành riêng cho JTAG Giao diện, người dùng có thể triển khai các hàm logic ẩn trong các macrocell liên kết với các chân này.

Bảng 3-1 ATF15xx CPLD JTAG Số pin

| JTAG Ghim | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Bật JTAG Giao diện với WinCUPL

Để kích hoạt JTAG giao diện với WinCUPL, loại thiết bị ISP ATF15xx thích hợp cần được chỉ định trước khi biên dịch thiết kế. Sau khi thiết kế được biên dịch thành công, JEDEC file với JTAG tính năng giao diện được kích hoạt được tạo ra. Khi JEDEC này file được lập trình vào ATF15xxCPLD, J của nóTAG giao diện được bật. Người dùng cũng có thể bật điện trở kéo lên bên trong TDI và TMS bằng cách đưa các câu lệnh thuộc tính sau vào thiết kế CUPL file.

- THUỘC TÍNH ATMEL {TDI_PULLUP = ON};

- THUỘC TÍNH ATMEL {TMS_PULLUP = ON};

Để ý: Nếu loại thiết bị ISP ATF15xx được sử dụng cho thiết kế sử dụng JTAG chân giao diện như chân I/O logic, WinCUPL sẽ tạo ra lỗi.

Các bước sau đây thảo luận về cách mở thiết kế hiện có trong WinCUPL, chỉ định loại thiết bị và biên dịch thiết kế.

- Trên menu chính của WinCUPL, chọn File > Mở. Chọn nguồn CUPL (.pld) file từ thư mục làm việc thích hợp.

- Chọn OK để mở nguồn PLD file.

- Trên menu chính của WinCUPL, chọn File > Lưu. Thao tác này lưu các thay đổi được thực hiện đối với nguồn file.

- Trên menu chính, chọn Options > Devices. Thao tác này sẽ mở hộp thoại Device Selection.

- Chọn thiết bị ISP ATF15xx phù hợp. Xem bảng sau để biết danh sách tất cả các loại thiết bị ATF15xx được WinCUPL hỗ trợ.

- Chọn OK để đóng menu chọn thiết bị.

- Lưu ý: Một phương pháp thay thế là chọn loại thiết bị ATF15xx phù hợp từ bảng sau và đưa nó vào phần tiêu đề của nguồn CUPL file.

- Trên menu chính của WinCUPL, chọn Run> Device Dependent Compile.

- WinCUPL biên dịch thiết kế và tạo ra bộ điều chỉnh thiết bị Atmel. Nếu thiết kế phù hợp, một JEDEC file được tạo tự động.

- Khi JEDEC file được lập trình vào thiết bị, JTAG giao diện, các chức năng kéo lên TMS và TDI tùy chọn bên trong và các mạch giữ chân tùy chọn được kích hoạt.

Ghi chú: Việc lựa chọn loại thiết bị ISP Atmel sẽ tự động kích hoạt JTAG giao diện mặc định khi Atmel WinCUPL chạy trình điều khiển thiết bị Atmel.

Nếu các thiết kế ngăn chặn việc dành tài nguyên cho JTAG giao diện hoặc ISP tùy chọn không được sử dụng, phải chọn loại thiết bị Atmel không phải ISP. Xem bảng bên dưới để biết danh sách các thiết bị. Sau đó, thiết bị có thể được lập trình lại bằng bộ lập trình thiết bị bên ngoài. Bảng bên dưới liệt kê các loại thiết bị Atmel ISP và Atmel không phải ISP cho WinCUPL.

Bảng 3-2 Loại thiết bị WinCUPL ATF15xx

| Tên thiết bị | Loại gói | Loại thiết bị WinCUPL | |

| JTAG Đã bật | JTAG Tàn tật | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Bật JTAG Giao diện với Atmel ProChip Designer

Để kích hoạt JTAG Giao diện với ProChip Designer:

- Mở dự án ProChip Designer phù hợp.

- Mở cửa sổ Tùy chọn Fitter bằng cách nhấp vào nút Atmel Fitter bên dưới Device Fitter.

- Chọn tab Thiết bị toàn cầu và sau đó kiểm tra JTAG Hộp cổng. Điện trở kéo lên bên trong TMS và TDI cũng có thể được bật bằng cách kiểm tra hộp TDI Pullup và TMS Pullup. Các hộp kiểm này được hiển thị trong hình bên dưới.

Hình 3-1 Giao diện người dùng tùy chọn lắp ghép ProChip Designer

Bật JTAG Giao diện với POF2JED

Trong POF2JED, JTAG Tùy chọn chế độ có thể được đặt thành Tự động để cho phép POF2JED xác định xem JTAG tính năng trong ATF15xx có nên được bật hay không và nó dựa trên việc JTAG được hỗ trợ trong CPLD của đối thủ cạnh tranh. Để bật JTAG trong ATF15xx CPLD bất kể JTAG được hỗ trợ trong CPLD của đối thủ cạnh tranh hay không, JTAG Tùy chọn chế độ nên được đặt thành Bật. Khi JTAG được bật trong ATF15xx, điện trở kéo lên bên trong TDI và TMS có thể được bật bằng cách kiểm tra Bật

TDI_PULLUP và Bật hộp TMS_PULLUP trong POF2JED. Xem hình bên dưới.

Hình 3-2 Giao diện người dùng POF2JED

Hướng dẫn và khuyến nghị

Chú ý: Cần chú ý thêm đến phần này khi thực hiện các hoạt động ISP trên CPLD ATF15xx. Phần này thảo luận một số JTAG Hướng dẫn, thông tin và khuyến nghị của ISP cần được lưu ý kỹ.

- Hãy chắc chắn rằng JTAG cổng cho tất cả các thiết bị trong JTAG chuỗi được kích hoạt.

- Đối với CPLD ATF15xx, JTAG cổng được bật nếu các thiết bị bị trống/xóa hoặc được lập trình bằng JTAG được bật.

- Tất cả các thiết bị Atmel ATF15xx đều được vận chuyển ở trạng thái trống/đã xóa; do đó, JTAG Cổng này được kích hoạt cho tất cả các thiết bị mới và sẵn sàng cho ISP.

- Thiết bị ATF15xx với JTAG bị vô hiệu hóa cần phải được xóa bằng cách sử dụng một thiết bị lập trình không phải ISP để kích hoạt lại JTAG cảng.

- Đảm bảo VCC vol thích hợptage được áp dụng cho từng thiết bị trong JTAG xích.

- CPLD ATF15xxAS/ASL trong các loại gói 84-PLCC, 100-TQFP và 100-PQFP: VCCINT phải nằm trong khoảng từ 4.5V đến 5.5V trong khi VCCIO có thể nằm trong khoảng từ 3.0V đến 3.6V hoặc 4.5V đến 5.5V.

- CPLD ATF15xxAS/ASL trong loại gói 44-PLCC và 44-TQFP: VCC phải nằm trong khoảng từ 4.5V đến 5.5V.

- CPLD ATF15xxASV/ASVL: VCC (VCCIO và VCCINT) phải nằm trong khoảng từ 3.0V đến 3.6V.

- VCC cho các thiết bị trong JTAG chuỗi phải được điều chỉnh và lọc đúng cách.

- Đối với CPLD ATF15xx được sử dụng trong hầu hết các ứng dụng, nên sử dụng một tụ tách ghép 0.22µF cho mỗi cặp VCC/GND.

- Nên sử dụng điểm nối đất chung cho tất cả các thiết bị trong JTAG chuỗi và JTAG phần cứng giao diện (ví dụ: Cáp tải xuống ISP ATDH1150USB).

- Nên tránh sử dụng lâu (không quá năm thiết bị) JTAG chuỗi.

- Nếu một J dàiTAG chuỗi là cần thiết, đệm tín hiệu TMS và TCK sau mỗi năm thiết bị. Nên sử dụng bộ đệm kích hoạt Schmitt.

- Bộ đệm định hình lại thời gian tăng và giảm của tín hiệu TMS và TCK.

- Cần phải tính đến độ trễ bổ sung do bộ đệm gây ra.

- Nên sử dụng điện trở kéo lên (4.7KΩ đến 10KΩ) cho tín hiệu TMS và TDI và điện trở kéo xuống cho tín hiệu TCK tại JTAG tiêu đề để ngăn các tín hiệu này trôi nổi khi chúng không được điều khiển bởi phần cứng giao diện.

- Có sẵn tùy chọn kéo lên bên trong trên TMS và TDI cho CPLD ATF15xx.

- Nên chấm dứt JTAG tín hiệu tại JTAG tiêu đề.

- Cả kết thúc chủ động và thụ động đều được chấp nhận; tuy nhiên, kết thúc thụ động được ưa chuộng hơn.

- Nó làm giảm tiếng chuông do độ dài của cáp/PCB.

- Việc chấm dứt là quan trọng nhất đối với TMS và TCK.

- Nên khuyến cáo rằng tất cả các đầu vào và I/O của các thiết bị trong JTAG chuỗi, ngoại trừ JTAG chân cắm phải ở trạng thái tĩnh khi CPLD ATF15xx được lập trình để giảm thiểu tiếng ồn.

- Khi sử dụng một trong các bo mạch phát triển/lập trình Atmel ATF15xx, phải TẮT nguồn điện của bo mạch khi thay đổi vị trí của các cầu nối chọn VCC.

- Đối với CPLD ATF15xx, JTAG ISP khả dụng khi bộ phận ở chế độ Tắt nguồn điều khiển bằng chốt hoặc khi thiết bị “công suất thấp” đang ở chế độ ngủ.

- Trạng thái thiết bị sau khi ISP bị ngắt:

- Nếu ISP bị gián đoạn, tất cả các chân I/O đều có trạng thái ba trạng thái bất kể trạng thái của mạch Pin-keeper.

- Ngăn chặn các thiết bị được lập trình một phần gây ra xung đột bus với các thiết bị khác trên bảng mạch.

- Trong quá trình lập trình ISP, tất cả các chân I/O đều ở một trong các điều kiện sau:

- Trạng thái trở kháng cao:

- Khi một thiết bị trống/bị xóa được lập trình.

- Khi thiết bị được lập trình lại với mạch Pin-keeper bị vô hiệu hóa.

- Ngăn ngừa xung đột bus với các thiết bị bên ngoài giao tiếp với CPLD ATF15xx trên bảng mạch.

- Kết nối yếu với trạng thái trước đó:

- Khi thiết bị đã lập trình được lập trình lại với mạch Pin-keeper được kích hoạt.

- Các chân I/O giữ nguyên mức logic trước ISP.

- Ngăn chặn ISP ảnh hưởng đến hoạt động của các thiết bị khác trên bo mạch hệ thống.

- Việc sử dụng nhiều JTAG không nên sử dụng nhiều chuỗi trên một bảng.

- Các thiết bị có thể tương tác giữa các J khác nhauTAG chuỗi.

- Bảng chỉ hoạt động khi tất cả các thiết bị trong tất cả JTAG chuỗi được lập trình thành công.

- Nếu lập trình không thành công đối với ít nhất một thiết bị trong chuỗi trong khi các thiết bị khácTAG chuỗi đã được lập trình thành công:

- Atmel hoặc các thiết bị khác trên bo mạch có thể bị hỏng do sự cố tranh chấp bus có thể xảy ra đối với đầu ra có thể có ba trạng thái.

- Trạng thái hoạt động của bo mạch hệ thống không được xác định; do đó, hoạt động không chính xác có thể xảy ra.

- Chèn mạch hoạt động giữa JTAG tiêu đề và JTAG không khuyến khích sử dụng thiết bị trong chuỗi. Nếu mạch hoạt động bị trục trặc, có thể gây ra sự cố lập trình/xác minh.

- Việc sử dụng hỗn hợp voltagthiết bị e JTAG không nên sử dụng xích.

- Đây là JTAG chuỗi với các thiết bị sử dụng VCC vol khác nhautages và/hoặc giao diện voltagnghĩa là

- Giao diện tậptagCác mức e (VIL, VIH, VOL, VOH) cho các thiết bị 5.0V có thể không tương thích với vol giao diệntagmức điện áp cho thiết bị 3.0V.

- Nếu ATMISP có vấn đề giao tiếp với JTAG chuỗi phần cứng thiết bị, hãy thử chạy Tự hiệu chuẩn hoặc Hiệu chuẩn thủ công để giảm tần số của JTAG tín hiệu.

- Đảm bảo đèn LED trên cáp ATDH1150USB được bật và có màu xanh lá cây trước khi bắt đầu lập trình. Đảm bảo cáp tải xuống ISP có thể giao tiếp đúng cách với phần mềm ATMISP.

- Đảm bảo VCC vol thích hợptage được áp dụng cho cáp ATDH1150USB.

- VCC được sử dụng bởi thiết bị đầu tiên trong JTAG chuỗi phải được cung cấp cho cáp ATDH1150USB thông qua chân 4 của J 10 chânTAG tiêu đề.

- Đối với CPLD ATF15xx có VCCINT và VCCIO riêng biệt, nên sử dụng VCCIO cho cáp ATDH1150USB.

Thông tin đặt hàng

| Mã đặt hàng | Sự miêu tả |

| ATF15xx-DK3-U | Bộ phát triển/lập trình CPLD (bao gồm ATF15xxDK3-SAA44 và ATDH1150USB hoặc ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | Bảng điều hợp ổ cắm TQFP 100 chân cho bảng DK3 |

| ATF15xxDK3-SAJ44 | Bảng điều hợp ổ cắm PLCC 44 chân cho bảng DK3 |

| ATF15xxDK3-SAJ84 | Bảng điều hợp ổ cắm PLCC 84 chân cho bảng DK3 |

| ATF15xxDK3-SAA44 | Bảng điều hợp ổ cắm TQFP 44 chân cho bảng DK3 |

| ATDH1150USB | Atmel ATF15xx CPLD dựa trên USB JTAG Cáp tải xuống ISP |

Lịch sử sửa đổi

| Tiến sĩ. Rev. | Ngày | Bình luận |

| A | 12/2015 | Phát hành tài liệu ban đầu. |

THÔNG TIN LIÊN HỆ

Tập đoàn Atmel

- Ổ đĩa công nghệ 1600, San Jose, CA 95110 Hoa Kỳ

- T: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_Hướng dẫn sử dụng-12/2015

Atmel®, logo Atmel và các kết hợp của chúng, Enabling Unlimited Possibilities® và các nhãn hiệu khác là nhãn hiệu đã đăng ký hoặc nhãn hiệu của Atmel Corporation tại Hoa Kỳ và các quốc gia khác. Các thuật ngữ và tên sản phẩm khác có thể là nhãn hiệu của những người khác.

KHUYẾN CÁO: Thông tin trong tài liệu này được cung cấp liên quan đến các sản phẩm của Atmel. Không có giấy phép, rõ ràng hay ngụ ý, bởi estoppel hoặc cách khác, đối với bất kỳ quyền sở hữu trí tuệ nào được cấp bởi tài liệu này hoặc liên quan đến việc bán các sản phẩm Atmel. NGOẠI TRỪ KHI ĐƯỢC ĐẶT RA TRONG ĐIỀU KHOẢN VÀ ĐIỀU KIỆN CỦA ATMEL TRÊN ATMEL WEBSITE, ATMEL KHÔNG CHỊU BẤT KỲ TRÁCH NHIỆM NÀO VÀ TỪ CHỐI BẤT KỲ BẢO HÀNH RÕ RÀNG, NGỤ Ý HOẶC THEO LUẬT ĐỊNH LIÊN QUAN ĐẾN CÁC SẢN PHẨM CỦA MÌNH, BAO GỒM NHƯNG KHÔNG GIỚI HẠN Ở, BẢO HÀNH NGỤ Ý VỀ KHẢ NĂNG THƯƠNG MẠI, SỰ PHÙ HỢP CHO MỘT MỤC ĐÍCH CỤ THỂ HOẶC KHÔNG VI PHẠM. Trong mọi trường hợp, ATMEL KHÔNG CHỊU TRÁCH NHIỆM ĐỐI VỚI BẤT KỲ THIỆT HẠI TRỰC TIẾP, GIÁN TIẾP, HẬU QUẢ, TRỪNG PHẠT, ĐẶC BIỆT HOẶC NGẪU NHIÊN NÀO (BAO GỒM NHƯNG KHÔNG GIỚI HẠN Ở THIỆT HẠI VỀ MẤT MÁT VÀ LỢI NHUẬN, GIÁN ĐOẠN KINH DOANH HOẶC MẤT THÔNG TIN) PHÁT SINH TỪ VIỆC SỬ DỤNG HOẶC KHÔNG THỂ SỬ DỤNG TÀI LIỆU NÀY, NGAY CẢ KHI ATMEL ĐÃ ĐƯỢC THÔNG BÁO VỀ KHẢ NĂNG XẢY RA NHỮNG THIỆT HẠI NHƯ VẬY. Atmel không đưa ra bất kỳ tuyên bố hoặc bảo đảm nào về tính chính xác hoặc đầy đủ của nội dung tài liệu này và có quyền thay đổi thông số kỹ thuật và mô tả sản phẩm bất kỳ lúc nào mà không cần thông báo. Atmel không cam kết cập nhật thông tin có trong tài liệu này. Trừ khi có quy định cụ thể khác, các sản phẩm của Atmel không phù hợp và không được sử dụng trong các ứng dụng ô tô. Các sản phẩm của Atmel không nhằm mục đích, không được ủy quyền hoặc bảo đảm để sử dụng làm thành phần trong các ứng dụng nhằm hỗ trợ hoặc duy trì sự sống. TUYÊN BỐ MIỄN TRỪ TRÁCH NHIỆM VỀ AN TOÀN QUAN TRỌNG, QUÂN SỰ VÀ Ô TÔ: Các sản phẩm Atmel không được thiết kế cho và sẽ không được sử dụng liên quan đến bất kỳ ứng dụng nào mà sự cố của các sản phẩm đó có thể dự kiến sẽ dẫn đến thương tích cá nhân đáng kể hoặc tử vong (“Các ứng dụng quan trọng về an toàn”) mà không có sự đồng ý bằng văn bản cụ thể của sĩ quan Atmel. Các ứng dụng quan trọng về an toàn bao gồm, nhưng không giới hạn ở, các thiết bị và hệ thống hỗ trợ sự sống, thiết bị hoặc hệ thống để vận hành các cơ sở hạt nhân và hệ thống vũ khí. Các sản phẩm Atmel không được thiết kế hoặc không có ý định sử dụng trong các ứng dụng hoặc môi trường quân sự hoặc hàng không vũ trụ trừ khi được Atmel chỉ định cụ thể là cấp độ quân sự. Các sản phẩm Atmel không được thiết kế hoặc không có ý định sử dụng trong các ứng dụng ô tô trừ khi được Atmel chỉ định cụ thể là cấp độ ô tô.

Tài liệu / Tài nguyên

|

Thiết bị logic lập trình phức hợp Atmel ATF15xx [tập tin pdf] Hướng dẫn sử dụng ATF15xx, Thiết bị logic lập trình phức hợp ATF15xx, Thiết bị logic lập trình phức hợp, Thiết bị logic lập trình, Thiết bị logic, Thiết bị |