Perangkat Logika Terprogram Kompleks Atmel ATF15xx

Spesifikasi

- Nama Produk: Pemrograman Dalam Sistem Atmel ATF15xx

- Model: ATF15xx

- Tipe: Perangkat Logika Terprogram Kompleks (CPLD)

- Metode Pemrograman: Pemrograman Dalam Sistem (ISP)

- Antarmuka: JTAG Antarmuka ISP

- Produsen: Atmel

Tanya Jawab Umum

T: Dapatkah saya menggunakan perangkat lunak pemrograman pihak ketiga dengan CPLD ATF15xx?

A: Ya, selama perangkat lunak mendukung algoritma pemrograman dan JTAG instruksi yang diperlukan untuk CPLD ATF15xx.

T: Apakah mungkin untuk memprogram beberapa CPLD ATF15xx secara bersamaan?

A: Ya, JTAG Antarmuka ISP mendukung pemrograman beberapa perangkat untuk pemrograman beberapa CPLD sekaligus secara efisien.

Perkenalan

- Perangkat Logika Terprogram Kompleks (CPLD) Atmel® ATF15xx dengan arsitektur Logic Doubling® mendukung Pemrograman Dalam Sistem (ISP) melalui IEEE Std. 1149.1 Joint Test Action Group (JTAG) antarmuka. Fitur ini meningkatkan fleksibilitas pemrograman dan memberikan manfaat dalam berbagai fase; pengembangan produk, produksi, dan penggunaan lapangan. Panduan pengguna ini menjelaskan metode desain dan persyaratan untuk mengimplementasikan ISP pada CPLD ATF15xx dengan dukungan ISP seperti yang tercantum di bawah ini:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Fitur dan Manfaat

Pemrograman dalam sistem memungkinkan pemrograman dan pemrograman ulang perangkat ISP setelah dipasang pada Papan Sirkuit Cetak (PCB). Hal ini menghilangkan langkah penanganan ekstra yang diperlukan dalam proses produksi untuk memprogram perangkat pada pemrogram perangkat eksternal sebelum dipasang pada PCB. Menghilangkan langkah ini mengurangi kemungkinan kerusakan kabel halus pada perangkat pemasangan permukaan dengan jumlah pin tinggi atau kerusakan perangkat melalui pelepasan muatan listrik statis (ESD) selama alur pemrograman. ISP juga memungkinkan pengguna untuk membuat perubahan desain dan pemutakhiran lapangan tanpa harus melepaskan perangkat ISP dari PCB. Lebih jauh, hal ini juga memungkinkan penggunaan mikrokontroler tertanam atau penguji dalam sirkuit untuk melakukan operasi pemrograman dalam sistem pada perangkat ISP dan mengintegrasikan operasi pemrograman ini ke dalam alur produksi papan sirkuit.

Sistem Pemrograman Dalam Sistem

Tiga komponen penting sistem ISP untuk CPLD ATF15xx adalah:

Perangkat lunak

Implementasi algoritma pemrograman, serta pembangkitan JTAG instruksi dan data untuk perangkat ISP target. Ini bisa berupa program perangkat lunak yang berjalan pada PC, mikrokontroler tertanam, atau peralatan pengujian dalam sirkuit.

Perangkat Keras Antarmuka

Saluran komunikasi antara perangkat lunak ISP dan perangkat ISP pada papan target. Ini bisa berupa kabel unduhan ISP atau programmer dari Atmel atau vendor pihak ketiga, peralatan pengujian dalam sirkuit, atau koneksi antara mikrokontroler tertanam dan perangkat ISP pada PCB.

Papan Target

Papan sirkuit yang berisi perangkat ISP di JTAG rantai. Ini bisa berupa papan Pengembangan/Pemrogram ATF15xx CPLD dari Atmel atau papan sirkuit yang dirancang khusus dengan J yang sesuaiTAG koneksi ke perangkat keras antarmuka.

Selain ketiga komponen ini, JEDEC file diperlukan untuk memprogram CPLD ATF15xx. JEDEC ini file dapat dibuat dengan menyusun desain file menggunakan perangkat lunak pengembangan yang mendukung CPLD ATF15xx seperti Atmel WinCUPL dan Atmel ProChip Designer. Atmel juga menyediakan utilitas perangkat lunak penerjemah, POF2JED.exe, yang mengubah output file dari format pemrograman pesaing ke JEDEC file kompatibel dengan ATF15xx CPLD. Untuk informasi lebih lanjut tentang utilitas ini, silakan lihat catatan aplikasi Atmel, “Konversi Keluarga Produk ATF15xx”, tersedia di Atmel websitus. Setelah JEDEC files dibuat untuk semua CPLD ATF15xx, mereka dapat diprogram pada papan target. CPLD ATF15xx dapat diprogram oleh sistem pemrograman dalam sistem berikut:

- Sistem Pemrograman Dalam Sistem ATF15xx

- Mikrokontroler tertanam

- Penguji dalam sirkuit

Sistem Pemrograman Dalam Sistem Atmel ATF15xx

Untuk pemrograman dalam sistem CPLD ATF15xx, perangkat lunak ISP, kabel unduhan, dan perangkat pengembangan/pemrogram tersedia dari Atmel dan dijelaskan pada bagian di bawah.

Perangkat Lunak ISP

Perangkat lunak Atmel ATF15xx ISP, ATMISP, adalah sarana utama untuk mengimplementasikan JTAG pemrograman dalam sistem pada CPLD ATF15xx. ATMISP berjalan pada PC host berbasis Windows dan menerapkan pemrograman dalam sistem CPLD ATF15xx pada sistem perangkat keras ISP target atau menghasilkan Serial Vector Format (.SVF) file untuk digunakan oleh Peralatan Pengujian Otomatis (ATE) untuk memprogram CPLD ATF15xx pada sistem target. ATMISP pertama-tama memperoleh semua informasi yang diperlukan dari pengguna tentang JTAG rantai perangkat dalam sistem target. Kemudian menjalankan perintah J yang sesuaiTAG Instruksi ISP ke JTAG rantai perangkat dalam sistem target menurut JTAG informasi rantai perangkat yang ditentukan oleh pengguna melalui port USB atau LPT PC. Informasi lebih lanjut tentang perangkat lunak Atmel ATMISP tersedia di www.atmel.com/tools/ATMISP.aspx.

Kabel Unduhan ISP

Kabel Unduhan ISP berbasis USB Atmel ATF15xx, ATDH1150USB, terhubung ke port USB standar komputer host di satu sisi dan ke JTAG header dari papan sirkuit target di sisi lain. Ini mentransfer JTAG instruksi dan data yang dihasilkan oleh ATMISP yang berjalan pada PC host ke perangkat ISP pada papan sirkuit target. Informasi lebih lanjut tentang kabel ATDH1150USB tersedia di www.atmel.com/tools/ATDH1150USB.aspx.

Pengembangan/Programmer

Kit Pengembangan/Pemrogram Atmel ATF15xx, ATF15xx-DK3-U, adalah sistem pengembangan lengkap dan pemrogram ISP untuk CPLD ATF15xx. Kit ini menyediakan cara yang sangat cepat dan mudah bagi para desainer untuk mengembangkan prototipe dan mengevaluasi desain baru dengan CPLD ISP ATF15xx. Dengan tersedianya berbagai papan adaptor soket untuk mendukung sebagian besar jenis paket yang ditawarkan dalam CPLD ATF15xx, kit ini dapat digunakan sebagai pemrogram ISP untuk memprogram CPLD ISP ATF15xx dalam sebagian besar jenis paket yang tersedia melalui JTAG antarmuka. Informasi lebih lanjut tentang kit Atmel ATF15xx-DK3-U tersedia di www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Sistem Mikrokontroler Tertanam

Algoritma pemrograman dan JTAG instruksi untuk CPLD ATF15xx dapat diimplementasikan dalam mikrokontroler atau mikroprosesor, yang kemudian dapat digunakan untuk memprogram CPLD ATF15xx pada papan target. Salah satu metode yang mungkin adalah mengekstrak semua J yang relevanTAG informasi protokol (yaitu JTAG instruksi dan data) dari SVF file dihasilkan oleh perangkat lunak ATMISP, dan kemudian menggunakan informasi ini untuk mengimplementasikan kode untuk mikrokontroler atau mikroprosesor yang akan menghasilkan JTAG sinyal untuk perangkat ISP di JTAG rantai. Pendekatan ini paling cocok untuk sistem yang sudah memiliki mikrokontroler atau mikroprosesor tertanam, dan ini menghilangkan penggunaan perangkat lunak pemrograman dan perangkat keras eksternal dalam sistem.

Sistem Pengujian Dalam Sirkuit

CPLD ATF15xx dapat diprogram pada papan sirkuit target melalui JTAG antarmuka selama pengujian papan sirkuit menggunakan penguji dalam sirkuit. Umumnya, SVF file yang dihasilkan oleh ATMISP harus berisi semua J yang relevanTAG informasi pemrograman dalam sistem yang dibutuhkan penguji dalam sirkuit untuk memprogram CPLD ATF15xx pada papan sirkuit target. Pendekatan ini memungkinkan integrasi langkah pemrograman ke dalam pengujiantage dari aliran produksi.

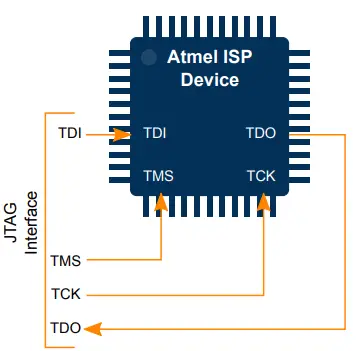

JTAG Antarmuka ISP

ISP untuk CPLD ATF15xx diimplementasikan menggunakan IEEE 1149.1 Std. JTAG antarmuka. Antarmuka ini dapat digunakan untuk menghapus, memprogram, dan memverifikasi CPLD ATF15xx. JTAG antarmuka adalah antarmuka serial yang terdiri dari sinyal TCK, TMS, TDI, dan TDO dan JTAG Pengontrol Test Access Port (TAP). Pin TCK adalah input clock untuk JTAG Pengontrol TAP dan untuk menggeser masuk/keluar JTAG instruksi dan data. Pin TDI adalah input data serial. Pin ini digunakan untuk menggeser instruksi pemrograman dan data ke perangkat ISP. Pin TDO adalah output data serial. Pin ini digunakan untuk menggeser keluar data dari perangkat ISP. Pin TMS adalah pin pemilihan mode. Pin ini mengontrol status JTAG Pengontrol TAP. JTAG pin antarmuka CPLD ATF15xx pada papan target ISP harus dihubungkan ke perangkat keras antarmuka ISP (misalnya kabel unduhan ISP) biasanya melalui header 10-pin. Perangkat keras antarmuka ISP juga perlu dihubungkan ke PC host yang menjalankan perangkat lunak ISP. Perangkat keras antarmuka ISP membangun komunikasi antara perangkat lunak ISP dan perangkat ISP, dan memungkinkan perangkat lunak ISP untuk mentransfer instruksi pemrograman dan data dari PC host ke CPLD ATF15xx. CPLD ATF15xx dengan JTAG fitur yang diaktifkan sepenuhnya JTAG kompatibel dan juga mendukung operasi Uji Pemindaian Batas (BST) yang diperlukan yang ditentukan dalam JTAG standar. CPLD ATF15xx dapat dikonfigurasi untuk menjadi bagian dari JTAG Rantai BST dengan J lainnyaTAG perangkat untuk pengujian sirkuit pada papan sistem. Dengan fitur ini, CPLD ATF15xx dapat diuji pada papan sirkuit bersama dengan JTAG-perangkat yang didukung tanpa harus melakukan pengujian di tempat.

Pemrograman Perangkat Tunggal

JTAG Antarmuka ISP dapat dikonfigurasi untuk memprogram satu CPLD ATF15xx.TAG konfigurasi untuk satu perangkat ditunjukkan pada gambar di bawah ini. Ketika CPLD ATF15xx dikonfigurasi dengan cara ini, sebuah register muncul di antara pin TDI dan TDO perangkat. Ukuran register bergantung pada JTAG lebar instruksi dan data yang digeser untuk instruksi tersebut. Gambar 2-1 JTAG Perangkat

Pemrograman Beberapa Perangkat

CPLD ATF15xx dapat dikonfigurasikan sebagai bagian dari rangkaian berantai beberapa JTAG-perangkat yang didukung seperti dijelaskan di bawah ini dan juga ditunjukkan pada gambar berikut.

- Hubungkan pin TMS dan TCK untuk setiap perangkat di JTAG rantai ke pin TMS dan TCK dari JTAG header antarmuka pada papan sirkuit.

- Hubungkan pin TDI dari perangkat pertama ke pin TDI dari JTAG judul antarmuka.

- Hubungkan pin TDO dari perangkat pertama ke pin TDI dari perangkat berikutnya. Lanjutkan proses ini hingga semua kecuali yang terakhir terhubung.

- Hubungkan pin TDO dari perangkat terakhir ke pin TDO dari JTAG judul antarmuka.

Gambar 2-2 Beberapa Perangkat JTAG Konfigurasi

Untuk memprogram beberapa perangkat dalam JTAG rantai, pengguna harus menggunakan perangkat lunak ISP yang mendukung fitur tersebut. Dalam perangkat lunak ISP, pengguna perlu menentukan:

- Jumlah perangkat di JTAG rantai.

- Nomor bagian perangkat dan posisi dalam JTAG rantai.

- JTAG operasi untuk setiap perangkat.

- J LainnyaTAG-informasi terkait seperti JTAG lebar instruksi untuk setiap perangkat.

Suatu ketika JTAG rantai daisy diatur dengan benar pada papan target ISP dan dalam perangkat lunak ISP, perangkat di JTAG rantai dapat diprogram pada saat yang sama.

Pertimbangan Desain

Untuk melakukan ISP pada CPLD ATF15xx, sumber daya untuk JTAG antarmuka di ATF15xx harus dicadangkan. Oleh karena itu, empat pin I/O untuk pin TMS, TDI, TDO, dan TCK harus dicadangkan untuk JTAG dan tidak dapat digunakan sebagai I/O pengguna. Nomor pin untuk pin ini bergantung pada ATF15xx CPLD yang digunakan dan jenis paketnya. Lihat tabel di bawah ini untuk informasi pinout. JTAG standar merekomendasikan agar pin TMS dan TDI ditarik ke atas untuk setiap perangkat di JTAG rantai. CPLD ATF15xx memiliki fitur pull-up internal untuk pin ini yang, jika diaktifkan, menghemat kebutuhan akan resistor pull-up eksternal. Lebih jauh, JTAG Fitur antarmuka harus diaktifkan untuk menjalankan ISP pada CPLD ATF15xx. Mengaktifkan JTAG antarmuka memerlukan pemilihan jenis perangkat Atmel tertentu atau pengaturan opsi sebelum mengkompilasi desain ATF15xx. Prosedur ini diuraikan untuk WinCUPL, ProChip Designer, dan POF2JED dalam panduan ini. Secara default, semua CPLD ATF15xx baru dikirimkan dengan JTAG antarmuka diaktifkan. Setelah sumber daya logika untuk JTAG antarmuka dicadangkan, pengguna dapat memprogram, memverifikasi, dan menghapus CPLD ATF15xx apa pun pada papan target menggunakan perangkat lunak ATMISP.

Tip:Meskipun keempat JTAG pin dicadangkan untuk JTAG antarmuka, pengguna dapat mengimplementasikan fungsi logika terpendam dalam sel makro yang terkait dengan pin ini.

Tabel 3-1 ATF15xx CPLD JTAG Nomor Pin

| JTAG Pin | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Aktifkan JTAG Antarmuka dengan WinCUPL

Untuk mengaktifkan JTAG antarmuka dengan WinCUPL, tipe perangkat ISP ATF15xx yang sesuai perlu ditentukan sebelum desain dikompilasi. Setelah desain berhasil dikompilasi, JEDEC file dengan JTAG fitur antarmuka yang diaktifkan dihasilkan. Ketika JEDEC ini file diprogram ke dalam ATF15xxCPLD, JTAG Antarmuka diaktifkan. Pengguna juga dapat mengaktifkan resistor pull-up internal TDI dan TMS dengan menyertakan pernyataan properti berikut dalam desain CUPL file.

- PROPERTI ATMEL {TDI_PULLUP = AKTIF};

- PROPERTI ATMEL {TMS_PULLUP = AKTIF};

Melihat:Jika tipe perangkat ISP ATF15xx digunakan untuk desain yang menggunakan JTAG pin antarmuka sebagai pin I/O logika, WinCUPL menghasilkan kesalahan.

Langkah-langkah berikut membahas cara membuka desain yang ada di WinCUPL, menentukan jenis perangkat, dan mengompilasi desain.

- Pada menu utama WinCUPL, pilih File > Buka. Pilih sumber CUPL (.pld) file dari direktori kerja yang sesuai.

- Pilih OK untuk membuka sumber PLD file.

- Pada menu utama WinCUPL, pilih File > Simpan. Ini menyimpan perubahan yang dibuat pada sumber file.

- Pada menu utama, pilih Opsi > Perangkat. Ini akan membuka kotak dialog Pemilihan Perangkat.

- Pilih perangkat ISP ATF15xx yang sesuai. Lihat tabel berikut untuk daftar semua jenis perangkat ATF15xx yang didukung oleh WinCUPL.

- Pilih OK untuk menutup menu pemilihan perangkat.

- Catatan: Metode alternatif adalah memilih jenis perangkat ATF15xx yang sesuai dari tabel berikut dan memasukkannya di bagian header sumber CUPL file.

- Pada menu utama WinCUPL, pilih Jalankan> Kompilasi Bergantung Perangkat.

- WinCUPL mengkompilasi desain dan memunculkan Atmel device fitter. Jika desainnya cocok, JEDEC file secara otomatis dibuat.

- Ketika JEDEC file diprogram ke dalam perangkat, JTAG antarmuka, pull-up TMS dan TDI internal opsional, dan sirkuit penjaga pin opsional diaktifkan.

Catatan:Memilih jenis perangkat Atmel ISP secara otomatis mengaktifkan JTAG antarmuka secara default saat Atmel WinCUPL menjalankan Atmel device fitter.

Jika desain mencegah reservasi sumber daya untuk JTAG Jika antarmuka atau ISP tidak digunakan secara opsional, tipe perangkat Atmel non-ISP harus dipilih. Lihat tabel di bawah untuk daftar perangkat. Perangkat kemudian dapat diprogram ulang menggunakan pemrogram perangkat eksternal. Tabel di bawah mencantumkan tipe perangkat Atmel ISP dan Atmel non-ISP untuk WinCUPL.

Tabel 3-2 Tipe Perangkat WinCUPL ATF15xx

| Nama Perangkat | Tipe Paket | Tipe Perangkat WinCUPL | |

| JTAG Diaktifkan | JTAG Dengan disabilitas | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Aktifkan JTAG Antarmuka dengan Atmel ProChip Designer

Untuk mengaktifkan JTAG antarmuka dengan ProChip Designer:

- Buka proyek ProChip Designer yang sesuai.

- Buka jendela Fitter Options dengan mengklik tombol Atmel Fitter di bawah Device Fitter.

- Pilih tab Perangkat Global lalu centang JTAG Kotak port. Resistor pull-up internal TMS dan TDI juga dapat diaktifkan dengan mencentang kotak TDI Pullup dan TMS Pullup. Kotak centang ini ditunjukkan pada gambar di bawah.

Gambar 3-1 Antarmuka Pengguna Opsi Fitter ProChip Designer

Aktifkan JTAG Antarmuka dengan POF2JED

Dalam POF2JED, JTAG Opsi mode dapat diatur ke Otomatis untuk membiarkan POF2JED menentukan apakah JTAG fitur di ATF15xx harus diaktifkan atau tidak, dan itu didasarkan pada apakah JTAG didukung dalam CPLD pesaing. Untuk mengaktifkan JTAG di CPLD ATF15xx terlepas dari apakah JTAG didukung dalam CPLD pesaing atau tidak, JTAG Opsi mode harus diatur ke Aktif. Saat JTAG diaktifkan di ATF15xx, resistor pull-up internal TDI dan TMS dapat diaktifkan dengan mencentang Enable

Kotak TDI_PULLUP dan Enable TMS_PULLUP di POF2JED. Lihat gambar di bawah.

Gambar 3-2 Antarmuka Pengguna POF2JED

Pedoman dan Rekomendasi

Perhatian: Perhatian ekstra harus diberikan pada bagian ini ketika melakukan operasi ISP pada CPLD ATF15xx. Bagian ini membahas beberapa JTAG Pedoman, informasi, dan rekomendasi ISP yang harus diperhatikan dengan baik.

- Pastikan JTAG port untuk semua perangkat di JTAG rantai diaktifkan.

- Untuk CPLD ATF15xx, JTAG port diaktifkan jika perangkat kosong/terhapus atau diprogram dengan JTAG diaktifkan.

- Semua perangkat Atmel ATF15xx dikirim dalam keadaan kosong/terhapus; oleh karena itu, JTAG Port diaktifkan untuk semua perangkat baru dan siap untuk ISP.

- Perangkat ATF15xx dengan JTAG dinonaktifkan perlu dihapus menggunakan programmer perangkat non-ISP untuk mengaktifkan kembali JTAG pelabuhan.

- Pastikan volume VCC yang tepattage diterapkan pada masing-masing perangkat di JTAG rantai.

- CPLD ATF15xxAS/ASL dalam tipe paket 84-PLCC, 100-TQFP, dan 100-PQFP: VCCINT harus antara 4.5V dan 5.5V sedangkan VCCIO dapat antara 3.0V dan 3.6V atau 4.5V dan 5.5V.

- CPLD ATF15xxAS/ASL dalam tipe paket 44-PLCC dan 44-TQFP: VCC harus antara 4.5V hingga 5.5V.

- CPLD ATF15xxASV/ASVL: VCC (VCCIO dan VCCINT) harus antara 3.0V hingga 3.6V.

- VCC untuk perangkat di JTAG rantai harus diatur dan disaring dengan benar.

- Untuk CPLD ATF15xx yang digunakan di sebagian besar aplikasi, disarankan untuk menggunakan satu kapasitor decoupling 0.22µF untuk setiap pasangan VCC/GND.

- Disarankan untuk menggunakan ground umum untuk semua perangkat di JTAG rantai dan JTAG perangkat keras antarmuka (yaitu Kabel Unduhan ISP ATDH1150USB).

- Disarankan untuk menghindari penggunaan J yang lama (tidak lebih dari lima perangkat)TAG rantai.

- Jika J panjangTAG rantai diperlukan, buffer sinyal TMS dan TCK setelah setiap perangkat kelima. Penggunaan buffer pemicu Schmitt lebih disukai.

- Buffer membentuk kembali waktu naik dan turunnya sinyal TMS dan TCK.

- Perlu mempertimbangkan penundaan tambahan yang dialami oleh buffer.

- Disarankan untuk menggunakan resistor pull-up (4.7KΩ hingga 10KΩ) untuk sinyal TMS dan TDI dan resistor pull-down untuk sinyal TCK di JTAG header untuk mencegah sinyal-sinyal ini mengambang saat tidak digerakkan oleh perangkat keras antarmuka.

- Pull-up internal opsional pada TMS dan TDI tersedia untuk CPLD ATF15xx.

- Disarankan untuk menghentikan JTAG sinyal di JTAG kepala.

- Baik penghentian aktif maupun pasif dapat diterima; namun, penghentian pasif lebih disukai.

- Mengurangi dering akibat panjang jalur kabel/PCB.

- Penghentian merupakan hal yang paling kritis untuk TMS dan TCK.

- Disarankan agar semua input dan I/O perangkat di JTAG rantai, kecuali JTAG pin, harus dalam keadaan statis saat CPLD ATF15xx diprogram untuk meminimalkan kebisingan.

- Saat menggunakan salah satu papan pengembangan/pemrogram Atmel ATF15xx, daya ke papan harus dimatikan saat posisi jumper pemilihan VCC diubah.

- Untuk CPLD ATF15xx, JTAG ISP tersedia saat komponen berada dalam mode Daya-turun yang dikontrol Pin atau saat perangkat “daya rendah” dalam keadaan tidur.

- Keadaan perangkat setelah gangguan ISP:

- Jika ISP terputus, semua pin I/O bersifat tri-stated tanpa mempedulikan kondisi sirkuit Pin-keeper.

- Mencegah perangkat yang terprogram sebagian menyebabkan pertentangan bus dengan perangkat lain pada papan sirkuit.

- Selama pemrograman ISP, semua pin I/O berada dalam salah satu kondisi berikut:

- Keadaan impedansi tinggi:

- Ketika perangkat kosong/terhapus diprogram.

- Ketika perangkat diprogram ulang dengan sirkuit Pin-keeper dinonaktifkan.

- Mencegah pertentangan bus dengan perangkat eksternal yang berinteraksi dengan CPLD ATF15xx pada papan sirkuit.

- Terikat lemah pada kondisi sebelumnya:

- Ketika perangkat yang diprogram diprogram ulang dengan sirkuit Pin-keeper diaktifkan.

- Pin I/O menyimpan level logika sebelumnya sebelum ISP.

- Mencegah ISP memengaruhi pengoperasian perangkat lain pada papan sistem.

- Penggunaan beberapa JTAG rantai pada satu papan tidak disarankan.

- Perangkat dapat berinteraksi antara J yang berbedaTAG rantai.

- Papan hanya berfungsi ketika semua perangkat di semua JTAG rantai diprogram dengan sukses.

- Jika pemrograman gagal untuk setidaknya satu perangkat dalam rantai sementara J lainnyaTAG rantai berhasil diprogram:

- Baik Atmel maupun perangkat lain di dalamnya dapat rusak karena kemungkinan masalah perebutan bus untuk keluaran tri-stateable.

- Status operasional papan sistem tidak ditentukan; dan oleh karena itu, operasi fungsional yang salah dapat terjadi.

- Memasukkan sirkuit aktif antara JTAG header dan JTAG perangkat dalam rantai tidak disarankan. Jika sirkuit aktif tidak berfungsi, hal itu dapat menyebabkan masalah pemrograman/verifikasi.

- Penggunaan volume campurantagperangkat e JTAG rantai tidak disarankan.

- Ini adalah JTAG rantai dengan perangkat yang menggunakan volume VCC yang berbedatages dan/atau antarmuka voltagyaitu.

- Antarmuka jilidtagLevel e (VIL, VIH, VOL, VOH) untuk perangkat 5.0V mungkin tidak kompatibel dengan antarmuka voltaglevel e untuk perangkat 3.0V.

- Jika ATMISP memiliki masalah dalam berkomunikasi dengan JTAG rantai perangkat keras perangkat, coba jalankan Kalibrasi Sendiri atau Kalibrasi Manual untuk menurunkan frekuensi JTAG sinyal.

- Pastikan lampu LED pada kabel ATDH1150USB menyala dan berwarna hijau sebelum memulai pemrograman. Pastikan kabel unduhan ISP dapat berkomunikasi dengan baik dengan perangkat lunak ATMISP.

- Pastikan volume VCC yang tepattage diterapkan pada kabel ATDH1150USB.

- VCC yang digunakan oleh perangkat pertama di JTAG rantai harus disuplai ke kabel ATDH1150USB melalui pin 4 dari 10-pin JTAG kepala.

- Untuk CPLD ATF15xx dengan VCCINT dan VCCIO terpisah, VCCIO harus digunakan untuk kabel ATDH1150USB.

Informasi Pemesanan

| Kode Pemesanan | Keterangan |

| ATF15xx-DK3-U | Kit Pengembangan/Pemrogram CPLD (termasuk ATF15xxDK3-SAA44 dan ATDH1150USB atau ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | Papan Adaptor Soket TQFP 100-pin untuk Papan DK3 |

| ATF15xxDK3-SAJ44 | Papan Adaptor Soket PLCC 44-pin untuk Papan DK3 |

| ATF15xxDK3-SAJ84 | Papan Adaptor Soket PLCC 84-pin untuk Papan DK3 |

| ATF15xxDK3-SAA44 | Papan Adaptor Soket TQFP 44-pin untuk Papan DK3 |

| ATDH1150USB | Atmel ATF15xx CPLD berbasis USB JTAG Kabel Unduhan ISP |

Riwayat Revisi

| Dokter. Putaran. | Tanggal | Komentar |

| A | 12/2015 | Rilis dokumen awal. |

INFORMASI KONTAK

Perusahaan Atmel

- 1600 Technology Drive, San Jose, CA 95110 AS

- T: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Revisi: Atmel-8968A-CPLD-ATF-ISP_Panduan Pengguna-12/2015

Atmel®, logo Atmel dan kombinasinya, Enabling Unlimited Possibilities®, dan lainnya adalah merek dagang terdaftar atau merek dagang Atmel Corporation di AS dan negara lain. Istilah dan nama produk lainnya mungkin merupakan merek dagang milik orang lain.

PENOLAKAN: Informasi dalam dokumen ini disediakan sehubungan dengan produk Atmel. Tidak ada lisensi, tersurat maupun tersirat, oleh estoppel atau sebaliknya, untuk hak kekayaan intelektual apa pun yang diberikan oleh dokumen ini atau sehubungan dengan penjualan produk Atmel. KECUALI YANG TERCANTUM DALAM SYARAT DAN KETENTUAN PENJUALAN ATMEL YANG TERLETAK DI ATMEL WEBSITUS, ATMEL TIDAK MENANGGUNG TANGGUNG JAWAB APAPUN DAN MENYANGKAL SEGALA JAMINAN TERSURAT, TERSIRAT, ATAU BERDASARKAN HUKUM YANG BERKAITAN DENGAN PRODUKNYA, TERMASUK NAMUN TIDAK TERBATAS PADA, JAMINAN TERSIRAT MENGENAI KEMAMPUAN UNTUK DIPERDAGANGKAN, KESESUAIAN UNTUK TUJUAN TERTENTU, ATAU TANPA PELANGGARAN. ATMEL DALAM KEADAAN APA PUN TIDAK BERTANGGUNG JAWAB ATAS KERUSAKAN LANGSUNG, TIDAK LANGSUNG, KONSEKUENSIAL, HUKUMAN, KHUSUS, ATAU INSIDENTAL (TERMASUK, TANPA BATASAN, KERUSAKAN ATAS KERUGIAN DAN KEUNTUNGAN, GANGGUAN BISNIS, ATAU HILANGNYA INFORMASI) YANG TIMBUL DARI PENGGUNAAN ATAU KETIDAKMAMPUAN MENGGUNAKAN DOKUMEN INI, BAHKAN JIKA ATMEL TELAH DIBERITAHUKAN TENTANG KEMUNGKINAN KERUSAKAN TERSEBUT. Atmel tidak membuat pernyataan atau jaminan sehubungan dengan keakuratan atau kelengkapan isi dokumen ini dan berhak untuk membuat perubahan pada spesifikasi dan deskripsi produk setiap saat tanpa pemberitahuan. Atmel tidak membuat komitmen apa pun untuk memperbarui informasi yang terkandung di sini. Kecuali jika secara khusus ditentukan lain, produk Atmel tidak cocok untuk, dan tidak boleh digunakan dalam aplikasi otomotif. Produk Atmel tidak dimaksudkan, diotorisasi, atau dijamin untuk digunakan sebagai komponen dalam aplikasi yang dimaksudkan untuk mendukung atau menopang kehidupan. PENAFIAN APLIKASI YANG KRITIS UNTUK KESELAMATAN, MILITER, DAN OTOMOTIF: Produk Atmel tidak dirancang untuk dan tidak akan digunakan sehubungan dengan aplikasi apa pun yang kegagalan produk tersebut secara wajar dapat mengakibatkan cedera pribadi atau kematian yang signifikan ("Aplikasi yang Kritis untuk Keselamatan") tanpa persetujuan tertulis khusus dari petugas Atmel. Aplikasi yang kritis untuk keselamatan mencakup, tanpa batasan, perangkat dan sistem pendukung kehidupan, peralatan atau sistem untuk pengoperasian fasilitas nuklir dan sistem persenjataan. Produk Atmel tidak dirancang atau dimaksudkan untuk digunakan dalam aplikasi atau lingkungan militer atau kedirgantaraan kecuali secara khusus ditetapkan oleh Atmel sebagai kelas militer. Produk Atmel tidak dirancang atau dimaksudkan untuk digunakan dalam aplikasi otomotif kecuali secara khusus ditetapkan oleh Atmel sebagai kelas otomotif.

Dokumen / Sumber Daya

|

Perangkat Logika Terprogram Kompleks Atmel ATF15xx [Bahasa Indonesia:] Panduan Pengguna ATF15xx, ATF15xx Perangkat Logika Terprogram Kompleks, Perangkat Logika Terprogram Kompleks, Perangkat Logika Terprogram, Perangkat Logika, Perangkat |