Dispositif logique programmable complexe Atmel ATF15xx

Caractéristiques

- Nom du produit : Programmation en système Atmel ATF15xx

- Modèle : ATF15xx

- Type : Dispositif logique programmable complexe (CPLD)

- Méthode de programmation : Programmation intégrée au système (ISP)

- Interface : JTAG Interface FAI

- Fabricant: Atmel

FAQ

Q : Puis-je utiliser un logiciel de programmation tiers avec les CPLD ATF15xx ?

R : Oui, à condition que le logiciel prenne en charge l'algorithme de programmation et JTAG instructions requises pour les CPLD ATF15xx.

Q : Est-il possible de programmer plusieurs CPLD ATF15xx simultanément ?

A : Oui, le JTAG L'interface ISP prend en charge la programmation de plusieurs appareils pour une programmation efficace de plusieurs CPLD à la fois.

Introduction

- Les dispositifs logiques programmables complexes (CPLD) Atmel® ATF15xx avec architecture Logic Doubling® prennent en charge la programmation in-system (ISP) via le Joint Test Action Group (J) de la norme IEEE 1149.1TAG) interface. Cette fonctionnalité améliore la flexibilité de programmation et offre des avantages dans différentes phases : développement du produit, production et utilisation sur le terrain. Ce guide d'utilisation décrit les méthodes de conception et les exigences pour la mise en œuvre de l'ISP sur les CPLD ATF15xx avec prise en charge de l'ISP, comme indiqué ci-dessous :

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Caractéristiques et avantages

La programmation en système permet de programmer et de reprogrammer les dispositifs ISP après leur montage sur les circuits imprimés (PCB). Cela élimine l'étape de manipulation supplémentaire requise dans le processus de fabrication pour programmer les dispositifs sur un programmateur de dispositifs externe avant leur montage sur les PCB. L'élimination de cette étape réduit le risque d'endommager les fils délicats des dispositifs à montage en surface à nombre élevé de broches ou d'endommager le dispositif par décharge électrostatique (ESD) pendant le flux de programmation. L'ISP permet également aux utilisateurs d'effectuer des modifications de conception et des mises à niveau sur le terrain sans avoir à retirer les dispositifs ISP des PCB. En outre, il permet également l'utilisation d'un microcontrôleur intégré ou d'un testeur en circuit pour effectuer des opérations de programmation en système sur les dispositifs ISP et intégrer ces opérations de programmation dans le flux de production des circuits imprimés.

Systèmes de programmation intégrés

Les trois composants essentiels d'un système ISP pour les CPLD ATF15xx sont :

Logiciel

Implémentation de l'algorithme de programmation, ainsi que la génération du JTAG instructions et données pour les appareils ISP cibles. Il peut s'agir d'un logiciel exécuté sur un PC, d'un microcontrôleur intégré ou d'un équipement de test en circuit.

Interface matérielle

Un canal de communication entre le logiciel ISP et les périphériques ISP sur la carte cible. Il peut s'agir d'un câble de téléchargement ISP ou d'un programmateur d'Atmel ou d'un fournisseur tiers, d'un équipement de test en circuit ou des connexions entre un microcontrôleur intégré et les périphériques ISP sur le PCB

Tableau cible

Circuit imprimé contenant les appareils ISP dans le JTAG chaîne. Il peut s'agir de la carte de développement/programmation CPLD ATF15xx d'Atmel ou d'une carte de circuit imprimé conçue sur mesure avec le J appropriéTAG connexions au matériel d'interface.

En plus de ces trois composants, un JEDEC file il est nécessaire de programmer un CPLD ATF15xx. Ce JEDEC file peut être créé en compilant une conception file en utilisant un logiciel de développement prenant en charge les CPLD ATF15xx tels que Atmel WinCUPL et Atmel ProChip Designer. Atmel fournit également un utilitaire de traduction, POF2JED.exe, qui convertit la sortie file du format de programmation du concurrent à un JEDEC file compatible avec le CPLD ATF15xx. Pour plus d'informations sur cet utilitaire, veuillez vous référer à la note d'application Atmel, « Conversion de la famille de produits ATF15xx », disponible sur le site Atmel website. Après le JEDEC fileLes CPLD ATF15xx sont créés pour tous les CPLD ATF15xx, ils peuvent être programmés sur la carte cible. Les CPLD ATFXNUMXxx peuvent être programmés par les systèmes de programmation intégrés suivants :

- Système de programmation intégré ATF15xx

- Microcontrôleurs embarqués

- Testeurs en circuit

Système de programmation intégré Atmel ATF15xx

Pour la programmation dans le système des CPLD ATF15xx, le logiciel ISP, le câble de téléchargement et le kit de développement/programmation sont disponibles auprès d'Atmel et sont décrits dans les sections ci-dessous.

Logiciel FAI

Le logiciel ISP Atmel ATF15xx, ATMISP, est le principal moyen de mise en œuvre de JTAG Programmation en système sur les CPLD ATF15xx. ATMISP s'exécute sur un PC hôte sous Windows et implémente la programmation en système des CPLD ATF15xx sur le système matériel ISP cible ou génère un format vectoriel série (.SVF) file à utiliser par l'équipement de test automatique (ATE) pour programmer les CPLD ATF15xx sur le système cible. ATMISP acquiert d'abord toutes les informations nécessaires auprès des utilisateurs sur le JTAG chaîne de périphériques dans le système cible. Il exécute ensuite le J appropriéTAG Instructions du FAI sur le JTAG chaîne de périphériques dans le système cible selon le JTAG informations sur la chaîne de périphériques spécifiées par les utilisateurs via le port USB ou LPT du PC. Plus d'informations sur le logiciel Atmel ATMISP sont disponibles à l'adresse www.atmel.com/tools/ATMISP.aspx.

Câble de téléchargement FAI

Le câble de téléchargement ISP USB Atmel ATF15xx, ATDH1150USB, se connecte à un port USB standard d'un ordinateur hôte d'un côté et à un JTAG en-tête de la carte de circuit cible de l'autre côté. Il transfère le JTAG instructions et données générées par ATMISP exécuté sur le PC hôte vers les périphériques ISP sur la carte de circuit cible. Plus d'informations sur le câble ATDH1150USB sont disponibles à l'adresse www.atmel.com/tools/ATDH1150USB.aspx.

Développeur/Programmeur

Le kit de développement/programmateur Atmel ATF15xx, ATF15xx-DK3-U, est un système de développement complet et un programmateur ISP pour les CPLD ATF15xx. Ce kit offre aux concepteurs un moyen très rapide et facile de développer des prototypes et d'évaluer de nouvelles conceptions avec un CPLD ISP ATF15xx. Avec la disponibilité des différentes cartes d'adaptation de socket pour prendre en charge la plupart des types de boîtiers proposés dans les CPLD ATF15xx, ce kit peut être utilisé comme programmateur ISP pour programmer les CPLD ISP ATF15xx dans la plupart des types de boîtiers disponibles via le JTAG interface. Plus d'informations sur le kit Atmel ATF15xx-DK3-U sont disponibles sur www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Système de microcontrôleur intégré

L'algorithme de programmation et JTAG Les instructions pour les CPLD ATF15xx peuvent être implémentées dans un microcontrôleur ou un microprocesseur, qui peut ensuite être utilisé pour programmer les CPLD ATF15xx sur la carte cible. Une méthode possible consiste à extraire tous les J pertinentsTAG informations sur le protocole (c'est-à-dire JTAG instructions et données) du SVF file généré par le logiciel ATMISP, puis utiliser ces informations pour implémenter le code du microcontrôleur ou du microprocesseur qui générerait le JTAG signaux pour les appareils ISP dans le JTAG chaîne. Cette approche est particulièrement adaptée aux systèmes qui disposent déjà d'un microcontrôleur ou d'un microprocesseur intégré, ce qui élimine l'utilisation de logiciels et d'outils matériels de programmation externes dans le système.

Système de test en circuit

Les CPLD ATF15xx peuvent être programmés sur la carte de circuit cible via le JTAG interface lors du test du circuit imprimé à l'aide d'un testeur en circuit. En général, le SVF file généré par ATMISP doit contenir tous les J pertinentsTAG informations de programmation intégrées dont les testeurs en circuit ont besoin pour programmer les CPLD ATF15xx sur la carte de circuit cible. Cette approche permet l'intégration de l'étape de programmation dans les teststage du flux de production.

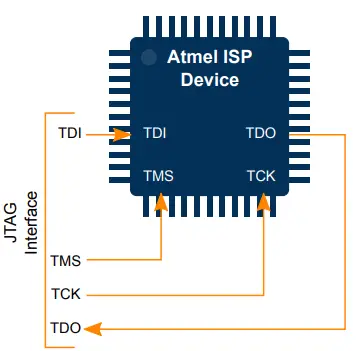

JTAG Interface FAI

L'ISP pour les CPLD ATF15xx est implémenté à l'aide de la norme IEEE 1149.1 Std. JTAG interface. Cette interface peut être utilisée pour effacer, programmer et vérifier les CPLD ATF15xx. Le JTAG L'interface est une interface série composée des signaux TCK, TMS, TDI et TDO et d'un JTAG Contrôleur de port d'accès de test (TAP). La broche TCK est l'entrée d'horloge pour le JTAG Contrôleur TAP et pour entrer/sortir le JTAG instructions et données. La broche TDI est l'entrée de données série. Elle est utilisée pour transférer les instructions de programmation et les données vers les périphériques ISP. La broche TDO est la sortie de données série. Elle est utilisée pour transférer les données des périphériques ISP. La broche TMS est une broche de sélection de mode. Elle contrôle l'état du JTAG Contrôleur TAP. Le JTAG Les broches d'interface du CPLD ATF15xx sur la carte cible ISP doivent être connectées au matériel d'interface ISP (c'est-à-dire au câble de téléchargement ISP) généralement via un connecteur à 10 broches. Le matériel d'interface ISP doit également être connecté au PC hôte exécutant le logiciel ISP. Le matériel d'interface ISP établit la communication entre le logiciel ISP et les périphériques ISP, et il permet au logiciel ISP de transférer les instructions de programmation et les données du PC hôte aux CPLD ATF15xx. CPLD ATF15xx avec le JTAG les fonctionnalités activées sont entièrement JTAG compatible et prend également en charge les opérations de test Boundary Scan (BST) requises spécifiées dans le JTAG standard. Les CPLD ATF15xx peuvent être configurés pour faire partie d'un JTAG Chaîne BST avec d'autres JTAG dispositifs pour les tests en circuit de la carte système. Grâce à cette fonctionnalité, les CPLD ATF15xx peuvent être testés sur la carte de circuit imprimé avec d'autres JTAG-appareils pris en charge sans recourir à des tests sur un lit de clous.

Programmation d'un seul appareil

Le JTAG L'interface ISP peut être configurée pour programmer un seul CPLD ATF15xx. Le JTAG La configuration d'un seul appareil est illustrée dans la figure ci-dessous. Lorsqu'un CPLD ATF15xx est configuré de cette manière, un registre apparaît entre les broches TDI et TDO de l'appareil. La taille du registre dépend de la JTAG largeur de l'instruction et les données décalées pour cette instruction. Figure 2-1 JTAG Appareil

Programmation de plusieurs appareils

Les CPLD ATF15xx peuvent être configurés dans le cadre d'une chaîne en guirlande de plusieurs JTAG- périphériques pris en charge comme décrit ci-dessous et également illustré dans la figure suivante.

- Connectez les broches TMS et TCK pour chaque appareil dans le JTAG chaîne aux broches TMS et TCK du JTAG en-tête d'interface sur le circuit imprimé.

- Connectez la broche TDI du premier appareil à la broche TDI du JTAG en-tête d'interface.

- Connectez la broche TDO du premier appareil à la broche TDI de l'appareil suivant. Continuez ce processus jusqu'à ce que tous les appareils, sauf le dernier, soient connectés.

- Connectez la broche TDO du dernier appareil à la broche TDO du JTAG en-tête d'interface.

Figure 2-2 Dispositif multiple JTAG Configuration

Pour programmer plusieurs appareils dans un JTAG chaîne, les utilisateurs doivent utiliser des outils logiciels FAI qui prennent en charge ces fonctionnalités. Dans le logiciel FAI, les utilisateurs doivent spécifier :

- Nombre d'appareils dans le JTAG chaîne.

- Numéros de référence des appareils et positions dans le JTAG chaîne.

- JTAG opérations pour chacun des appareils.

- Autre JTAG-des informations connexes telles que le JTAG largeur d'instruction pour chacun des périphériques.

Une fois le JTAG la connexion en guirlande est correctement configurée sur la carte cible ISP et dans le logiciel ISP, les périphériques du JTAG la chaîne peut être programmée en même temps.

Considérations de conception

Pour effectuer un ISP sur un CPLD ATF15xx, des ressources pour le JTAG l'interface de l'ATF15xx doit être réservée. Par conséquent, les quatre broches d'E/S pour les broches TMS, TDI, TDO et TCK doivent être réservées pour JTAG et ne peuvent pas être utilisés comme E/S utilisateur. Les numéros de broches de ces broches dépendent du CPLD ATF15xx utilisé et de son type de boîtier. Reportez-vous au tableau ci-dessous pour obtenir des informations sur le brochage. Le JTAG la norme recommande que les broches TMS et TDI soient tirées vers le haut pour chaque appareil du JTAG chaîne. Les CPLD ATF15xx ont une fonction de rappel interne pour ces broches qui, lorsqu'elle est activée, évite d'avoir recours à des résistances de rappel externes. De plus, le JTAG La fonction d'interface doit être activée pour pouvoir exécuter l'ISP sur les CPLD ATF15xx. L'activation de la fonction JTAG L'interface nécessite de choisir des types de périphériques Atmel spécifiques ou des paramètres d'option avant de compiler la conception ATF15xx. Ces procédures sont décrites pour WinCUPL, ProChip Designer et POF2JED dans ce guide. Par défaut, tous les CPLD ATF15xx flambant neufs sont livrés avec le JTAG interface activée. Une fois les ressources logiques pour le JTAG les interfaces sont réservées, les utilisateurs peuvent programmer, vérifier et effacer n'importe quel CPLD ATF15xx sur la carte cible à l'aide du logiciel ATMISP.

Conseil:Bien que les quatre JTAG les broches sont réservées pour un JTAG interface, les utilisateurs peuvent implémenter des fonctions logiques enfouies dans les macrocellules associées à ces broches.

Tableau 3-1 ATF15xx CPLD JTAG Numéros de broche

| JTAG Épingle | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Activer JTAG Interface avec WinCUPL

Pour activer le JTAG Pour une interface avec WinCUPL, le type de périphérique ISP ATF15xx approprié doit être spécifié avant la compilation d'une conception. Une fois la conception compilée avec succès, un JEDEC file avec le JTAG la fonctionnalité d'interface activée est générée. Lorsque ce JEDEC file est programmé dans un ATF15xxCPLD, son JTAG l'interface est activée. Les utilisateurs peuvent également activer les résistances de rappel internes TDI et TMS en incluant les instructions de propriété suivantes dans la conception CUPL file.

- PROPRIÉTÉ ATMEL {TDI_PULLUP = ON};

- PROPRIÉTÉ ATMEL {TMS_PULLUP = ON};

Avis:Si un type de périphérique ISP ATF15xx est utilisé pour une conception qui utilise le JTAG broches d'interface comme broches d'E/S logiques, WinCUPL génère une erreur.

Les étapes suivantes expliquent comment ouvrir une conception existante dans WinCUPL, spécifier le type de périphérique et compiler la conception.

- Dans le menu principal de WinCUPL, sélectionnez File > Ouvrir. Sélectionner la source CUPL (.pld) file à partir du répertoire de travail approprié.

- Sélectionnez OK pour ouvrir la source PLD file.

- Dans le menu principal de WinCUPL, sélectionnez File > Enregistrer. Cela enregistre les modifications apportées à la source file.

- Dans le menu principal, sélectionnez Options > Périphériques. La boîte de dialogue Sélection de périphérique s'ouvre.

- Choisissez le périphérique ISP ATF15xx approprié. Consultez le tableau suivant pour obtenir une liste de tous les types de périphériques ATF15xx pris en charge par WinCUPL.

- Sélectionnez OK pour fermer le menu de sélection de l’appareil.

- Remarque : une autre méthode consiste à choisir un type de périphérique ATF15xx approprié dans le tableau suivant et à l'inclure dans la section d'en-tête de la source CUPL file.

- Dans le menu principal de WinCUPL, sélectionnez Exécuter > Compilation dépendante du périphérique.

- WinCUPL compile la conception et génère l'outil d'adaptation de l'appareil Atmel. Si la conception est conforme, un JEDEC file est automatiquement créé.

- Lorsque le JEDEC file est programmé dans l'appareil, le JTAG l'interface, les résistances de rappel TMS et TDI internes en option et les circuits de maintien de broches en option sont activés.

Note: La sélection d'un type de périphérique ISP Atmel active automatiquement le JTAG interface par défaut lorsque Atmel WinCUPL exécute l'installateur de périphériques Atmel.

Si les conceptions empêchent de réserver des ressources pour le JTAG Si une interface ou un FAI n'est pas utilisé, un type de périphérique Atmel non FAI doit être sélectionné. Consultez le tableau ci-dessous pour obtenir une liste des périphériques. Le périphérique peut ensuite être reprogrammé à l'aide d'un programmateur de périphérique externe. Le tableau ci-dessous répertorie les types de périphériques Atmel ISP et Atmel non FAI pour WinCUPL.

Tableau 3-2 Type de périphérique WinCUPL ATF15xx

| Nom de l'appareil | Type de paquet | Type de périphérique WinCUPL | |

| JTAG Activé | JTAG Désactivé | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Activer JTAG Interface avec Atmel ProChip Designer

Pour activer le JTAG interface avec ProChip Designer :

- Ouvrez le projet ProChip Designer approprié.

- Ouvrez la fenêtre Options du monteur en cliquant sur le bouton Atmel Fitter sous Device Fitter.

- Sélectionnez l'onglet Périphérique global, puis cochez la case JTAG Boîte de ports. Les résistances de rappel internes TMS et TDI peuvent également être activées en cochant les cases Pullup TDI et Pullup TMS. Ces cases à cocher sont illustrées dans la figure ci-dessous.

Figure 3-1 Interface utilisateur des options d'ajustement de ProChip Designer

Activer JTAG Interface avec POF2JED

Dans POF2JED, le JTAG L'option Mode peut être définie sur Auto pour permettre à POF2JED de déterminer si le JTAG la fonctionnalité dans l'ATF15xx doit être activée ou non, et elle dépend du fait que JTAG est pris en charge dans le CPLD du concurrent. Pour activer JTAG dans le CPLD ATF15xx indépendamment du fait que JTAG est pris en charge dans le CPLD du concurrent ou non, le JTAG L'option Mode doit être réglée sur Activé. Lorsque JTAG est activé dans l'ATF15xx, les résistances de rappel internes TDI et TMS peuvent être activées en cochant la case Activer

Cases TDI_PULLUP et Activer TMS_PULLUP dans POF2JED. Voir la figure ci-dessous.

Figure 3-2 Interface utilisateur POF2JED

Lignes directrices et recommandations

Attention: Une attention particulière doit être accordée à cette section lors de l'exécution d'opérations ISP sur des CPLD ATF15xx. Cette section décrit certains des JTAG Lignes directrices, informations et recommandations des FAI qu'il convient de bien noter.

- Assurez-vous que le JTAG port pour tous les appareils du JTAG la chaîne est activée.

- Pour les CPLD ATF15xx, le JTAG le port est activé si les périphériques sont vierges/effacés ou programmés avec JTAG activé.

- Tous les appareils Atmel ATF15xx sont expédiés dans un état vierge/effacé ; par conséquent, le JTAG le port est activé pour tous les nouveaux appareils et prêt pour le FAI.

- Appareils ATF15xx avec JTAG les désactivés doivent être effacés à l'aide d'un programmateur de périphérique non FAI pour réactiver le JTAG port.

- Assurez-vous que le volume VCC est correcttage est appliqué à chacun des appareils du JTAG chaîne.

- CPLD ATF15xxAS/ASL dans les types de boîtier 84-PLCC, 100-TQFP et 100-PQFP : VCCINT doit être compris entre 4.5 V et 5.5 V tandis que VCCIO peut être compris entre 3.0 V et 3.6 V ou 4.5 V et 5.5 V.

- CPLD ATF15xxAS/ASL dans les types de boîtier 44-PLCC et 44-TQFP : VCC doit être compris entre 4.5 V et 5.5 V.

- CPLD ATF15xxASV/ASVL : VCC (VCCIO et VCCINT) doit être compris entre 3.0 V et 3.6 V.

- Le VCC pour les appareils dans le JTAG la chaîne doit être correctement régulée et filtrée.

- Pour les CPLD ATF15xx utilisés dans la plupart des applications, il est recommandé d'utiliser un condensateur de découplage de 0.22 µF pour chacune des paires VCC/GND.

- Il est recommandé d'utiliser une masse commune pour tous les appareils du JTAG chaîne et le JTAG matériel d'interface (c'est-à-dire câble de téléchargement ISP ATDH1150USB).

- Il est recommandé d'éviter les longues durées (pas plus de cinq appareils) JTAG chaînes.

- Si un long JTAG Il est nécessaire de mettre en mémoire tampon les signaux TMS et TCK tous les cinq appareils. L'utilisation d'un tampon de déclenchement de Schmitt est préférable.

- Les tampons remodèlent les temps de montée et de descente des signaux TMS et TCK.

- Il faut prendre en compte le délai supplémentaire engendré par les tampons.

- Il est recommandé d'utiliser des résistances de rappel (4.7 KΩ à 10 KΩ) pour les signaux TMS et TDI et une résistance de rappel pour le signal TCK au niveau J.TAG en-tête pour empêcher ces signaux de flotter lorsqu'ils ne sont pas pilotés par le matériel d'interface.

- Des pull-ups internes optionnels sur TMS et TDI sont disponibles pour les CPLD ATF15xx.

- Il est recommandé de terminer JTAG signaux au JTAG en-tête.

- Les terminaisons actives et passives sont toutes deux acceptables ; cependant, la terminaison passive est préférée.

- Il réduit les sonneries dues aux longues longueurs de câble/trace PCB.

- La terminaison est particulièrement critique pour TMS et TCK.

- Il est recommandé que toutes les entrées et E/S des périphériques du JTAG chaîne, sauf le JTAG les broches doivent être dans un état statique lorsque les CPLD ATF15xx sont programmés pour minimiser le bruit.

- Lorsque vous utilisez l'une des cartes de développement/programmation Atmel ATF15xx, l'alimentation de la carte doit être coupée lorsque les positions des cavaliers de sélection VCC sont modifiées.

- Pour les CPLD ATF15xx, JTAG L'ISP est disponible lorsque le composant est en mode de mise hors tension contrôlée par broche ou lorsque le périphérique « basse consommation » est en veille.

- État de l'appareil après interruption du FAI :

- Si l'ISP est interrompu, toutes les broches d'E/S sont à trois états, quel que soit l'état des circuits Pin-keeper.

- Empêche les périphériques partiellement programmés de provoquer des conflits de bus avec d'autres périphériques sur le circuit imprimé.

- Lors de la programmation ISP, toutes les broches d'E/S sont dans l'une des conditions suivantes :

- État de haute impédance :

- Lorsqu'un périphérique vierge/effacé est programmé.

- Lorsqu'un appareil est reprogrammé avec les circuits Pin-keeper désactivés.

- Empêche les conflits de bus avec des périphériques externes en interface avec les CPLD ATF15xx sur le circuit imprimé.

- Faiblement verrouillé à l'état précédent :

- Lorsqu'un appareil programmé est reprogrammé avec les circuits Pin-keeper activés.

- Les broches d'E/S conservent les niveaux logiques précédents avant l'ISP.

- Empêche le FAI d’affecter le fonctionnement d’autres périphériques sur la carte système.

- L'utilisation de plusieurs JTAG les chaînes sur une seule planche ne sont pas recommandées.

- Les appareils peuvent interagir entre différents JTAG chaînes.

- La carte n'est fonctionnelle que lorsque tous les appareils de tous les JTAG les chaînes sont programmées avec succès.

- Si la programmation échoue pour au moins un périphérique d'une chaîne tandis que d'autres JTAG les chaînes ont été programmées avec succès :

- Atmel ou d'autres appareils embarqués peuvent être endommagés en raison d'un éventuel problème de contention de bus pour les sorties à trois états.

- L'état de fonctionnement de la carte système est indéfini ; par conséquent, un fonctionnement incorrect peut se produire.

- Insertion de circuits actifs entre JTAG en-tête et le JTAG Il n'est pas recommandé de connecter des appareils en chaîne. Si le circuit actif fonctionne mal, cela peut entraîner des problèmes de programmation/vérification.

- L'utilisation de vol. mixtetagl'appareil JTAG les chaînes ne sont pas recommandées.

- Ce sont des JTAG chaînes avec des appareils qui utilisent différents volumes VCCtages et/ou interface voltaget.

- Volume d'interfacetagLes niveaux (VIL, VIH, VOL, VOH) pour les appareils 5.0 V peuvent ne pas être compatibles avec l'interface voltagniveaux e pour les appareils 3.0 V.

- Si ATMISP a des problèmes de communication avec le JTAG chaîne matérielle de l'appareil, essayez d'exécuter l'auto-étalonnage ou l'étalonnage manuel pour réduire les fréquences du JTAG Signaux.

- Assurez-vous que le voyant du câble ATDH1150USB est allumé et qu'il est vert avant de commencer la programmation. Assurez-vous que le câble de téléchargement ISP est capable de communiquer correctement avec le logiciel ATMISP.

- Assurez-vous que le volume VCC est correcttage est appliqué au câble ATDH1150USB.

- Le VCC utilisé par le premier appareil du JTAG la chaîne doit être fournie au câble ATDH1150USB via la broche 4 du J 10 brochesTAG en-tête.

- Pour les CPLD ATF15xx avec VCCINT et VCCIO séparés, VCCIO doit être utilisé pour le câble ATDH1150USB.

Informations de commande

| Code de commande | Description |

| ATF15xx-DK3-U | Kit de développement/programmation CPLD (comprend l'ATF15xxDK3-SAA44 et l'ATDH1150USB ou l'ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | Carte adaptateur de prise TQFP 100 broches pour carte DK3 |

| ATF15xxDK3-SAJ44 | Carte adaptateur de prise PLCC 44 broches pour carte DK3 |

| ATF15xxDK3-SAJ84 | Carte adaptateur de prise PLCC 84 broches pour carte DK3 |

| ATF15xxDK3-SAA44 | Carte adaptateur de prise TQFP 44 broches pour carte DK3 |

| ATDH1150USB | Atmel ATF15xx CPLD basé sur USB JTAG Câble de téléchargement FAI |

Historique des révisions

| Doc. Tour. | Date | Commentaires |

| A | 12/2015 | Publication initiale du document. |

COORDONNÉES

Société Atmel

- 1600 Technology Drive, San Jose, CA 95110 États-Unis

- Tél : (+1)(408) 441.0311

- Fax : (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rév. : Atmel-8968A-CPLD-ATF-ISP_Guide de l'utilisateur-12/2015

Atmel®, le logo Atmel et leurs combinaisons, Enabling Unlimited Possibilities® et autres sont des marques déposées ou des marques commerciales d'Atmel Corporation aux États-Unis et dans d'autres pays. Les autres termes et noms de produits peuvent être des marques commerciales de tiers.

AVIS DE NON-RESPONSABILITÉ : Les informations contenues dans ce document sont fournies en relation avec les produits Atmel. Aucune licence, expresse ou implicite, par préclusion ou autrement, sur un droit de propriété intellectuelle n'est accordée par ce document ou en relation avec la vente de produits Atmel. SAUF INDICATION DANS LES CONDITIONS GÉNÉRALES DE VENTE ATMEL SITUÉES SUR ATMEL WEBATMEL N'ASSUME AUCUNE RESPONSABILITÉ ET DÉCLINE TOUTE GARANTIE EXPRESSE, IMPLICITE OU LÉGALE CONCERNANT SES PRODUITS, Y COMPRIS, MAIS SANS S'Y LIMITER, LA GARANTIE IMPLICITE DE QUALITÉ MARCHANDE, D'ADÉQUATION À UN USAGE PARTICULIER OU DE NON-CONTREFAÇON. ATMEL NE SERA EN AUCUN CAS RESPONSABLE DE TOUT DOMMAGE DIRECT, INDIRECT, CONSÉCUTIF, PUNITIF, SPÉCIAL OU ACCESSOIRE (Y COMPRIS, SANS S'Y LIMITER, LES DOMMAGES POUR PERTE DE PROFITS, INTERRUPTION D'ACTIVITÉ OU PERTE D'INFORMATIONS) DÉCOULANT DE L'UTILISATION OU DE L'INCAPACITÉ D'UTILISER CE DOCUMENT, MÊME SI ATMEL A ÉTÉ AVISÉ DE LA POSSIBILITÉ DE TELS DOMMAGES. Atmel ne fait aucune déclaration ni ne donne aucune garantie quant à l'exactitude ou à l'exhaustivité du contenu de ce document et se réserve le droit d'apporter des modifications aux spécifications et aux descriptions de produits à tout moment sans préavis. Atmel ne s'engage pas à mettre à jour les informations contenues dans ce document. Sauf indication contraire spécifique, les produits Atmel ne sont pas adaptés et ne doivent pas être utilisés dans des applications automobiles. Les produits Atmel ne sont pas destinés, autorisés ou garantis à être utilisés comme composants dans des applications destinées à soutenir ou à maintenir la vie. AVIS DE NON-RESPONSABILITÉ CONCERNANT LES APPLICATIONS CRITIQUES POUR LA SÉCURITÉ, LES APPLICATIONS MILITAIRES ET AUTOMOBILES : Les produits Atmel ne sont pas conçus et ne seront pas utilisés dans le cadre d'applications où la défaillance de ces produits pourrait raisonnablement entraîner des blessures corporelles importantes ou la mort (« Applications critiques pour la sécurité ») sans le consentement écrit spécifique d'un responsable d'Atmel. Les applications critiques pour la sécurité comprennent, sans limitation, les dispositifs et systèmes de survie, les équipements ou systèmes pour le fonctionnement des installations nucléaires et des systèmes d'armes. Les produits Atmel ne sont pas conçus ni destinés à être utilisés dans des applications ou environnements militaires ou aérospatiaux, sauf s'ils sont spécifiquement désignés par Atmel comme étant de qualité militaire. Les produits Atmel ne sont pas conçus ni destinés à être utilisés dans des applications automobiles, sauf s'ils sont spécifiquement désignés par Atmel comme étant de qualité automobile.

Documents / Ressources

|

Dispositif logique programmable complexe Atmel ATF15xx [pdf] Guide de l'utilisateur ATF15xx, ATF15xx Dispositif logique programmable complexe, Dispositif logique programmable complexe, Dispositif logique programmable, Dispositif logique, Dispositif |