Atmel ATF15xx Gailu Logiko Programagarri Konplexua

Zehaztapenak

- Produktuaren izena: Atmel ATF15xx Sistema barneko programazioa

- Eredua: ATF15xx

- Mota: Gailu Logiko Programagarri Konplexua (CPLD)

- Programazio metodoa: Sistema barneko programazioa (ISP)

- Interfazea: JTAG ISP Interfazea

- Fabrikatzailea: Atmel

Ohiko galderak

G: Erabili al dezaket hirugarrenen programazio softwarea ATF15xx CPLDekin?

A: Bai, softwareak programazio algoritmoa eta JTAG ATF15xx CPLDetarako behar diren argibideak.

G: Posible al da ATF15xx CPLD anitz aldi berean programatzea?

A: Bai, JTAG ISP interfazeak hainbat gailuren programazioa onartzen du CPLD anitz aldi berean eraginkortasunez programatzeko.

Sarrera

- Atmel® ATF15xx Gailu Logiko Programagarri Konplexuek (CPLD) Logic Doublebling® arkitektura duten sistema barneko programazioa (ISP) onartzen dute IEEE Std. 1149.1 Proba Ekintza Talde Bateratua (JTAG) interfazea. Ezaugarri honek programazioaren malgutasuna hobetzen du eta hainbat fasetan onurak ematen ditu; produktuen garapena, ekoizpena eta landa erabilera. Erabiltzaile-gida honek ISP-a ISP laguntzarekin ATF15xx CPLDetan ezartzeko diseinu-metodoak eta eskakizunak deskribatzen ditu behean zerrendatzen den moduan:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Ezaugarriak eta Abantailak

Sistema barneko programazioak ISP gailuak programatu eta birprogramatzea ahalbidetzen du, Zirkuitu Inprimatuko Plaketan (PCB) muntatu ondoren. Honek fabrikazio-prozesuan gailuak kanpoko gailu programatzaile batean programatzeko beharrezkoa den manipulazio-urrats gehigarria ezabatzen du PCBetan muntatu aurretik. Urrats hau ezabatzeak pin kopuru handiko gainazalean muntatzeko gailuen kable delikatuak kaltetzeko aukera murrizten du edo deskarga elektrostatikoen (ESD) bidez gailua kaltetzeko aukera murrizten du programazio-fluxuan zehar. ISP-k erabiltzaileei diseinu-aldaketak eta eremu-berritzeak ere ahalbidetzen die ISP gailuak PCBetatik kendu beharrik gabe. Gainera, txertatutako mikrokontrolagailu edo zirkuitu barruko probatzaile bat erabiltzeko aukera ematen du ISP gailuetan sisteman programazio-eragiketak egiteko eta programazio-eragiketa horiek zirkuitu-plaken ekoizpen-fluxuan integratzeko.

Sistema barneko programazio sistemak

ATF15xx CPLDetarako ISP sistema baten funtsezko hiru osagaiak hauek dira:

Softwarea

Programazio algoritmoa ezartzea, baita JTAG helburuko ISP gailuetarako argibideak eta datuak. Hau ordenagailu batean exekutatzen den software-programa bat izan daiteke, mikrokontrolagailu txertatu batean edo zirkuitu barruko proba-ekipo batean.

Interfazearen Hardwarea

Helburu-taulan dauden ISP softwarearen eta ISP gailuen arteko komunikazio kanala. Hau Atmel-en edo hirugarrenen saltzaile baten ISP deskargatzeko kablea edo programatzailea izan daiteke, zirkuitu barruko proba-ekipoa edo PCBko mikrokontrolagailu txertatuaren eta ISP gailuen arteko konexioak.

Xede-batzordea

ISP gailuak dituen zirkuitu plaka JTAG katea. Hau izan daiteke Atmel-eko ATF15xx CPLD Garapen/Programatzaile plaka edo J egokia duen neurrira diseinatutako zirkuitu plaka.TAG interfazearen hardwarerako konexioak.

Hiru osagai horiez gain, JEDEC bat file beharrezkoa da ATF15xx CPLD bat programatzeko. JEDEC hau file diseinu bat osatuz sor daiteke file Atmel WinCUPL eta Atmel ProChip Designer bezalako ATF15xx CPLD onartzen dituen garapen softwarea erabiliz. Atmel-ek itzultzaile-software-erabilgarri bat ere eskaintzen du, POF2JED.exe, irteera bihurtzen duena file lehiakidearen programazio formatutik JEDEC batera file ATF15xx CPLD-rekin bateragarria. Erabilgarritasun honi buruzko informazio gehiago lortzeko, ikusi Atmel aplikazioaren oharra, "ATF15xx Product Family Conversion", Atmel-en eskuragarri. webgunea. JEDECen ostean files ATF15xx CPLD guztietarako sortzen dira, xede-taulan programatu daitezke. ATF15xx CPLD sistema barneko programazio sistema hauek programatu daitezke:

- ATF15xx Sistema barneko programazio sistema

- Mikrokontrolagailu txertatuak

- Zirkuitu barruko probatzaileak

Atmel ATF15xx Sistema barneko programazio sistema

ATF15xx CPLD-en sisteman programatzeko, ISP softwarea, deskargatzeko kablea eta garapen/programatzaileen kit eskuragarri daude Atmel-en eta beheko ataletan deskribatzen dira.

ISP softwarea

Atmel ATF15xx ISP softwarea, ATMISP, J inplementatzeko bitarteko nagusia daTAG sistema barneko programazioa ATF15xx CPLDetan. ATMISP Windows-en oinarritutako ordenagailu ostalari batean exekutatzen da eta ATF15xx CPLDen sistemako programazioa ezartzen du xede ISP hardware sisteman edo Serial Vector Format (.SVF) sortzen du. file Proba Automatikoko Ekipamenduak (ATE) erabiltzeko ATF15xx CPLD xede-sisteman programatzeko. ATMISP-k lehenik erabiltzaileengandik beharrezko informazio guztia eskuratzen du JTAG gailu-katea xede-sisteman. Ondoren, egokia den J exekutatzen duTAG ISP argibideak JTAG gailu-katea xede-sisteman JTAG Erabiltzaileek ordenagailuaren USB edo LPT atakaren bidez zehaztutako gailu-katearen informazioa. Atmel ATMISP softwareari buruzko informazio gehiago hemen dago eskuragarri www.atmel.com/tools/ATMISP.aspx.

ISP deskargatzeko kablea

Atmel ATF15xx USB-en oinarritutako ISP deskargatzeko kablea, ATDH1150USB, ordenagailu ostalari baten USB ataka estandar batera konektatzen da alde batetik eta J batera.TAG helburuko zirkuitu plakaren goiburua beste aldean. J. transferitzen duTAG Ostalari PCan exekutatzen ari den ATMISP-ek sortutako argibideak eta datuak xede-zirkuitu plakan dauden ISP gailuetara. ATDH1150USB kableari buruzko informazio gehiago hemen dago eskuragarri www.atmel.com/tools/ATDH1150USB.aspx.

Garapena/Programatzailea

Atmel ATF15xx Garapen/Programatzaile Kita, ATF15xx-DK3-U, garapen sistema osoa eta ATF15xx CPLDentzako ISP programatzailea da. Kit honek diseinatzaileei prototipoak garatzeko eta diseinu berriak ebaluatzeko oso modu azkar eta erraz bat eskaintzen die ATF15xx ISP CPLD batekin. ATF15xx CPLD-etan eskaintzen diren pakete-mota gehienak onartzeko entxufe egokitzaile-plaka ezberdinen erabilgarritasunarekin, kit hau ISP programatzaile gisa erabil daiteke ATF15xx ISP CPLD-ak eskuragarri dauden pakete-mota gehienetan J bidez programatzeko.TAG interfazea. Atmel ATF15xx-DK3-U kitari buruzko informazio gehiago hemen dago eskuragarri www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Mikrokontrolagailu sistema txertatua

Programazio algoritmoa eta JTAG ATF15xx CPLD-etarako argibideak mikrokontrolagailu edo mikroprozesadore batean inplementa daitezke, eta ondoren ATF15xx CPLDak xede-taulan programatzeko erabil daitezke. Metodo posible bat J egoki guztiak ateratzea daTAG protokoloaren informazioa (adibidez, JTAG argibideak eta datuak) SVF-tik file ATMISP softwareak sortutakoa, eta informazio hori erabili J-a sortuko lukeen mikrokontrolagailu edo mikroprozesadorerako kodea ezartzeko.TAG ISP gailuetarako seinaleak JTAG katea. Ikuspegi hau lehendik mikrokontrolagailu edo mikroprozesadore txertatua duten sistemetarako da egokiena, eta honek sistema barruko kanpoko programazio software eta hardware tresnen erabilera ezabatzen du.

Zirkuitu barruko proba sistema

ATF15xx CPLDak helburuko zirkuitu plakan programatu daitezke JTAG interfazea zirkuitu plakaren probak zehar zirkuitu barruko probatzaile bat erabiliz. Orokorrean, SVF file ATMISP-ek sortutako J agortu guztiak eduki beharko lituzkeTAG ATF15xx CPLD-ak xede-zirkuitu plakan programatzeko behar duten zirkuituko probatzaileek sistema barneko programazio-informazioa. Ikuspegi honek programazio-urratsa testing-en integrazioa ahalbidetzen dutagprodukzio-fluxuaren e.

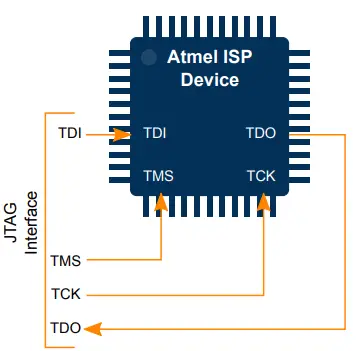

JTAG ISP Interfazea

ATF15xx CPLDetarako ISP IEEE 1149.1 Std erabiliz inplementatzen da. JTAG interfazea. Interfaze hau ATF15xx CPLDak ezabatu, programatu eta egiaztatzeko erabil daiteke. JTAG interfazea serieko interfaze bat da, TCK, TMS, TDI eta TDO seinalez eta JTAG Test Access Port (TAP) kontrolagailua. TCK pina J-rako erlojuaren sarrera daTAG TAP kontrolagailua eta JTAG argibideak eta datuak. TDI pina serieko datuen sarrera da. Programazio-argibideak eta datuak ISP gailuetara aldatzeko erabiltzen da. TDO pin serieko datuen irteera da. ISP gailuetatik datuak kanporatzeko erabiltzen da. TMS pina modu hautatzeko pin bat da. J-ren egoera kontrolatzen duTAG TAP kontrolagailua. JTAG ISP xede-taulan ATF15xx CPLD-ren interfazearen pinak ISP interfazearen hardwarera (hau da, ISP deskargatzeko kablea) konektatu behar dira normalean 10 pineko goiburu baten bidez. ISP interfazearen hardwarea ISP softwarea exekutatzen duen ordenagailu ostalarira ere konektatu behar da. ISP interfazearen hardwareak ISP softwarearen eta ISP gailuen arteko komunikazioa ezartzen du, eta ISP softwareari programazio-argibideak eta datuak ostalari PCtik ATF15xx CPLDetara transferitzeko aukera ematen dio. ATF15xx CPLDak JTAG gaituta dauden funtzioak guztiz J diraTAG bateragarria eta J-n zehaztutako muga-eskaneatze-proba (BST) eragiketak ere onartzen dituTAG estandarra. ATF15xx CPLDak J baten parte izateko konfigura daitezkeTAG BST katea beste JTAG sistema-plakaren zirkuitu barruko probak egiteko gailuak. Ezaugarri honekin, ATF15xx CPLDak zirkuitu plakan probatu daitezke beste JTAG- Onartutako gailuak iltzeen ohearen probara jo gabe.

Gailu bakarreko programazioa

JTAG ISP interfazea ATF15xx CPLD bakarra programatzeko konfigura daiteke. JTAG gailu bakar baten konfigurazioa beheko irudian ageri da. ATF15xx CPLD bat horrela konfiguratzen denean, erregistro bat agertzen da gailuaren TDI eta TDO pinen artean. Erregistroaren tamaina J-ren araberakoa daTAG instrukzio-zabalera eta instrukzio horretarako mugitzen diren datuak. 2-1 irudia JTAG Gailua

Gailu anitzeko programazioa

ATF15xx CPLDak J anitzeko kate baten zati gisa konfigura daitezkeTAG- Onartutako gailuak behean deskribatzen den moduan eta hurrengo irudian ere erakusten dira.

- Konektatu TMS eta TCK pina gailu bakoitzeko J-nTAG katea J-ren TMS eta TCK pinetaraTAG interfazearen goiburua zirkuitu plakan.

- Konektatu TDI pina lehen gailutik J-ren TDI pineraTAG interfazearen goiburua.

- Konektatu TDO pina lehen gailutik hurrengo gailuko TDI pinera. Jarraitu prozesu honekin azkena izan ezik guztiak konektatu arte.

- Konektatu TDO pina azken gailutik J-ren TDO pineraTAG interfazearen goiburua.

2-2 Irudia gailu anitz JTAG Konfigurazioa

Hainbat gailu programatzeko JTAG kate, erabiltzaileek ezaugarri horiek onartzen dituzten ISP software-tresnak erabili behar dituzte. ISP softwarean, erabiltzaileek zehaztu behar dute:

- J-ko gailu kopuruaTAG katea.

- Gailuen pieza-zenbakiak eta J-ren barruan dauden posizioakTAG katea.

- JTAG gailu bakoitzeko eragiketak.

- Beste JTAG- erlazionatutako informazioa, esate baterako, JTAG argibideen zabalera gailu bakoitzeko.

Behin JTAG margarita katea behar bezala konfiguratuta dago ISP xede-taulan eta ISP softwarean, J-ko gailuak.TAG katea aldi berean programatu daiteke.

Diseinu-gogoetak

ISP ATF15xx CPLD batean egiteko, JTAG ATF15xx-ko interfazea erreserbatuta egon behar da. Beraz, TMS, TDI, TDO eta TCK pinetarako lau I/O pinak J-rentzat gorde behar dira.TAG eta ezin da erabiltzailearen I/O gisa erabili. Pin hauen pin zenbakiak ATF15xx CPLD erabiltzen den eta pakete motaren araberakoak dira. Ikusi beheko taulara pin-out informazioa lortzeko. JTAG estandarrak TMS eta TDI pinak gora ateratzea gomendatzen du gailu bakoitzerako JTAG katea. ATF15xx CPLD-ek pin hauetarako barne-tiratze-eginbide bat dute eta horrek, gaituta dagoenean, kanpoko tira-erresistentzien beharra aurrezten du. Gainera, JTAG interfazearen eginbidea gaituta egon behar da ATF15xx CPLDetan ISP egiteko. JTAG interfazeak Atmel gailu mota edo aukera-ezarpen zehatzak aukeratu behar ditu ATF15xx diseinua konpilatu aurretik. Prozedura hauek WinCUPL, ProChip Designer eta POF2JEDentzako zehazten dira gida honetan. Lehenespenez, ATF15xx CPLD berri guztiak JTAG interfazea gaituta. Behin J.-rako baliabide logikoakTAG interfazea erreserbatuta dago, erabiltzaileek helburu-taulan edozein ATF15xx CPLD programatu, egiaztatu eta ezabatu dezakete ATMISP softwarea erabiliz.

Aholkua: lau JTAG pinak J batentzat gordeta daudeTAG interfazea, erabiltzaileek lurperatutako funtzio logikoak ezar ditzakete pin horiekin lotutako makrozeluletan.

3-1 taula ATF15xx CPLD JTAG Pin zenbakiak

| JTAG Pin | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Gaitu JTAG WinCUPL-rekin interfazea

JTAG WinCUPL-rekin interfazea, diseinu bat konpilatu aurretik ATF15xx ISP gailu mota egokia zehaztu behar da. Diseinu bat arrakastaz osatu ondoren, JEDEC bat file J.-rekinTAG gaituta dagoen interfazearen eginbidea sortzen da. JEDEC honek file ATF15xxCPLD batean programatuta dago, bere JTAG interfazea gaituta dago. Erabiltzaileek TDI eta TMS barne-erresistentziak ere gaitu ditzakete CUPL diseinuan propietate-adierazpen hauek sartuz file.

- PROPIETATE ATMEL {TDI_PULLUP = ON};

- PROPIETATE ATMEL {TMS_PULLUP = ON};

Oharra: ATF15xx ISP gailu mota bat erabiltzen bada JTAG interfazearen pinak I/O pin logiko gisa, WinCUPL-ek errore bat sortzen du.

Hurrengo urratsek WinCUPL-en dagoen diseinu bat nola ireki, gailu mota zehaztu eta diseinua nola konpilatu aztertzen dute.

- WinCUPL menu nagusian, hautatu File > Ireki. Hautatu CUPL (.pld) iturria file dagokion lan-direktoriotik.

- Hautatu Ados PLD iturria irekitzeko file.

- WinCUPL menu nagusian, hautatu File > Gorde. Honek iturburuan egindako aldaketak gordetzen ditu file.

- Menu nagusian, hautatu Aukerak > Gailuak. Honek Gailua aukeratzeko elkarrizketa-koadroa irekitzen du.

- Aukeratu ATF15xx ISP gailu egokia. Ikusi hurrengo taula WinCUPL-ek onartzen dituen ATF15xx gailu mota guztien zerrendarako.

- Hautatu Ados gailua hautatzeko menua ixteko.

- Oharra: beste metodo bat hurrengo taulatik ATF15xx gailu mota egokia aukeratzea eta CUPL iturburuko goiburuko atalean sartzea da. file.

- WinCUPL menu nagusian, hautatu Exekutatu> Gailuaren menpeko konpilazioa.

- WinCUPL-ek diseinua konpilatzen du eta Atmel gailu egokitzailea sortzen du. Diseinua egokitzen bada, JEDEC bat file automatikoki sortzen da.

- JEDEC-ek file gailuan programatuta dago, JTAG interfazea, aukerako barneko TMS eta TDI pull-upak eta hautazko pin-keeper zirkuituak gaituta daude.

Oharra: Atmel ISP gailu mota bat hautatzeak automatikoki gaitzen du JTAG interfazea lehenespenez Atmel WinCUPL-ek Atmel gailu egokitzailea exekutatzen duenean.

Diseinuek baliabideak erreserbatzea eragozten badute JTAG interfazea edo ISP bat aukeran ez da erabiltzen, Atmel ez-ISP gailu mota bat hautatu behar da. Ikusi beheko taula gailuen zerrenda ikusteko. Ondoren, gailua berriro programatu daiteke kanpoko gailu programatzaile baten bidez. Beheko taulan WinCUPLrako Atmel ISP eta Atmel ez-ISP gailu motak zerrendatzen dira.

3-2 Taula WinCUPL ATF15xx Gailu Mota

| Gailuaren izena | Pakete mota | WinCUPL Gailu Mota | |

| JTAG Gaituta | JTAG Ezindua | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Gaitu JTAG Atmel ProChip Designer-ekin interfazea

JTAG Interfazea ProChip Designer-ekin:

- Ireki ProChip Designer proiektu egokia.

- Ireki Fitter Aukerak leihoa Atmel Fitter botoian klik eginez Device Fitter.

- Hautatu gailu globala fitxa eta egiaztatu JTAG Portuko kutxa. TMS eta TDI barne-erresistentziak ere gaitu daitezke TDI Pullup eta TMS Pullup laukiak egiaztatuz. Kontrol-lauki hauek beheko irudian agertzen dira.

3-1 Irudia ProChip Designer Fitter Aukerak Erabiltzaile Interfazea

Gaitu JTAG POF2JED-rekin interfazea

POF2JED-en, JTAG Modu aukera Auto moduan ezar daiteke POF2JEDek JTAG ATF15xx-en eginbidea gaituta egon behar da edo ez, eta JTAG lehiakidearen CPLD-n onartzen da. J aktibatzekoTAG ATF15xx CPLDn, JTAG lehiakidearen CPLDan onartzen da edo ez, JTAG Modu aukera Aktibatu gisa ezarri behar da. JTAG ATF15xx-n gaituta dago, TDI eta TMS barne-erresistentziak gaitu daitezke Gaitu hautatuta.

TDI_PULLUP eta Gaitu TMS_PULLUP kutxak POF2JED-en. Ikus beheko irudia.

3-2 Irudia POF2JED Erabiltzaile Interfazea

Jarraibideak eta Gomendioak

Arreta: Atal honi arreta berezia jarri behar zaio ATF15xx CPLDetan ISP eragiketak egitean. Atal honetan JTAG Ondo kontuan hartu beharreko ISPren jarraibideak, informazioa eta gomendioak.

- Ziurtatu JTAG ataka J-ko gailu guztientzatTAG katea gaituta daude.

- ATF15xx CPLDetarako, JTAG ataka gaituta dago gailuak hutsik/ezabatuta edo J-rekin programatuta badaudeTAG gaituta.

- Atmel ATF15xx gailu guztiak hutsik/ezabatutako egoeran bidaltzen dira; beraz, JTAG ataka gailu berri guztietarako gaituta dago eta ISPrako prest dago.

- ATF15xx gailuak JTAG desgaituak ezabatu behar dira ISP ez den gailu programatzaile bat erabiliz JTAG portua.

- Ziurtatu VCC voltagJ-ko gailu bakoitzari e aplikatzen zaioTAG katea.

- 15-PLCC, 84-TQFP eta 100-PQFP pakete motetan ATF100xxAS/ASL CPLDak: VCCINTek 4.5 V eta 5.5 V artean egon behar du, eta VCCIO 3.0 V eta 3.6 V edo 4.5 V eta 5.5 V artean egon daiteke.

- ATF15xxAS/ASL CPLD 44-PLCC eta 44-TQFP pakete motetan: VCC-k 4.5 V eta 5.5 V artean izan behar du.

- ATF15xxASV/ASVL CPLDak: VCC (VCCIO eta VCCINT) 3.0 V eta 3.6 V artean egon behar du.

- J.-ko gailuetarako VCCaTAG katea behar bezala erregulatu eta iragazi behar da.

- Aplikazio gehienetan erabiltzen diren ATF15xx CPLDetarako, 0.22µF desakoplatze-kondentsadore bat erabiltzea gomendatzen da VCC/GND bikote bakoitzeko.

- J-ko gailu guztietarako oinarri komun bat erabiltzea gomendatzen daTAG katea eta JTAG interfazearen hardwarea (adibidez, ATDH1150USB ISP deskargatzeko kablea).

- Luzeak (bost gailu baino gehiago) saihestea gomendatzen da JTAG kateak.

- J luze bat badaTAG katea beharrezkoa da, buffer TMS eta TCK seinaleak bosgarren gailuaren ondoren. Schmitt trigger buffer-a erabiltzea hobetsi da.

- Bufferek TMS eta TCK seinaleen igoera eta jaitsiera denborak birmoldatzen dituzte.

- Bufferek eragindako atzerapen gehigarria kontuan hartu behar da.

- TMS eta TDI seinaleetarako pull-up erresistentzia (4.7KΩ eta 10KΩ) erabiltzea gomendatzen da eta J-n TCK seinalerako pull-down erresistentzia.TAG goiburukoa seinale horiek flotatzen ez daitezen interfazearen hardwareak gidatzen ez dituenean.

- ATF15xx CPLD-etarako TMS eta TDI-n barneko pull-up aukerakoak daude eskuragarri.

- J amaitzea gomendatzen daTAG seinaleak JTAG goiburua.

- Bai aktiboak bai pasiboak onargarriak dira; hala ere, amaiera pasiboa hobesten da.

- Kable/PCB traza luzeak direla eta dei-deitasuna murrizten du.

- Amaiera da TMS eta TCKrentzat kritikoena.

- Gomendagarria da gailuen sarrera eta I/O guztiak JTAG katea, JTAG pinak, egoera estatikoan egon behar du ATF15xx CPLDak zarata minimizatzeko programatzen ari direnean.

- Atmel ATF15xx garapen/programatzaile-plaketako bat erabiltzen duzunean, VCC hautapen-jauzien posizioak aldatzen ari direnean plakaren energia itzali behar da.

- ATF15xx CPLDetarako, JTAG ISP erabilgarri dago pieza Pin bidez kontrolatutako itzali moduan dagoenean edo "potentzia baxuko" gailua lo dagoenean.

- Gailuaren egoera ISP eten ondoren:

- ISP eteten bada, I/O pin guztiak hiru adieraziko dira Pin-keeper zirkuituen egoera edozein dela ere.

- Partzialki programatutako gailuek zirkuitu plakako beste gailu batzuekin bus gatazkak sortzea eragozten du.

- ISP programazioan, I/O pin guztiak baldintza hauetako batean daude:

- Inpedantzia handiko egoera:

- Hutsik/ezabatutako gailu bat programatzen denean.

- Gailu bat berriro programatzen denean Pin-keeper zirkuituak desgaituta.

- Zirkuitu plakako ATF15xx CPLD-ekin konektatzen diren kanpoko gailuekin autobusen gatazkak saihesten ditu.

- Aurreko egoerara ahul loturik:

- Programatutako gailu bat Pin-keeper zirkuituak gaituta dituela berriro programatzen denean.

- I/O pinek aurreko logika maila mantentzen dute ISParen aurretik.

- ISP-k sistema-plakako beste gailu batzuen funtzionamenduan eragitea eragozten du.

- J anitz erabiltzeaTAG ez da gomendagarria taula bateko kateak.

- Gailuek J desberdinen artean elkarreragin dezaketeTAG kateak.

- Taula funtzionala da J guztietan gailu guztiak daudenean soilikTAG kateak ongi programatu dira.

- Gutxienez kate bateko gailu batean programazioak huts egiten badu beste JTAG kateak arrakastaz programatu dira:

- Atmel-ek edo ontzian dauden beste gailu batzuk kaltetu egin daitezke irteeren hiru egoeratan dauden autobus-arazoak direla eta.

- Sistema-plakaren egoera operatiboa zehaztu gabe dago; eta, beraz, funtzionamendu okerra gerta daiteke.

- J-ren artean zirkuitu aktiboak txertatzeaTAG goiburua eta JTAG ez da gomendagarria katean dauden gailuak. Zirkuitu aktiboak gaizki funtzionatzen badu, programazio/egiaztapen arazoak sor ditzake.

- Vol. mistoaren erabilerataggailua JTAG kateak ez dira gomendagarriak.

- Hauek dira JTAG VCC vol. desberdinak erabiltzen dituzten gailuekin kateaktages eta/edo interface voltages.

- Interfazea voltagBaliteke 5.0V-ko gailuetarako e mailak (VIL, VIH, VOL, VOH) bateragarriak ez izatea interfazearen vol.tag3.0V gailuetarako e mailak.

- ATMISP-k J-rekin komunikatzeko arazoak badituTAG gailuaren hardware katea, saiatu Self Calibrate edo Eskuz Kalibratu exekutatzen J-ren maiztasunak jaistekoTAG seinaleak.

- Ziurtatu ATDH1150USB kablearen LEDa piztuta dagoela eta berdea dagoela programazioa hasi aurretik. Ziurtatu ISP deskargatzeko kablea ATMISP softwarearekin behar bezala komunikatzeko gai dela.

- Ziurtatu VCC voltage ATDH1150USB kableari aplikatzen zaio.

- J.-ko lehen gailuak erabilitako VCCaTAG katea ATDH1150USB kableari hornitu behar zaio 4 pin J-ko 10. pinaren bidezTAG goiburua.

- VCCINT eta VCCIO bereizitako ATF15xx CPLDetarako, VCCIO erabili behar da ATDH1150USB kablerako.

Eskaeraren informazioa

| Agindu Kodea | Deskribapena |

| ATF15xx-DK3-U | CPLD garapen/programatzaile kit (ATF15xxDK3-SAA44 eta ATDH1150USB edo ATDH1150USB-K barne) |

| ATF15xxDK3-SAA100 | 100 pin TQFP entxufe egokitzailea DK3 plakarako |

| ATF15xxDK3-SAJ44 | DK44 plakarako 3 pin PLCC entxufe egokitzailea |

| ATF15xxDK3-SAJ84 | DK84 plakarako 3 pin PLCC entxufe egokitzailea |

| ATF15xxDK3-SAA44 | 44 pin TQFP entxufe egokitzailea DK3 plakarako |

| ATDH1150USB | Atmel ATF15xx CPLD USB-en oinarritutako JTAG ISP deskargatzeko kablea |

Berrikuspen historia

| Dok. Errev. | Data | Iruzkinak |

| A | 12/2015 | Hasierako dokumentuaren kaleratzea. |

HARREMANETARAKO INFORMAZIOA

Atmel Korporazioa

- 1600 Technology Drive, San Jose, CA 95110 AEB

- Telefonoa: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_User Guide-12/2015

Atmel®, Atmel logotipoa eta horien konbinazioak, Enabling Unlimited Possibilities® eta beste batzuk Atmel Corporation-en marka erregistratuak edo marka komertzialak dira AEBetan eta beste herrialde batzuetan. Beste termino eta produktuen izenak besteen marka komertzialak izan daitezke.

LEHEN OHARRA: Dokumentu honetako informazioa Atmel produktuekin lotuta dago. Dokumentu honen bidez edo Atmel produktuen salmentarekin lotuta, ez da inolako lizentziarik, espresuki edo inplizituki, deuseztatuta edo bestela, jabetza intelektualeko eskubiderik ematen. ATMEL-EN KOKATUTAKO SALMENTA-BALDINTZA ETA BALDINTZAK EZATUTAKOA IZAN EZ WEBGUNEA, ATMEL-ek EZ DU EZ DIO EZOLAKO ERANTZUKIZUN ERABILTZEN ETA BERE PRODUKTUEI BURUZKO BERME ESPERIALIZKO, INPLIZITU ETA LEGEZKO BERME EZKO DU. ATMEL EZ DA INOLA EZ DUTE ERANTZUKIZUNA ERABILTZEKO GAITASUNAK ERABILTZEKO GAITASUNAK SORTZEN DITUZTEN KALTE ZUZENEKO, ZEHHENAK, ONDORIOZKO, ZIGORREZ, BEREZI EDO BEHARREKO KALTEEN Erantzukizunik ERABILI DOKUMENTU HAU, NAHIZ ATMEL-ek KALTE HONEK EGITEKO AUKERA EGON IZAN DU. Atmel-ek ez du inolako adierazpenik edo bermerik ematen dokumentu honen edukiaren zehaztasunari edo osotasunari buruz eta edozein unetan zehaztapenetan eta produktuen deskribapenetan aldaketak egiteko eskubidea gordetzen du jakinarazi gabe. Atmel-ek ez du inongo konpromisorik hartzen hemen jasotako informazioa eguneratzeko. Berariaz bestelakorik xedatu ezean, Atmel produktuak ez dira egokiak eta ez dira automobilgintzako aplikazioetan erabiliko. Atmel-eko produktuak ez daude diseinatuta, baimenduta edo bermatuta, bizitzari eusteko edo iraunarazteko xedea duten aplikazioetan osagai gisa erabiltzeko. SEGURTASUN KRITIKOA, MILITAR ETA AUTOMOTITZAKO APLIKAZIOEN EZEN OHARRA: Atmel produktuak ez daude diseinatuta eta ez dira erabiliko produktu horien hutsegiteek kalte pertsonal garrantzitsuak edo heriotza eragin dezaketen aplikazioetarako («Segurtasun-kritikoa Aplikazioak”) Atmel-eko ofizial baten berariazko idatzizko baimenik gabe. Segurtasunerako funtsezkoak diren aplikazioak, mugarik gabe, bizi-euskarriko gailuak eta sistemak, instalazio nuklearrak eta arma-sistemak ustiatzeko ekipoak edo sistemak dira. Atmel produktuak ez daude diseinatuta, ezta aplikazio militar edo aeroespazialetan edo inguruneetan erabiltzeko ere, Atmel-ek maila militar gisa izendatu ezean. Atmel produktuak ez daude diseinatuta, ezta automobilgintzako aplikazioetan erabiltzeko ere, Atmel-ek berariaz automozio-maila gisa izendatu ezean.

Dokumentuak / Baliabideak

|

Atmel ATF15xx Gailu Logiko Programagarri Konplexua [pdfErabiltzailearen gida ATF15xx, ATF15xx Gailu logiko programagarri konplexua, Gailu logiko programagarri konplexua, Gailu logiko programagarria, Gailu logikoa, Gailua |