Комплексно програмируемо логическо устройство Atmel ATF15xx

Спецификации

- Име на продукта: Atmel ATF15xx In-System Programming

- Модел: ATF15xx

- Тип: Комплексно програмируемо логическо устройство (CPLD)

- Метод на програмиране: Вътрешносистемно програмиране (ISP)

- Интерфейс: JTAG Интерфейс на ISP

- Производител: Atmel

Често задавани въпроси

Въпрос: Мога ли да използвам софтуер за програмиране на трети страни с ATF15xx CPLD?

О: Да, стига софтуерът да поддържа алгоритъма за програмиране и JTAG инструкции, необходими за ATF15xx CPLD.

В: Възможно ли е едновременно програмиране на множество ATF15xx CPLD?

О: Да, JTAG Интерфейсът на ISP поддържа програмиране на множество устройства за ефективно програмиране на множество CPLD наведнъж.

Въведение

- Комплексните програмируеми логически устройства Atmel® ATF15xx (CPLD) с архитектура Logic Doubling® поддържат вътрешносистемно програмиране (ISP) чрез IEEE Std. 1149.1 Група за съвместно изпитване (JTAG) интерфейс. Тази функция подобрява гъвкавостта на програмирането и осигурява предимства в различни фази; разработване на продукти, производство и използване на място. Това ръководство за потребителя описва методите за проектиране и изискванията за внедряване на ISP на ATF15xx CPLD с поддръжка на ISP, както е посочено по-долу:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Характеристики и предимства

Вътрешното системно програмиране позволява програмиране и препрограмиране на ISP устройства, след като са монтирани върху печатни платки (PCB). Това елиминира допълнителната стъпка на манипулиране, необходима в производствения процес за програмиране на устройствата на външен програматор на устройства, преди да бъдат монтирани на печатни платки. Премахването на тази стъпка намалява възможността от повреда на деликатните проводници на устройства за повърхностен монтаж с висок брой щифтове или повреда на устройството чрез електростатичен разряд (ESD) по време на процеса на програмиране. ISP също така позволява на потребителите да правят промени в дизайна и полеви надстройки, без да се налага да премахват ISP устройствата от печатните платки. Освен това, той също така позволява използването на вграден микроконтролер или вътрешен тестер за извършване на операции по системно програмиране на устройствата на ISP и интегриране на тези операции по програмиране в производствения поток на печатните платки.

Системи за вътрешносистемно програмиране

Трите основни компонента на ISP система за ATF15xx CPLD са:

Софтуер

Внедряването на програмния алгоритъм, както и генерирането на JTAG инструкции и данни за целевите ISP устройства. Това може да бъде софтуерна програма, работеща на компютър, вграден микроконтролер или оборудване за тестване във верига.

Хардуер на интерфейса

Комуникационен канал между ISP софтуера и ISP устройствата на целевата платка. Това може да бъде кабел за изтегляне на ISP или програмист от Atmel или доставчик на трета страна, оборудване за тестване във веригата или връзките между вграден микроконтролер и ISP устройства на PCB

Целева дъска

Печатна платка, съдържаща ISP устройствата в JTAG верига. Това може да бъде платката за разработка/програмиране ATF15xx CPLD от Atmel или специално проектирана платка с подходящия JTAG връзки към хардуера на интерфейса.

В допълнение към тези три компонента, JEDEC file е необходимо за програмиране на ATF15xx CPLD. Този JEDEC file може да се създаде чрез компилиране на дизайн file използване на софтуер за разработка, който поддържа ATF15xx CPLD, като Atmel WinCUPL и Atmel ProChip Designer. Atmel също така предоставя помощна програма за софтуер за превод, POF2JED.exe, която преобразува изхода file от програмния формат на конкурента до JEDEC file съвместим с ATF15xx CPLD. За повече информация относно тази помощна програма, моля, вижте бележката за приложението на Atmel, „Преобразуване на семейство продукти ATF15xx“, налична на Atmel webсайт. След JEDEC files са създадени за всички ATF15xx CPLD, те могат да бъдат програмирани на целевата платка. ATF15xx CPLD могат да бъдат програмирани от следните системи за програмиране в системата:

- ATF15xx Система за вътрешносистемно програмиране

- Вградени микроконтролери

- Вътрешни тестери

Система за вътрешносистемно програмиране Atmel ATF15xx

За вътрешносистемно програмиране на ATF15xx CPLD, ISP софтуер, кабел за изтегляне и комплект за разработка/програмиране се предлагат от Atmel и са описани в разделите по-долу.

ISP софтуер

Софтуерът Atmel ATF15xx ISP, ATMISP, е основното средство за внедряване на JTAG вътрешносистемно програмиране на ATF15xx CPLD. ATMISP работи на базиран на Windows хост компютър и прилага вътрешносистемно програмиране на ATF15xx CPLD на целевата хардуерна система на ISP или генерира сериен векторен формат (.SVF) file да се използва от оборудване за автоматично тестване (ATE) за програмиране на ATF15xx CPLD на целевата система. ATMISP първо получава цялата необходима информация от потребителите за JTAG верига от устройства в целевата система. След това изпълнява подходящия JTAG Инструкции на ISP на JTAG верига на устройства в целевата система според JTAG информация за веригата на устройството, зададена от потребителите през USB или LPT порта на компютъра. Повече информация за софтуера Atmel ATMISP можете да намерите на www.atmel.com/tools/ATMISP.aspx.

Кабел за изтегляне на ISP

Atmel ATF15xx USB-базиран ISP кабел за изтегляне, ATDH1150USB, се свързва към стандартен USB порт на хост компютър от едната страна и към JTAG заглавката на целевата платка от другата страна. Прехвърля ДжTAG инструкции и данни, генерирани от ATMISP, работещ на хост компютъра, към ISP устройствата на целевата печатна платка. Повече информация за кабела ATDH1150USB можете да намерите на www.atmel.com/tools/ATDH1150USB.aspx.

Разработка/Програмист

Atmel ATF15xx Development/Programmer Kit, ATF15xx-DK3-U, е цялостна система за разработка и ISP програмист за ATF15xx CPLD. Този комплект предоставя на дизайнерите много бърз и лесен начин за разработване на прототипи и оценка на нови дизайни с ATF15xx ISP CPLD. С наличието на различни адаптерни платки за гнезда за поддръжка на повечето типове пакети, предлагани в ATF15xx CPLD, този комплект може да се използва като ISP програмист за програмиране на ATF15xx ISP CPLD в повечето от наличните типове пакети чрез JTAG интерфейс. Повече информация за комплекта Atmel ATF15xx-DK3-U е достъпна на www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Вградена микроконтролерна система

Алгоритъмът за програмиране и ДжTAG инструкциите за ATF15xx CPLD могат да бъдат внедрени в микроконтролер или микропроцесор, който след това може да се използва за програмиране на ATF15xx CPLD на целевата платка. Един възможен метод е да се извлекат всички подходящи JTAG информация за протокола (т.е. JTAG инструкции и данни) от SVF file генериран от софтуера ATMISP, и след това използвайте тази информация, за да внедрите код за микроконтролера или микропроцесора, който ще генерира JTAG сигнали за ISP устройствата в JTAG верига. Този подход е най-подходящ за системи, които вече имат вграден микроконтролер или микропроцесор и това елиминира използването на външни софтуерни и хардуерни инструменти за програмиране в системата.

Вътрешна система за тестване

ATF15xx CPLD могат да бъдат програмирани на целевата платка чрез JTAG интерфейс по време на тестването на платката с помощта на вътрешен тестер. Като цяло SVF file генерирани от ATMISP, трябва да съдържат всички подходящи JTAG информация за вътрешносистемно програмиране, от която тестерите във веригата се нуждаят, за да програмират ATF15xx CPLD на целевата печатна платка. Този подход позволява интегрирането на програмната стъпка в тестванетоtage от производствения поток.

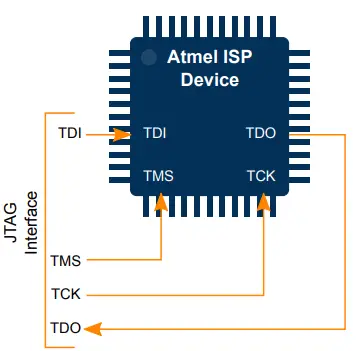

JTAG Интерфейс на ISP

ISP за ATF15xx CPLD се реализира с помощта на IEEE 1149.1 Std. ДжTAG интерфейс. Този интерфейс може да се използва за изтриване, програмиране и проверка на ATF15xx CPLD. ДжTAG интерфейсът е сериен интерфейс, състоящ се от сигналите TCK, TMS, TDI и TDO и JTAG Тествайте контролера за порт за достъп (TAP). Пинът TCK е входът на часовника за JTAG TAP контролер и за превключване на JTAG инструкции и данни. TDI щифтът е серийният вход за данни. Използва се за прехвърляне на инструкции за програмиране и данни в устройствата на ISP. Пинът TDO е серийният изход за данни. Използва се за изхвърляне на данни от устройствата на ISP. TMS щифтът е щифт за избор на режим. Той контролира състоянието на JTAG TAP контролер. ДжTAG интерфейсните щифтове на ATF15xx CPLD на целевата платка на ISP трябва да бъдат свързани към хардуера на интерфейса на ISP (т.е. кабел за изтегляне на ISP) обикновено чрез 10-пинов конектор. Хардуерът на интерфейса на ISP също трябва да бъде свързан към хост компютъра, на който работи софтуерът на ISP. Интерфейсният хардуер на ISP установява комуникация между софтуера на ISP и устройствата на ISP и позволява на софтуера на ISP да прехвърля инструкциите за програмиране и данните от хост компютъра към ATF15xx CPLD. ATF15xx CPLD с JTAG активираните функции са напълно JTAG съвместими и също така поддържат необходимите операции за тест за гранично сканиране (BST), посочени в JTAG стандартен. ATF15xx CPLD могат да бъдат конфигурирани да бъдат част от JTAG BST верига с други JTAG устройства за вътрешносхемно тестване на системната платка. С тази функция ATF15xx CPLD могат да бъдат тествани на платката заедно с други JTAG-поддържани устройства, без да се прибягва до тестване на леглото на ноктите.

Програмиране на едно устройство

ДжTAG Интерфейсът на ISP може да бъде конфигуриран да програмира един ATF15xx CPLD. ДжTAG конфигурация за едно устройство е показана на фигурата по-долу. Когато ATF15xx CPLD е конфигуриран по този начин, се появява регистър между TDI и TDO щифтовете на устройството. Размерът на регистъра зависи от JTAG ширината на инструкцията и данните, които се преместват за тази инструкция. Фигура 2-1 JTAG устройство

Програмиране на множество устройства

ATF15xx CPLD могат да бъдат конфигурирани като част от последователна верига от множество JTAG-поддържани устройства, както е описано по-долу и също показано на следващата фигура.

- Свържете TMS и TCK щифта за всяко устройство в JTAG верига към щифтовете TMS и TCK на JTAG заглавна част на интерфейса на платката.

- Свържете TDI щифта от първото устройство към TDI щифта на JTAG заглавка на интерфейса.

- Свържете TDO щифта от първото устройство към TDI щифта на следващото устройство. Продължете този процес, докато всички освен последния не бъдат свързани.

- Свържете TDO щифта от последното устройство към TDO щифта на JTAG заглавка на интерфейса.

Фигура 2-2 Множество устройства JTAG Конфигурация

За да програмирате множество устройства в JTAG верига, потребителите трябва да използват софтуерни инструменти на ISP, които поддържат такива функции. В софтуера на ISP потребителите трябва да посочат:

- Брой устройства в JTAG верига.

- Номерата на части на устройствата и позициите в JTAG верига.

- JTAG операции за всяко от устройствата.

- Други ДжTAG-свързана информация, като JTAG ширина на инструкциите за всяко от устройствата.

След като ДжTAG daisy chain е правилно настроен на целевата платка на ISP и в софтуера на ISP, устройствата в JTAG веригата може да се програмира едновременно.

Съображения за проектиране

За извършване на ISP на ATF15xx CPLD, ресурси за JTAG интерфейс в ATF15xx трябва да бъде запазен. Следователно четирите I/O пина за TMS, TDI, TDO и TCK пина трябва да бъдат запазени за JTAG и не може да се използва като потребителски I/O. Номерата на щифтовете за тези щифтове зависят от това кой ATF15xx CPLD се използва и неговия тип пакет. Обърнете се към таблицата по-долу за информация за pinout. ДжTAG стандартът препоръчва щифтовете TMS и TDI да бъдат изтеглени нагоре за всяко устройство в JTAG верига. ATF15xx CPLD имат вътрешна функция за изтегляне за тези щифтове, която, когато е активирана, спестява нуждата от външни издърпващи резистори. Освен това ДжTAG функцията за интерфейс трябва да бъде активирана, за да изпълнява ISP на ATF15xx CPLD. Разрешаване на JTAG интерфейсът изисква избор на специфични типове устройства на Atmel или настройки на опции, преди да компилирате дизайна ATF15xx. Тези процедури са описани за WinCUPL, ProChip Designer и POF2JED в това ръководство. По подразбиране всички чисто нови ATF15xx CPLD се доставят с JTAG интерфейсът е активиран. Веднъж логически ресурси за JTAG интерфейсът е запазен, потребителите могат да програмират, проверяват и изтриват всеки ATF15xx CPLD на целевата платка с помощта на софтуера ATMISP.

съвет: Въпреки че четиримата ДжTAG щифтовете са запазени за JTAG интерфейс, потребителите могат да прилагат скрити логически функции в макроклетките, свързани с тези щифтове.

Таблица 3-1 ATF15xx CPLD JTAG Pin номера

| JTAG ПИН | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Разрешете JTAG Интерфейс с WinCUPL

За да активирате JTAG интерфейс с WinCUPL, подходящият тип ATF15xx ISP устройство трябва да бъде указан, преди да бъде компилиран дизайн. След като дизайнът е успешно компилиран, JEDEC file с ДжTAG активирана интерфейсна функция се генерира. Когато този JEDEC file е програмиран в ATF15xxCPLD, неговият JTAG интерфейсът е активиран. Потребителите могат също така да активират TDI и TMS вътрешните издърпващи резистори, като включат следните изявления за свойства в дизайна на CUPL file.

- СВОЙСТВО ATMEL {TDI_PULLUP = ON};

- СВОЙСТВО ATMEL {TMS_PULLUP = ON};

Забележете: Ако тип устройство ATF15xx ISP се използва за дизайн, който използва JTAG интерфейсни щифтове като логически I/O щифтове, WinCUPL генерира грешка.

Следващите стъпки обсъждат как да отворите съществуващ дизайн в WinCUPL, да посочите типа устройство и да компилирате дизайна.

- В главното меню на WinCUPL изберете File > Отворете. Изберете източника CUPL (.pld). file от съответната работна директория.

- Изберете OK, за да отворите PLD източника file.

- В главното меню на WinCUPL изберете File > Запази. Това запазва промените, направени в източника file.

- В главното меню изберете Опции > Устройства. Това отваря диалоговия прозорец за избор на устройство.

- Изберете подходящото ISP устройство ATF15xx. Вижте следната таблица за списък на всички типове устройства ATF15xx, поддържани от WinCUPL.

- Изберете OK, за да затворите менюто за избор на устройство.

- Забележка: Алтернативен метод е да изберете подходящ тип устройство ATF15xx от следната таблица и да го включите в секцията за заглавка на източника на CUPL file.

- В главното меню на WinCUPL изберете Run> Device Dependent Compile.

- WinCUPL компилира дизайна и създава инструмента за монтиране на устройства Atmel. Ако дизайнът пасва, JEDEC file се създава автоматично.

- Когато JEDEC file е програмиран в устройството, JTAG интерфейс, опционалните вътрешни TMS и TDI издърпвания и опционалните вериги за поддържане на щифтове са активирани.

Забележка: Избирането на тип устройство на Atmel ISP автоматично активира JTAG интерфейс по подразбиране, когато Atmel WinCUPL изпълнява инструмента за монтиране на устройства на Atmel.

Ако проектите възпрепятстват запазването на ресурси за JTAG интерфейс или ISP по желание не се използва, трябва да бъде избран тип устройство Atmel, който не е ISP. Вижте таблицата по-долу за списък с устройства. След това устройството може да бъде препрограмирано с помощта на програматор на външно устройство. Таблицата по-долу изброява типовете устройства Atmel ISP и Atmel без ISP за WinCUPL.

Таблица 3-2 WinCUPL ATF15xx Тип устройство

| Име на устройството | Тип опаковка | WinCUPL тип устройство | |

| JTAG Активирано | JTAG Забранено | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Разрешете JTAG Интерфейс с Atmel ProChip Designer

За да активирате JTAG интерфейс с ProChip Designer:

- Отворете съответния проект на ProChip Designer.

- Отворете прозореца с опции на Fitter, като щракнете върху бутона Atmel Fitter под Device Fitter.

- Изберете раздела Глобално устройство и след това проверете JTAG Порт кутия. Вътрешните издърпващи резистори TMS и TDI също могат да бъдат активирани чрез отметка на квадратчетата TDI Pullup и TMS Pullup. Тези квадратчета за отметка са показани на фигурата по-долу.

Фигура 3-1 Потребителски интерфейс на ProChip Designer Fitter Options

Разрешете JTAG Интерфейс с POF2JED

В POF2JED, JTAG Опцията за режим може да бъде зададена на Auto, за да позволи на POF2JED да определи дали JTAG функцията в ATF15xx трябва да бъде активирана или не и зависи от това дали JTAG се поддържа в CPLD на конкурента. За да включите ДжTAG в ATF15xx CPLD, независимо дали JTAG поддържа ли се в CPLD на конкурента или не, JTAG Опцията за режим трябва да бъде включена. Когато ДжTAG е активиран в ATF15xx, вътрешните издърпващи резистори TDI и TMS могат да бъдат активирани чрез отметка на Enable

TDI_PULLUP и Активиране на полета TMS_PULLUP в POF2JED. Вижте фигурата по-долу.

Фигура 3-2 Потребителски интерфейс POF2JED

Насоки и препоръки

внимание: Трябва да се обърне допълнително внимание на този раздел, когато се извършват ISP операции на ATF15xx CPLD. Този раздел обсъжда някои от JTAG Насоки, информация и препоръки на ISP, които трябва да се вземат предвид.

- Уверете се, че JTAG порт за всички устройства в JTAG веригата са активирани.

- За ATF15xx CPLD, JTAG портът е активиран, ако устройствата са празни/изтрити или програмирани с JTAG активиран.

- Всички устройства Atmel ATF15xx се доставят в празно/изтрито състояние; следователно ДжTAG портът е активиран за всички чисто нови устройства и е готов за ISP.

- ATF15xx устройства с JTAG забранени трябва да бъдат изтрити с помощта на програматор на устройство, който не е доставчик на интернет услуги, за да активирате отново JTAG порт.

- Уверете се, че правилният VCC voltage се прилага към всяко от устройствата в JTAG верига.

- ATF15xxAS/ASL CPLD в типове пакети 84-PLCC, 100-TQFP и 100-PQFP: VCCINT трябва да бъде между 4.5 V и 5.5 V, докато VCCIO може да бъде между 3.0 V и 3.6 V или 4.5 V и 5.5 V.

- ATF15xxAS/ASL CPLD в типове пакети 44-PLCC и 44-TQFP: VCC трябва да бъде между 4.5 V до 5.5 V.

- ATF15xxASV/ASVL CPLD: VCC (VCCIO и VCCINT) трябва да бъде между 3.0 V до 3.6 V.

- VCC за устройствата в JTAG веригата трябва да бъде правилно регулирана и филтрирана.

- За ATF15xx CPLD, използвани в повечето приложения, се препоръчва да се използва един отделящ кондензатор 0.22µF за всяка от двойките VCC/GND.

- Препоръчително е да използвате обща основа за всички устройства в JTAG веригата и ДжTAG интерфейсен хардуер (т.е. ATDH1150USB ISP кабел за изтегляне).

- Препоръчително е да се избягват дълги (не повече от пет устройства) JTAG вериги.

- Ако дълго JTAG е необходима верига, буферирайте TMS и TCK сигналите след всяко пето устройство. За предпочитане е използването на тригерен буфер на Шмит.

- Буферите променят времето на нарастване и спадане на TMS и TCK сигналите.

- Трябва да се вземе предвид допълнителното забавяне, причинено от буферите.

- Препоръчително е да използвате изтеглящи резистори (4.7 KΩ до 10 KΩ) за TMS и TDI сигналите и изтеглящ резистор за TCK сигнала при JTAG заглавие, за да предотврати плаващи сигнали, когато не се управляват от хардуера на интерфейса.

- Допълнителни вътрешни издърпвания на TMS и TDI са налични за ATF15xx CPLD.

- Препоръчително е да прекратите JTAG сигнали на ДжTAG заглавка.

- Приемливи са както активни, така и пасивни прекъсвания; все пак пасивното прекратяване е за предпочитане.

- Намалява звъненето, дължащо се на дългите кабелни/печатни платки.

- Прекратяването е най-критично за TMS и TCK.

- Препоръчително е всички входове и I/O на устройствата в JTAG верига, с изключение на JTAG щифтове, трябва да са в статично състояние, когато ATF15xx CPLD се програмират за минимизиране на шума.

- Когато използвате една от платките за разработка/програмиране на Atmel ATF15xx, захранването на платката трябва да бъде изключено, когато позициите на джъмперите за избор на VCC се променят.

- За ATF15xx CPLD, JTAG ISP е наличен, когато частта е в режим на изключване, контролиран от щифта, или когато устройството с „ниска мощност“ е в режим на заспиване.

- Състояние на устройството след прекъсване на ISP:

- Ако ISP бъде прекъснат, всички I/O пинове са в три състояния, независимо от състоянието на веригите на Pin-keeper.

- Предотвратява частично програмирани устройства да причинят конкуренция на шината с други устройства на печатната платка.

- По време на програмирането на ISP всички I/O пинове са в едно от следните състояния:

- Състояние с висок импеданс:

- Когато е програмирано празно/изтрито устройство.

- Когато дадено устройство е препрограмирано с дезактивирани веригите на Pin-keeper.

- Предотвратява конкуренция на шина с външни устройства, взаимодействащи с ATF15xx CPLD на печатната платка.

- Слабо фиксиран към предишното състояние:

- Когато програмираното устройство се препрограмира с активирани схеми за поддържане на пин-кипер.

- I/O щифтовете запазват предишни логически нива преди ISP.

- Предотвратява ISP да повлияе на работата на други устройства на системната платка.

- Използването на множество JTAG вериги на една дъска не се препоръчва.

- Устройствата могат да взаимодействат между различни JTAG вериги.

- Платката е функционална само когато всички устройства във всички JTAG веригите са програмирани успешно.

- Ако програмирането е неуспешно за поне едно устройство във веригата, докато други JTAG вериги бяха успешно програмирани:

- Или Atmel, или други устройства на борда могат да бъдат повредени поради възможен проблем с конкуренцията на шината за три-stateable изходи.

- Работното състояние на системната платка е недефинирано; и следователно може да възникне неправилна функционална работа.

- Вмъкване на активни вериги между JTAG заглавката и JTAG устройства във веригата не се препоръчва. Ако активната верига не функционира правилно, това може да причини проблеми с програмирането/проверката.

- Използването на смесен обtagелектронно устройство JTAG вериги не се препоръчва.

- Това са ДжTAG вериги с устройства, които използват различни VCC обtages и/или интерфейс voltagес.

- Интерфейс обtage нивата (VIL, VIH, VOL, VOH) за 5.0V устройства може да не са съвместими с интерфейс voltage нива за 3.0V устройства.

- Ако ATMISP има проблем с комуникацията с JTAG хардуерна верига на устройството, опитайте да стартирате Self Calibrate или Manually Calibrate, за да намалите честотите на JTAG сигнали.

- Уверете се, че светодиодът на кабела ATDH1150USB е включен и свети в зелено, преди да започне програмирането. Уверете се, че кабелът за изтегляне на ISP може правилно да комуникира със софтуера ATMISP.

- Уверете се, че правилният VCC voltage се прилага към кабела ATDH1150USB.

- VCC, използван от първото устройство в JTAG веригата трябва да се подава към кабела ATDH1150USB чрез пин 4 на 10-пиновия JTAG заглавка.

- За ATF15xx CPLD с отделни VCCINT и VCCIO, VCCIO трябва да се използва за ATDH1150USB кабела.

Информация за поръчка

| Код за поръчка | Описание |

| ATF15xx-DK3-U | CPLD комплект за разработка/програмиране (включва ATF15xxDK3-SAA44 и ATDH1150USB или ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | 100-пинов TQFP адаптер за гнездо за платка DK3 |

| ATF15xxDK3-SAJ44 | 44-пинов PLCC адаптер за гнездо за платка DK3 |

| ATF15xxDK3-SAJ84 | 84-пинов PLCC адаптер за гнездо за платка DK3 |

| ATF15xxDK3-SAA44 | 44-пинов TQFP адаптер за гнездо за платка DK3 |

| ATDH1150USB | Atmel ATF15xx CPLD USB-базиран JTAG Кабел за изтегляне на ISP |

История на ревизиите

| Док. Rev. | Дата | Коментари |

| A | 12/2015 | Първоначално издаване на документ. |

ИНФОРМАЦИЯ ЗА КОНТАКТИ

Atmel Corporation

- 1600 Technology Drive, Сан Хосе, Калифорния 95110 САЩ

- Т: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Рев.: Atmel-8968A-CPLD-ATF-ISP_Ръководство за потребителя-12/2015

Atmel®, логото на Atmel и комбинациите от тях, Enabling Unlimited Possibilities® и други са регистрирани търговски марки или търговски марки на Atmel Corporation в САЩ и други страни. Други термини и имена на продукти може да са търговски марки на други.

ОТКАЗ ОТ ОТГОВОРНОСТ: Информацията в този документ е предоставена във връзка с продуктите на Atmel. Този документ или във връзка с продажбата на продуктите на Atmel не предоставя никакъв лиценз, изричен или подразбиращ се, чрез изключване или по друг начин, за право на интелектуална собственост. ОСВЕН КАКВОТО Е ПОСОЧЕНО В ПРАВИЛАТА И УСЛОВИЯТА ЗА ПРОДАЖБА НА ATMEL, РАЗПОЛОЖЕНИ В ATMEL WEBСАЙТ, ATMEL НЕ ПОЕМА НИКАКВА ОТГОВОРНОСТ И ОТХВЪРЛЯ ИЗРИЧНА, КОСВЕНА ИЛИ ЗАКОНОВА ГАРАНЦИЯ, СВЪРЗАНА С НЕГОВИТЕ ПРОДУКТИ, ВКЛЮЧИТЕЛНО, НО НЕ САМО, КОСВЕНАТА ГАРАНЦИЯ ЗА ПРОДАВАЕМОСТ, ГОДНОСТ ЗА ОПРЕДЕЛЕНА ЦЕЛ ИЛИ НЕНАРУШАВАНЕ МЕНТ. В НИКАКЪВ СЛУЧАЙ ATMEL НЕ НОСИ ОТГОВОРНОСТ ЗА НИКАКВИ ПРЕКИ, КОСВЕНИ, ПОСЛЕДВАЩИ, НАКАЗАТЕЛНИ, СПЕЦИАЛНИ ИЛИ СЛУЧАЙНИ ЩЕТИ (ВКЛЮЧИТЕЛНО, БЕЗ ОГРАНИЧЕНИЕ, ЩЕТИ ЗА ЗАГУБИ И ПЕЧАЛБИ, ПРЕКЪСВАНЕ НА БИЗНЕС ИЛИ ЗАГУБА НА ИНФОРМАЦИЯ), ПРОИЗТИЧАЩИ ОТ УПОТРЕБАТА ИЛИ НЕВЪЗМОЖНОСТ ЗА ИЗПОЛЗВАЙТЕ ТОЗИ ДОКУМЕНТ, ДОРИ АКО ATMEL Е БИЛА УВЕДОМЕНА ЗА ВЪЗМОЖНОСТТА ОТ ТАКИВА ЩЕТИ. Atmel не дава никакви декларации или гаранции по отношение на точността или пълнотата на съдържанието на този документ и си запазва правото да прави промени в спецификациите и описанията на продуктите по всяко време без предизвестие. Atmel не поема никакъв ангажимент да актуализира информацията, съдържаща се тук. Освен ако изрично не е предвидено друго, продуктите на Atmel не са подходящи и не трябва да се използват в автомобилни приложения. Продуктите на Atmel не са предназначени, разрешени или гарантирани за употреба като компоненти в приложения, предназначени да поддържат или поддържат живота. КРИТИЧНИ ЗА БЕЗОПАСНОСТТА, ВОЕННИ И АВТОМОБИЛНИ ПРИЛОЖЕНИЯ ОТКАЗ ОТ ОТГОВОРНОСТ: Продуктите на Atmel не са проектирани и няма да се използват във връзка с приложения, при които повредата на такива продукти би могло разумно да се очаква да доведе до значителни лични наранявания или смърт („Критични за безопасността“ Приложения”) без изричното писмено съгласие на служител на Atmel. Критични за безопасността приложения включват, без ограничение, животоподдържащи устройства и системи, оборудване или системи за експлоатация на ядрени съоръжения и оръжейни системи. Продуктите на Atmel не са проектирани, нито предназначени за използване във военни или аерокосмически приложения или среди, освен ако изрично не са определени от Atmel като военни. Продуктите на Atmel не са проектирани, нито предназначени за използване в автомобилни приложения, освен ако изрично не са определени от Atmel като автомобилни.

Документи / Ресурси

|

Комплексно програмируемо логическо устройство Atmel ATF15xx [pdf] Ръководство за потребителя ATF15xx, ATF15xx Комплексно програмируемо логическо устройство, Комплексно програмируемо логическо устройство, Програмируемо логическо устройство, Логическо устройство, Устройство |