Dyfais Rhesymeg Rhaglenadwy Cymhleth Atmel ATF15xx

Manylebau

- Enw'r Cynnyrch: Rhaglennu Mewn-System Atmel ATF15xx

- Model: ATF15xx

- Math: Dyfais Rhesymeg Rhaglenadwy Cymhleth (CPLD)

- Dull Rhaglennu: Rhaglennu Mewn-System (ISP)

- Rhyngwyneb: JTAG Rhyngwyneb ISP

- Gwneuthurwr: Atmel

Cwestiynau Cyffredin

C: A allaf ddefnyddio meddalwedd rhaglennu trydydd parti gyda'r ATF15xx CPLDs?

A: Ydy, cyn belled â bod y meddalwedd yn cefnogi'r algorithm rhaglennu a JTAG cyfarwyddiadau sydd eu hangen ar gyfer CPLDs ATF15xx.

C: A yw'n bosibl rhaglennu CPLDs ATF15xx lluosog ar yr un pryd?

A: Ydw, mae'r JTAG Mae rhyngwyneb ISP yn cefnogi rhaglennu dyfeisiau lluosog ar gyfer rhaglennu CPLDs lluosog yn effeithlon ar unwaith.

Rhagymadrodd

- Mae Dyfeisiau Rhesymeg Rhaglenadwy Cymhleth Atmel® ATF15xx (CPLDs) gyda phensaernïaeth Logic Doubling® yn cefnogi Rhaglennu Mewn-System (ISP) trwy'r IEEE Std. 1149.1 Grŵp Gweithredu Prawf ar y Cyd (JTAG) rhyngwyneb. Mae'r nodwedd hon yn gwella hyblygrwydd rhaglennu ac yn darparu buddion mewn cyfnodau amrywiol; datblygu cynnyrch, cynhyrchu, a defnydd maes. Mae'r canllaw defnyddiwr hwn yn disgrifio'r dulliau dylunio a'r gofynion ar gyfer gweithredu ISP ar ATF15xx CPLDs gyda chefnogaeth ISP fel y rhestrir isod:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Nodweddion a Manteision

Mae rhaglennu yn y system yn caniatáu rhaglennu ac ail-raglennu dyfeisiau ISP ar ôl iddynt gael eu gosod ar y Byrddau Cylchdaith Argraffedig (PCBs). Mae hyn yn dileu'r cam trin ychwanegol sydd ei angen yn y broses weithgynhyrchu i raglennu'r dyfeisiau ar raglennydd dyfeisiau allanol cyn iddynt gael eu gosod ar y PCBs. Mae dileu'r cam hwn yn lleihau'r posibilrwydd o niweidio gwifrau cain dyfeisiau gosod wyneb cyfrif pin uchel neu niweidio'r ddyfais trwy ryddhad electrostatig (ESD) yn ystod y llif rhaglennu. Mae ISP hefyd yn caniatáu i ddefnyddwyr wneud newidiadau dylunio ac uwchraddio maes heb orfod tynnu'r dyfeisiau ISP o'r PCBs. Ar ben hynny, mae hefyd yn caniatáu defnyddio microreolydd wedi'i fewnosod neu brofwr mewn cylched i gyflawni gweithrediadau rhaglennu mewn system ar y dyfeisiau ISP ac integreiddio'r gweithrediadau rhaglennu hyn i lif cynhyrchu'r byrddau cylched.

Systemau Rhaglennu Mewn-System

Y tair cydran hanfodol o system ISP ar gyfer yr ATF15xx CPLDs yw:

Meddalwedd

Gweithredu'r algorithm rhaglennu, yn ogystal â chynhyrchu'r JTAG cyfarwyddiadau a data ar gyfer y dyfeisiau targed ISP. Gall hyn fod yn rhaglen feddalwedd sy'n rhedeg ar gyfrifiadur personol, yn ficroreolydd wedi'i fewnosod, neu'n offer profi mewn cylched.

Caledwedd Rhyngwyneb

Sianel gyfathrebu rhwng meddalwedd ISP a dyfeisiau ISP ar y bwrdd targed. Gall hwn fod yn gebl lawrlwytho ISP neu raglennydd gan Atmel neu werthwr trydydd parti, offer profi mewn cylched, neu'r cysylltiadau rhwng microreolydd wedi'i fewnosod a dyfeisiau ISP ar y PCB

Bwrdd Targed

Bwrdd cylched yn cynnwys y dyfeisiau ISP yn y JTAG cadwyn. Gall hwn fod yn fwrdd Datblygu / Rhaglennydd CPLD ATF15xx o Atmel neu fwrdd cylched wedi'i ddylunio'n arbennig gyda'r J priodol.TAG cysylltiadau â chaledwedd y rhyngwyneb.

Yn ogystal â'r tair cydran hyn, mae JEDEC file yn angenrheidiol i raglennu CPLD ATF15xx. JEDEC hwn file gellir ei greu trwy lunio dyluniad file defnyddio meddalwedd datblygu sy'n cefnogi CPLDs ATF15xx fel Atmel WinCUPL ac Atmel ProChip Designer. Mae Atmel hefyd yn darparu meddalwedd cyfieithydd, POF2JED.exe, sy'n trosi allbwn file o fformat rhaglennu'r cystadleuydd i JEDEC file gydnaws â CPLD ATF15xx. I gael rhagor o wybodaeth am y cyfleustodau hwn, cyfeiriwch at nodyn cais Atmel, “Trosi Teulu Cynnyrch ATF15xx”, sydd ar gael ar yr Atmel websafle. Ar ôl y JEDEC files yn cael eu creu ar gyfer pob CPLD ATF15xx, gellir eu rhaglennu ar y bwrdd targed. Gall y CPLDs ATF15xx gael eu rhaglennu gan y systemau rhaglennu mewn-system canlynol:

- System Rhaglennu Mewn-System ATF15xx

- Microreolyddion wedi'u mewnblannu

- Profwyr mewn cylched

Atmel ATF15xx System Rhaglennu Mewn-System

Ar gyfer rhaglennu CPLDs ATF15xx yn y system, mae meddalwedd ISP, cebl lawrlwytho, a phecyn datblygu/rhaglennydd ar gael gan Atmel ac fe'u disgrifir yn yr adrannau isod.

Meddalwedd ISP

Meddalwedd ISP Atmel ATF15xx, ATMISP, yw'r prif ddull o weithredu JTAG rhaglennu yn y system ar yr ATF15xx CPLDs. Mae ATMISP yn rhedeg ar gyfrifiadur gwesteiwr Windows ac yn gweithredu rhaglennu CPLDs ATF15xx yn y system ar y system galedwedd ISP targed neu'n cynhyrchu Fformat Fector Cyfresol (.SVF) file i'w ddefnyddio gan Offer Profi Awtomatig (ATE) i raglennu'r ATF15xx CPLDs ar y system darged. Yn gyntaf mae ATMISP yn cael yr holl wybodaeth angenrheidiol gan y defnyddwyr am y JTAG cadwyn ddyfais yn y system darged. Yna mae'n gweithredu'r J priodolTAG Cyfarwyddiadau ISP i'r JTAG cadwyn ddyfais yn y system darged yn ôl y JTAG gwybodaeth cadwyn dyfais a bennir gan y defnyddwyr trwy borthladd USB neu LPT y PC. Mae rhagor o wybodaeth am feddalwedd Atmel ATMISP ar gael yn www.atmel.com/tools/ATMISP.aspx.

Cebl Lawrlwytho ISP

Mae Cebl Lawrlwytho ISP USB Atmel ATF15xx, ATDH1150USB, yn cysylltu â phorthladd USB safonol o gyfrifiadur gwesteiwr ar un ochr ac i J.TAG pennawd y bwrdd cylched targed ar yr ochr arall. Mae'n trosglwyddo'r JTAG cyfarwyddiadau a data a gynhyrchir gan ATMISP sy'n rhedeg ar y PC gwesteiwr i'r dyfeisiau ISP ar y bwrdd cylched targed. Mae mwy o wybodaeth am y cebl ATDH1150USB ar gael yn www.atmel.com/tools/ATDH1150USB.aspx.

Datblygiad/Rhaglennydd

Mae Pecyn Datblygu/Rhaglennydd Atmel ATF15xx, ATF15xx-DK3-U, yn system ddatblygu gyflawn ac yn rhaglennydd ISP ar gyfer CPLDs ATF15xx. Mae'r pecyn hwn yn rhoi ffordd gyflym a hawdd iawn i ddylunwyr ddatblygu prototeipiau a gwerthuso dyluniadau newydd gydag ISP CPLD ATF15xx. Gydag argaeledd y gwahanol fyrddau addasydd soced i gefnogi'r rhan fwyaf o'r mathau o becynnau a gynigir yn yr ATF15xx CPLDs, gellir defnyddio'r pecyn hwn fel rhaglennydd ISP i raglennu CPLDs ISP ATF15xx yn y rhan fwyaf o'r mathau o becynnau sydd ar gael trwy'r J.TAG rhyngwyneb. Mae mwy o wybodaeth am y pecyn Atmel ATF15xx-DK3-U ar gael yn www.atmel.com/tools/ATF15XX-DK3-U.aspx.

System Microreolydd Mewnosodedig

Mae'r algorithm rhaglennu a JTAG gellir gweithredu cyfarwyddiadau ar gyfer CPLDs ATF15xx mewn microreolydd neu ficrobrosesydd, y gellir ei ddefnyddio wedyn i raglennu CPLDs ATF15xx ar y bwrdd targed. Un dull posibl yw tynnu'r holl J perthnasolTAG gwybodaeth protocol (hy JTAG cyfarwyddiadau a data) o'r SVF file a gynhyrchir gan feddalwedd ATMISP, ac yna defnyddiwch y wybodaeth hon i weithredu cod ar gyfer y microreolydd neu'r microbrosesydd a fyddai'n cynhyrchu'r JTAG signalau ar gyfer y dyfeisiau ISP yn y JTAG cadwyn. Mae'r dull hwn yn fwyaf addas ar gyfer systemau sydd eisoes â micro-reolydd neu ficrobrosesydd wedi'i fewnosod, ac mae hyn yn dileu'r defnydd o feddalwedd rhaglennu allanol yn y system ac offer caledwedd.

System Profi Mewn Cylchdaith

Gellir rhaglennu'r CPLDs ATF15xx ar y bwrdd cylched targed trwy'r JTAG rhyngwyneb wrth brofi'r bwrdd cylched gan ddefnyddio profwr mewn cylched. Yn gyffredinol, y SVF file a gynhyrchir gan ATMISP gynnwys yr holl J perthnasolTAG gwybodaeth rhaglennu yn y system sydd ei hangen ar y profwyr mewn cylched i raglennu'r CPLDs ATF15xx ar y bwrdd cylched targed. Mae'r dull hwn yn caniatáu integreiddio'r cam rhaglennu i'r profion stage y llif cynhyrchu.

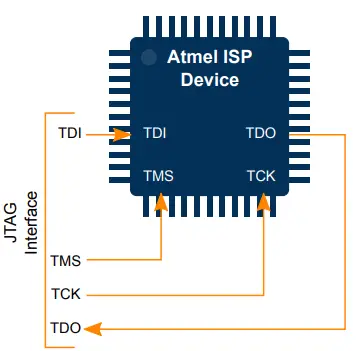

JTAG Rhyngwyneb ISP

Mae ISP ar gyfer CPLDs ATF15xx yn cael ei weithredu gan ddefnyddio'r IEEE 1149.1 Std. JTAG rhyngwyneb. Gellir defnyddio'r rhyngwyneb hwn i ddileu, rhaglennu a dilysu CPLDs ATF15xx. Mae'r JTAG rhyngwyneb cyfresol sy'n cynnwys y signalau TCK, TMS, TDI, a TDO a signal JTAG Rheolydd Porth Mynediad Profi (TAP). Y pin TCK yw'r mewnbwn cloc ar gyfer y JTAG Rheolydd TAP a symud y JTAG cyfarwyddiadau a data. Y pin TDI yw'r mewnbwn data cyfresol. Fe'i defnyddir i symud cyfarwyddiadau rhaglennu a data i mewn i'r dyfeisiau ISP. Y pin TDO yw'r allbwn data cyfresol. Fe'i defnyddir i symud data o'r dyfeisiau ISP. Mae'r pin TMS yn bin dewis modd. Mae'n rheoli cyflwr y JTAG Rheolydd TAP. Mae'r JTAG Rhaid cysylltu pinnau rhyngwyneb ATF15xx CPLD ar fwrdd targed yr ISP â chaledwedd rhyngwyneb ISP (hy cebl lawrlwytho ISP) fel arfer trwy bennawd 10-pin. Mae angen cysylltu caledwedd rhyngwyneb yr ISP hefyd â'r PC gwesteiwr sy'n rhedeg y meddalwedd ISP. Mae caledwedd rhyngwyneb ISP yn sefydlu cyfathrebu rhwng meddalwedd ISP a dyfeisiau ISP, ac mae'n caniatáu i feddalwedd yr ISP drosglwyddo'r cyfarwyddiadau rhaglennu a'r data o'r PC gwesteiwr i'r CPLDs ATF15xx. ATF15xx CPLDs gyda'r JTAG nodwedd wedi'i galluogi yn llawn JTAG gydnaws a hefyd yn cefnogi'r gweithrediadau Prawf Sganio Terfyn (BST) gofynnol a nodir yn y JTAG safonol. Gellir ffurfweddu CPLDs ATF15xx i fod yn rhan o JTAG Cadwyn BST gyda J eraillTAG dyfeisiau ar gyfer profi bwrdd system mewn cylched. Gyda'r nodwedd hon, gellir profi'r CPLDs ATF15xx ar y bwrdd cylched ynghyd â JTAG- cefnogi dyfeisiau heb droi at brofion gwely o ewinedd.

Rhaglennu Dyfais Sengl

Mae'r J.TAG Gellir ffurfweddu rhyngwyneb ISP i raglennu un CPLD ATF15xx. Mae'r JTAG dangosir cyfluniad ar gyfer dyfais sengl yn y ffigur isod. Pan fydd CPLD ATF15xx wedi'i ffurfweddu yn y modd hwn, mae cofrestr yn ymddangos rhwng pinnau TDI a TDO y ddyfais. Mae maint y gofrestr yn dibynnu ar y JTAG lled cyfarwyddyd a'r data'n cael ei symud i mewn ar gyfer y cyfarwyddyd hwnnw. Ffigur 2-1 JTAG Dyfais

Rhaglennu Dyfeisiau Lluosog

Gellir ffurfweddu CPLDs ATF15xx fel rhan o gadwyn llygad y dydd o luosog JTAG- cefnogi dyfeisiau fel y disgrifir isod a hefyd yn dangos yn y ffigur canlynol.

- Cysylltwch y pin TMS a TCK ar gyfer pob dyfais yn y JTAG cadwyn i binnau TMS a TCK y JTAG pennawd rhyngwyneb ar y bwrdd cylched.

- Cysylltwch y pin TDI o'r ddyfais gyntaf â phin TDI y JTAG pennawd rhyngwyneb.

- Cysylltwch y pin TDO o'r ddyfais gyntaf i bin TDI y ddyfais nesaf. Parhewch â'r broses hon nes bod pawb heblaw'r un olaf wedi'u cysylltu.

- Cysylltwch y pin TDO o'r ddyfais olaf â phin TDO y JTAG pennawd rhyngwyneb.

Ffigur 2-2 Dyfais Lluosog JTAG Cyfluniad

I raglennu dyfeisiau lluosog mewn JTAG gadwyn, rhaid i ddefnyddwyr ddefnyddio offer meddalwedd ISP sy'n cefnogi nodweddion o'r fath. Yn y meddalwedd ISP, mae angen i ddefnyddwyr nodi:

- Nifer y dyfeisiau yn y JTAG cadwyn.

- Rhifau rhannau o'r dyfeisiau a'r safleoedd o fewn y JTAG cadwyn.

- JTAG gweithrediadau ar gyfer pob un o'r dyfeisiau.

- Arall JTAG- gwybodaeth gysylltiedig megis y JTAG lled cyfarwyddyd ar gyfer pob un o'r dyfeisiau.

Unwaith y daeth JTAG cadwyn llygad y dydd wedi'i sefydlu'n iawn ar fwrdd targed yr ISP ac yn y meddalwedd ISP, y dyfeisiau yn y JTAG gellir rhaglennu cadwyn ar yr un pryd.

Ystyriaethau Dylunio

I berfformio ISP ar CPLD ATF15xx, mae adnoddau ar gyfer y JTAG rhaid cadw rhyngwyneb yn yr ATF15xx. Felly, rhaid cadw'r pedwar pin I/O ar gyfer y pinnau TMS, TDI, TDO, a TCK ar gyfer JTAG ac ni ellir ei ddefnyddio fel defnyddiwr I/O. Mae'r rhifau pin ar gyfer y pinnau hyn yn dibynnu ar ba ATF15xx CPLD a ddefnyddir a'i fath o becyn. Cyfeiriwch at y tabl isod am wybodaeth pinout. Mae'r JTAG Mae safon yn argymell bod y pinnau TMS a TDI yn cael eu tynnu i fyny ar gyfer pob dyfais yn y JTAG cadwyn. Mae gan yr ATF15xx CPLDs nodwedd tynnu i fyny fewnol ar gyfer y pinnau hyn sydd, o'u galluogi, yn arbed yr angen am wrthyddion tynnu i fyny allanol. Ymhellach, mae'r JTAG rhaid galluogi nodwedd rhyngwyneb er mwyn perfformio ISP ar yr ATF15xx CPLDs. Gan alluogi'r JTAG rhyngwyneb yn gofyn am ddewis mathau penodol o ddyfais Atmel neu osodiadau opsiwn cyn llunio'r dyluniad ATF15xx. Amlinellir y gweithdrefnau hyn ar gyfer WinCUPL, ProChip Designer, a POF2JED yn y canllaw hwn. Yn ddiofyn, mae pob CPLD ATF15xx newydd sbon yn cael ei gludo gyda'r JTAG rhyngwyneb wedi'i alluogi. Adnoddau rhesymeg unwaith ar gyfer y JTAG rhyngwyneb yn cael eu cadw, gall defnyddwyr raglennu, gwirio, a dileu unrhyw CPLD ATF15xx ar y bwrdd targed gan ddefnyddio meddalwedd ATMISP.

Tip: Er bod y pedwar JTAG cedwir pinnau ar gyfer JTAG rhyngwyneb, gall defnyddwyr weithredu swyddogaethau rhesymeg claddedig yn y macrocells sy'n gysylltiedig â'r pinnau hyn.

Tabl 3-1 ATF15xx CPLD JTAG Rhifau Pin

| JTAG Pin | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Galluogi JTAG Rhyngwyneb â WinCUPL

Er mwyn galluogi'r JTAG rhyngwyneb â WinCUPL, mae angen nodi'r math dyfais ISP ATF15xx priodol cyn llunio dyluniad. Ar ôl i ddyluniad gael ei lunio'n llwyddiannus, bydd JEDEC file gyda'r JTAG nodwedd rhyngwyneb galluogi yn cael ei gynhyrchu. Pan fydd hyn JEDEC file wedi'i raglennu i mewn i ATF15xxCPLD, ei JTAG rhyngwyneb wedi'i alluogi. Gall defnyddwyr hefyd alluogi gwrthyddion tynnu i fyny mewnol TDI a TMS trwy gynnwys y datganiadau eiddo canlynol yn nyluniad CUPL file.

- ATMEL EIDDO {TDI_PULLUP = YMLAEN};

- ATMEL EIDDO {TMS_PULLUP = YMLAEN};

Hysbysiad: Os defnyddir math dyfais ISP ATF15xx ar gyfer dyluniad sy'n defnyddio'r JTAG pinnau rhyngwyneb fel pinnau rhesymeg I/O, mae WinCUPL yn cynhyrchu gwall.

Mae'r camau canlynol yn trafod sut i agor dyluniad presennol yn WinCUPL, nodi'r math o ddyfais, a llunio'r dyluniad.

- Ar brif ddewislen WinCUPL, dewiswch File > Agor. Dewiswch y ffynhonnell CUPL (.pld). file o'r cyfeiriadur gweithio priodol.

- Dewiswch Iawn i agor y ffynhonnell PLD file.

- Ar brif ddewislen WinCUPL, dewiswch File > Arbed. Mae hyn yn arbed newidiadau a wnaed i'r ffynhonnell file.

- Ar y brif ddewislen, dewiswch Opsiynau > Dyfeisiau. Mae hyn yn agor y blwch deialog Dewis Dyfais.

- Dewiswch y ddyfais ISP ATF15xx priodol. Gweler y tabl canlynol am restr o'r holl fathau o ddyfeisiau ATF15xx a gefnogir gan WinCUPL.

- Dewiswch Iawn i gau'r ddewislen dewis dyfais.

- Nodyn: Dull arall yw dewis math dyfais ATF15xx priodol o'r tabl canlynol a'i gynnwys yn adran pennawd y ffynhonnell CUPL file.

- Ar brif ddewislen WinCUPL, dewiswch Rhedeg> Llunio Dibynnol ar Ddychymyg.

- Mae WinCUPL yn llunio'r dyluniad ac yn silio'r gosodwr dyfais Atmel. Os yw'r dyluniad yn cyd-fynd, JEDEC file yn cael ei greu yn awtomatig.

- Pan fydd y JEDEC file wedi'i raglennu i'r ddyfais, mae'r JTAG rhyngwyneb, mae'r TMS mewnol dewisol a thynnu-ups TDI, a'r cylchedau pin-keeper dewisol yn cael eu galluogi.

Nodyn: Mae dewis math o ddyfais ISP Atmel yn awtomatig yn galluogi'r JTAG rhyngwyneb yn ddiofyn pan fydd Atmel WinCUPL yn rhedeg y gosodwr dyfais Atmel.

Os yw'r dyluniadau'n atal cadw adnoddau ar gyfer y JTAG nid yw rhyngwyneb neu ISP yn cael ei ddefnyddio'n ddewisol, rhaid dewis math o ddyfais Atmel nad yw'n ISP. Gweler y tabl isod am restr o ddyfeisiau. Yna gellir ail-raglennu'r ddyfais gan ddefnyddio rhaglennydd dyfais allanol. Mae'r tabl isod yn rhestru'r mathau o ddyfeisiau Atmel ISP ac Atmel nad ydynt yn ISP ar gyfer WinCUPL.

Tabl 3-2 WinCUPL ATF15xx Math o Ddychymyg

| Enw Dyfais | Math Pecyn | Math Dyfais WinCUPL | |

| JTAG Galluogwyd | JTAG Anabl | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Galluogi JTAG Rhyngwyneb â Dylunydd Atmel ProChip

Er mwyn galluogi'r JTAG rhyngwyneb gyda ProChip Designer:

- Agorwch y prosiect ProChip Designer priodol.

- Agorwch y ffenestr Fitter Options trwy glicio ar y botwm Atmel Fitter o dan Device Fitter.

- Dewiswch y tab Dyfais Byd-eang ac yna gwiriwch y JTAG Blwch porthladd. Gellir galluogi'r gwrthyddion tynnu i fyny mewnol TMS a TDI hefyd trwy wirio'r blychau TDI Pullup a TMS Pullup. Dangosir y blychau ticio hyn yn y ffigur isod.

Ffigur 3-1 Rhyngwyneb Defnyddiwr Opsiynau Ffitiwr Dylunydd ProChip

Galluogi JTAG Rhyngwyneb â POF2JED

Yn POF2JED, mae'r JTAG Gellir gosod opsiwn modd i Auto i adael i POF2JED benderfynu a yw'r JTAG dylid galluogi nodwedd yn yr ATF15xx ai peidio, ac mae'n seiliedig ar a yw JTAG yn cael ei gefnogi yn CPLD y cystadleuydd. I droi J ymlaenTAG yn yr ATF15xx CPLD ni waeth a yw JTAG yn cael ei gefnogi yn CPLD y cystadleuydd ai peidio, y JTAG Dylid gosod opsiwn modd i On. Pan oedd JTAG wedi'i alluogi yn yr ATF15xx, gellir galluogi'r gwrthyddion tynnu i fyny mewnol TDI a TMS trwy wirio'r Galluogi

TDI_PULLUP a Galluogi blychau TMS_PULLUP yn POF2JED. Gweler y ffigwr isod.

Ffigur 3-2 Rhyngwyneb Defnyddiwr POF2JED

Canllawiau ac Argymhellion

Sylw: Dylid rhoi sylw ychwanegol i'r adran hon wrth berfformio gweithrediadau ISP ar ATF15xx CPLDs. Mae'r adran hon yn trafod rhai o'r JTAG Canllawiau, gwybodaeth ac argymhellion ISP y dylid eu nodi'n dda.

- Gwnewch yn siŵr bod JTAG porthladd ar gyfer yr holl ddyfeisiau yn y JTAG cadwyn yn cael eu galluogi.

- Ar gyfer y CPLDs ATF15xx, mae'r JTAG porthladd wedi'i alluogi os yw'r dyfeisiau'n wag / wedi'u dileu neu wedi'u rhaglennu gyda JTAG galluogi.

- Mae holl ddyfeisiau Atmel ATF15xx yn cael eu cludo yn y cyflwr gwag / wedi'u dileu; felly, mae'r JTAG porthladd wedi'i alluogi ar gyfer pob dyfais newydd sbon ac yn barod ar gyfer ISP.

- Dyfeisiau ATF15xx gyda JTAG anabl gael ei ddileu gan ddefnyddio rhaglennydd dyfais nad yw'n ISP i ail-alluogi'r JTAG porthladd.

- Sicrhewch fod y VCC cywir cyftage yn cael ei gymhwyso at bob un o'r dyfeisiau yn y JTAG cadwyn.

- CPLDs ATF15xxAS/ASL mewn mathau o becynnau 84-PLCC, 100-TQFP, a 100-PQFP: rhaid i VCCINT fod rhwng 4.5V a 5.5V tra gall VCCIO fod rhwng 3.0V a 3.6V neu 4.5V a 5.5V.

- CPLDs ATF15xxAS/ASL mewn mathau o becynnau 44-PLCC a 44-TQFP: rhaid i VCC fod rhwng 4.5V a 5.5V.

- ATF15xxASV/ASVL CPLDs: Rhaid i VCC (VCCIO a VCCINT) fod rhwng 3.0V a 3.6V.

- Y VCC ar gyfer y dyfeisiau yn y JTAG rhaid i gadwyn gael ei reoleiddio a'i hidlo'n iawn.

- Ar gyfer y CPLDs ATF15xx a ddefnyddir yn y rhan fwyaf o gymwysiadau, argymhellir defnyddio un cynhwysydd datgysylltu 0.22µF ar gyfer pob un o'r parau VCC/GND.

- Argymhellir defnyddio tir cyffredin ar gyfer yr holl ddyfeisiau yn y JTAG cadwyn a'r JTAG caledwedd rhyngwyneb (hy ATDH1150USB ISP Download Cable).

- Argymhellir osgoi hir (dim mwy na phum dyfais) JTAG cadwyni.

- Os hir JTAG cadwyn yn angenrheidiol, clustogi'r signalau TMS a TCK ar ôl pob pumed dyfais. Mae'n well defnyddio byffer sbardun Schmitt.

- Mae byfferau yn ail-lunio amseroedd codi a chwympo'r signalau TMS a TCK.

- Angen cymryd i ystyriaeth yr oedi ychwanegol a achoswyd gan y byfferau.

- Argymhellir defnyddio gwrthyddion tynnu i fyny (4.7KΩ i 10KΩ) ar gyfer y signalau TMS a TDI a gwrthydd tynnu i lawr ar gyfer y signal TCK yn y JTAG pennawd i atal y signalau hyn rhag arnofio pan nad ydynt yn cael eu gyrru gan galedwedd y rhyngwyneb.

- Mae tynnu i fyny mewnol dewisol ar TMS a TDI ar gael ar gyfer yr ATF15xx CPLDs.

- Argymhellir terfynu JTAG signalau yn y JTAG pennyn.

- Mae terfyniadau gweithredol a goddefol yn dderbyniol; fodd bynnag, mae terfyniad goddefol yn well.

- Mae'n lleihau modrwyo oherwydd hyd olrhain cebl / PCB hir.

- Mae terfynu yn hollbwysig ar gyfer TMS a TCK.

- Argymhellir bod holl fewnbynnau ac I/O y dyfeisiau yn y JTAG gadwyn, heblaw y JTAG pinnau, fod mewn cyflwr statig pan fydd yr ATF15xx CPLDs yn cael eu rhaglennu i leihau sŵn.

- Wrth ddefnyddio un o fyrddau datblygu/rhaglennwr Atmel ATF15xx, rhaid diffodd pŵer y bwrdd pan fydd safleoedd y siwmperi dethol VCC yn cael eu newid.

- Ar gyfer y CPLDs ATF15xx, mae JTAG Mae ISP ar gael pan fydd y rhan yn y modd Power-down a reolir gan Pin neu pan fydd y ddyfais “pŵer isel” yn cysgu.

- Cyflwr dyfais ar ôl ymyrraeth ISP:

- Os amharir ar yr ISP, mae'r holl binnau I/O wedi'u nodi'n driphlyg waeth beth fo cyflwr y cylchedau Pin-keeper.

- Yn atal dyfeisiau sydd wedi'u rhaglennu'n rhannol rhag achosi cynnen mewn bysiau â dyfeisiau eraill ar y bwrdd cylched.

- Yn ystod rhaglennu ISP, mae pob pin I / O yn un o'r amodau canlynol:

- Cyflwr rhwystriant uchel:

- Pan fydd dyfais wag/wedi'i dileu yn cael ei rhaglennu.

- Pan fydd dyfais yn cael ei hail-raglennu gyda'r cylchedau Pin-keeper wedi'u hanalluogi.

- Yn atal cynnen bws gyda dyfeisiau allanol yn rhyngwynebu â'r ATF15xx CPLDs ar y bwrdd cylched.

- Wedi'i gysylltu'n wan â'r cyflwr blaenorol:

- Pan fydd dyfais wedi'i rhaglennu yn cael ei hail-raglennu gyda'r cylchedau Pin-keeper wedi'u galluogi.

- Mae pinnau I/O yn cadw lefelau rhesymeg blaenorol cyn ISP.

- Yn atal ISP rhag effeithio ar weithrediad dyfeisiau eraill ar fwrdd y system.

- Y defnydd o luosog JTAG nid yw cadwyni ar un bwrdd yn cael ei argymell.

- Gall dyfeisiau ryngweithio rhwng gwahanol JTAG cadwyni.

- Mae'r bwrdd yn weithredol dim ond pan fydd pob dyfais ym mhob JTAG cadwyni yn cael eu rhaglennu'n llwyddiannus.

- Os bydd rhaglennu yn methu ar gyfer o leiaf un ddyfais mewn cadwyn tra bod un arall JTAG rhaglennwyd cadwyni yn llwyddiannus:

- Gall naill ai Atmel neu ddyfeisiau eraill ar fwrdd y llong gael eu difrodi oherwydd problem gynnen bws bosibl ar gyfer allbynnau tri-datganadwy.

- Nid yw cyflwr gweithredol bwrdd y system wedi'i ddiffinio; ac felly, gall y gweithrediad swyddogaethol anghywir ddigwydd.

- Mewnosod cylchedau gweithredol rhwng JTAG pennawd a'r JTAG ni argymhellir dyfeisiau mewn cadwyn. Os bydd cylchedau gweithredol yn camweithio, gall achosi problemau rhaglennu/gwirio.

- Mae'r defnydd o gymysg-cyftage ddyfais JTAG ni argymhellir cadwyni.

- Dyma JTAG cadwyni gyda dyfeisiau sy'n defnyddio gwahanol VCC cyftages a/neu ryngwyneb cyftages.

- Rhyngwyneb cyftagefallai na fydd lefelau e (VIL, VIH, VOL, VOH) ar gyfer dyfeisiau 5.0V yn gydnaws â chyfrol rhyngwynebtage lefelau ar gyfer dyfeisiau 3.0V.

- Os oes gan ATMISP broblem wrth gyfathrebu â'r JTAG cadwyn caledwedd dyfais, ceisiwch redeg Self Calibro neu Calibro â Llaw i ostwng amlder y JTAG signalau.

- Gwnewch yn siŵr bod y LED ar y cebl ATDH1150USB wedi'i droi ymlaen a'i fod yn wyrdd cyn i'r rhaglennu ddechrau. Sicrhewch fod y cebl lawrlwytho ISP yn gallu cyfathrebu'n iawn â meddalwedd ATMISP.

- Sicrhewch fod y VCC cywir cyftage yn cael ei gymhwyso i'r cebl ATDH1150USB.

- Y VCC a ddefnyddir gan y ddyfais gyntaf yn y JTAG rhaid cyflenwi cadwyn i'r cebl ATDH1150USB trwy bin 4 o'r J 10-pinTAG pennyn.

- Ar gyfer ATF15xx CPLDs gyda VCCINT a VCCIO ar wahân, dylid defnyddio VCCIO ar gyfer y cebl ATDH1150USB.

Gwybodaeth Archebu

| Cod Archebu | Disgrifiad |

| ATF15xx-DK3-U | Pecyn Datblygu/Rhaglennydd CPLD (yn cynnwys yr ATF15xxDK3-SAA44 ac ATDH1150USB neu ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | Bwrdd addasydd soced TQFP 100-pin ar gyfer Bwrdd DK3 |

| ATF15xxDK3-SAJ44 | Bwrdd addasydd soced PLCC 44-pin ar gyfer Bwrdd DK3 |

| ATF15xxDK3-SAJ84 | Bwrdd addasydd soced PLCC 84-pin ar gyfer Bwrdd DK3 |

| ATF15xxDK3-SAA44 | Bwrdd addasydd soced TQFP 44-pin ar gyfer Bwrdd DK3 |

| ATDH1150USB | Atmel ATF15xx CPLD seiliedig ar USB JTAG Cebl Lawrlwytho ISP |

Hanes Adolygu

| Doc. Parch. | Dyddiad | Sylwadau |

| A | 12/2015 | Rhyddhau dogfen gychwynnol. |

GWYBODAETH GYSWLLT

Corfforaeth Atmel

- 1600 Technology Drive, San Jose, CA 95110 UDA

- T: (+1)(408) 441.0311

- Dd: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_User Guide-12/2015

Mae Atmel®, logo Atmel a chyfuniadau ohonynt, Galluogi Unlimited Possibilities®, ac eraill yn nodau masnach cofrestredig neu'n nodau masnach Atmel Corporation yn yr UD a gwledydd eraill. Gall termau ac enwau cynnyrch eraill fod yn nodau masnach eraill.

YMWADIAD: Darperir y wybodaeth yn y ddogfen hon mewn cysylltiad â chynhyrchion Atmel. Nid yw'r ddogfen hon nac mewn cysylltiad â gwerthu cynhyrchion Atmel yn rhoi unrhyw drwydded, yn benodol neu'n oblygedig, trwy estopel neu fel arall, i unrhyw hawl eiddo deallusol. AC EITHRIO FEL A NODIR YN Y TELERAU AC AMODAU GWERTHIANT ATMEL A LEOLIR AR YR ATMEL WEBSAFLE, NID YW ATMEL YN DYCHMYGU UNRHYW ATEBOLRWYDD O BETH FELLY AC YN GWRTHOD UNRHYW WARANT MYNEGOL, GOBLYGEDIG, NEU WARANT STATUDOL YNGHYLCH EI CHYNHYRCHION GAN GYNNWYS, OND NID YN GYFYNGEDIG I'R GWARANT OBLYGEDIG O FEL HYSBYSIAD, CYFIAWNDER AR GYFER PERTHNASOL, A CHYFIAWNDER. NI DDYLAI ATMEL FODD YN ATEBOL AM UNRHYW DDIFROD UNIONGYRCHOL, ANUNIONGYRCHOL, GANLYNIADOL, COSBUS, ARBENNIG, NEU ANGENRHEIDIOL (GAN GYNNWYS, HEB GYFYNGIAD, IAWNDAL COLLI AC Elw, Amhariad BUSNES, NEU GOLLI GWYBODAETH) OHERWYDD UNIONGYRCHOL, NEU GOLLI GWYBODAETH. DOGFEN, HYD YN OED OS YW ATMEL WEDI HYSBYSU POSIBILRWYDD DIFROD O'R FATH. Nid yw Atmel yn gwneud unrhyw sylwadau na gwarantau mewn perthynas â chywirdeb na chyflawnrwydd cynnwys y ddogfen hon ac mae'n cadw'r hawl i wneud newidiadau i fanylebau a disgrifiadau cynnyrch ar unrhyw adeg heb rybudd. Nid yw Atmel yn gwneud unrhyw ymrwymiad i ddiweddaru'r wybodaeth a gynhwysir yma. Oni bai y darperir yn benodol fel arall, nid yw cynhyrchion Atmel yn addas ar gyfer cymwysiadau modurol, ac ni ddylid eu defnyddio. Nid yw cynhyrchion Atmel wedi'u bwriadu, eu hawdurdodi na'u gwarantu i'w defnyddio fel cydrannau mewn cymwysiadau a fwriedir i gynnal neu gynnal bywyd. CEISIADAU DIOGELWCH-CRINACHOL, MILWROL A MODUROL: Nid yw cynhyrchion Atmel wedi'u cynllunio ar gyfer ac ni chânt eu defnyddio mewn cysylltiad ag unrhyw geisiadau lle byddai disgwyl yn rhesymol i fethiant cynhyrchion o'r fath arwain at anaf personol sylweddol neu farwolaeth (“Ceisiadau Diogelwch Hanfodol”) heb ganiatâd ysgrifenedig penodol swyddog Atmel. Mae cymwysiadau sy'n hanfodol i ddiogelwch yn cynnwys, heb gyfyngiad, dyfeisiau a systemau cynnal bywyd, offer neu systemau ar gyfer gweithredu cyfleusterau niwclear a systemau arfau. Nid yw cynhyrchion Atmel wedi'u dylunio na'u bwriadu i'w defnyddio mewn cymwysiadau neu amgylcheddau milwrol neu awyrofod oni bai eu bod wedi'u dynodi'n benodol gan Atmel fel gradd filwrol. Nid yw cynhyrchion Atmel wedi'u dylunio na'u bwriadu i'w defnyddio mewn cymwysiadau modurol oni bai eu bod wedi'u dynodi'n benodol gan Atmel fel gradd modurol.

Dogfennau / Adnoddau

|

Dyfais Rhesymeg Rhaglenadwy Cymhleth Atmel ATF15xx [pdfCanllaw Defnyddiwr ATF15xx, Dyfais Rhesymeg Rhaglenadwy Cymhleth ATF15xx, Dyfais Rhesymeg Rhaglenadwy Cymhleth, Dyfais Rhesymeg Rhaglenadwy, Dyfais Rhesymeg, Dyfais |