Atmel ATF15xx Kompleksowe programowalne urządzenie logiczne

Specyfikacje

- Nazwa produktu: Atmel ATF15xx programowanie w systemie

- Model: ATF15xx

- Typ: Złożone programowalne urządzenie logiczne (CPLD)

- Metoda programowania: programowanie w systemie (ISP)

- Interfejs: JTAG Interfejs dostawcy usług internetowych

- Producent: Atmel

Często zadawane pytania

P: Czy mogę używać oprogramowania programującego innych firm z układami CPLD ATF15xx?

O: Tak, o ile oprogramowanie obsługuje algorytm programowania i JTAG instrukcje wymagane dla układów CPLD ATF15xx.

P: Czy możliwe jest programowanie wielu układów CPLD ATF15xx jednocześnie?

A: Tak, JTAG Interfejs ISP obsługuje programowanie wielu urządzeń, co pozwala na efektywne programowanie wielu układów CPLD jednocześnie.

Wstęp

- Układy CPLD Atmel® ATF15xx z architekturą Logic Doubling® obsługują programowanie wewnątrz systemu (ISP) zgodnie z normą IEEE Std. 1149.1 Joint Test Action Group (JTAG) interfejs. Ta funkcja zwiększa elastyczność programowania i zapewnia korzyści w różnych fazach: rozwoju produktu, produkcji i użytkowania w terenie. W tym podręczniku użytkownika opisano metody projektowania i wymagania dotyczące implementacji ISP na układach CPLD ATF15xx z obsługą ISP, jak wymieniono poniżej:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Cechy i korzyści

Programowanie w systemie umożliwia programowanie i ponowne programowanie urządzeń ISP po ich zamontowaniu na płytkach drukowanych (PCB). Eliminuje to dodatkowy etap obsługi wymagany w procesie produkcyjnym w celu zaprogramowania urządzeń na zewnętrznym programatorze urządzeń przed ich zamontowaniem na płytkach PCB. Wyeliminowanie tego etapu zmniejsza możliwość uszkodzenia delikatnych wyprowadzeń urządzeń do montażu powierzchniowego o dużej liczbie pinów lub uszkodzenia urządzenia przez wyładowania elektrostatyczne (ESD) podczas przepływu programowania. ISP umożliwia również użytkownikom wprowadzanie zmian konstrukcyjnych i ulepszeń w terenie bez konieczności wyjmowania urządzeń ISP z płytek PCB. Ponadto umożliwia również użycie wbudowanego mikrokontrolera lub testera w układzie do wykonywania operacji programowania w systemie na urządzeniach ISP i integrowania tych operacji programowania z przepływem produkcji płytek drukowanych.

Systemy programowania w systemie

Trzy podstawowe komponenty systemu ISP dla układów CPLD ATF15xx to:

Oprogramowanie

Implementacja algorytmu programowania oraz generowanie JTAG instrukcje i dane dla urządzeń docelowych ISP. Może to być program komputerowy działający na komputerze, wbudowany mikrokontroler lub sprzęt do testowania w obwodzie.

Sprzęt interfejsu

Kanał komunikacyjny między oprogramowaniem ISP a urządzeniami ISP na płycie docelowej. Może to być kabel do pobierania ISP lub programator firmy Atmel lub zewnętrznego dostawcy, sprzęt do testowania w obwodzie lub połączenia między wbudowanym mikrokontrolerem a urządzeniami ISP na płytce PCB

Tablica docelowa

Płytka drukowana zawierająca urządzenia ISP w JTAG łańcuch. Może to być płytka rozwojowa/programująca ATF15xx CPLD firmy Atmel lub specjalnie zaprojektowana płytka drukowana z odpowiednim JTAG połączenia ze sprzętem interfejsu.

Oprócz tych trzech komponentów, JEDEC file jest konieczne do zaprogramowania ATF15xx CPLD. Ten JEDEC file można utworzyć poprzez skompilowanie projektu file korzystając z oprogramowania deweloperskiego obsługującego układy CPLD ATF15xx, takiego jak Atmel WinCUPL i Atmel ProChip Designer. Atmel dostarcza również narzędzie do tłumaczenia, POF2JED.exe, które konwertuje dane wyjściowe file z formatu programowania konkurencji do JEDEC file kompatybilny z ATF15xx CPLD. Aby uzyskać więcej informacji na temat tego narzędzia, zapoznaj się z notatką aplikacyjną Atmel, „ATF15xx Product Family Conversion”, dostępną na stronie Atmel webstrona. Po JEDEC files są tworzone dla wszystkich CPLD ATF15xx, mogą być programowane na płycie docelowej. CPLD ATF15xx mogą być programowane przez następujące systemy programowania wewnątrz systemu:

- System programowania w systemie ATF15xx

- Wbudowane mikrokontrolery

- Testery obwodowe

Atmel ATF15xx System programowania w systemie

Do programowania w systemie układów CPLD ATF15xx firma Atmel oferuje oprogramowanie ISP, kabel do pobrania oraz zestaw programistyczny/rozwojowy, które opisano w poniższych sekcjach.

Oprogramowanie ISP

Oprogramowanie Atmel ATF15xx ISP, ATMISP, jest podstawowym sposobem implementacji JTAG programowanie w systemie na układach CPLD ATF15xx. ATMISP działa na komputerze hosta z systemem Windows i implementuje programowanie w systemie układów CPLD ATF15xx na docelowym sprzęcie ISP lub generuje plik Serial Vector Format (.SVF) file do wykorzystania przez Automatic Testing Equipment (ATE) do programowania układów CPLD ATF15xx w systemie docelowym. ATMISP najpierw uzyskuje od użytkowników wszystkie niezbędne informacje o JTAG łańcuch urządzeń w systemie docelowym. Następnie wykonuje odpowiedni JTAG Instrukcje ISP na JTAG łańcuch urządzeń w systemie docelowym zgodnie z JTAG informacje o łańcuchu urządzeń określone przez użytkowników poprzez port USB lub LPT komputera. Więcej informacji o oprogramowaniu Atmel ATMISP można znaleźć na stronie www.atmel.com/tools/ATMISP.aspx.

Kabel do pobrania dostawcy usług internetowych

Kabel do pobierania danych ISP Atmel ATF15xx oparty na USB, ATDH1150USB, łączy się z jednym ze standardowych portów USB komputera hosta, a z drugim ze złącza J.TAG nagłówek płytki docelowej po drugiej stronie. Przenosi JTAG instrukcje i dane generowane przez ATMISP działające na komputerze hosta do urządzeń ISP na płycie docelowej. Więcej informacji o kablu ATDH1150USB można znaleźć na stronie www.atmel.com/tools/ATDH1150USB.aspx.

Rozwój/Programista

Zestaw Atmel ATF15xx Development/Programmer Kit, ATF15xx-DK3-U, to kompletny system rozwojowy i programator ISP dla układów CPLD ATF15xx. Zestaw ten zapewnia projektantom bardzo szybki i łatwy sposób na opracowywanie prototypów i ocenę nowych projektów z układem CPLD ATF15xx ISP. Dzięki dostępności różnych płyt adapterów gniazd obsługujących większość typów obudów oferowanych w układach CPLD ATF15xx, zestaw ten można wykorzystać jako programator ISP do programowania układów CPLD ATF15xx ISP w większości dostępnych typów obudów za pośrednictwem JTAG interfejs. Więcej informacji o zestawie Atmel ATF15xx-DK3-U można znaleźć na stronie www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Wbudowany system mikrokontrolera

Algorytm programowania i JTAG instrukcje dla układów CPLD ATF15xx mogą być implementowane w mikrokontrolerze lub mikroprocesorze, który następnie może być użyty do zaprogramowania układów CPLD ATF15xx na płycie docelowej. Jedną z możliwych metod jest wyodrębnienie wszystkich stosownych JTAG informacje o protokole (tj. JTAG instrukcje i dane) z SVF file wygenerowane przez oprogramowanie ATMISP, a następnie wykorzystać te informacje do zaimplementowania kodu dla mikrokontrolera lub mikroprocesora, który wygeneruje JTAG sygnały dla urządzeń ISP w JTAG łańcuch. To podejście jest najbardziej odpowiednie dla systemów, które mają już wbudowany mikrokontroler lub mikroprocesor, i eliminuje użycie zewnętrznego oprogramowania do programowania w systemie i narzędzi sprzętowych.

System testowania w obwodzie

Układy CPLD ATF15xx można programować na płytce docelowej za pomocą JTAG interfejs podczas testowania płytki drukowanej za pomocą testera w obwodzie. Generalnie SVF file wygenerowane przez ATMISP powinny zawierać wszystkie istotne elementy JTAG informacje o programowaniu w systemie, których testerzy w obwodzie potrzebują do zaprogramowania układów CPLD ATF15xx na docelowej płytce drukowanej. Takie podejście umożliwia integrację kroku programowania z testowaniemtage przepływu produkcji.

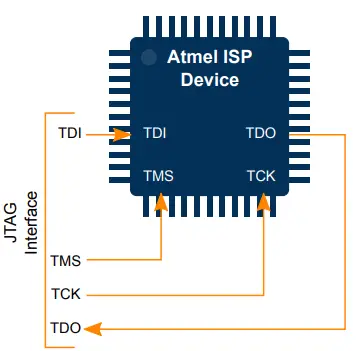

JTAG Interfejs dostawcy usług internetowych

ISP dla układów CPLD ATF15xx jest implementowany przy użyciu standardu IEEE 1149.1 Std. JTAG interfejs. Interfejs ten może być używany do kasowania, programowania i weryfikacji układów CPLD ATF15xx. JTAG Interfejs jest interfejsem szeregowym składającym się z sygnałów TCK, TMS, TDI i TDO oraz JTAG Kontroler portu dostępu testowego (TAP). Pin TCK jest wejściem zegara dla JTAG Kontroler TAP i zmiana kierunku JTAG instrukcje i dane. Pin TDI to szeregowe wejście danych. Służy do przesuwania instrukcji programowania i danych do urządzeń ISP. Pin TDO to szeregowe wyjście danych. Służy do przesuwania danych z urządzeń ISP. Pin TMS to pin wyboru trybu. Steruje stanem JTAG Kontroler TAP. JTAG piny interfejsu ATF15xx CPLD na płycie docelowej ISP muszą być podłączone do sprzętu interfejsu ISP (tj. kabla do pobierania ISP), zazwyczaj za pomocą 10-pinowej nagłówki. Sprzęt interfejsu ISP musi być również podłączony do komputera hosta, na którym działa oprogramowanie ISP. Sprzęt interfejsu ISP nawiązuje komunikację między oprogramowaniem ISP a urządzeniami ISP i umożliwia oprogramowaniu ISP przesyłanie instrukcji programowania i danych z komputera hosta do układów CPLD ATF15xx. Układy CPLD ATF15xx z JTAG funkcja włączona jest w pełni JTAG zgodne i obsługujące wymagane operacje testu Boundary Scan Test (BST) określone w JTAG standard. CPLD ATF15xx można skonfigurować tak, aby były częścią JTAG Łańcuch BST z innymi JTAG urządzenia do testowania w obwodzie płyty systemowej. Dzięki tej funkcji układy CPLD ATF15xx można testować na płycie systemowej wraz z innymi urządzeniami JTAG- obsługiwane urządzenia bez uciekania się do testowania metodą „łóżka gwoździ”.

Programowanie pojedynczego urządzenia

JTAG Interfejs ISP można skonfigurować tak, aby programował pojedynczy układ CPLD ATF15xx.TAG konfiguracja pojedynczego urządzenia jest pokazana na poniższym rysunku. Gdy układ CPLD ATF15xx jest skonfigurowany w ten sposób, rejestr pojawia się między pinami TDI i TDO urządzenia. Rozmiar rejestru zależy od JTAG szerokość instrukcji i dane przesuwane dla tej instrukcji. Rysunek 2-1 JTAG Urządzenie

Programowanie wielu urządzeń

Urządzenia CPLD ATF15xx można skonfigurować jako część łańcucha składającego się z wielu urządzeń JTAG- obsługiwane urządzenia, jak opisano poniżej i pokazano na poniższym rysunku.

- Podłącz pin TMS i TCK dla każdego urządzenia w JTAG łańcuch do pinów TMS i TCK JTAG Nagłówek interfejsu na płytce drukowanej.

- Podłącz pin TDI pierwszego urządzenia do pinu TDI urządzenia JTAG Nagłówek interfejsu.

- Podłącz pin TDO pierwszego urządzenia do pinu TDI następnego urządzenia. Kontynuuj ten proces, aż wszystkie oprócz ostatniego zostaną podłączone.

- Podłącz pin TDO ostatniego urządzenia do pinu TDO urządzenia JTAG Nagłówek interfejsu.

Rysunek 2-2 Wiele urządzeń JTAG Konfiguracja

Aby zaprogramować wiele urządzeń w JTAG chain, użytkownicy muszą używać narzędzi oprogramowania ISP, które obsługują takie funkcje. W oprogramowaniu ISP użytkownicy muszą określić:

- Liczba urządzeń w JTAG łańcuch.

- Numery części urządzeń i ich pozycje w JTAG łańcuch.

- JTAG operacji dla każdego z urządzeń.

- Inne JTAG-powiązane informacje, takie jak JTAG szerokość instrukcji dla każdego z urządzeń.

Kiedyś JTAG łańcuch jest prawidłowo skonfigurowany na płycie docelowej ISP i w oprogramowaniu ISP, urządzenia w JTAG łańcuch można zaprogramować w tym samym czasie.

Rozważania projektowe

Aby wykonać ISP na CPLD ATF15xx, zasoby dla JTAG interfejs w ATF15xx musi być zarezerwowany. Dlatego cztery piny I/O dla pinów TMS, TDI, TDO i TCK muszą być zarezerwowane dla JTAG i nie mogą być używane jako wejścia/wyjścia użytkownika. Numery pinów dla tych pinów zależą od tego, który układ CPLD ATF15xx jest używany i jaki jest jego typ obudowy. Informacje na temat pinów znajdują się w poniższej tabeli. JTAG norma zaleca podciągnięcie pinów TMS i TDI dla każdego urządzenia w JTAG łańcuch. CPLD ATF15xx mają wewnętrzną funkcję podciągania dla tych pinów, która po włączeniu oszczędza potrzebę stosowania zewnętrznych rezystorów podciągających. Ponadto JTAG funkcja interfejsu musi być włączona, aby wykonać ISP na CPLD ATF15xx. Włączanie JTAG interfejs wymaga wybrania konkretnych typów urządzeń Atmel lub ustawień opcji przed skompilowaniem projektu ATF15xx. Procedury te są opisane dla WinCUPL, ProChip Designer i POF2JED w tym przewodniku. Domyślnie wszystkie nowe układy CPLD ATF15xx są dostarczane z JTAG interfejs włączony. Po udostępnieniu zasobów logicznych dla JTAG interfejs jest zarezerwowany, użytkownicy mogą programować, weryfikować i kasować dowolny układ CPLD ATF15xx na płycie docelowej przy użyciu oprogramowania ATMISP.

Wskazówka:Chociaż cztery JTAG piny są zarezerwowane dla JTAG interfejs, użytkownicy mogą implementować ukryte funkcje logiczne w makrokomórkach powiązanych z tymi pinami.

Tabela 3-1 ATF15xx CPLD JTAG Numery PIN

| JTAG Szpilka | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Włącz JTAG Interfejs z WinCUPL

Aby włączyć JTAG interfejs z WinCUPL, odpowiedni typ urządzenia ATF15xx ISP musi zostać określony przed skompilowaniem projektu. Po pomyślnym skompilowaniu projektu, JEDEC file z JTAG funkcja interfejsu włączona jest generowana. Kiedy ten JEDEC file jest zaprogramowany w ATF15xxCPLD, jego JTAG interfejs jest włączony. Użytkownicy mogą również włączyć wewnętrzne rezystory podciągające TDI i TMS, włączając następujące oświadczenia właściwości do projektu CUPL file.

- WŁAŚCIWOŚĆ ATMEL {TDI_PULLUP = ON};

- WŁAŚCIWOŚĆ ATMEL {TMS_PULLUP = ON};

Ogłoszenie:Jeśli do projektu wykorzystującego J używany jest typ urządzenia ATF15xx ISPTAG piny interfejsu jako piny logicznego wejścia/wyjścia, WinCUPL generuje błąd.

Poniższe kroki opisują, jak otworzyć istniejący projekt w WinCUPL, określić typ urządzenia i skompilować projekt.

- W menu głównym WinCUPL wybierz File > Otwórz. Wybierz źródło CUPL (.pld) file z odpowiedniego katalogu roboczego.

- Wybierz OK, aby otworzyć źródło PLD file.

- W menu głównym WinCUPL wybierz File > Zapisz. To zapisuje zmiany wprowadzone do źródła file.

- W menu głównym wybierz Opcje > Urządzenia. Spowoduje to otwarcie okna dialogowego Wybór urządzenia.

- Wybierz odpowiednie urządzenie ATF15xx ISP. Zobacz poniższą tabelę, aby uzyskać listę wszystkich typów urządzeń ATF15xx obsługiwanych przez WinCUPL.

- Wybierz OK, aby zamknąć menu wyboru urządzenia.

- Uwaga: Inną metodą jest wybranie odpowiedniego typu urządzenia ATF15xx z poniższej tabeli i uwzględnienie go w sekcji nagłówka źródła CUPL file.

- W menu głównym WinCUPL wybierz Uruchom > Kompilacja zależna od urządzenia.

- WinCUPL kompiluje projekt i tworzy narzędzie dopasowujące urządzenia Atmel. Jeśli projekt pasuje, JEDEC file jest tworzony automatycznie.

- Kiedy JEDEC file jest zaprogramowany w urządzeniu, JTAG interfejs, opcjonalne wewnętrzne układy podciągające TMS i TDI oraz opcjonalne obwody utrzymujące piny są włączone.

Notatka:Wybranie typu urządzenia Atmel ISP automatycznie włącza JTAG interfejs domyślnie, gdy Atmel WinCUPL uruchamia program dopasowujący urządzenia Atmel.

Jeżeli projekty uniemożliwiają rezerwację zasobów dla JTAG interfejs lub ISP nie jest opcjonalnie używany, należy wybrać typ urządzenia Atmel non-ISP. Zobacz poniższą tabelę, aby zapoznać się z listą urządzeń. Urządzenie można następnie przeprogramować za pomocą zewnętrznego programatora urządzeń. Poniższa tabela zawiera listę typów urządzeń Atmel ISP i Atmel non-ISP dla WinCUPL.

Tabela 3-2 Typ urządzenia WinCUPL ATF15xx

| Nazwa urządzenia | Typ pakietu | Typ urządzenia WinCUPL | |

| JTAG Włączony | JTAG Wyłączony | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Włącz JTAG Interfejs z Atmel ProChip Designer

Aby włączyć JTAG interfejs z ProChip Designer:

- Otwórz odpowiedni projekt ProChip Designer.

- Otwórz okno Opcje Fittera, klikając przycisk Atmel Fitter w obszarze Device Fitter.

- Wybierz kartę Urządzenie globalne, a następnie zaznacz pole wyboru JTAG Port box. Wewnętrzne rezystory podciągające TMS i TDI można również włączyć, zaznaczając pola wyboru TDI Pullup i TMS Pullup. Te pola wyboru są pokazane na poniższym rysunku.

Rysunek 3-1 Interfejs użytkownika opcji dopasowania ProChip Designer

Włącz JTAG Interfejs z POF2JED

W POF2JED JTAG Opcję trybu można ustawić na Auto, aby umożliwić programowi POF2JED określenie, czy JTAG funkcja w ATF15xx powinna być włączona czy nie, i zależy to od tego, czy JTAG jest obsługiwany w CPLD konkurenta. Aby włączyć JTAG w ATF15xx CPLD niezależnie od tego, czy JTAG jest obsługiwany w CPLD konkurencji czy nie, JTAG Opcja Tryb powinna być ustawiona na Wł. Gdy JTAG jest włączony w ATF15xx, wewnętrzne rezystory podciągające TDI i TMS można włączyć, zaznaczając opcję Włącz

Pola TDI_PULLUP i Enable TMS_PULLUP w POF2JED. Zobacz poniższy rysunek.

Rysunek 3-2 Interfejs użytkownika POF2JED

Wytyczne i zalecenia

Uwaga: Należy zwrócić szczególną uwagę na tę sekcję podczas wykonywania operacji ISP na układach CPLD ATF15xx. W tej sekcji omówiono niektóre z JTAG Należy zwrócić szczególną uwagę na wytyczne, informacje i zalecenia dostawców usług internetowych.

- Upewnij się, że JTAG port dla wszystkich urządzeń w JTAG łańcuchy są włączone.

- W przypadku układów CPLD ATF15xx JTAG port jest włączony, jeśli urządzenia są puste/skasowane lub zaprogramowane za pomocą JTAG włączony.

- Wszystkie urządzenia Atmel ATF15xx są wysyłane w stanie pustym/wymazanym, dlatego JTAG port jest włączony dla wszystkich nowych urządzeń i gotowy na współpracę z dostawcą usług internetowych.

- Urządzenia ATF15xx z JTAG wyłączone muszą zostać usunięte przy użyciu programatora urządzeń innego niż ISP, aby ponownie włączyć JTAG port.

- Upewnij się, że wybrano właściwy wolumen VCCtage jest stosowane do każdego z urządzeń w JTAG łańcuch.

- Układy CPLD ATF15xxAS/ASL w obudowach typu 84-PLCC, 100-TQFP i 100-PQFP: napięcie VCCINT musi wynosić od 4.5 V do 5.5 V, natomiast napięcie VCCIO może wynosić od 3.0 V do 3.6 V lub od 4.5 V do 5.5 V.

- Układy CPLD ATF15xxAS/ASL w obudowach 44-PLCC i 44-TQFP: napięcie VCC musi wynosić od 4.5 V do 5.5 V.

- Układy CPLD ATF15xxASV/ASVL: napięcie VCC (VCCIO i VCCINT) musi wynosić od 3.0 V do 3.6 V.

- VCC dla urządzeń w JTAG łańcuch musi być odpowiednio regulowany i filtrowany.

- W przypadku układów CPLD ATF15xx stosowanych w większości zastosowań zaleca się stosowanie jednego kondensatora odsprzęgającego 0.22 µF na każdą parę VCC/GND.

- Zaleca się stosowanie wspólnego uziemienia dla wszystkich urządzeń w JTAG łańcuch i JTAG sprzęt interfejsu (np. kabel do pobierania ISP ATDH1150USB).

- Zaleca się unikanie długiego (nie więcej niż pięciu urządzeń) JTAG więzy.

- Jeśli długi JTAG łańcuch jest konieczny, buforuj sygnały TMS i TCK po każdym piątym urządzeniu. Preferowane jest użycie bufora wyzwalacza Schmitta.

- Bufory zmieniają czasy narastania i opadania sygnałów TMS i TCK.

- Należy wziąć pod uwagę dodatkowe opóźnienie spowodowane buforami.

- Zaleca się stosowanie rezystorów podciągających (4.7KΩ do 10KΩ) dla sygnałów TMS i TDI oraz rezystora podciągającego dla sygnału TCK w punkcie J.TAG nagłówek, aby zapobiec przemieszczaniu się tych sygnałów, gdy nie są one sterowane przez sprzęt interfejsu.

- Opcjonalne wewnętrzne układy podciągające w TMS i TDI są dostępne dla układów CPLD ATF15xx.

- Zaleca się zakończenie JTAG sygnały w JTAG chodnikowiec.

- Dopuszczalne są zarówno zakończenia aktywne, jak i pasywne, jednak preferowane jest zakończenie pasywne.

- Redukuje dzwonienie spowodowane długimi ścieżkami kabla/PCB.

- Zakończenie jest najważniejsze w przypadku TMS i TCK.

- Zaleca się, aby wszystkie wejścia i wejścia/wyjścia urządzeń w JTAG łańcuch, z wyjątkiem JTAG piny powinny być w stanie statycznym podczas programowania układów CPLD ATF15xx w celu zminimalizowania szumów.

- W przypadku korzystania z jednej z płytek programujących/rozwojowych Atmel ATF15xx, zasilanie płytki musi być wyłączone podczas zmiany położenia zworek wyboru VCC.

- W przypadku układów CPLD ATF15xx JTAG ISP jest dostępny, gdy część znajduje się w trybie wyłączania zasilania sterowanym pinami lub gdy urządzenie „o niskim poborze mocy” jest uśpione.

- Stan urządzenia po przerwaniu połączenia ISP:

- Jeżeli ISP zostanie przerwane, wszystkie piny I/O zostaną potrójnie zwarte, niezależnie od stanu obwodów Pin-keeper.

- Zapobiega konfliktom na magistrali między częściowo zaprogramowanymi urządzeniami a innymi urządzeniami na płytce drukowanej.

- Podczas programowania ISP wszystkie piny I/O znajdują się w jednym z następujących stanów:

- Stan wysokiej impedancji:

- Gdy zaprogramowane jest puste/wymazane urządzenie.

- Gdy urządzenie zostanie przeprogramowane z wyłączonymi obwodami Pin-keeper.

- Zapobiega konfliktom na magistrali z urządzeniami zewnętrznymi komunikującymi się z układami CPLD ATF15xx na płytce drukowanej.

- Słabo przywiązany do poprzedniego stanu:

- Gdy zaprogramowane urządzenie zostanie przeprogramowane z włączonymi obwodami Pin-keeper.

- Piny I/O zachowują poprzednie poziomy logiczne przed ISP.

- Zapobiega wpływowi dostawcy usług internetowych na pracę innych urządzeń na płycie głównej.

- Zastosowanie wielu JTAG Nie zaleca się stosowania łańcuchów na jednej desce.

- Urządzenia mogą oddziaływać na siebie pomiędzy różnymi JTAG więzy.

- Płyta jest funkcjonalna tylko wtedy, gdy wszystkie urządzenia we wszystkich JTAG łańcuchy są programowane pomyślnie.

- Jeżeli programowanie nie powiedzie się dla co najmniej jednego urządzenia w łańcuchu, podczas gdy inne urządzenia JTAG łańcuchy zostały pomyślnie zaprogramowane:

- Urządzenia Atmel lub inne urządzenia na pokładzie mogą ulec uszkodzeniu z powodu możliwego problemu z konfliktem sygnałów na magistrali dla wyjść trójstanowych.

- Stan operacyjny płyty systemowej jest nieokreślony, w związku z czym może wystąpić nieprawidłowe działanie funkcjonalne.

- Wstawianie obwodów aktywnych pomiędzy JTAG nagłówek i JTAG urządzenia w łańcuchu nie są zalecane. Jeśli obwód aktywny ulegnie awarii, może to spowodować problemy z programowaniem/weryfikacją.

- Zastosowanie mieszanej objętościtagurządzenie JTAG Nie zaleca się stosowania łańcuchów.

- To są JTAG łańcuchy z urządzeniami, które wykorzystują różne objętości VCCtages i/lub interfejs voltagt.j.

- Interfejs objtagPoziomy e (VIL, VIH, VOL, VOH) dla urządzeń 5.0 V mogą nie być zgodne z poziomem głośności interfejsutagPoziomy e dla urządzeń 3.0 V.

- Jeżeli ATMISP ma problem z komunikacją z JTAG w przypadku łańcucha sprzętowego urządzenia spróbuj uruchomić funkcję Self Calibrate lub Manually Calibrate, aby obniżyć częstotliwości JTAG sygnały.

- Przed rozpoczęciem programowania upewnij się, że dioda LED na kablu ATDH1150USB jest włączona i świeci na zielono. Upewnij się, że kabel do pobierania ISP może prawidłowo komunikować się z oprogramowaniem ATMISP.

- Upewnij się, że wybrano właściwy wolumen VCCtage jest stosowany do kabla ATDH1150USB.

- VCC używany przez pierwsze urządzenie w JTAG łańcuch musi być dostarczany do kabla ATDH1150USB poprzez pin 4 10-stykowego złącza JTAG chodnikowiec.

- W przypadku układów CPLD ATF15xx z oddzielnymi zaciskami VCCINT i VCCIO, w kablu ATDH1150USB należy użyć zacisku VCCIO.

Informacje o zamówieniu

| Kod zamówienia | Opis |

| ATF15xx-DK3-U | Zestaw programisty/programisty CPLD (zawiera ATF15xxDK3-SAA44 i ATDH1150USB lub ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | 100-pinowa płytka adaptera gniazda TQFP do płytki DK3 |

| ATF15xxDK3-SAJ44 | 44-pinowa płytka adaptera gniazda PLCC do płytki DK3 |

| ATF15xxDK3-SAJ84 | 84-pinowa płytka adaptera gniazda PLCC do płytki DK3 |

| ATF15xxDK3-SAA44 | 44-pinowa płytka adaptera gniazda TQFP do płytki DK3 |

| ATDH1150USB | Atmel ATF15xx CPLD oparty na USB JTAG Kabel do pobrania dostawcy usług internetowych |

Historia rewizji

| Doc. Obrót silnika. | Data | Uwagi |

| A | 12/2015 | Wstępne wydanie dokumentu. |

INFORMACJE KONTAKTOWE

Korporacja Atmel

- 1600 Technology Drive, San Jose, Kalifornia 95110 USA

- T: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_Podręcznik użytkownika-12/2015

Atmel®, logo Atmel i ich kombinacje, Enabling Unlimited Possibilities® i inne są zarejestrowanymi znakami towarowymi lub znakami towarowymi Atmel Corporation w Stanach Zjednoczonych i innych krajach. Inne terminy i nazwy produktów mogą być znakami towarowymi innych osób.

ZASTRZEŻENIE: Informacje zawarte w tym dokumencie dotyczą produktów firmy Atmel. W niniejszym dokumencie lub w związku ze sprzedażą produktów firmy Atmel nie jest udzielana żadna licencja, wyraźna lub dorozumiana, w drodze estoppelu lub w inny sposób, do jakichkolwiek praw własności intelektualnej. Z WYJĄTKIEM OKREŚLONYCH W WARUNKACH SPRZEDAŻY ATMEL ZNAJDUJĄCYCH SIĘ NA ATMEL WEBWITRYNA, ATMEL NIE PONOSI ŻADNEJ ODPOWIEDZIALNOŚCI I ZRZEKA SIĘ WSZELKIEJ WYRAŹNEJ, DOROZUMIANEJ LUB USTAWOWEJ GWARANCJI DOTYCZĄCEJ SWOICH PRODUKTÓW, W TYM MIĘDZY INNYMI DOROZUMIANEJ GWARANCJI PRZYDATNOŚCI HANDLOWEJ, PRZYDATNOŚCI DO OKREŚLONEGO CELU LUB NIENARUSZALNOŚCI. W ŻADNYM WYPADKU ATMEL NIE PONOSI ODPOWIEDZIALNOŚCI ZA JAKIEKOLWIEK BEZPOŚREDNIE, POŚREDNIE, WTÓRNE, KARNE, SPECJALNE LUB PRZYPADKOWE SZKODY (W TYM, BEZ OGRANICZEŃ, SZKODY ZA STRATY I ZYSKI, PRZERWY W DZIAŁALNOŚCI LUB UTRATĘ INFORMACJI) WYNIKAJĄCE Z UŻYTKOWANIA LUB NIEMOŻNOŚCI UŻYTKOWANIA TEGO DOKUMENTU, NAWET JEŚLI ATMEL ZOSTAŁ POINFORMOWANY O MOŻLIWOŚCI WYSTĄPIENIA TAKICH SZKÓD. Atmel nie składa żadnych oświadczeń ani gwarancji co do dokładności lub kompletności treści niniejszego dokumentu i zastrzega sobie prawo do wprowadzania zmian w specyfikacjach i opisach produktów w dowolnym momencie bez powiadomienia. Atmel nie zobowiązuje się do aktualizacji informacji zawartych w niniejszym dokumencie. O ile nie zaznaczono inaczej, produkty Atmel nie nadają się do zastosowań motoryzacyjnych i nie powinny być w nich stosowane. Produkty firmy Atmel nie są przeznaczone, autoryzowane ani objęte gwarancją do użytku jako komponenty w zastosowaniach mających na celu podtrzymywanie życia. ZASTOSOWANIA KRYTYCZNE DLA BEZPIECZEŃSTWA, WOJSKOWE I MOTORYZACYJNE ZASTRZEŻENIE: Produkty firmy Atmel nie są przeznaczone i nie będą używane w związku z żadnymi zastosowaniami, w których awaria takich produktów mogłaby w uzasadniony sposób spowodować poważne obrażenia ciała lub śmierć („Zastosowania krytyczne dla bezpieczeństwa”) bez wyraźnej pisemnej zgody urzędnika firmy Atmel. Zastosowania krytyczne dla bezpieczeństwa obejmują, bez ograniczeń, urządzenia i systemy podtrzymywania życia, sprzęt lub systemy do obsługi obiektów jądrowych i systemów uzbrojenia. Produkty firmy Atmel nie są zaprojektowane ani przeznaczone do użytku w zastosowaniach wojskowych lub lotniczych lub środowiskach, chyba że zostały wyraźnie oznaczone przez firmę Atmel jako klasy wojskowej. Produkty firmy Atmel nie są zaprojektowane ani przeznaczone do użytku w zastosowaniach motoryzacyjnych, chyba że zostały wyraźnie oznaczone przez firmę Atmel jako klasy motoryzacyjnej.

Dokumenty / Zasoby

|

Atmel ATF15xx Kompleksowe programowalne urządzenie logiczne [plik PDF] Instrukcja użytkownika ATF15xx, ATF15xx Kompleksowe Programowalne Urządzenie Logiczne, Kompleksowe Programowalne Urządzenie Logiczne, Programowalne Urządzenie Logiczne, Urządzenie Logiczne, Urządzenie |