Atmel ATF15xx Complex Programmable Logic Device

Mga pagtutukoy

- Pangalan ng Produkto: Atmel ATF15xx In-System Programming

- Modelo: ATF15xx

- Uri: Complex Programmable Logic Device (CPLD)

- Paraan ng Programming: In-System Programming (ISP)

- Interface: JTAG Interface ng ISP

- Tagagawa: Atmel

Mga FAQ

Q: Maaari ba akong gumamit ng third-party programming software sa mga ATF15xx CPLD?

A: Oo, hangga't sinusuportahan ng software ang programming algorithm at JTAG kinakailangan ang mga tagubilin para sa mga ATF15xx CPLD.

T: Posible bang magprogram ng maraming ATF15xx CPLD nang sabay-sabay?

A: Oo, ang JTAG Sinusuportahan ng interface ng ISP ang maramihang device programming para sa mahusay na programming ng maramihang CPLD nang sabay-sabay.

Panimula

- Ang Atmel® ATF15xx Complex Programmable Logic Devices (CPLDs) na may Logic Doubling® architecture ay sumusuporta sa In-System Programming (ISP) sa pamamagitan ng IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface. Pinahuhusay ng tampok na ito ang flexibility ng programming at nagbibigay ng mga benepisyo sa iba't ibang yugto; pagbuo ng produkto, produksyon, at paggamit sa larangan. Ang gabay sa gumagamit na ito ay naglalarawan ng mga pamamaraan ng disenyo at mga kinakailangan para sa pagpapatupad ng ISP sa mga ATF15xx CPLD na may suporta sa ISP tulad ng nakalista sa ibaba:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Mga Tampok at Benepisyo

Ang in-system programming ay nagbibigay-daan sa programming at re-programming ng mga ISP device pagkatapos na mai-mount ang mga ito sa Printed Circuit Boards (PCBs). Tinatanggal nito ang karagdagang hakbang sa pangangasiwa na kinakailangan sa proseso ng pagmamanupaktura upang i-program ang mga device sa isang external device programmer bago sila i-mount sa mga PCB. Ang pag-aalis sa hakbang na ito ay binabawasan ang posibilidad na masira ang mga maselan na lead ng mga high pin count surface mount device o masira ang device sa pamamagitan ng electrostatic discharge (ESD) sa panahon ng daloy ng programming. Pinapayagan din ng ISP ang mga user na gumawa ng mga pagbabago sa disenyo at pag-upgrade sa field nang hindi kinakailangang alisin ang mga ISP device mula sa mga PCB. Higit pa rito, pinapayagan din nito ang paggamit ng isang naka-embed na microcontroller o in-circuit tester upang magsagawa ng mga in-system programming operations sa mga ISP device at isama ang mga programming operation na ito sa daloy ng produksyon ng mga circuit board.

In-System Programming Systems

Ang tatlong mahahalagang bahagi ng isang ISP system para sa mga ATF15xx CPLD ay:

Software

Pagpapatupad ng programming algorithm, pati na rin ang henerasyon ng JTAG mga tagubilin at data para sa mga target na ISP device. Ito ay maaaring isang software program na tumatakbo sa isang PC, isang naka-embed na microcontroller, o isang in-circuit testing equipment.

Hardware ng Interface

Isang channel ng komunikasyon sa pagitan ng ISP software at ISP device sa target board. Ito ay maaaring isang ISP download cable o programmer mula sa Atmel o isang third-party na vendor, in-circuit testing equipment, o ang mga koneksyon sa pagitan ng isang naka-embed na microcontroller at ISP device sa PCB

Target Board

Circuit board na naglalaman ng mga ISP device sa JTAG kadena. Ito ay maaaring ang ATF15xx CPLD Development/Programmer board mula sa Atmel o isang custom-designed circuit board na may naaangkop na JTAG mga koneksyon sa hardware ng interface.

Bilang karagdagan sa tatlong sangkap na ito, isang JEDEC file ay kinakailangan upang magprogram ng ATF15xx CPLD. Itong JEDEC file maaaring malikha sa pamamagitan ng pag-compile ng isang disenyo file gamit ang development software na sumusuporta sa mga ATF15xx CPLD gaya ng Atmel WinCUPL at Atmel ProChip Designer. Nagbibigay din ang Atmel ng translator software utility, POF2JED.exe, na nagko-convert ng output file mula sa format ng programming ng kakumpitensya hanggang sa isang JEDEC file tugma sa ATF15xx CPLD. Para sa karagdagang impormasyon sa utility na ito, mangyaring sumangguni sa Atmel application note, “ATF15xx Product Family Conversion”, na available sa Atmel website. Pagkatapos ng JEDEC files ay nilikha para sa lahat ng ATF15xx CPLD, maaari silang i-program sa target board. Ang mga ATF15xx CPLD ay maaaring i-program ng mga sumusunod na in-system programming system:

- ATF15xx In-System Programming system

- Mga naka-embed na microcontroller

- Mga in-circuit tester

Atmel ATF15xx In-System Programming System

Para sa in-system programming ng ATF15xx CPLDs, ISP software, download cable, at development/programmer kit ay available mula sa Atmel at inilalarawan ang mga ito sa mga seksyon sa ibaba.

ISP Software

Ang Atmel ATF15xx ISP software, ATMISP, ay ang pangunahing paraan para sa pagpapatupad ng JTAG in-system programming sa mga ATF15xx CPLD. Tumatakbo ang ATMISP sa isang Windows-based na host PC at nagpapatupad ng in-system programming ng mga ATF15xx CPLD sa target na ISP hardware system o bumubuo ng Serial Vector Format (.SVF) file na gagamitin ng Automatic Testing Equipment (ATE) para i-program ang mga ATF15xx CPLD sa target na sistema. Unang nakuha ng ATMISP ang lahat ng kinakailangang impormasyon mula sa mga gumagamit tungkol sa JTAG chain ng device sa target na sistema. Pagkatapos ay isinasagawa nito ang naaangkop na JTAG Mga tagubilin ng ISP sa JTAG chain ng device sa target na sistema ayon sa JTAG impormasyon ng chain ng device na tinukoy ng mga user sa pamamagitan ng USB o LPT port ng PC. Higit pang impormasyon tungkol sa Atmel ATMISP software ay makukuha sa www.atmel.com/tools/ATMISP.aspx.

ISP Download Cable

Ang Atmel ATF15xx USB-based ISP Download Cable, ATDH1150USB, ay kumokonekta sa isang karaniwang USB port ng isang host computer sa isang gilid at sa isang JTAG header ng target na circuit board sa kabilang panig. Inilipat nito ang JTAG mga tagubilin at data na nabuo ng ATMISP na tumatakbo sa host PC sa mga ISP device sa target na circuit board. Higit pang impormasyon tungkol sa ATDH1150USB cable ay makukuha sa www.atmel.com/tools/ATDH1150USB.aspx.

Pag-unlad/Programmer

Ang Atmel ATF15xx Development/Programmer Kit, ATF15xx-DK3-U, ay isang kumpletong development system at isang ISP programmer para sa ATF15xx CPLDs. Ang kit na ito ay nagbibigay sa mga designer ng napakabilis at madaling paraan upang bumuo ng mga prototype at suriin ang mga bagong disenyo gamit ang ATF15xx ISP CPLD. Sa pagkakaroon ng iba't ibang socket adapter boards upang suportahan ang karamihan sa mga uri ng package na inaalok sa ATF15xx CPLDs, ang kit na ito ay maaaring gamitin bilang isang ISP programmer upang i-program ang ATF15xx ISP CPLD sa karamihan ng mga available na uri ng package sa pamamagitan ng JTAG interface. Higit pang impormasyon tungkol sa Atmel ATF15xx-DK3-U kit ay makukuha sa www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Naka-embed na Microcontroller System

Ang programming algorithm at JTAG Ang mga tagubilin para sa mga ATF15xx CPLD ay maaaring ipatupad sa isang microcontroller o microprocessor, na pagkatapos ay magagamit upang i-program ang mga ATF15xx CPLD sa target na board. Ang isang posibleng paraan ay ang pagkuha ng lahat ng nauugnay na JTAG impormasyon ng protocol (ibig sabihin, JTAG mga tagubilin at data) mula sa SVF file nabuo ng ATMISP software, at pagkatapos ay gamitin ang impormasyong ito upang ipatupad ang code para sa microcontroller o microprocessor na bubuo ng JTAG signal para sa mga ISP device sa JTAG kadena. Ang diskarte na ito ay pinakaangkop para sa mga system na mayroon nang naka-embed na microcontroller o microprocessor, at inaalis nito ang paggamit ng panlabas na in-system programming software at mga tool sa hardware.

In-circuit Testing System

Ang mga ATF15xx CPLD ay maaaring i-program sa target na circuit board sa pamamagitan ng JTAG interface sa panahon ng pagsubok ng circuit board gamit ang isang in-circuit tester. Sa pangkalahatan, ang SVF file na nabuo ng ATMISP ay dapat maglaman ng lahat ng nauugnay na JTAG in-system programming information na kailangan ng mga in-circuit tester na i-program ang mga ATF15xx CPLD sa target na circuit board. Ang diskarte na ito ay nagbibigay-daan sa pagsasama ng hakbang sa programming sa mga pagsuboktage ng daloy ng produksyon.

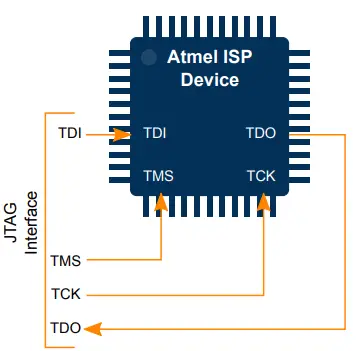

JTAG Interface ng ISP

Ang ISP para sa mga ATF15xx CPLD ay ipinatupad gamit ang IEEE 1149.1 Std. JTAG interface. Maaaring gamitin ang interface na ito upang burahin, iprograma, at i-verify ang mga ATF15xx CPLD. Ang JTAG Ang interface ay isang serial interface na binubuo ng mga signal ng TCK, TMS, TDI, at TDO at isang JTAG Test Access Port (TAP) controller. Ang TCK pin ay ang input ng orasan para sa JTAG TAP controller at para i-shift in/out ang JTAG mga tagubilin at datos. Ang TDI pin ay ang serial data input. Ito ay ginagamit upang ilipat ang mga tagubilin sa programming at data sa mga ISP device. Ang TDO pin ay ang serial data output. Ito ay ginagamit upang ilipat ang data mula sa mga ISP device. Ang TMS pin ay isang mode-select pin. Kinokontrol nito ang estado ng JTAG TAP controller. Ang JTAG interface pin ng ATF15xx CPLD sa ISP target board ay dapat na konektado sa ISP interface hardware (ibig sabihin, ISP download cable) karaniwang sa pamamagitan ng isang 10-pin header. Ang ISP interface hardware ay kailangan ding konektado sa host PC na nagpapatakbo ng ISP software. Ang ISP interface hardware ay nagtatatag ng komunikasyon sa pagitan ng ISP software at ISP device, at pinapayagan nito ang ISP software na ilipat ang mga tagubilin sa programming at data mula sa host PC patungo sa ATF15xx CPLDs. Mga ATF15xx CPLD kasama ang JTAG Ang tampok na pinagana ay ganap na JTAG katugma at sinusuportahan din ang kinakailangang mga operasyon ng Boundary Scan Test (BST) na tinukoy sa JTAG pamantayan. Ang mga ATF15xx CPLD ay maaaring i-configure upang maging bahagi ng isang JTAG BST chain kasama ang iba pang JTAG mga device para sa in-circuit testing ng system board. Sa tampok na ito, ang mga ATF15xx CPLD ay maaaring masuri sa circuit board kasama ng iba pang JTAG-mga sinusuportahang device nang hindi gumagamit ng bed-of-nails testing.

Single Device Programming

Ang JTAG Maaaring i-configure ang interface ng ISP para mag-program ng isang ATF15xx CPLD. Ang JTAG ang configuration para sa isang device ay ipinapakita sa figure sa ibaba. Kapag ang isang ATF15xx CPLD ay na-configure sa ganitong paraan, isang rehistro ang lalabas sa pagitan ng TDI at TDO pin ng device. Ang laki ng rehistro ay depende sa JTAG lapad ng pagtuturo at ang data na inililipat para sa pagtuturo na iyon. Larawan 2-1 JTAG Device

Programming ng Maramihang Device

Ang mga ATF15xx CPLD ay maaaring i-configure bilang bahagi ng daisy chain ng maramihang JTAG-mga sinusuportahang device tulad ng inilarawan sa ibaba at ipinapakita din sa sumusunod na figure.

- Ikonekta ang TMS at TCK pin para sa bawat device sa JTAG chain sa TMS at TCK pin ng JTAG interface header sa circuit board.

- Ikonekta ang TDI pin mula sa unang device sa TDI pin ng JTAG header ng interface.

- Ikonekta ang TDO pin mula sa unang device sa TDI pin ng susunod na device. Ipagpatuloy ang prosesong ito hanggang ang lahat maliban sa huli ay konektado.

- Ikonekta ang TDO pin mula sa huling device sa TDO pin ng JTAG header ng interface.

Figure 2-2 Maramihang Device JTAG Configuration

Upang mag-program ng maraming device sa isang JTAG chain, ang mga user ay dapat gumamit ng ISP software tools na sumusuporta sa mga naturang feature. Sa software ng ISP, kailangang tukuyin ng mga user ang:

- Bilang ng mga device sa JTAG kadena.

- Mga numero ng bahagi ng mga device at ang mga posisyon sa loob ng JTAG kadena.

- JTAG mga operasyon para sa bawat isa sa mga device.

- Iba pang JTAG-kaugnay na impormasyon tulad ng JTAG lapad ng pagtuturo para sa bawat isa sa mga device.

Sa sandaling ang JTAG Ang daisy chain ay maayos na naka-set up sa ISP target board at sa ISP software, ang mga device sa JTAG chain ay maaaring i-program sa parehong oras.

Mga Pagsasaalang-alang sa Disenyo

Upang magsagawa ng ISP sa isang ATF15xx CPLD, ang mga mapagkukunan para sa JTAG interface sa ATF15xx ay dapat na nakalaan. Samakatuwid, ang apat na I/O pin para sa TMS, TDI, TDO, at TCK pin ay dapat na nakalaan para sa JTAG at hindi maaaring gamitin bilang user I/Os. Ang mga numero ng pin para sa mga pin na ito ay nakadepende kung aling ATF15xx CPLD ang ginagamit at ang uri ng package nito. Sumangguni sa talahanayan sa ibaba para sa impormasyon ng pinout. Ang JTAG Inirerekomenda ng standard na ang mga TMS at TDI pin ay hilahin pataas para sa bawat device sa JTAG kadena. Ang mga ATF15xx CPLD ay may panloob na tampok na pull-up para sa mga pin na, kapag pinagana, nakakatipid ng pangangailangan para sa mga panlabas na pull-up resistors. Higit pa rito, ang JTAG ang tampok na interface ay dapat na pinagana upang maisagawa ang ISP sa mga ATF15xx CPLD. Paganahin ang JTAG interface ay nangangailangan ng pagpili ng mga partikular na uri ng device ng Atmel o mga setting ng opsyon bago i-compile ang disenyo ng ATF15xx. Ang mga pamamaraang ito ay nakabalangkas para sa WinCUPL, ProChip Designer, at POF2JED sa gabay na ito. Bilang default, lahat ng bagong ATF15xx CPLD ay ipinapadala kasama ng JTAG pinagana ang interface. Sa sandaling ang mga mapagkukunan ng lohika para sa JTAG Ang interface ay nakalaan, ang mga user ay maaaring mag-program, mag-verify, at magbura ng anumang ATF15xx CPLD sa target board gamit ang ATMISP software.

Tip: Bagaman ang apat na JTAG Ang mga pin ay nakalaan para sa isang JTAG interface, maaaring ipatupad ng mga user ang nakabaon na logic function sa mga macrocell na nauugnay sa mga pin na ito.

Talahanayan 3-1 ATF15xx CPLD JTAG Mga Numero ng Pin

| JTAG Pin | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Paganahin ang JTAG Interface sa WinCUPL

Upang paganahin ang JTAG interface sa WinCUPL, ang naaangkop na uri ng device na ATF15xx ISP ay kailangang tukuyin bago mag-compile ang isang disenyo. Pagkatapos ng isang disenyo ay matagumpay na naipon, isang JEDEC file kasama ang JTAG nabuo ang tampok na interface na pinagana. Kapag itong JEDEC file ay naka-program sa isang ATF15xxCPLD, ang JTAG pinagana ang interface. Maaari ding paganahin ng mga user ang TDI at TMS internal pull-up resistors sa pamamagitan ng pagsasama ng mga sumusunod na property statement sa CUPL design file.

- PROPERTY ATMEL {TDI_PULLUP = ON};

- PROPERTY ATMEL {TMS_PULLUP = ON};

Pansinin: Kung ang uri ng device na ATF15xx ISP ay ginagamit para sa isang disenyo na gumagamit ng JTAG interface pin bilang logic I/O pins, ang WinCUPL ay bumubuo ng error.

Tinatalakay ng mga sumusunod na hakbang kung paano buksan ang isang umiiral na disenyo sa WinCUPL, tukuyin ang uri ng device, at i-compile ang disenyo.

- Sa pangunahing menu ng WinCUPL, piliin File > Buksan. Piliin ang CUPL (.pld) source file mula sa naaangkop na direktoryo ng trabaho.

- Piliin ang OK para buksan ang PLD source file.

- Sa pangunahing menu ng WinCUPL, piliin File > I-save. Ito ay nagse-save ng mga pagbabagong ginawa sa pinagmulan file.

- Sa pangunahing menu, piliin ang Opsyon > Mga Device. Binubuksan nito ang dialog box ng Pagpili ng Device.

- Piliin ang naaangkop na ATF15xx ISP device. Tingnan ang sumusunod na talahanayan para sa isang listahan ng lahat ng mga uri ng device ng ATF15xx na sinusuportahan ng WinCUPL.

- Piliin ang OK upang isara ang menu ng pagpili ng device.

- Tandaan: Ang isang alternatibong paraan ay ang pumili ng naaangkop na uri ng device na ATF15xx mula sa sumusunod na talahanayan at isama ito sa seksyon ng header ng CUPL source file.

- Sa pangunahing menu ng WinCUPL, piliin ang Run> Device Dependent Compile.

- WinCUPL compiles ang disenyo at spawn ang Atmel device fitter. Kung magkasya ang disenyo, isang JEDEC file ay awtomatikong nalilikha.

- Kapag ang JEDEC file ay naka-program sa device, ang JTAG interface, ang opsyonal na panloob na TMS at TDI pull-up, at ang opsyonal na pin-keeper circuit ay pinagana.

Tandaan: Ang pagpili ng uri ng device ng Atmel ISP ay awtomatikong nagbibigay-daan sa JTAG interface bilang default kapag pinapatakbo ng Atmel WinCUPL ang Atmel device fitter.

Kung pinipigilan ng mga disenyo ang pagreserba ng mga mapagkukunan para sa JTAG interface o isang ISP ay opsyonal na hindi ginagamit, dapat pumili ng uri ng device na hindi ISP ng Atmel. Tingnan ang talahanayan sa ibaba para sa isang listahan ng mga device. Pagkatapos ay maaaring i-reprogram ang device gamit ang external device programmer. Inililista ng talahanayan sa ibaba ang mga uri ng device ng Atmel ISP at Atmel na hindi ISP para sa WinCUPL.

Talahanayan 3-2 WinCUPL ATF15xx Uri ng Device

| Pangalan ng Device | Uri ng Package | Uri ng Device ng WinCUPL | |

| JTAG Pinagana | JTAG Hindi pinagana | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Paganahin ang JTAG Interface sa Atmel ProChip Designer

Upang paganahin ang JTAG interface sa ProChip Designer:

- Buksan ang naaangkop na proyekto ng ProChip Designer.

- Buksan ang window ng Fitter Options sa pamamagitan ng pag-click sa Atmel Fitter button sa ilalim ng Device Fitter.

- Piliin ang tab na Global Device at pagkatapos ay suriin ang JTAG Port box. Ang TMS at TDI internal pull-up resistors ay maaari ding paganahin sa pamamagitan ng pagsuri sa TDI Pullup at TMS Pullup box. Ang mga check box na ito ay ipinapakita sa figure sa ibaba.

Figure 3-1 ProChip Designer Fitter Options User Interface

Paganahin ang JTAG Interface sa POF2JED

Sa POF2JED, ang JTAG Ang opsyon sa mode ay maaaring itakda sa Auto upang hayaan ang POF2JED na matukoy kung ang JTAG Ang tampok sa ATF15xx ay dapat na paganahin o hindi, at ito ay batay sa kung JTAG ay suportado sa CPLD ng kakumpitensya. Para i-on si JTAG sa ATF15xx CPLD hindi alintana kung si JTAG ay suportado sa CPLD ng kakumpitensya o hindi, ang JTAG Ang opsyon sa mode ay dapat itakda sa Naka-on. Nang si JTAG ay pinagana sa ATF15xx, ang TDI at TMS internal pull-up resistors ay maaaring paganahin sa pamamagitan ng pagsuri sa Enable

TDI_PULLUP at Paganahin ang TMS_PULLUP na mga kahon sa POF2JED. Tingnan ang figure sa ibaba.

Larawan 3-2 POF2JED User Interface

Mga Alituntunin at Rekomendasyon

Pansin: Ang karagdagang pansin sa seksyong ito ay dapat gawin kapag nagsasagawa ng mga pagpapatakbo ng ISP sa mga ATF15xx CPLD. Tinatalakay ng seksyong ito ang ilan sa JTAG Mga alituntunin, impormasyon at rekomendasyon ng ISP na dapat mapansing mabuti.

- Siguraduhin na ang JTAG port para sa lahat ng device sa JTAG naka-enable ang chain.

- Para sa mga ATF15xx CPLD, ang JTAG Ang port ay pinagana kung ang mga device ay blangko/binura o naka-program gamit ang JTAG pinagana.

- Ang lahat ng mga aparatong Atmel ATF15xx ay ipinadala sa blangko/binura na estado; samakatuwid, ang JTAG naka-enable ang port para sa lahat ng bagong device at handa na para sa ISP.

- ATF15xx device na may JTAG ang hindi pinagana ay kailangang burahin gamit ang isang non-ISP device programmer upang muling paganahin ang JTAG daungan.

- Siguraduhin na ang wastong VCC voltage ay inilalapat sa bawat isa sa mga device sa JTAG kadena.

- Mga ATF15xxAS/ASL CPLD sa 84-PLCC, 100-TQFP, at 100-PQFP na mga uri ng package: Ang VCCINT ay dapat nasa pagitan ng 4.5V at 5.5V habang ang VCCIO ay maaaring nasa pagitan ng 3.0V at 3.6V o 4.5V at 5.5V.

- Mga ATF15xxAS/ASL CPLD sa 44-PLCC at 44-TQFP na mga uri ng package: Ang VCC ay dapat nasa pagitan ng 4.5V hanggang 5.5V.

- Mga ATF15xxASV/ASVL CPLD: Ang VCC (VCCIO at VCCINT) ay dapat nasa pagitan ng 3.0V hanggang 3.6V.

- Ang VCC para sa mga device sa JTAG chain ay dapat na maayos na kinokontrol at na-filter.

- Para sa mga ATF15xx CPLD na ginagamit sa karamihan ng mga application, inirerekomendang gumamit ng isang 0.22µF decoupling capacitor para sa bawat isa sa mga pares ng VCC/GND.

- Inirerekomenda na gumamit ng isang karaniwang batayan para sa lahat ng mga aparato sa JTAG chain at ang JTAG interface hardware (ie ATDH1150USB ISP Download Cable).

- Inirerekomenda na iwasan ang mahaba (hindi hihigit sa limang device) JTAG mga tanikala.

- Kung ang isang mahabang JTAG chain ay kinakailangan, buffer ang TMS at TCK signal pagkatapos ng bawat ikalimang aparato. Mas gusto ang paggamit ng Schmitt trigger buffer.

- Binabago ng mga buffer ang mga oras ng pagtaas at pagbaba ng mga signal ng TMS at TCK.

- Kailangang isaalang-alang ang karagdagang pagkaantala na natamo ng mga buffer.

- Inirerekomenda na gumamit ng mga pull-up resistor (4.7KΩ hanggang 10KΩ) para sa TMS at TDI signal at pull-down resistor para sa TCK signal sa JTAG header upang pigilan ang mga signal na ito na lumutang kapag hindi ito hinihimok ng hardware ng interface.

- Available ang mga opsyonal na panloob na pull-up sa TMS at TDI para sa mga ATF15xx CPLD.

- Inirerekomenda na wakasan ang JTAG signal sa JTAG header.

- Parehong aktibo at passive na pagwawakas ay katanggap-tanggap; gayunpaman, mas gusto ang passive termination.

- Binabawasan nito ang pag-ring dahil sa mahabang haba ng bakas ng cable/PCB.

- Ang pagwawakas ay pinakamahalaga para sa TMS at TCK.

- Inirerekomenda na ang lahat ng mga input at I/Os ng mga device sa JTAG chain, maliban sa JTAG ang mga pin, ay dapat na nasa static na estado kapag ang mga ATF15xx CPLD ay na-program upang mabawasan ang ingay.

- Kapag gumagamit ng isa sa Atmel ATF15xx development/programmer boards, dapat na naka-OFF ang power to the board kapag binago ang mga posisyon ng VCC selection jumper.

- Para sa mga ATF15xx CPLD, JTAG Available ang ISP kapag ang bahagi ay nasa Pin-controlled Power-down mode o kapag ang "low-power" na device ay tulog.

- Status ng device pagkatapos maputol ang ISP:

- Kung maaantala ang ISP, lahat ng I/O pin ay tri-stateed anuman ang estado ng Pin-keeper circuits.

- Pinipigilan ang bahagyang naka-program na mga device na magdulot ng pagtatalo sa bus sa iba pang mga device sa circuit board.

- Sa panahon ng ISP programming, lahat ng I/O pin ay nasa isa sa mga sumusunod na kondisyon:

- High-impedance na estado:

- Kapag ang isang blangko/binura na aparato ay na-program.

- Kapag ang isang device ay muling na-program na ang Pin-keeper circuit ay hindi pinagana.

- Pinipigilan ang pagtatalo sa bus sa mga external na device na nakikipag-interface sa mga ATF15xx CPLD sa circuit board.

- Mahina na nakakabit sa nakaraang estado:

- Kapag ang isang naka-program na device ay muling na-program nang pinagana ang Pin-keeper circuits.

- Pinapanatili ng mga I/O pin ang mga nakaraang antas ng lohika bago ang ISP.

- Pinipigilan ang ISP na makaapekto sa pagpapatakbo ng iba pang mga device sa system board.

- Ang paggamit ng maramihang JTAG ang mga chain sa isang board ay hindi inirerekomenda.

- Maaaring makipag-ugnayan ang mga device sa pagitan ng iba't ibang JTAG mga tanikala.

- Ang board ay gumagana lamang kapag ang lahat ng mga aparato sa lahat ng JTAG matagumpay na na-program ang mga chain.

- Kung nabigo ang programming para sa hindi bababa sa isang device sa isang chain habang ang iba pang JTAG ang mga chain ay matagumpay na na-program:

- Maaaring masira ang alinman sa Atmel o iba pang mga device na nakasakay dahil sa posibleng problema sa pagtatalo sa bus para sa mga tri-stateable na output.

- Ang estado ng pagpapatakbo ng system board ay hindi natukoy; at samakatuwid, maaaring mangyari ang maling pagpapaandar.

- Ang pagpasok ng mga aktibong circuit sa pagitan ng JTAG header at ang JTAG hindi inirerekomenda ang mga device sa chain. Kung hindi gumagana ang aktibong circuit, maaari itong magdulot ng mga problema sa programming/verify.

- Ang paggamit ng mixed-voltage device JTAG ang mga kadena ay hindi inirerekomenda.

- Ito ay si JTAG chain na may mga device na gumagamit ng iba't ibang VCC voltages at/o interface voltages.

- Interface voltage level (VIL, VIH, VOL, VOH) para sa 5.0V device ay maaaring hindi tugma sa interface voltage level para sa 3.0V device.

- Kung ang ATMISP ay may problema sa pakikipag-usap sa JTAG chain ng hardware ng device, subukang patakbuhin ang Self Calibrate o Manually Calibrate upang babaan ang mga frequency ng JTAG mga senyales.

- Tiyaking naka-on ang LED sa ATDH1150USB cable at berde ito bago magsimula ang programming. Siguraduhin na ang ISP download cable ay maayos na nakikipag-ugnayan sa ATMISP software.

- Siguraduhin na ang wastong VCC voltage ay inilapat sa ATDH1150USB cable.

- Ang VCC na ginamit ng unang device sa JTAG dapat ibigay ang chain sa ATDH1150USB cable sa pamamagitan ng pin 4 ng 10-pin JTAG header.

- Para sa mga ATF15xx CPLD na may hiwalay na VCCINT at VCCIO, dapat gamitin ang VCCIO para sa ATDH1150USB cable.

Impormasyon sa Pag-order

| Code ng Pag-order | Paglalarawan |

| ATF15xx-DK3-U | CPLD Development/Programmer Kit (kasama ang ATF15xxDK3-SAA44 at ATDH1150USB o ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | 100-pin TQFP Socket Adapter Board para sa DK3 Board |

| ATF15xxDK3-SAJ44 | 44-pin PLCC Socket Adapter Board para sa DK3 Board |

| ATF15xxDK3-SAJ84 | 84-pin PLCC Socket Adapter Board para sa DK3 Board |

| ATF15xxDK3-SAA44 | 44-pin TQFP Socket Adapter Board para sa DK3 Board |

| ATDH1150USB | Atmel ATF15xx CPLD USB-based na JTAG ISP Download Cable |

Kasaysayan ng Pagbabago

| Dok. Sinabi ni Rev. | Petsa | Mga komento |

| A | 12/2015 | Paunang paglabas ng dokumento. |

IMPORMASYON SA CONTACT

Atmel Corporation

- 1600 Technology Drive, San Jose, CA 95110 USA

- T: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_User Guide-12/2015

Ang Atmel®, logo ng Atmel at mga kumbinasyon nito, Pag-enable ng Walang Limitasyong Posibilidad®, at iba pa ay mga rehistradong trademark o trademark ng Atmel Corporation sa US at iba pang mga bansa. Ang ibang mga termino at pangalan ng produkto ay maaaring mga trademark ng iba.

DISCLAIMER: Ang impormasyon sa dokumentong ito ay ibinigay kaugnay ng mga produkto ng Atmel. Walang lisensya, hayag o ipinahiwatig, sa pamamagitan ng estoppel o kung hindi man, sa anumang karapatan sa intelektwal na ari-arian ang ibinibigay ng dokumentong ito o kaugnay ng pagbebenta ng mga produkto ng Atmel. MALIBAN SA ITINAKDA SA MGA TUNTUNIN AT KUNDISYON NG ATMEL NG SALES NA MATATAGPUAN SA ATMEL WEBSITE, ANG ATMEL AY WALANG PANANAGUTAN KAHIT ANO MAN AT TINATAWAN ANG ANUMANG TAHAS, IPINAHIWATIT, O STATUTORY WARRANTY NA KAUGNAY SA MGA PRODUKTO NITO KASAMA, NGUNIT HINDI LIMITADO SA, ANG IPINAHIWATIG NA WARRANTY NG KAKAYKAL, KAANGKUPAN PARA SA ISANG PARTIKULAR NA PURPOSE. KAHIT KAHIT KAHIT KAHIT KAHIT PANANAGUTAN ANG ATMEL PARA SA ANUMANG DIREKTA, DIREKTO, KINAHIHUNGNAN, PUNITIVE, ESPESYAL, O INSIDENTAL NA MGA PINSALA (KASAMA ANG, WALANG LIMITASYON, MGA PINSALA PARA SA PAGKAWAL AT KITA, PAGBABAG SA NEGOSYO, O PAGKAWALA NG IMPORMASYON SA PAGGAMIT) GAMITIN ANG DOKUMENTONG ITO, KAHIT NAABISYO NA ANG ATMEL SA POSIBILIDAD NG GANITONG MGA PINSALA. Ang Atmel ay hindi gumagawa ng mga representasyon o warranty na may paggalang sa katumpakan o pagkakumpleto ng mga nilalaman ng dokumentong ito at inilalaan ang karapatang gumawa ng mga pagbabago sa mga detalye at paglalarawan ng produkto anumang oras nang walang abiso. Ang Atmel ay hindi gumagawa ng anumang pangako na i-update ang impormasyong nakapaloob dito. Maliban kung partikular na ibinigay kung hindi man, ang mga produkto ng Atmel ay hindi angkop para sa, at hindi dapat gamitin sa mga automotive application. Ang mga produkto ng Atmel ay hindi inilaan, pinahintulutan, o ginagarantiyahan para sa paggamit bilang mga bahagi sa mga application na nilayon upang suportahan o mapanatili ang buhay. SAFETY-CRITICAL, MILITARY, AT AUTOMOTIVE APPLICATIONS DISCLAIMER: Ang mga produkto ng Atmel ay hindi idinisenyo para sa at hindi gagamitin kaugnay ng anumang mga application kung saan ang pagkabigo ng naturang mga produkto ay makatuwirang inaasahang magreresulta sa malaking personal na pinsala o kamatayan ("Safety-Critical Mga aplikasyon”) nang walang partikular na nakasulat na pahintulot ng opisyal ng Atmel. Kabilang sa mga application na kritikal sa kaligtasan, nang walang limitasyon, ang mga device at system na sumusuporta sa buhay, kagamitan o sistema para sa pagpapatakbo ng mga pasilidad ng nuklear at sistema ng armas. Ang mga produkto ng Atmel ay hindi idinisenyo o inilaan para sa paggamit sa militar o aerospace na mga aplikasyon o kapaligiran maliban kung partikular na itinalaga ng Atmel bilang militar-grade. Ang mga produkto ng Atmel ay hindi idinisenyo o inilaan para sa paggamit sa mga automotive application maliban kung partikular na itinalaga ng Atmel bilang automotive-grade.

Mga Dokumento / Mga Mapagkukunan

|

Atmel ATF15xx Complex Programmable Logic Device [pdf] Gabay sa Gumagamit ATF15xx, ATF15xx Complex Programmable Logic Device, Complex Programmable Logic Device, Programmable Logic Device, Logic Device, Device |