Dispositivo lóxico programable complexo Atmel ATF15xx

Especificacións

- Nome do produto: Atmel ATF15xx Programación no sistema

- Modelo: ATF15xx

- Tipo: Dispositivo lóxico programable complexo (CPLD)

- Método de programación: Programación no sistema (ISP)

- Interface: JTAG Interface ISP

- Fabricante: Atmel

Preguntas frecuentes

P: Podo usar software de programación de terceiros cos CPLD ATF15xx?

R: Si, sempre que o software admita o algoritmo de programación e JTAG instrucións necesarias para os CPLD ATF15xx.

P: É posible programar varios CPLD ATF15xx simultaneamente?

R: Si, o JTAG A interface do ISP admite a programación de varios dispositivos para unha programación eficiente de varios CPLD á vez.

Introdución

- Os dispositivos lóxicos programables complexos (CPLD) Atmel® ATF15xx con arquitectura Logic Doubling® admiten programación en sistema (ISP) a través do estándar IEEE. 1149.1 Grupo de acción de proba conxunto (JTAG) interface. Esta característica mellora a flexibilidade de programación e proporciona beneficios en varias fases; desenvolvemento de produtos, produción e uso no campo. Esta guía do usuario describe os métodos de deseño e os requisitos para implementar ISP en CPLD ATF15xx con compatibilidade con ISP, como se indica a continuación:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Características e beneficios

A programación no sistema permite programar e reprogramar os dispositivos ISP despois de que se montan nas placas de circuíto impreso (PCB). Isto elimina o paso adicional de manipulación necesario no proceso de fabricación para programar os dispositivos nun programador de dispositivos externos antes de montarlos nos PCB. Eliminar este paso reduce a posibilidade de danar os cables delicados dos dispositivos de montaxe en superficie de gran número de pinos ou de danar o dispositivo a través da descarga electrostática (ESD) durante o fluxo de programación. O ISP tamén permite aos usuarios facer cambios de deseño e actualizacións de campo sen ter que eliminar os dispositivos ISP dos PCB. Ademais, tamén permite o uso dun microcontrolador incorporado ou un probador de circuíto para realizar operacións de programación no sistema nos dispositivos ISP e integrar estas operacións de programación no fluxo de produción das placas de circuíto.

Sistemas de programación dentro do sistema

Os tres compoñentes esenciais dun sistema ISP para os CPLD ATF15xx son:

Software

Implementación do algoritmo de programación, así como a xeración do JTAG instrucións e datos para os dispositivos ISP de destino. Este pode ser un programa de software que se executa nun PC, un microcontrolador integrado ou un equipo de proba en circuíto.

Hardware de interface

Unha canle de comunicación entre o software do ISP e os dispositivos do ISP na placa de destino. Este pode ser un cable de descarga de ISP ou programador de Atmel ou un provedor de terceiros, equipos de proba en circuíto ou as conexións entre un microcontrolador integrado e os dispositivos ISP na PCB.

Xunta de destino

Placa de circuíto que contén os dispositivos ISP no JTAG cadea. Esta pode ser a placa de desenvolvemento/programador CPLD ATF15xx de Atmel ou unha placa de circuíto deseñada a medida co J apropiado.TAG conexións ao hardware da interface.

Ademais destes tres compoñentes, un JEDEC file é necesario programar un CPLD ATF15xx. Este JEDEC file pódese crear compilando un deseño file utilizando software de desenvolvemento que admita os CPLD ATF15xx como Atmel WinCUPL e Atmel ProChip Designer. Atmel tamén ofrece unha utilidade de software de tradutor, POF2JED.exe, que converte a saída file desde o formato de programación do competidor ata un JEDEC file compatible co ATF15xx CPLD. Para obter máis información sobre esta utilidade, consulte a nota da aplicación Atmel, "Conversión da familia de produtos ATF15xx", dispoñible no Atmel. websitio. Despois do JEDEC files créanse para todos os CPLD ATF15xx, pódense programar na placa de destino. Os CPLD ATF15xx pódense programar polos seguintes sistemas de programación do sistema:

- Sistema de programación en sistema ATF15xx

- Microcontroladores embebidos

- Probadores en circuíto

Sistema de programación en sistema Atmel ATF15xx

Para a programación no sistema dos CPLD ATF15xx, o software do ISP, o cable de descarga e o kit de desenvolvemento/programador están dispoñibles en Atmel e descríbense nas seccións a continuación.

Software ISP

O software Atmel ATF15xx ISP, ATMISP, é o medio principal para implementar JTAG programación no sistema nos CPLD ATF15xx. ATMISP execútase nun PC host baseado en Windows e implementa a programación no sistema dos CPLD ATF15xx no sistema de hardware do ISP de destino ou xera un formato vectorial en serie (.SVF) file para ser usado polo equipo de proba automático (ATE) para programar os CPLD ATF15xx no sistema de destino. ATMISP adquire primeiro toda a información necesaria dos usuarios sobre o JTAG cadea de dispositivos no sistema de destino. Despois executa o JTAG Instrucións do ISP sobre JTAG cadea de dispositivos no sistema de destino segundo JTAG información da cadea de dispositivos especificada polos usuarios a través do porto USB ou LPT do PC. Máis información sobre o software Atmel ATMISP está dispoñible en www.atmel.com/tools/ATMISP.aspx.

Cable de descarga do ISP

O cable de descarga de ISP baseado en USB Atmel ATF15xx, ATDH1150USB, conéctase a un porto USB estándar dun ordenador host nun lado e a un JTAG cabeceira da placa de circuíto de destino no outro lado. Transfiere o JTAG instrucións e datos xerados por ATMISP en execución no PC host para os dispositivos ISP na placa de circuíto de destino. Máis información sobre o cable ATDH1150USB está dispoñible en www.atmel.com/tools/ATDH1150USB.aspx.

Desenvolvedor/Programador

O kit de desenvolvemento/programador Atmel ATF15xx, ATF15xx-DK3-U, é un sistema de desenvolvemento completo e un programador ISP para os CPLD ATF15xx. Este kit ofrece aos deseñadores un xeito moi rápido e sinxelo de desenvolver prototipos e avaliar novos deseños cun CPLD ISP ATF15xx. Coa dispoñibilidade das diferentes placas adaptadoras de socket para soportar a maioría dos tipos de paquetes ofrecidos nos CPLD ATF15xx, este kit pódese usar como programador ISP para programar os CPLD ATF15xx ISP na maioría dos tipos de paquetes dispoñibles a través do JTAG interface. Máis información sobre o kit Atmel ATF15xx-DK3-U está dispoñible en www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Sistema de microcontrolador integrado

O algoritmo de programación e JTAG as instrucións para os CPLD ATF15xx pódense implementar nun microcontrolador ou microprocesador, que logo pode usarse para programar os CPLD ATF15xx na placa de destino. Un método posible é extraer todos os datos de JTAG información de protocolo (ie JTAG instrucións e datos) do SVF file xerado polo software ATMISP e, a continuación, use esta información para implementar código para o microcontrolador ou microprocesador que xeraría o JTAG sinais para os dispositivos ISP en JTAG cadea. Este enfoque é máis adecuado para sistemas que xa teñen un microcontrolador ou un microprocesador incorporado, e isto elimina o uso de ferramentas de hardware e software de programación externas no sistema.

Sistema de proba en circuíto

Os CPLD ATF15xx pódense programar na placa de circuíto de destino a través do JTAG interface durante a proba da placa de circuíto mediante un comprobador de circuíto. Xeralmente, o SVF file xerado por ATMISP debe conter todos os datos JTAG información de programación no sistema que necesitan os probadores de circuíto para programar os CPLD ATF15xx na placa de circuíto de destino. Este enfoque permite a integración do paso de programación no testing stage do fluxo de produción.

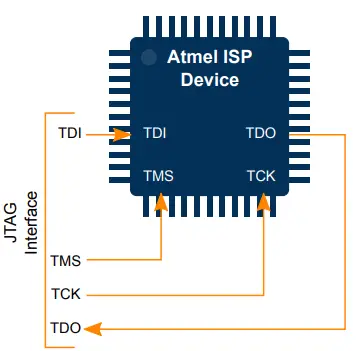

JTAG Interface ISP

O ISP para os CPLD ATF15xx está implementado mediante o estándar IEEE 1149.1. JTAG interface. Esta interface pódese usar para borrar, programar e verificar os CPLD ATF15xx. O JTAG interface é unha interface en serie formada polos sinais TCK, TMS, TDI e TDO e un JTAG Controlador de porto de acceso de proba (TAP). O pin TCK é a entrada de reloxo para JTAG TAP controlador e para cambiar a entrada/saída do JTAG instrucións e datos. O pin TDI é a entrada de datos en serie. Utilízase para transferir as instrucións de programación e os datos aos dispositivos ISP. O pin TDO é a saída de datos en serie. Utilízase para transferir datos dos dispositivos ISP. O pin TMS é un pin de selección de modo. Controla o estado do JTAG Controlador TAP. O JTAG os pinos da interface do ATF15xx CPLD na placa de destino do ISP deben conectarse ao hardware da interface do ISP (é dicir, o cable de descarga do ISP) normalmente mediante un encabezado de 10 pinos. O hardware da interface do ISP tamén debe estar conectado ao ordenador host que executa o software do ISP. O hardware da interface do ISP establece a comunicación entre o software do ISP e os dispositivos do ISP, e permite que o software do ISP transfira as instrucións de programación e os datos do PC host aos CPLD ATF15xx. CPLD ATF15xx con JTAG as funcións habilitadas son totalmente JTAG compatible e tamén admite as operacións de proba de exploración de límites (BST) necesarias especificadas no JTAG estándar. Os CPLD ATF15xx pódense configurar para formar parte dun JTAG Cadea BST con outros JTAG dispositivos para probas en circuíto da placa base. Con esta función, os CPLD ATF15xx pódense probar na placa de circuíto xunto con outros JTAG-dispositivos compatibles sen recorrer á proba de uñas.

Programación dun único dispositivo

O JTAG A interface ISP pódese configurar para programar un único CPLD ATF15xx. O JTAG a configuración dun único dispositivo móstrase na seguinte figura. Cando se configura un CPLD ATF15xx deste xeito, aparece un rexistro entre os pinos TDI e TDO do dispositivo. O tamaño do rexistro depende do JTAG ancho da instrución e os datos que se están cambiando para esa instrución. Figura 2-1 JTAG Dispositivo

Programación de varios dispositivos

Os CPLD ATF15xx pódense configurar como parte dunha cadea de varios JTAG-dispositivos compatibles como se describe a continuación e tamén se mostra na seguinte figura.

- Conecte o pin TMS e TCK para cada dispositivo no JTAG cadea aos pinos TMS e TCK do JTAG cabeceira da interface na placa de circuíto.

- Conecte o pin TDI do primeiro dispositivo ao pin TDI do JTAG cabeceira da interface.

- Conecte o pin TDO do primeiro dispositivo ao pin TDI do seguinte dispositivo. Continúa este proceso ata que todos, excepto o último, estean conectados.

- Conecte o pin TDO do último dispositivo ao pin TDO do JTAG cabeceira da interface.

Figura 2-2 Dispositivo múltiple JTAG Configuración

Para programar varios dispositivos nun JTAG cadea, os usuarios deben utilizar ferramentas de software do ISP que admitan tales funcións. No software do ISP, os usuarios deben especificar:

- Número de dispositivos en JTAG cadea.

- Números de peza dos dispositivos e posicións dentro do JTAG cadea.

- JTAG operacións para cada un dos dispositivos.

- Outros JTAG-información relacionada como JTAG ancho de instrucións para cada un dos dispositivos.

Unha vez que JTAG a cadea de margaritas está configurada correctamente na placa de destino do ISP e no software do ISP, os dispositivos do JTAG a cadea pódese programar ao mesmo tempo.

Consideracións de deseño

Para realizar un ISP nun CPLD ATF15xx, recursos para JTAG debe reservarse a interface no ATF15xx. Polo tanto, os catro pinos de E/S para os pinos TMS, TDI, TDO e TCK deben reservarse para JTAG e non se pode utilizar como E/S de usuario. Os números de pin para estes pinos dependen do CPLD ATF15xx que se utilice e do tipo de paquete. Consulte a seguinte táboa para obter información sobre o pinout. O JTAG estándar recomenda que os pinos TMS e TDI se levanten para cada dispositivo no JTAG cadea. Os CPLD ATF15xx teñen unha función de extracción interna para estes pinos que, cando se activa, aforra a necesidade de resistencias de extracción externas. Ademais, o JTAG A función de interface debe estar activada para realizar ISP nos CPLD ATF15xx. Habilitando JTAG A interface require escoller tipos específicos de dispositivos Atmel ou opcións de configuración antes de compilar o deseño ATF15xx. Estes procedementos descríbense para WinCUPL, ProChip Designer e POF2JED nesta guía. De forma predeterminada, todos os novos CPLD ATF15xx envíanse co JTAG interface habilitada. Unha vez que os recursos lóxicos para JTAG interface están reservadas, os usuarios poden programar, verificar e borrar calquera CPLD ATF15xx na placa de destino usando o software ATMISP.

Consello: Aínda que os catro JTAG os pinos están reservados para un JTAG interface, os usuarios poden implementar funcións lóxicas enterradas nas macrocélulas asociadas a estes pinos.

Táboa 3-1 ATF15xx CPLD JTAG Números de Pin

| JTAG Pin | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Activar JTAG Interface con WinCUPL

Para habilitar JTAG interface con WinCUPL, o tipo de dispositivo ATF15xx ISP adecuado debe especificarse antes de compilar un deseño. Despois de compilar un deseño con éxito, un JEDEC file co JTAG Xérase a función da interface habilitada. Cando este JEDEC file está programado nun ATF15xxCPLD, o seu JTAG interface está activada. Os usuarios tamén poden activar as resistencias de extracción internas TDI e TMS incluíndo as seguintes declaracións de propiedade no deseño CUPL file.

- PROPIEDADE ATMEL {TDI_PULLUP = ON};

- PROPIEDADE ATMEL {TMS_PULLUP = ON};

Aviso: Se se usa un tipo de dispositivo ISP ATF15xx para un deseño que utiliza o JTAG pins da interface como pines de E/S lóxica, WinCUPL xera un erro.

Os seguintes pasos explican como abrir un deseño existente en WinCUPL, especificar o tipo de dispositivo e compilar o deseño.

- No menú principal de WinCUPL, seleccione File > Abrir. Seleccione a fonte CUPL (.pld). file dende o directorio de traballo axeitado.

- Seleccione Aceptar para abrir a fonte PLD file.

- No menú principal de WinCUPL, seleccione File > Gardar. Isto gárdanse os cambios feitos na fonte file.

- No menú principal, seleccione Opcións > Dispositivos. Isto abre o cadro de diálogo Selección de dispositivos.

- Escolla o dispositivo ATF15xx ISP adecuado. Consulte a seguinte táboa para ver unha lista de todos os tipos de dispositivos ATF15xx compatibles con WinCUPL.

- Seleccione Aceptar para pechar o menú de selección de dispositivos.

- Nota: Un método alternativo é escoller un tipo de dispositivo ATF15xx axeitado da seguinte táboa e incluílo na sección de cabeceira da fonte CUPL file.

- No menú principal de WinCUPL, seleccione Executar> Compilación dependente do dispositivo.

- WinCUPL compila o deseño e xera o instalador de dispositivos Atmel. Se o deseño encaixa, un JEDEC file créase automaticamente.

- Cando o JEDEC file está programado no dispositivo, o JTAG están habilitados os pull-ups internos opcionales de TMS e TDI e os circuítos de garda-pins opcionais.

Nota: A selección dun tipo de dispositivo ISP de Atmel activa automaticamente o dispositivo JTAG interface por defecto cando Atmel WinCUPL executa o instalador de dispositivos Atmel.

Se os deseños impiden reservar recursos para o JTAG interface ou un ISP opcionalmente non se utiliza, debe seleccionarse un tipo de dispositivo Atmel non ISP. Consulte a táboa seguinte para ver unha lista de dispositivos. O dispositivo pódese reprogramar mediante un programador externo. A seguinte táboa enumera os tipos de dispositivos Atmel ISP e Atmel non ISP para WinCUPL.

Táboa 3-2 Tipo de dispositivo WinCUPL ATF15xx

| Nome do dispositivo | Tipo de paquete | Tipo de dispositivo WinCUPL | |

| JTAG Activado | JTAG Desactivado | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Activar JTAG Interface con Atmel ProChip Designer

Para habilitar JTAG interface con ProChip Designer:

- Abra o proxecto ProChip Designer adecuado.

- Abre a xanela Opcións do instalador facendo clic no botón Atmel Fitter en Device Fitter.

- Seleccione a pestana Dispositivo global e, a continuación, marque JTAG Caixa de porto. As resistencias de pull-up internas de TMS e TDI tamén se poden activar marcando as caixas TDI Pullup e TMS Pullup. Estas caixas de verificación móstranse na seguinte figura.

Figura 3-1 Interface de usuario das opcións do instalador de ProChip Designer

Activar JTAG Interface con POF2JED

En POF2JED, o JTAG A opción de modo pódese configurar en Auto para que POF2JED determine se o JTAG A función do ATF15xx debería estar activada ou non, e baséase en se JTAG é compatible no CPLD do competidor. Para activar JTAG no CPLD ATF15xx independentemente de que JTAG está admitido no CPLD do competidor ou non, o JTAG A opción de modo debe estar activada. Cando JTAG está activado no ATF15xx, as resistencias de pull-up internas TDI e TMS pódense activar marcando a opción Activar

TDI_PULLUP e Activar caixas TMS_PULLUP en POF2JED. Vexa a figura a continuación.

Figura 3-2 Interface de usuario POF2JED

Directrices e recomendacións

Atención: Débese prestar especial atención a esta sección ao realizar operacións de ISP en CPLD ATF15xx. Esta sección trata algúns dos JTAG Directrices, información e recomendacións do ISP que deben ser ben observadas.

- Asegúrese de que JTAG porto para todos os dispositivos do JTAG cadea están habilitadas.

- Para os CPLD ATF15xx, o JTAG o porto está habilitado se os dispositivos están en branco/borrados ou programados con JTAG activado.

- Todos os dispositivos Atmel ATF15xx envíanse no estado en branco/borrado; polo tanto, JTAG O porto está habilitado para todos os dispositivos novos e listo para o ISP.

- Dispositivos ATF15xx con JTAG os desactivados deben borrarse usando un programador de dispositivos que non sexa ISP para volver habilitar o JTAG porto.

- Asegúrese de que o VCC voltage aplícase a cada un dos dispositivos do JTAG cadea.

- CPLD ATF15xxAS/ASL nos tipos de paquete 84-PLCC, 100-TQFP e 100-PQFP: VCCINT debe estar entre 4.5 V e 5.5 V mentres que VCCIO pode estar entre 3.0 V e 3.6 V ou 4.5 V e 5.5 V.

- CPLD ATF15xxAS/ASL nos tipos de paquete 44-PLCC e 44-TQFP: VCC debe estar entre 4.5 V e 5.5 V.

- CPLD ATF15xxASV/ASVL: VCC (VCCIO e VCCINT) debe estar entre 3.0 V e 3.6 V.

- O VCC para os dispositivos do JTAG a cadea debe estar debidamente regulada e filtrada.

- Para os CPLD ATF15xx utilizados na maioría das aplicacións, recoméndase utilizar un capacitor de desacoplamento de 0.22 µF para cada un dos pares VCC/GND.

- Recoméndase utilizar un punto común para todos os dispositivos do JTAG cadea e JTAG hardware de interface (por exemplo, cable de descarga ATDH1150USB ISP).

- Recoméndase evitar longos (non máis de cinco dispositivos) JTAG cadeas.

- Se un longo JTAG é necesaria unha cadea, tampone os sinais TMS e TCK despois de cada quinto dispositivo. É preferible o uso do búfer de activación de Schmitt.

- Os buffers remodelan os tempos de subida e baixada dos sinais TMS e TCK.

- Hai que ter en conta o atraso adicional causado polos buffers.

- Recoméndase utilizar resistencias pull-up (4.7KΩ a 10KΩ) para os sinais TMS e TDI e unha resistencia pull-down para o sinal TCK no J.TAG cabeceira para evitar que estes sinais floten cando non están sendo controlados polo hardware da interface.

- Os pull-ups internos opcionais en TMS e TDI están dispoñibles para os CPLD ATF15xx.

- Recoméndase finalizar JTAG sinais na JTAG cabeceira.

- As terminacións activas e pasivas son aceptables; non obstante, prefírese a terminación pasiva.

- Reduce o timbre debido ás longas lonxitudes de trazo de cable/PCB.

- A terminación é a máis crítica para TMS e TCK.

- Recoméndase que todas as entradas e E/S dos dispositivos no JTAG cadea, excepto a JTAG pins, deberían estar en estado estático cando se están programando os CPLD ATF15xx para minimizar o ruído.

- Cando se utiliza unha das placas de desenvolvemento/programación Atmel ATF15xx, a alimentación da placa debe estar desactivada cando se cambien as posicións dos puentes de selección VCC.

- Para os CPLD ATF15xx, JTAG O ISP está dispoñible cando a peza está no modo de apagamento controlado por Pin ou cando o dispositivo de "baixa potencia" está durmido.

- Estado do dispositivo despois da interrupción do ISP:

- Se se interrompe o ISP, todos os pinos de E/S están en tres estados independentemente do estado dos circuítos do Pin-keeper.

- Evita que os dispositivos parcialmente programados causen conflitos de bus con outros dispositivos da placa de circuíto.

- Durante a programación do ISP, todos os pinos de E/S están nunha das seguintes condicións:

- Estado de alta impedancia:

- Cando se programa un dispositivo en branco/borrado.

- Cando se reprograma un dispositivo cos circuítos Pin-keeper desactivados.

- Evita a contención de bus con dispositivos externos que interactúan cos CPLD ATF15xx da placa de circuíto.

- Debilmente pegado ao estado anterior:

- Cando se reprograma un dispositivo programado cos circuítos Pin-keeper habilitados.

- Os pines de E/S manteñen os niveis lóxicos anteriores antes do ISP.

- Evita que o ISP afecte o funcionamento doutros dispositivos da placa base.

- O uso de múltiples JTAG non se recomendan cadeas nun taboleiro.

- Os dispositivos poden interactuar entre diferentes JTAG cadeas.

- A placa só funciona cando todos os dispositivos en todos os dispositivos JTAG as cadeas están programadas correctamente.

- Se a programación falla para polo menos un dispositivo nunha cadea mentres que outros JTAG as cadeas foron programadas con éxito:

- Calquera Atmel ou outros dispositivos a bordo poden danarse debido a un posible problema de contención do bus para as saídas de tres estados.

- O estado operativo da placa do sistema non está definido; e polo tanto, pode producirse a operación funcional incorrecta.

- Inserción de circuítos activos entre JTAG cabeceira e JTAG dispositivos en cadea non se recomenda. Se o circuíto activo funciona mal, pode causar problemas de programación/verificación.

- O uso de mixed-voltago dispositivo JTAG non se recomenda cadeas.

- Estes son JTAG cadeas con dispositivos que utilizan diferentes VCC voltages e/ou interface voltages.

- Interface voltagOs niveis e (VIL, VIH, VOL, VOH) para dispositivos de 5.0 V poden non ser compatibles coa interface voltagNiveis e para dispositivos de 3.0 V.

- Se ATMISP ten problemas para comunicarse co JTAG cadea de hardware do dispositivo, intente executar Self Calibrate ou Manually Calibrate para baixar as frecuencias do JTAG sinais.

- Asegúrese de que o LED do cable ATDH1150USB estea acendido e que estea en verde antes de comezar a programación. Asegúrese de que o cable de descarga do ISP poida comunicarse correctamente co software ATMISP.

- Asegúrese de que o VCC voltage aplícase ao cable ATDH1150USB.

- O VCC usado polo primeiro dispositivo no JTAG A cadea debe subministrarse ao cable ATDH1150USB a través do pin 4 do conector J de 10 pines.TAG cabeceira.

- Para CPLD ATF15xx con VCCINT e VCCIO separados, VCCIO debe utilizarse para o cable ATDH1150USB.

Información de pedido

| Código de pedido | Descrición |

| ATF15xx-DK3-U | Kit de desenvolvemento/programador CPLD (inclúe ATF15xxDK3-SAA44 e ATDH1150USB ou ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | Placa adaptadora de enchufe TQFP de 100 pines para placa DK3 |

| ATF15xxDK3-SAJ44 | Placa adaptadora de enchufe PLCC de 44 pines para placa DK3 |

| ATF15xxDK3-SAJ84 | Placa adaptadora de enchufe PLCC de 84 pines para placa DK3 |

| ATF15xxDK3-SAA44 | Placa adaptadora de enchufe TQFP de 44 pines para placa DK3 |

| ATDH1150USB | Atmel ATF15xx CPLD baseado en USB JTAG Cable de descarga do ISP |

Historial de revisións

| Doc. Rev. | Data | Comentarios |

| A | 12/2015 | Publicación do documento inicial. |

INFORMACIÓN DE CONTACTO

Corporación Atmel

- 1600 Technology Drive, San Jose, CA 95110 USA

- Teléfono: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_Guía de usuario-12/2015

Atmel®, o logotipo de Atmel e as súas combinacións, Enabling Unlimited Possibilities® e outros son marcas rexistradas ou marcas comerciais de Atmel Corporation nos EUA e noutros países. Outros termos e nomes de produtos poden ser marcas comerciais doutros.

EXENCIÓN DE RESPONSABILIDADE: A información deste documento ofrécese en relación cos produtos Atmel. Este documento ou en relación coa venda de produtos Atmel non concede ningunha licenza, expresa ou implícita, por exclusión ou doutra forma, a ningún dereito de propiedade intelectual. EXCEPTO O ESTABLECIDO NOS TERMOS E CONDICIÓNS DE VENDA DE ATMEL UBICADOS NO ATMEL WEBSITIO, ATMEL NON ASUME NINGUNHA RESPONSABILIDADE E RENUNCIA A NINGÚN GARANTÍA EXPRESA, IMPLÍCITA OU ESTATUTORIA RELACIONADA COS SEUS PRODUTOS INCLUÍENDO, PERO NON LIMITADO A, A GARANTÍA IMPLÍCITA DE COMERCIABILIDADE, ADECUACIÓN PARA UN FIN PARTICULAR INFANTIL. EN NINGÚN CASO ATMEL SERÁ RESPONSABLE DE NINGÚN DANOS DIRECTOS, INDIRECTOS, CONSECUENTES, PUNITIVOS, ESPECIAIS OU INCIDENTAIS (INCLUIDOS, SEN LIMITACIÓNS, DANOS POR PERDAS E BENEFICIOS, INTERRUPCIÓN DE NEGOCIOS OU PERDA DE INFORMACIÓN) DERIVADOS DA CAPACIDADE DE USO USE ESTE DOCUMENTO, AÍNDA QUE ATMEL FOI AVISO DA POSIBILIDADE DE ESTOS DANOS. Atmel non fai ningunha representación ou garantía con respecto á exactitude ou integridade do contido deste documento e resérvase o dereito de facer cambios nas especificacións e descricións dos produtos en calquera momento sen previo aviso. Atmel non se compromete a actualizar a información aquí contida. A non ser que se dispoña expresamente o contrario, os produtos Atmel non son axeitados para, e non se deben utilizar en aplicacións automotivas. Os produtos Atmel non están destinados, autorizados ou garantidos para o seu uso como compoñentes en aplicacións destinadas a soportar ou manter a vida útil. EXENCIÓN DE RESPONSABILIDADE DE APLICACIÓNS CRÍTICAS PARA A SEGURIDADE, MILITAR E AUTOMOTRIZ: os produtos Atmel non están deseñados e non se utilizarán en conexión con ningunha aplicación na que se poida esperar razoablemente que o fallo destes produtos produza danos persoais significativos ou morte ("Críticas para a seguridade Aplicacións”) sen o consentimento escrito específico dun oficial de Atmel. As aplicacións críticas para a seguridade inclúen, sen limitación, dispositivos e sistemas de soporte vital, equipos ou sistemas para o funcionamento de instalacións nucleares e sistemas de armas. Os produtos Atmel non están deseñados nin destinados para o seu uso en aplicacións ou ambientes militares ou aeroespaciais a non ser que Atmel o designe especificamente como de grao militar. Os produtos Atmel non están deseñados nin destinados para o seu uso en aplicacións automotrices a non ser que Atmel o designe especificamente como aptos para automoción.

Documentos/Recursos

|

Dispositivo lóxico programable complexo Atmel ATF15xx [pdfGuía do usuario ATF15xx, ATF15xx Dispositivo lóxico programable complexo, Dispositivo lóxico programable complexo, Dispositivo lóxico programable, Dispositivo lóxico, Dispositivo |