Dispositiu lògic programable complex Atmel ATF15xx

Especificacions

- Nom del producte: Atmel ATF15xx Programació en el sistema

- Model: ATF15xx

- Tipus: dispositiu lògic programable complex (CPLD)

- Mètode de programació: programació en el sistema (ISP)

- Interfície: JTAG Interfície ISP

- Fabricant: Atmel

Preguntes freqüents

P: Puc utilitzar programari de programació de tercers amb els CPLD ATF15xx?

R: Sí, sempre que el programari admeti l'algoritme de programació i JTAG instruccions necessàries per als CPLD ATF15xx.

P: És possible programar diversos CPLD ATF15xx simultàniament?

A: Sí, el JTAG La interfície ISP admet la programació de diversos dispositius per a una programació eficient de diversos CPLD alhora.

Introducció

- Els dispositius lògics programables complexos (CPLD) Atmel® ATF15xx amb arquitectura Logic Doubling® admeten la programació en el sistema (ISP) a través de l'IEEE Std. 1149.1 Joint Test Action Group (JTAG) interfície. Aquesta característica millora la flexibilitat de programació i proporciona avantatges en diverses fases; desenvolupament de productes, producció i ús de camp. Aquesta guia de l'usuari descriu els mètodes de disseny i els requisits per implementar l'ISP als CPLD ATF15xx amb compatibilitat amb ISP, tal com s'enumeren a continuació:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Característiques i avantatges

La programació dins del sistema permet programar i reprogramar els dispositius ISP després de muntar-los a les plaques de circuits impresos (PCB). Això elimina el pas addicional de manipulació requerit en el procés de fabricació per programar els dispositius en un programador de dispositius externs abans que es muntin a les PCB. L'eliminació d'aquest pas redueix la possibilitat de danyar els cables delicats dels dispositius de muntatge en superfície amb un gran nombre de pins o de danyar el dispositiu mitjançant descàrregues electrostàtiques (ESD) durant el flux de programació. L'ISP també permet als usuaris fer canvis de disseny i actualitzacions de camp sense haver de treure els dispositius ISP de les PCB. A més, també permet l'ús d'un microcontrolador incrustat o provador en circuit per realitzar operacions de programació dins del sistema als dispositius ISP i integrar aquestes operacions de programació en el flux de producció de les plaques de circuit.

Sistemes de programació dins del sistema

Els tres components essencials d'un sistema ISP per als CPLD ATF15xx són:

Programari

Implementació de l'algorisme de programació, així com la generació del JTAG instruccions i dades per als dispositius ISP objectiu. Pot ser un programa de programari que s'executa en un ordinador, un microcontrolador incrustat o un equip de prova en circuit.

Maquinari d'interfície

Un canal de comunicació entre el programari ISP i els dispositius ISP a la placa de destinació. Pot ser un cable de descàrrega d'ISP o un programador d'Atmel o un proveïdor extern, equips de prova en circuit o les connexions entre un microcontrolador incrustat i dispositius ISP a la PCB.

Junta de destinació

Placa de circuits que conté els dispositius ISP a JTAG cadena. Aquesta pot ser la placa de desenvolupament/programador CPLD ATF15xx d'Atmel o una placa de circuit dissenyada a mida amb la J adequada.TAG connexions al maquinari de la interfície.

A més d'aquests tres components, un JEDEC file és necessari programar un CPLD ATF15xx. Aquest JEDEC file es pot crear compilant un disseny file utilitzant programari de desenvolupament que admet els CPLD ATF15xx com Atmel WinCUPL i Atmel ProChip Designer. Atmel també ofereix una utilitat de programari de traducció, POF2JED.exe, que converteix la sortida file des del format de programació del competidor fins a un JEDEC file compatible amb el CPLD ATF15xx. Per obtenir més informació sobre aquesta utilitat, consulteu la nota de l'aplicació Atmel, "Conversió de la família de productes ATF15xx", disponible a Atmel. weblloc. Després del JEDEC files es creen per a tots els CPLD ATF15xx, es poden programar a la placa de destinació. Els CPLD ATF15xx es poden programar mitjançant els sistemes de programació del sistema següents:

- Sistema de programació dins del sistema ATF15xx

- Microcontroladors encastats

- Comprovadors en circuit

Sistema de programació al sistema Atmel ATF15xx

Per a la programació al sistema dels CPLD ATF15xx, el programari ISP, el cable de descàrrega i el kit de desenvolupament/programador estan disponibles a Atmel i es descriuen a les seccions següents.

Programari ISP

El programari Atmel ATF15xx ISP, ATMISP, és el mitjà principal per implementar JTAG programació interna del sistema als CPLD ATF15xx. ATMISP s'executa en un ordinador amfitrió basat en Windows i implementa la programació al sistema dels CPLD ATF15xx al sistema de maquinari de l'ISP objectiu o genera un format vectorial sèrie (.SVF) file per ser utilitzat per l'equip de prova automàtic (ATE) per programar els CPLD ATF15xx al sistema objectiu. ATMISP primer adquireix tota la informació necessària dels usuaris sobre el JTAG cadena de dispositius al sistema objectiu. A continuació, executa el JTAG Instruccions de l'ISP al fitxer JTAG cadena de dispositius al sistema objectiu segons JTAG informació de la cadena de dispositius especificada pels usuaris a través del port USB o LPT del PC. Més informació sobre el programari Atmel ATMISP està disponible a www.atmel.com/tools/ATMISP.aspx.

Cable de descàrrega de l'ISP

El cable de descàrrega d'ISP basat en USB d'Atmel ATF15xx, ATDH1150USB, es connecta a un port USB estàndard d'un ordinador amfitrió en un costat i a un JTAG capçalera de la placa de circuit objectiu a l'altre costat. Transfereix el JTAG instruccions i dades generades per ATMISP que s'executa a l'ordinador amfitrió als dispositius ISP a la placa de circuit objectiu. Trobareu més informació sobre el cable ATDH1150USB a www.atmel.com/tools/ATDH1150USB.aspx.

Desenvolupament/Programador

El kit de desenvolupament/programador Atmel ATF15xx, ATF15xx-DK3-U, és un sistema de desenvolupament complet i un programador ISP per als CPLD ATF15xx. Aquest kit proporciona als dissenyadors una manera molt ràpida i senzilla de desenvolupar prototips i avaluar nous dissenys amb un CPLD ATF15xx ISP. Amb la disponibilitat de les diferents plaques adaptadores de socket per suportar la majoria dels tipus de paquets que s'ofereixen als CPLD ATF15xx, aquest kit es pot utilitzar com a programador ISP per programar els CPLD ATF15xx ISP en la majoria dels tipus de paquets disponibles mitjançant el J.TAG interfície. Més informació sobre el kit Atmel ATF15xx-DK3-U està disponible a www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Sistema de microcontrolador incrustat

L'algorisme de programació i JTAG Les instruccions per als CPLD ATF15xx es poden implementar en un microcontrolador o microprocessador, que després es poden utilitzar per programar els CPLD ATF15xx a la placa objectiu. Un mètode possible és extreure tots els elements de JTAG informació del protocol (és a dir, JTAG instruccions i dades) de l'SVF file generat pel programari ATMISP, i després utilitzar aquesta informació per implementar codi per al microcontrolador o microprocessador que generaria la JTAG senyals per als dispositius ISP a JTAG cadena. Aquest enfocament és més adequat per als sistemes que ja tenen un microcontrolador o un microprocessador incrustat, i això elimina l'ús de programari de programació i eines de maquinari externes al sistema.

Sistema de proves en circuit

Els CPLD ATF15xx es poden programar a la placa de circuit de destinació mitjançant el JTAG interfície durant les proves de la placa de circuit mitjançant un provador en circuit. En general, l'SVF file generada per ATMISP hauria de contenir tots els elements JTAG informació de programació del sistema que necessiten els provadors dins del circuit per programar els CPLD ATF15xx a la placa de circuit objectiu. Aquest enfocament permet la integració del pas de programació en les provestage del flux de producció.

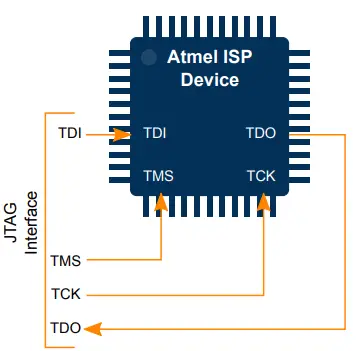

JTAG Interfície ISP

L'ISP per als CPLD ATF15xx s'implementa mitjançant la norma IEEE 1149.1 Std. JTAG interfície. Aquesta interfície es pot utilitzar per esborrar, programar i verificar els CPLD ATF15xx. El JTAG La interfície és una interfície en sèrie que consta dels senyals TCK, TMS, TDI i TDO i una interfície JTAG Controlador del port d'accés de prova (TAP). El pin TCK és l'entrada del rellotge per al JTAG TAP controlador i per canviar d'entrada / sortida del JTAG instruccions i dades. El pin TDI és l'entrada de dades en sèrie. S'utilitza per traslladar instruccions i dades de programació als dispositius ISP. El pin TDO és la sortida de dades en sèrie. S'utilitza per desplaçar dades dels dispositius ISP. El pin TMS és un pin de selecció de mode. Controla l'estat de la JTAG Controlador TAP. El JTAG Els pins d'interfície de l'ATF15xx CPLD a la placa de destinació de l'ISP s'han de connectar al maquinari de la interfície de l'ISP (és a dir, el cable de descàrrega de l'ISP) normalment mitjançant una capçalera de 10 pins. El maquinari de la interfície ISP també ha d'estar connectat a l'ordinador amfitrió que executa el programari ISP. El maquinari de la interfície ISP estableix la comunicació entre el programari ISP i els dispositius ISP, i permet que el programari ISP transfereixi les instruccions i dades de programació des de l'ordinador amfitrió als CPLD ATF15xx. CPLD ATF15xx amb el JTAG Les funcions habilitades són totalment JTAG compatible i també és compatible amb les operacions de prova d'escaneig de límits (BST) requerides especificades al document JTAG estàndard. Els CPLD ATF15xx es poden configurar per formar part d'un JTAG Cadena BST amb altres JTAG dispositius per a proves en circuit de la placa del sistema. Amb aquesta característica, els CPLD ATF15xx es poden provar a la placa de circuit juntament amb altres JTAG-dispositius compatibles sense recórrer a proves de llit d'ungles.

Programació d'un sol dispositiu

El JTAG La interfície ISP es pot configurar per programar un únic CPLD ATF15xx. El JTAG La configuració d'un únic dispositiu es mostra a la figura següent. Quan un CPLD ATF15xx es configura d'aquesta manera, apareix un registre entre els pins TDI i TDO del dispositiu. La mida del registre depèn de la JTAG l'amplada de la instrucció i les dades que s'estan desplaçant per a aquesta instrucció. Figura 2-1 JTAG Dispositiu

Programació de múltiples dispositius

Els CPLD ATF15xx es poden configurar com a part d'una cadena en cadena de múltiples JTAG-dispositius compatibles tal com es descriu a continuació i també es mostra a la figura següent.

- Connecteu el pin TMS i TCK per a cada dispositiu al JTAG cadena als pins TMS i TCK del JTAG capçalera de la interfície a la placa de circuit.

- Connecteu el pin TDI del primer dispositiu al pin TDI de JTAG capçalera de la interfície.

- Connecteu el pin TDO del primer dispositiu al pin TDI del següent dispositiu. Continueu aquest procés fins que tots, excepte l'últim, estiguin connectats.

- Connecteu el pin TDO de l'últim dispositiu al pin TDO del JTAG capçalera de la interfície.

Figura 2-2 Dispositiu múltiple JTAG Configuració

Per programar diversos dispositius en un fitxer JTAG cadena, els usuaris han d'utilitzar eines de programari de l'ISP que admetin aquestes funcions. Al programari ISP, els usuaris han d'especificar:

- Nombre de dispositius a JTAG cadena.

- Els números de part dels dispositius i les posicions dins de la JTAG cadena.

- JTAG operacions per a cadascun dels dispositius.

- Altres JTAG-informació relacionada com la JTAG amplada d'instruccions per a cadascun dels dispositius.

Un cop el JTAG La cadena de margarides està configurada correctament a la placa de destinació de l'ISP i al programari de l'ISP, els dispositius de la JTAG la cadena es pot programar al mateix temps.

Consideracions de disseny

Per dur a terme un ISP en un CPLD ATF15xx, recursos per a JTAG s'ha de reservar la interfície de l'ATF15xx. Per tant, els quatre pins d'E/S per als pins TMS, TDI, TDO i TCK s'han de reservar per a JTAG i no es poden utilitzar com a E/S d'usuari. Els números de pins d'aquests pins depenen de quin ATF15xx CPLD s'utilitza i del tipus de paquet. Consulteu la taula següent per obtenir informació sobre el pinout. El JTAG L'estàndard recomana que els pins TMS i TDI s'aixequin per a cada dispositiu del JTAG cadena. Els CPLD ATF15xx tenen una funció d'extracció interna per a aquests pins que, quan s'habilita, estalvia la necessitat de resistències d'extracció externes. A més, el JTAG La funció d'interfície s'ha d'habilitar per executar l'ISP als CPLD ATF15xx. Habilitant el JTAG La interfície requereix triar tipus de dispositiu Atmel específics o configuracions d'opcions abans de compilar el disseny ATF15xx. Aquests procediments es descriuen per a WinCUPL, ProChip Designer i POF2JED en aquesta guia. Per defecte, tots els nous CPLD ATF15xx s'envien amb el JTAG interfície activada. Un cop els recursos lògics per a JTAG La interfície està reservada, els usuaris poden programar, verificar i esborrar qualsevol CPLD ATF15xx a la placa de destinació mitjançant el programari ATMISP.

Consell: Tot i que els quatre JTAG els pins estan reservats per a un JTAG interfície, els usuaris poden implementar funcions lògiques enterrades a les macrocel·les associades a aquests pins.

Taula 3-1 ATF15xx CPLD JTAG Números de pins

| JTAG Pin | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Activa JTAG Interfície amb WinCUPL

Per habilitar el JTAG interfície amb WinCUPL, cal especificar el tipus de dispositiu ISP ATF15xx adequat abans de compilar un disseny. Després de compilar un disseny amb èxit, un JEDEC file amb el JTAG es genera la funció de la interfície activada. Quan aquest JEDEC file està programat en un ATF15xxCPLD, el seu JTAG la interfície està habilitada. Els usuaris també poden habilitar les resistències de pull-up internes TDI i TMS mitjançant la inclusió de les declaracions de propietat següents al disseny CUPL file.

- PROPIETAT ATMEL {TDI_PULLUP = ON};

- PROPIETAT ATMEL {TMS_PULLUP = ON};

Avís: Si s'utilitza un tipus de dispositiu ISP ATF15xx per a un disseny que utilitza el JTAG pins d'interfície com a pins d'E/S lògics, WinCUPL genera un error.

Els passos següents expliquen com obrir un disseny existent a WinCUPL, especificar el tipus de dispositiu i compilar el disseny.

- Al menú principal de WinCUPL, seleccioneu File > Obre. Seleccioneu la font CUPL (.pld). file des del directori de treball corresponent.

- Seleccioneu D'acord per obrir la font PLD file.

- Al menú principal de WinCUPL, seleccioneu File > Desa. Això desa els canvis fets a la font file.

- Al menú principal, seleccioneu Opcions > Dispositius. Això obre el quadre de diàleg Selecció de dispositiu.

- Trieu el dispositiu ISP ATF15xx adequat. Consulteu la taula següent per obtenir una llista de tots els tipus de dispositius ATF15xx compatibles amb WinCUPL.

- Seleccioneu D'acord per tancar el menú de selecció del dispositiu.

- Nota: Un mètode alternatiu és triar un tipus de dispositiu ATF15xx adequat de la taula següent i incloure-lo a la secció de capçalera de la font CUPL file.

- Al menú principal de WinCUPL, seleccioneu Executar> Compilació dependent del dispositiu.

- WinCUPL compila el disseny i genera l'ajustador de dispositius Atmel. Si el disseny encaixa, un JEDEC file es crea automàticament.

- Quan la JEDEC file està programat al dispositiu, el JTAG interfície, els pull-ups interns opcionals de TMS i TDI i els circuits de pin-keeper opcionals estan habilitats.

Nota: Si seleccioneu un tipus de dispositiu ISP d'Atmel, s'activa automàticament el dispositiu JTAG interfície per defecte quan Atmel WinCUPL executa l'ajustador de dispositius Atmel.

Si els dissenys impedeixen reservar recursos per a JTAG interfície o un ISP opcionalment no s'utilitza, cal seleccionar un tipus de dispositiu Atmel que no sigui ISP. Consulteu la taula següent per obtenir una llista de dispositius. Aleshores, el dispositiu es pot reprogramar mitjançant un programador de dispositiu extern. La taula següent enumera els tipus de dispositius Atmel ISP i Atmel no ISP per a WinCUPL.

Taula 3-2 Tipus de dispositiu WinCUPL ATF15xx

| Nom del dispositiu | Tipus de paquet | Tipus de dispositiu WinCUPL | |

| JTAG Habilitat | JTAG Inhabilitat | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Activa JTAG Interfície amb Atmel ProChip Designer

Per habilitar el JTAG interfície amb ProChip Designer:

- Obriu el projecte ProChip Designer adequat.

- Obriu la finestra Opcions de l'ajustador fent clic al botó Atmel Fitter a sota de l'ajustador de dispositius.

- Seleccioneu la pestanya Dispositiu global i, a continuació, comproveu JTAG Caixa del port. Les resistències de pull-up internes TMS i TDI també es poden activar marcant les caselles TDI Pullup i TMS Pullup. Aquestes caselles de verificació es mostren a la figura següent.

Figura 3-1 Interfície d'usuari d'opcions de l'ajustador del dissenyador de ProChip

Activa JTAG Interfície amb POF2JED

A POF2JED, el JTAG L'opció de mode es pot configurar a Automàtic per permetre que POF2JED determini si el JTAG La funció de l'ATF15xx hauria d'estar activada o no, i es basa en si JTAG és compatible amb el CPLD del competidor. Per activar JTAG al CPLD ATF15xx independentment de si JTAG és compatible o no al CPLD del competidor, el JTAG L'opció de mode ha d'estar activada. Quan JTAG està habilitat a l'ATF15xx, les resistències d'extracció internes TDI i TMS es poden habilitar marcant l'opció Habilita

TDI_PULLUP i Habilita les caselles TMS_PULLUP a POF2JED. Vegeu la figura següent.

Figura 3-2 Interfície d'usuari de POF2JED

Directrius i recomanacions

Atenció: Cal prestar una atenció especial a aquesta secció quan es realitzen operacions d'ISP en CPLD ATF15xx. Aquesta secció tracta alguns dels JTAG Directrius, informació i recomanacions de l'ISP que cal tenir en compte.

- Assegureu-vos que el JTAG port per a tots els dispositius del JTAG cadena estan habilitades.

- Per als CPLD ATF15xx, el JTAG El port està habilitat si els dispositius estan en blanc/esborrats o programats amb JTAG habilitat.

- Tots els dispositius Atmel ATF15xx s'envien en blanc/esborrat; per tant, el JTAG El port està habilitat per a tots els dispositius nous i llest per a ISP.

- Dispositius ATF15xx amb JTAG desactivats s'han d'esborrar mitjançant un programador de dispositius que no sigui ISP per tornar a habilitar el JTAG port.

- Assegureu-vos que el VCC voltage s'aplica a cadascun dels dispositius de JTAG cadena.

- CPLD ATF15xxAS/ASL als tipus de paquet 84-PLCC, 100-TQFP i 100-PQFP: VCCINT ha d'estar entre 4.5 V i 5.5 V mentre que VCCIO pot estar entre 3.0 V i 3.6 V o 4.5 V i 5.5 V.

- CPLD ATF15xxAS/ASL en tipus de paquet 44-PLCC i 44-TQFP: VCC ha d'estar entre 4.5 V i 5.5 V.

- CPLD ATF15xxASV/ASVL: VCC (VCCIO i VCCINT) ha d'estar entre 3.0 V i 3.6 V.

- El VCC per als dispositius de JTAG la cadena s'ha de regular i filtrar adequadament.

- Per als CPLD ATF15xx utilitzats en la majoria d'aplicacions, es recomana utilitzar un condensador de desacoblament de 0.22 µF per a cadascun dels parells VCC/GND.

- Es recomana utilitzar un punt comú per a tots els dispositius de JTAG cadena i el JTAG maquinari d'interfície (és a dir, cable de baixada ATDH1150USB ISP).

- Es recomana evitar llargs (no més de cinc dispositius) JTAG cadenes.

- Si un llarg JTAG És necessària una cadena, tamponeu els senyals TMS i TCK després de cada cinquè dispositiu. Es prefereix l'ús de la memòria intermèdia d'activació de Schmitt.

- Els buffers remodelen els temps de pujada i baixada dels senyals TMS i TCK.

- Cal tenir en compte el retard addicional causat pels buffers.

- Es recomana utilitzar resistències pull-up (4.7KΩ a 10KΩ) per als senyals TMS i TDI i una resistència pull-down per al senyal TCK a la J.TAG capçalera per evitar que aquests senyals flotin quan no els controla el maquinari de la interfície.

- Els pull-ups interns opcionals a TMS i TDI estan disponibles per als CPLD ATF15xx.

- Es recomana acabar amb JTAG senyals a la JTAG capçalera.

- Tant les terminacions actives com les passives són acceptables; no obstant això, es prefereix la terminació passiva.

- Redueix el timbre a causa de les llargues longituds de traça de cable/PCB.

- La terminació és la més crítica per a TMS i TCK.

- Es recomana que totes les entrades i E/S dels dispositius de JTAG cadena, excepte la JTAG pins, haurien d'estar en estat estàtic quan s'estan programant els CPLD ATF15xx per minimitzar el soroll.

- Quan utilitzeu una de les plaques de desenvolupament/programador Atmel ATF15xx, l'alimentació de la placa s'ha d'apagar quan es canvien les posicions dels ponts de selecció VCC.

- Per als CPLD ATF15xx, JTAG L'ISP està disponible quan la peça està en mode d'apagada controlada per pins o quan el dispositiu de "baixa potència" està adormit.

- Estat del dispositiu després de la interrupció de l'ISP:

- Si s'interromp l'ISP, tots els pins d'E/S tenen tres estats independentment de l'estat dels circuits de pin-keeper.

- Impedeix que els dispositius parcialment programats ocasionin conflictes de bus amb altres dispositius de la placa de circuit.

- Durant la programació de l'ISP, tots els pins d'E/S es troben en una de les condicions següents:

- Estat d'alta impedància:

- Quan es programa un dispositiu en blanc/esborrat.

- Quan es reprograma un dispositiu amb els circuits Pin-keeper desactivats.

- Evita la contenció de bus amb dispositius externs que s'interfaça amb els CPLD ATF15xx de la placa de circuit.

- Feblement enganxat a l'estat anterior:

- Quan es torna a programar un dispositiu programat amb els circuits Pin-keeper activats.

- Els pins d'E/S mantenen els nivells lògics anteriors a l'ISP.

- Evita que l'ISP afecti el funcionament d'altres dispositius de la placa base.

- L'ús de múltiples JTAG no es recomana cadenes en un tauler.

- Els dispositius poden interactuar entre diferents JTAG cadenes.

- El tauler només funciona quan tots els dispositius de tots els dispositius JTAG les cadenes es programen correctament.

- Si la programació falla per almenys un dispositiu d'una cadena mentre que un altre JTAG les cadenes es van programar amb èxit:

- Tant l'Atmel com altres dispositius a bord es poden danyar a causa d'un possible problema de contenció del bus per a sortides tri-estatables.

- L'estat operatiu de la placa del sistema no està definit; i per tant, es pot produir l'operació funcional incorrecta.

- Inserció de circuits actius entre JTAG capçalera i el JTAG no es recomana dispositius en cadena. Si el circuit actiu funciona malament, pot causar problemes de programació/verificació.

- L'ús de mixed-voltagEl dispositiu JTAG no es recomana cadenes.

- Aquests són JTAG cadenes amb dispositius que utilitzen diferents VCC voltages i/o interfície voltages.

- Interfície voltagEls nivells e (VIL, VIH, VOL, VOH) per a dispositius de 5.0 V poden no ser compatibles amb la interfície voltagnivells e per a dispositius de 3.0 V.

- Si ATMISP té problemes per comunicar-se amb el JTAG cadena de maquinari del dispositiu, proveu d'executar Self Calibrate o Manually Calibrate per reduir les freqüències del JTAG senyals.

- Assegureu-vos que el LED del cable ATDH1150USB estigui encès i que estigui verd abans de començar la programació. Assegureu-vos que el cable de descàrrega de l'ISP es pugui comunicar correctament amb el programari ATMISP.

- Assegureu-vos que el VCC voltage s'aplica al cable ATDH1150USB.

- El VCC utilitzat pel primer dispositiu de JTAG La cadena s'ha de subministrar al cable ATDH1150USB a través del pin 4 del connector J de 10 pins.TAG capçalera.

- Per als CPLD ATF15xx amb VCCINT i VCCIO separats, s'ha d'utilitzar VCCIO per al cable ATDH1150USB.

Informació de comanda

| Codi de comanda | Descripció |

| ATF15xx-DK3-U | Kit de desenvolupament/programador CPLD (inclou ATF15xxDK3-SAA44 i ATDH1150USB o ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | Placa adaptadora de presa TQFP de 100 pins per a placa DK3 |

| ATF15xxDK3-SAJ44 | Placa adaptadora de sòcol PLCC de 44 pins per a placa DK3 |

| ATF15xxDK3-SAJ84 | Placa adaptadora de sòcol PLCC de 84 pins per a placa DK3 |

| ATF15xxDK3-SAA44 | Placa adaptadora de presa TQFP de 44 pins per a placa DK3 |

| ATDH1150USB | Atmel ATF15xx CPLD basat en USB JTAG Cable de descàrrega de l'ISP |

Historial de revisions

| Doc. Rev. | Data | Comentaris |

| A | 12/2015 | Lliurament del document inicial. |

INFORMACIÓ DE CONTACTE

Corporació Atmel

- 1600 Technology Drive, San Jose, CA 95110 EUA

- Telèfon: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_Guia de l'usuari-12/2015

Atmel®, el logotip d'Atmel i les seves combinacions, Enabling Unlimited Possibilities® i altres són marques registrades o marques comercials d'Atmel Corporation als EUA i altres països. Altres termes i noms de productes poden ser marques comercials d'altres.

EXENCIÓ DE RESPONSABILITAT: La informació d'aquest document es proporciona en relació amb els productes Atmel. No s'atorga cap llicència, expressa o implícita, per preclusió o d'una altra manera, a cap dret de propietat intel·lectual en aquest document o en relació amb la venda de productes Atmel. EXCEPTE EL QUE ESTABLECTE ALS TERMES I CONDICIONS DE VENDA D'ATMEL UBICATS A L'ATMEL WEBLLOC, ATMEL NO ASSUMIR RESPONSABILITAT I RENUNCIA A QUALSEVOL GARANTIA EXPLÍCITA, IMPLÍCITA O LEGAL RELACIONADA AMB ELS SEUS PRODUCTES, INCLOSA, PERÒ NO LIMITATIVAMENT, LA GARANTIA IMPLÍCITA DE COMERCIABILITAT, IDONEIDAD PER A UN FINS NO PARTICULAR, INFECCIÓ. EN CAP CAS ATMEL SERÀ RESPONSABLE DE CAP DANYS DIRECTS, INDIRECTS, CONSEQUENTLS, PUNITIUS, ESPECIALS O INCIDENTALS (INCLOSOS, SENSE LIMITACIÓ, DANYS PER PÈRDUES I BENEFICIS, INTERRUPCIÓ DEL NEGOCI O PÈRDUA D'INFORMACIÓ) QUE SORRIREN DE LA CAPACITAT D'UTILIZAR-SE PER A LA UTILITZACIÓ. ATMEL S'HA AVISAT DE LA POSSIBILITAT D'AQUESTS DANYS. Atmel no fa representacions ni garanteix respecte a l'exactitud o la integritat del contingut d'aquest document i es reserva el dret de fer canvis a les especificacions i descripcions dels productes en qualsevol moment sense previ avís. Atmel no es compromet a actualitzar la informació aquí continguda. Llevat que s'especifiqui el contrari, els productes Atmel no són adequats ni s'han d'utilitzar en aplicacions d'automoció. Els productes Atmel no estan pensats, autoritzats o garantits per utilitzar-los com a components en aplicacions destinades a donar suport o mantenir la vida. EXENCIÓ DE RESPONSABILITAT D'APLICACIONS CRÍTIQUES PER A LA SEGURETAT, MILITARS I AUTOMOTRIUS: els productes Atmel no estan dissenyats ni s'utilitzaran en relació amb cap aplicació en què s'espera raonablement que el fracàs d'aquests productes provoqui lesions personals importants o la mort ("Aplicacions crítiques per a la seguretat") sense el consentiment específic per escrit d'un oficial d'Atmel. Les aplicacions crítiques per a la seguretat inclouen, sense limitació, dispositius i sistemes de suport vital, equips o sistemes per al funcionament d'instal·lacions nuclears i sistemes d'armes. Els productes d'Atmel no estan dissenyats ni dissenyats per utilitzar-los en aplicacions o entorns militars o aeroespacials tret que Atmel els designi específicament com a grau militar. Els productes d'Atmel no estan dissenyats ni destinats a utilitzar-se en aplicacions d'automoció, tret que Atmel els designi específicament com a qualitat d'automoció.

Documents/Recursos

|

Dispositiu lògic programable complex Atmel ATF15xx [pdfGuia de l'usuari ATF15xx, ATF15xx Dispositiu lògic programable complex, Dispositiu lògic programable complex, Dispositiu lògic programable, Dispositiu lògic, Dispositiu |