Atmel ATF15xx 复杂可编程逻辑器件

规格

- 产品名称:Atmel ATF15xx 在系统编程

- 型号:ATF15xx

- 类型:复杂可编程逻辑器件 (CPLD)

- 编程方法:在系统编程(ISP)

- 接口:JTAG ISP 接口

- 制造商:Atmel

常见问题解答

问:我可以将第三方编程软件与 ATF15xx CPLD 一起使用吗?

答:是的,只要软件支持编程算法和JTAG ATF15xx CPLD 所需的指令。

问:是否可以同时对多个 ATF15xx CPLD 进行编程?

答:是的,JTAG ISP 接口支持多设备编程,可以同时高效地对多个 CPLD 进行编程。

介绍

- 采用逻辑倍增® 架构的 Atmel® ATF15xx 复杂可编程逻辑器件 (CPLD) 支持通过 IEEE 标准 1149.1 联合测试行动组 (JTAG) 接口。此功能增强了编程灵活性,并在产品开发、生产和现场使用等各个阶段提供了好处。本用户指南介绍了在具有 ISP 支持的 ATF15xx CPLD 上实现 ISP 的设计方法和要求,如下所示:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

特点和优点

在系统编程允许在将 ISP 设备安装到印刷电路板 (PCB) 上之后对其进行编程和重新编程。这消除了制造过程中在将设备安装到 PCB 上之前在外部设备编程器上对设备进行编程所需的额外处理步骤。消除此步骤可降低在编程流程中损坏高引脚数表面贴装设备的精密引线或通过静电放电 (ESD) 损坏设备的可能性。ISP 还允许用户进行设计更改和现场升级,而无需从 PCB 上移除 ISP 设备。此外,它还允许使用嵌入式微控制器或在线测试器对 ISP 设备执行在系统编程操作,并将这些编程操作集成到电路板的生产流程中。

在系统编程系统

ATF15xx CPLD 的 ISP 系统的三个基本组件是:

软件

编程算法的实现,以及J的生成TAG 目标 ISP 设备的指令和数据。这可以是在 PC、嵌入式微控制器或在线测试设备上运行的软件程序。

接口硬件

ISP 软件与目标板上的 ISP 设备之间的通信通道。这可以是 Atmel 或第三方供应商的 ISP 下载电缆或编程器、在线测试设备,或嵌入式微控制器与 PCB 上的 ISP 设备之间的连接

目标板

包含J中的ISP设备的电路板TAG 链。这可以是 Atmel 的 ATF15xx CPLD 开发/编程器板,也可以是带有适当 JTAG 到接口硬件的连接。

除了这三个组件之外,JEDEC file 是编程 ATF15xx CPLD 所必需的。此 JEDEC file 可以通过编译设计来创建 file 使用支持 ATF15xx CPLD 的开发软件,如 Atmel WinCUPL 和 Atmel ProChip Designer。Atmel 还提供了一个转换器软件实用程序 POF2JED.exe,可将输出转换为 file 从竞争对手的编程格式到 JEDEC file 与 ATF15xx CPLD 兼容。有关此实用程序的更多信息,请参阅 Atmel 应用说明“ATF15xx 产品系列转换”,可在 Atmel web网站。在 JEDEC file为所有 ATF15xx CPLD 创建,它们可以在目标板上进行编程。ATF15xx CPLD 可以通过以下系统内编程系统进行编程:

- ATF15xx 在系统编程系统

- 嵌入式微控制器

- 在线测试仪

Atmel ATF15xx 在系统编程系统

对于 ATF15xx CPLD 的系统内编程,Atmel 提供了 ISP 软件、下载电缆和开发/编程器套件,并在以下章节中进行了介绍。

ISP 软件

Atmel ATF15xx ISP 软件 ATMISP 是实现 JTAG 在 ATF15xx CPLD 上进行系统内编程。 ATMISP 在基于 Windows 的主机 PC 上运行,并在目标 ISP 硬件系统上实现 ATF15xx CPLD 的系统内编程或生成串行矢量格式 (.SVF) file 供自动测试设备 (ATE) 使用,用于在目标系统上对 ATF15xx CPLD 进行编程。 ATMISP 首先从用户那里获取有关 JTAG 目标系统中的设备链。然后执行适当的 JTAG ISP 指令到 JTAG 目标系统中的设备链根据JTAG 用户通过 PC 的 USB 或 LPT 端口指定的设备链信息。有关 Atmel ATMISP 软件的更多信息,请访问 www.atmel.com/tools/ATMISP.aspx.

ISP下载线

Atmel ATF15xx USB ISP 下载电缆 ATDH1150USB 一端连接到主机的标准 USB 端口,另一端连接到 JTAG 另一侧的目标电路板的头部。它将 JTAG 将主机 PC 上运行的 ATMISP 生成的指令和数据传输到目标电路板上的 ISP 设备。有关 ATDH1150USB 电缆的更多信息,请访问 www.atmel.com/tools/ATDH1150USB.aspx.

开发/程序员

Atmel ATF15xx 开发/编程器套件 ATF15xx-DK3-U 是一个完整的开发系统和 ATF15xx CPLD 的 ISP 编程器。该套件为设计人员提供了一种非常快速简便的方法来开发原型并评估使用 ATF15xx ISP CPLD 的新设计。由于可以使用不同的插座适配器板来支持 ATF15xx CPLD 中提供的大多数封装类型,因此该套件可用作 ISP 编程器,通过 J 对大多数可用封装类型的 ATF15xx ISP CPLD 进行编程TAG 接口。有关 Atmel ATF15xx-DK3-U 套件的更多信息,请访问 www.atmel.com/tools/ATF15XX-DK3-U.aspx.

嵌入式微控制器系统

规划算法与JTAG 可以在微控制器或微处理器中实现 ATF15xx CPLD 的指令,然后可以使用这些指令对目标板上的 ATF15xx CPLD 进行编程。一种可能的方法是提取所有相关的 JTAG 协议信息(即 JTAG SVF 发送的指令和数据 file 由 ATMISP 软件生成的,然后使用此信息为微控制器或微处理器实现生成 JTAG J 中的 ISP 设备信号TAG 链。这种方法最适合已经具有嵌入式微控制器或微处理器的系统,这样就无需使用外部系统内编程软件和硬件工具。

在线测试系统

ATF15xx CPLD 可通过 JTAG 在使用在线测试仪测试电路板时,可以使用 SVF 接口。通常,SVF file ATMISP 生成的应包含所有相关的 JTAG 在系统编程信息,在线测试人员需要对目标电路板上的 ATF15xx CPLD 进行编程。这种方法允许将编程步骤集成到测试系统中tag生产流程的 e。

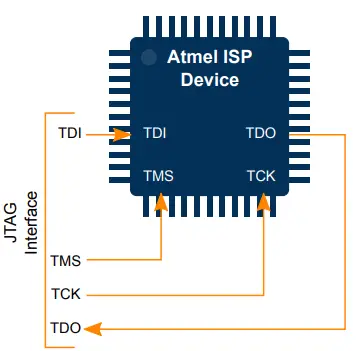

JTAG ISP 接口

ATF15xx CPLD 的 ISP 是使用 IEEE 1149.1 Std. J 实现的TAG 接口。此接口可用于擦除、编程和验证 ATF15xx CPLD。JTAG 接口是一个串行接口,由TCK、TMS、TDI、TDO信号和JTAG 测试访问端口 (TAP) 控制器。TCK 引脚是 JTAG TAP 控制器并移入/移出 JTAG 指令和数据。TDI 引脚是串行数据输入。它用于将编程指令和数据移入 ISP 设备。TDO 引脚是串行数据输出。它用于将数据从 ISP 设备移出。TMS 引脚是模式选择引脚。它控制 JTAG TAP 控制器。JTAG ISP 目标板上的 ATF15xx CPLD 的接口引脚必须通过 10 针接头连接到 ISP 接口硬件(即 ISP 下载电缆)。ISP 接口硬件还需要连接到运行 ISP 软件的主机 PC。ISP 接口硬件在 ISP 软件和 ISP 设备之间建立通信,并允许 ISP 软件将编程指令和数据从主机 PC 传输到 ATF15xx CPLD。带有 JTAG 已启用的功能完全 JTAG 兼容,并支持J中规定的所需边界扫描测试(BST)操作TAG 标准。ATF15xx CPLD 可以配置为 JTAG 与其他 J 的 BST 链TAG 设备用于系统板的在线测试。借助此功能,ATF15xx CPLD 可以与其他 JTAG- 支持的设备,无需进行钉床测试。

单设备编程

JTAG ISP 接口可以配置为对单个 ATF15xx CPLD 进行编程。JTAG 下图显示了单个设备的配置。当以这种方式配置 ATF15xx CPLD 时,设备的 TDI 和 TDO 引脚之间会出现一个寄存器。寄存器的大小取决于 JTAG 指令宽度和该指令移入的数据。图 2-1 JTAG 设备

多设备编程

ATF15xx CPLD 可以配置为多个 JTAG- 支持的设备如下所述,如下图所示。

- 连接 J 中每个设备的 TMS 和 TCK 引脚TAG 链到J的TMS和TCK引脚TAG 电路板上的接口接头。

- 将第一个设备的 TDI 引脚连接到 JTAG 接口头。

- 将第一个设备的 TDO 引脚连接到下一个设备的 TDI 引脚。继续此过程,直到除最后一个引脚外所有引脚都连接完毕。

- 将最后一个设备的 TDO 引脚连接到 JTAG 接口头。

图 2-2 多设备 JTAG 配置

在 J 中对多个设备进行编程TAG 链,用户必须使用支持此类功能的 ISP 软件工具。在 ISP 软件中,用户需要指定:

- J 中的设备数量TAG 链。

- 设备的部件编号和 J 内的位置TAG 链。

- JTAG 对每个设备执行的操作。

- 其他TAG相关信息,如 JTAG 每个设备的指令宽度。

一旦 JTAG 在 ISP 目标板和 ISP 软件中正确设置菊花链后,JTAG 可以同时对多个链进行编程。

设计考虑

要在 ATF15xx CPLD 上执行 ISP,JTAG ATF15xx 接口必须保留。因此,必须为 JTAG 不能用作用户 I/O。这些引脚的引脚号取决于所用的 ATF15xx CPLD 及其封装类型。请参阅下表了解引脚分布信息。JTAG 标准建议将 JTAG 链。ATF15xx CPLD 具有针对这些引脚的内部上拉功能,启用后,无需使用外部上拉电阻。此外,JTAG 必须启用接口功能才能在 ATF15xx CPLD 上执行 ISP。启用 JTAG 接口需要在编译 ATF15xx 设计之前选择特定的 Atmel 设备类型或选项设置。本指南针对 WinCUPL、ProChip Designer 和 POF2JED 概述了这些程序。默认情况下,所有全新的 ATF15xx CPLD 都附带 JTAG 接口启用。一旦逻辑资源为 JTAG 接口被保留,用户可以使用ATMISP 软件对目标板上的任何ATF15xx CPLD 进行编程、验证和擦除。

提示:虽然四个 JTAG 引脚保留用于 JTAG 接口,用户可以在与这些引脚相关的宏单元中实现埋藏的逻辑功能。

表 3-1 ATF15xx CPLD JTAG 针号

| JTAG 别针 | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| 甲苯二异氰酸酯 | 1 | 7 | 14 | 4 | 6 |

| 时差 | 32 | 38 | 71 | 73 | 75 |

| 经颅磁共振 | 7 | 13 | 23 | 15 | 17 |

| 中枢肌钙蛋白 | 26 | 32 | 62 | 62 | 64 |

启用 JTAG 与 WinCUPL 接口

要启用 JTAG 与 WinCUPL 接口,在编译设计之前需要指定适当的 ATF15xx ISP 设备类型。设计成功编译后,JEDEC file 与 JTAG 接口功能已启用时生成。当此 JEDEC file 被编程到ATF15xxCPLD中,它的JTAG 接口已启用。用户还可以通过在 CUPL 设计中包含以下属性语句来启用 TDI 和 TMS 内部上拉电阻 file.

- 属性ATMEL {TDI_PULLUP = ON};

- 属性 ATMEL {TMS_PULLUP = ON};

注意:如果 ATF15xx ISP 设备类型用于使用 JTAG 接口引脚作为逻辑 I/O 引脚,WinCUPL 会产生错误。

以下步骤讨论如何在 WinCUPL 中打开现有设计、指定设备类型以及编译设计。

- 在 WinCUPL 主菜单上,选择 File > 打开。选择 CUPL (.pld) 源 file 从适当的工作目录。

- 选择OK打开PLD源 file.

- 在 WinCUPL 主菜单上,选择 File > 保存。这将保存对源所做的更改 file.

- 在主菜单上,选择选项 > 设备。这将打开设备选择对话框。

- 选择适当的 ATF15xx ISP 设备。请参阅下表,了解 WinCUPL 支持的所有 ATF15xx 设备类型的列表。

- 选择“确定”关闭设备选择菜单。

- 注意:另一种方法是从下表中选择合适的 ATF15xx 设备类型,并将其包含在 CUPL 源的标头部分中 file.

- 在 WinCUPL 主菜单上,选择运行 > 设备相关编译。

- WinCUPL 编译设计并生成 Atmel 设备适配器。如果设计符合要求,则 JEDEC file 是自动创建的。

- 当 JEDEC file 被编程到设备中,JTAG 接口、可选的内部 TMS 和 TDI 上拉电阻以及可选的引脚保持电路均已启用。

笔记:选择 Atmel ISP 设备类型会自动启用 JTAG 当 Atmel WinCUPL 运行 Atmel 设备适配器时,默认使用接口。

如果设计阻止为 J 保留资源TAG 如果不使用 ISP 接口或 ISP,则必须选择 Atmel 非 ISP 设备类型。请参阅下表了解设备列表。然后可以使用外部设备编程器对设备进行重新编程。下表列出了 WinCUPL 的 Atmel ISP 和 Atmel 非 ISP 设备类型。

表 3-2 WinCUPL ATF15xx 设备类型

| 设备名称 | 封装类型 | WinCUPL 设备类型 | |

| JTAG 已启用 | JTAG 已禁用 | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

启用 JTAG 与 Atmel ProChip Designer 接口

要启用 JTAG 与 ProChip Designer 的接口:

- 打开适当的 ProChip Designer 项目。

- 单击 Device Fitter 下的 Atmel Fitter 按钮,打开 Fitter Options 窗口。

- 选择“全局设备”选项卡,然后选中 JTAG 端口框。还可以通过选中 TDI Pullup 和 TMS Pullup 框来启用 TMS 和 TDI 内部上拉电阻。这些复选框如下图所示。

图 3-1 ProChip Designer Fitter 选项用户界面

启用 JTAG 与 POF2JED 接口

在 POF2JED 中,JTAG 模式选项可以设置为自动,让 POF2JED 确定 JTAG ATF15xx 中的功能是否应启用,这取决于 JTAG 竞争对手的 CPLD 也支持此功能。要打开 JTAG 在ATF15xx CPLD中,无论JTAG 无论竞争对手的 CPLD 是否支持该功能,JTAG 模式选项应设置为开。当TAG 在ATF15xx中启用,可以通过选中启用

POF2JED 中的 TDI_PULLUP 和 Enable TMS_PULLUP 框。参见下图。

图 3-2 POF2JED 用户界面

准则和建议

注意力:在 ATF15xx CPLD 上执行 ISP 操作时,应特别注意本节。本节讨论了一些 JTAG 需要注意的 ISP 指南、信息和建议。

- 确保 JTAG J 中的所有设备的端口TAG 链已启用。

- 对于 ATF15xx CPLD,JTAG 如果设备为空白/擦除或用 J 编程,则端口启用TAG 已启用。

- 所有 Atmel ATF15xx 设备都是以空白/已擦除状态发货的;因此,JTAG 所有全新设备均已启用端口并可供 ISP 使用。

- 带有 J 的 ATF15xx 设备TAG 禁用需要使用非ISP设备编程器擦除以重新启用JTAG 港口。

- 确保正确的VCC音量tage 应用于 J 中的每个设备TAG 链。

- 15-PLCC、84-TQFP 和 100-PQFP 封装类型的 ATF100xxAS/ASL CPLD:VCCINT 必须介于 4.5V 和 5.5V 之间,而 VCCIO 可以介于 3.0V 和 3.6V 或 4.5V 和 5.5V 之间。

- 15-PLCC 和 44-TQFP 封装类型的 ATF44xxAS/ASL CPLD:VCC 必须在 4.5V 至 5.5V 之间。

- ATF15xxASV/ASVL CPLD:VCC(VCCIO 和 VCCINT)必须在 3.0V 至 3.6V 之间。

- J 中的设备的 VCCTAG 链必须得到适当的调节和过滤。

- 对于大多数应用中使用的 ATF15xx CPLD,建议为每个 VCC/GND 对使用一个 0.22µF 去耦电容。

- 建议对 J 中的所有设备使用一个公共接地TAG 链和 JTAG 接口硬件(即ATDH1150USB ISP下载线)。

- 建议避免长时间(不超过五个设备)JTAG 鏈。

- 如果长 JTAG 需要链,每五个设备后缓冲 TMS 和 TCK 信号。最好使用施密特触发器缓冲器。

- 缓冲器重塑 TMS 和 TCK 信号的上升和下降时间。

- 需要考虑缓冲区产生的额外延迟。

- 建议在 J 端对 TMS 和 TDI 信号使用上拉电阻(4.7KΩ 至 10KΩ),对 TCK 信号使用下拉电阻。TAG 接头以防止这些信号在未被接口硬件驱动时浮动。

- TMS 和 TDI 上的可选内部上拉电阻可用于 ATF15xx CPLD。

- 建议终止JTAG J 处的信号TAG 標軸。

- 主动和被动终止都是可以接受的;然而,被动终止是首选。

- 它可减少因长电缆/PCB 走线长度而引起的振铃。

- 终止对于 TMS 和 TCK 来说最为关键。

- 建议 J 中的所有设备的输入和 I/OTAG 链条,J 型除外TAG 在对 ATF15xx CPLD 进行编程时,引脚应处于静态,以尽量减少噪音。

- 当使用 Atmel ATF15xx 开发/编程器板之一时,在更改 VCC 选择跳线的位置时必须关闭该板的电源。

- 对于 ATF15xx CPLD,JTAG 当部件处于引脚控制的断电模式或“低功耗”设备处于睡眠状态时,ISP 可用。

- ISP中断后设备状态:

- 如果 ISP 中断,则无论引脚保持器电路的状态如何,所有 I/O 引脚都将处于三态。

- 防止部分编程的设备与电路板上的其他设备发生总线争用。

- 在 ISP 编程期间,所有 I/O 引脚都处于下列状态之一:

- 高阻状态:

- 当对空白/已擦除的设备进行编程时。

- 当对设备进行重新编程并且引脚保持电路被禁用时。

- 防止与电路板上的 ATF15xx CPLD 接口的外部设备发生总线争用。

- 弱锁定到先前的状态:

- 当已编程的设备在引脚保持电路启用的情况下被重新编程时。

- I/O 引脚保持 ISP 之前的逻辑电平。

- 防止 ISP 影响系统板上其他设备的运行。

- 使用多个 JTAG 不建议在一块板上安装链条。

- 设备之间可能会发生交互TAG 鏈。

- 仅当所有 J 中的所有设备都处于活动状态时,电路板才起作用TAG 链编程成功。

- 如果链中至少一个设备的编程失败,而其他 JTAG 链已成功编程:

- 由于三态输出可能存在总线争用问题,Atmel 或板上的其他设备都可能被损坏。

- 系统板的运行状态未定义;因此,可能会发生错误的功能操作。

- 在 J 之间插入有源电路TAG 标题和 JTAG 不建议将器件串联起来。如果有源电路发生故障,可能会导致编程/验证问题。

- 使用混合卷tag设备 JTAG 不建议使用链条。

- 这些是 JTAG 与使用不同VCC卷的设备链tages 和/或接口卷tag西。

- 接口卷tag5.0V 设备的电平(VIL、VIH、VOL、VOH)可能与接口电压不兼容tag3.0V 设备的 e 级别。

- 如果 ATMISP 与 J 通信时出现问题TAG 设备硬件链,尝试运行自我校准或手动校准以降低 J 的频率TAG 信號。

- 编程开始前,请确保 ATDH1150USB 电缆上的 LED 亮起且为绿色。确保 ISP 下载电缆能够与 ATMISP 软件正确通信。

- 确保正确的VCC音量tage 适用于 ATDH1150USB 电缆。

- J 中第一个设备使用的 VCCTAG 必须通过 1150 针 J 形电缆的针脚 4 为 ATDH10USB 电缆供电TAG 標軸。

- 对于具有独立 VCCINT 和 VCCIO 的 ATF15xx CPLD,应将 VCCIO 用于 ATDH1150USB 电缆。

订购信息

| 订购代码 | 描述 |

| ATF15xx-DK3-U | CPLD 开发/编程器套件(包括 ATF15xxDK3-SAA44 和 ATDH1150USB 或 ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | 用于 DK100 板的 3 针 TQFP 插座适配器板 |

| ATF15xxDK3-SAJ44 | 用于 DK44 板的 3 针 PLCC 插座适配器板 |

| ATF15xxDK3-SAJ84 | 用于 DK84 板的 3 针 PLCC 插座适配器板 |

| ATF15xxDK3-SAA44 | 用于 DK44 板的 3 针 TQFP 插座适配器板 |

| ATDH1150USB | Atmel ATF15xx CPLD 基于 USB 的 JTAG ISP下载线 |

修订历史

| 博士。 牧师 | 日期 | 评论 |

| A | 12/2015 | 初始文件发布。 |

联系信息

爱特梅尔公司

- 1600 Technology Drive, 圣何塞, CA 95110 美国

- 电话:(+1)(408) 441.0311

- 女:(+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel 公司。/ 修订版:Atmel-8968A-CPLD-ATF-ISP_用户指南-12 年 2015 月

Atmel®、Atmel 徽标及其组合、Enabling Unlimited Possibilities® 等是 Atmel Corporation 在美国和其他国家/地区的注册商标或商标。其他术语和产品名称可能是其他公司的商标。

免责声明:本文档中的信息与 Atmel 产品有关。 本文档或与爱特梅尔产品的销售有关的任何知识产权均未通过禁止反言或其他方式授予任何明示或暗示的许可。 位于 ATMEL 上的销售条款和条件中规定的除外 WEB网站,ATMEL 不承担任何责任并且否认与其产品有关的任何明示、暗示或法定的保证,包括但不限于适销性、针对特定用途的适用性或非侵权性的暗示保证。在任何情况下,ATMEL 均不对因使用或无法使用本文档而导致的任何直接、间接、后果性、惩罚性、特殊或偶发性损害(包括但不限于利润损失、业务中断或信息丢失)负责,即使 ATMEL 已被告知存在此类损害的可能性。Atmel 对本文档内容的准确性或完整性不作任何陈述或保证,并保留随时更改规格和产品说明的权利,恕不另行通知。Atmel 不承诺更新此处包含的信息。除非另有明确规定,否则 Atmel 产品不适用于汽车应用,也不得用于汽车应用。 Atmel 产品并非旨在、授权或保证用作支持或维持生命的应用中的组件。安全关键、军事和汽车应用免责声明:未经 Atmel 官员的明确书面同意,Atmel 产品并非设计用于且不会用于任何此类产品故障可合理预期会导致严重人身伤害或死亡的应用(“安全关键应用”)。安全关键应用包括但不限于生命支持设备和系统、用于核设施和武器系统的设备或系统。除非 Atmel 明确指定为军用级,否则 Atmel 产品并非设计或旨在用于军事或航空航天应用或环境。除非 Atmel 明确指定为汽车级,否则 Atmel 产品并非设计或旨在用于汽车应用。

文件/资源

|

Atmel ATF15xx 复杂可编程逻辑器件 [pdf] 用户指南 ATF15xx,ATF15xx 复杂可编程逻辑器件,复杂可编程逻辑器件,可编程逻辑器件,逻辑器件,器件 |