Peranti Logik Boleh Aturcara Kompleks Atmel ATF15xx

Spesifikasi

- Nama Produk: Atmel ATF15xx Pengaturcaraan Dalam Sistem

- Model: ATF15xx

- Jenis: Peranti Logik Boleh Aturcara Kompleks (CPLD)

- Kaedah Pengaturcaraan: Pengaturcaraan Dalam Sistem (ISP)

- Antara muka: JTAG Antara Muka ISP

- Pengilang: Atmel

Soalan Lazim

S: Bolehkah saya menggunakan perisian pengaturcaraan pihak ketiga dengan CPLD ATF15xx?

J: Ya, selagi perisian menyokong algoritma pengaturcaraan dan JTAG arahan yang diperlukan untuk CPLD ATF15xx.

S: Adakah mungkin untuk memprogramkan berbilang CPLD ATF15xx secara serentak?

A: Ya, JTAG Antara muka ISP menyokong pelbagai pengaturcaraan peranti untuk pengaturcaraan yang cekap bagi berbilang CPLD sekaligus.

pengenalan

- Atmel® ATF15xx Complex Programmable Logic Devices (CPLDs) dengan seni bina Logic Doubling® menyokong Pengaturcaraan Dalam Sistem (ISP) melalui IEEE Std. 1149.1 Kumpulan Bertindak Ujian Bersama (JTAG) antara muka. Ciri ini meningkatkan fleksibiliti pengaturcaraan dan memberikan faedah dalam pelbagai fasa; pembangunan produk, pengeluaran dan penggunaan lapangan. Panduan pengguna ini menerangkan kaedah reka bentuk dan keperluan untuk melaksanakan ISP pada ATF15xx CPLD dengan sokongan ISP seperti yang disenaraikan di bawah:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Ciri dan Faedah

Pengaturcaraan dalam sistem membenarkan pengaturcaraan dan pengaturcaraan semula peranti ISP selepas ia dipasang pada Papan Litar Bercetak (PCB). Ini menghapuskan langkah pengendalian tambahan yang diperlukan dalam proses pembuatan untuk memprogram peranti pada pengaturcara peranti luaran sebelum ia dipasang pada PCB. Menghapuskan langkah ini mengurangkan kemungkinan merosakkan petunjuk halus peranti pelekap permukaan kiraan pin tinggi atau merosakkan peranti melalui nyahcas elektrostatik (ESD) semasa aliran pengaturcaraan. ISP juga membenarkan pengguna membuat perubahan reka bentuk dan naik taraf medan tanpa perlu mengalih keluar peranti ISP daripada PCB. Tambahan pula, ia juga membenarkan penggunaan mikropengawal terbenam atau penguji litar untuk melaksanakan operasi pengaturcaraan dalam sistem pada peranti ISP dan menyepadukan operasi pengaturcaraan ini ke dalam aliran pengeluaran papan litar.

Sistem Pengaturcaraan Dalam Sistem

Tiga komponen penting sistem ISP untuk CPLD ATF15xx ialah:

Perisian

Pelaksanaan algoritma pengaturcaraan, serta penjanaan JTAG arahan dan data untuk peranti ISP sasaran. Ini boleh menjadi program perisian yang dijalankan pada PC, mikropengawal terbenam atau peralatan ujian dalam litar.

Perkakasan Antara Muka

Saluran komunikasi antara perisian ISP dan peranti ISP pada papan sasaran. Ini boleh menjadi kabel muat turun ISP atau pengaturcara daripada Atmel atau vendor pihak ketiga, peralatan ujian dalam litar, atau sambungan antara mikropengawal terbenam dan peranti ISP pada PCB

Papan Sasaran

Papan litar yang mengandungi peranti ISP dalam JTAG rantai. Ini boleh menjadi papan ATF15xx CPLD Development/Programmer daripada Atmel atau papan litar yang direka khas dengan J yang sesuaiTAG sambungan kepada perkakasan antara muka.

Sebagai tambahan kepada tiga komponen ini, JEDEC file adalah perlu untuk memprogramkan CPLD ATF15xx. JEDEC ini file boleh dibuat dengan menyusun reka bentuk file menggunakan perisian pembangunan yang menyokong CPLD ATF15xx seperti Atmel WinCUPL dan Atmel ProChip Designer. Atmel juga menyediakan utiliti perisian penterjemah, POF2JED.exe, yang menukar output file daripada format pengaturcaraan pesaing kepada JEDEC file serasi dengan ATF15xx CPLD. Untuk mendapatkan maklumat lanjut tentang utiliti ini, sila rujuk nota aplikasi Atmel, "Penukaran Keluarga Produk ATF15xx", yang tersedia di Atmel webtapak. Selepas JEDEC files dicipta untuk semua CPLD ATF15xx, ia boleh diprogramkan pada papan sasaran. CPLD ATF15xx boleh diprogramkan oleh sistem pengaturcaraan dalam sistem berikut:

- Sistem Pengaturcaraan Dalam Sistem ATF15xx

- Pengawal mikro terbenam

- Penguji dalam litar

Sistem Pengaturcaraan Dalam Sistem Atmel ATF15xx

Untuk pengaturcaraan dalam sistem CPLD ATF15xx, perisian ISP, kabel muat turun dan kit pembangunan/pengaturcara boleh didapati daripada Atmel dan ia diterangkan dalam bahagian di bawah.

Perisian ISP

Perisian Atmel ATF15xx ISP, ATMISP, adalah cara utama untuk melaksanakan JTAG pengaturcaraan dalam sistem pada CPLD ATF15xx. ATMISP berjalan pada PC hos berasaskan Windows dan melaksanakan pengaturcaraan dalam sistem CPLD ATF15xx pada sistem perkakasan ISP sasaran atau menjana Format Vektor Bersiri (.SVF) file untuk digunakan oleh Automatic Testing Equipment (ATE) untuk memprogramkan ATF15xx CPLD pada sistem sasaran. ATMISP mula-mula memperoleh semua maklumat yang diperlukan daripada pengguna tentang JTAG rantai peranti dalam sistem sasaran. Ia kemudian melaksanakan J yang sesuaiTAG Arahan ISP ke JTAG rantai peranti dalam sistem sasaran mengikut JTAG maklumat rangkaian peranti yang ditentukan oleh pengguna melalui port USB atau LPT PC. Maklumat lanjut tentang perisian Atmel ATMISP boleh didapati di www.atmel.com/tools/ATMISP.aspx.

Kabel Muat Turun ISP

Kabel Muat Turun ISP berasaskan USB Atmel ATF15xx, ATDH1150USB, bersambung ke port USB standard komputer hos pada satu sisi dan ke JTAG pengepala papan litar sasaran di sisi lain. Ia memindahkan JTAG arahan dan data yang dijana oleh ATMISP berjalan pada PC hos ke peranti ISP pada papan litar sasaran. Maklumat lanjut mengenai kabel ATDH1150USB tersedia di www.atmel.com/tools/ATDH1150USB.aspx.

Pembangunan / Pengaturcara

Kit Pembangunan/Programmer Atmel ATF15xx, ATF15xx-DK3-U, ialah sistem pembangunan lengkap dan pengaturcara ISP untuk CPLD ATF15xx. Kit ini menyediakan pereka cara yang sangat cepat dan mudah untuk membangunkan prototaip dan menilai reka bentuk baharu dengan ATF15xx ISP CPLD. Dengan ketersediaan papan penyesuai soket yang berbeza untuk menyokong kebanyakan jenis pakej yang ditawarkan dalam CPLD ATF15xx, kit ini boleh digunakan sebagai pengaturcara ISP untuk memprogramkan CPLD ISP ATF15xx dalam kebanyakan jenis pakej yang tersedia melalui JTAG antara muka. Maklumat lanjut tentang kit Atmel ATF15xx-DK3-U boleh didapati di www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Sistem Pengawal Mikro Terbenam

Algoritma pengaturcaraan dan JTAG arahan untuk CPLD ATF15xx boleh dilaksanakan dalam mikropengawal atau mikropemproses, yang kemudiannya boleh digunakan untuk memprogramkan CPLD ATF15xx pada papan sasaran. Satu kaedah yang mungkin adalah untuk mengekstrak semua J yang berkaitanTAG maklumat protokol (iaitu JTAG arahan dan data) daripada SVF file dihasilkan oleh perisian ATMISP, dan kemudian gunakan maklumat ini untuk melaksanakan kod untuk mikropengawal atau mikropemproses yang akan menjana JTAG isyarat untuk peranti ISP dalam JTAG rantai. Pendekatan ini paling sesuai untuk sistem yang sudah mempunyai mikropengawal atau mikropemproses terbenam, dan ini menghapuskan penggunaan perisian dan alatan perkakasan pengaturcaraan dalam sistem luaran.

Sistem Pengujian dalam litar

CPLD ATF15xx boleh diprogramkan pada papan litar sasaran melalui JTAG antara muka semasa ujian papan litar menggunakan penguji dalam litar. Secara amnya, SVF file yang dihasilkan oleh ATMISP harus mengandungi semua J yang berkaitanTAG maklumat pengaturcaraan dalam sistem yang penguji dalam litar perlu memprogramkan CPLD ATF15xx pada papan litar sasaran. Pendekatan ini membenarkan penyepaduan langkah pengaturcaraan ke dalam ujiantage aliran pengeluaran.

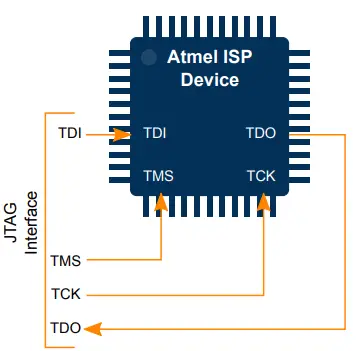

JTAG Antara Muka ISP

ISP untuk CPLD ATF15xx dilaksanakan menggunakan IEEE 1149.1 Std. JTAG antara muka. Antara muka ini boleh digunakan untuk memadam, memprogram dan mengesahkan CPLD ATF15xx. JTAG antara muka ialah antara muka bersiri yang terdiri daripada isyarat TCK, TMS, TDI dan TDO dan isyarat JTAG Pengawal Ujian Capaian Port (TAP). Pin TCK ialah input jam untuk JTAG Pengawal TAP dan untuk mengalih masuk/keluar JTAG arahan dan data. Pin TDI ialah input data bersiri. Ia digunakan untuk mengalihkan arahan pengaturcaraan dan data ke dalam peranti ISP. Pin TDO ialah output data bersiri. Ia digunakan untuk mengalih keluar data daripada peranti ISP. Pin TMS ialah pin pilihan mod. Ia mengawal keadaan JTAG Pengawal TAP. JTAG pin antara muka ATF15xx CPLD pada papan sasaran ISP mesti disambungkan kepada perkakasan antara muka ISP (iaitu kabel muat turun ISP) biasanya melalui pengepala 10 pin. Perkakasan antara muka ISP juga perlu disambungkan ke PC hos yang menjalankan perisian ISP. Perkakasan antara muka ISP mewujudkan komunikasi antara perisian ISP dan peranti ISP, dan ia membenarkan perisian ISP untuk memindahkan arahan pengaturcaraan dan data daripada PC hos kepada CPLD ATF15xx. ATF15xx CPLD dengan JTAG ciri yang didayakan adalah J sepenuhnyaTAG serasi dan juga menyokong operasi Ujian Imbasan Sempadan (BST) yang diperlukan yang dinyatakan dalam JTAG standard. CPLD ATF15xx boleh dikonfigurasikan untuk menjadi sebahagian daripada JTAG Rantaian BST dengan J yang lainTAG peranti untuk ujian litar dalam papan sistem. Dengan ciri ini, CPLD ATF15xx boleh diuji pada papan litar bersama-sama dengan JTAG-peranti yang disokong tanpa menggunakan ujian dasar kuku.

Pengaturcaraan Peranti Tunggal

JTAG Antara muka ISP boleh dikonfigurasikan untuk memprogramkan satu ATF15xx CPLD. JTAG konfigurasi untuk satu peranti ditunjukkan dalam rajah di bawah. Apabila CPLD ATF15xx dikonfigurasikan dengan cara ini, daftar muncul di antara pin TDI dan TDO peranti. Saiz daftar bergantung pada JTAG lebar arahan dan data yang dialihkan untuk arahan itu. Rajah 2-1 JTAG Peranti

Pengaturcaraan Berbilang Peranti

CPLD ATF15xx boleh dikonfigurasikan sebagai sebahagian daripada rantai daisy berbilang JTAG-peranti yang disokong seperti yang diterangkan di bawah dan juga ditunjukkan dalam rajah berikut.

- Sambungkan pin TMS dan TCK untuk setiap peranti dalam JTAG rantai ke pin TMS dan TCK JTAG pengepala antara muka pada papan litar.

- Sambungkan pin TDI dari peranti pertama ke pin TDI JTAG pengepala antara muka.

- Sambungkan pin TDO dari peranti pertama ke pin TDI peranti seterusnya. Teruskan proses ini sehingga semua kecuali yang terakhir disambungkan.

- Sambungkan pin TDO dari peranti terakhir ke pin TDO JTAG pengepala antara muka.

Rajah 2-2 Peranti Berbilang JTAG Konfigurasi

Untuk memprogramkan berbilang peranti dalam JTAG rantaian, pengguna mesti menggunakan alat perisian ISP yang menyokong ciri tersebut. Dalam perisian ISP, pengguna perlu menentukan:

- Bilangan peranti dalam JTAG rantai.

- Nombor bahagian peranti dan kedudukan dalam JTAG rantai.

- JTAG operasi untuk setiap peranti.

- J yang lainTAG-maklumat berkaitan seperti JTAG lebar arahan untuk setiap peranti.

Sebaik sahaja JTAG rantai daisy disediakan dengan betul pada papan sasaran ISP dan dalam perisian ISP, peranti dalam JTAG rantaian boleh diprogramkan pada masa yang sama.

Pertimbangan Reka Bentuk

Untuk melaksanakan ISP pada ATF15xx CPLD, sumber untuk JTAG antara muka dalam ATF15xx mesti ditempah. Oleh itu, empat pin I/O untuk pin TMS, TDI, TDO dan TCK mesti dikhaskan untuk JTAG dan tidak boleh digunakan sebagai I/O pengguna. Nombor pin untuk pin ini bergantung pada ATF15xx CPLD yang digunakan dan jenis pakejnya. Rujuk jadual di bawah untuk maklumat pinout. JTAG standard mengesyorkan bahawa pin TMS dan TDI ditarik ke atas untuk setiap peranti dalam JTAG rantai. CPLD ATF15xx mempunyai ciri tarik naik dalaman untuk pin ini yang, apabila didayakan, menjimatkan keperluan perintang tarik naik luaran. Tambahan pula, JTAG ciri antara muka mesti didayakan untuk melaksanakan ISP pada CPLD ATF15xx. Mendayakan JTAG antara muka memerlukan memilih jenis peranti Atmel tertentu atau tetapan pilihan sebelum menyusun reka bentuk ATF15xx. Prosedur ini digariskan untuk WinCUPL, ProChip Designer dan POF2JED dalam panduan ini. Secara lalai, semua ATF15xx CPLD yang serba baharu dihantar dengan JTAG antara muka didayakan. Sekali sumber logik untuk JTAG antara muka dikhaskan, pengguna boleh memprogram, mengesahkan dan memadam sebarang ATF15xx CPLD pada papan sasaran menggunakan perisian ATMISP.

Petua: Walaupun empat JTAG pin dikhaskan untuk JTAG antara muka, pengguna boleh melaksanakan fungsi logik terkubur dalam makrosel yang dikaitkan dengan pin ini.

Jadual 3-1 ATF15xx CPLD JTAG Nombor Pin

| JTAG Pin | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| TMS | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Dayakan JTAG Antara muka dengan WinCUPL

Untuk membolehkan JTAG antara muka dengan WinCUPL, jenis peranti ATF15xx ISP yang sesuai perlu dinyatakan sebelum reka bentuk disusun. Selepas reka bentuk berjaya disusun, JEDEC file dengan JTAG ciri antara muka didayakan dihasilkan. Apabila JEDEC ini file diprogramkan ke dalam ATF15xxCPLD, JTAG antara muka didayakan. Pengguna juga boleh mendayakan perintang tarik dalaman TDI dan TMS dengan memasukkan pernyataan sifat berikut dalam reka bentuk CUPL file.

- ATMEL HARTANAH {TDI_PULLUP = HIDUP};

- ATMEL HARTANAH {TMS_PULLUP = HIDUP};

Notis: Jika jenis peranti ISP ATF15xx digunakan untuk reka bentuk yang menggunakan JTAG pin antara muka sebagai pin I/O logik, WinCUPL menjana ralat.

Langkah berikut membincangkan cara membuka reka bentuk sedia ada dalam WinCUPL, nyatakan jenis peranti dan susun reka bentuk.

- Pada menu utama WinCUPL, pilih File > Buka. Pilih sumber CUPL (.pld). file daripada direktori kerja yang sesuai.

- Pilih OK untuk membuka sumber PLD file.

- Pada menu utama WinCUPL, pilih File > Jimat. Ini menjimatkan perubahan yang dibuat pada sumber file.

- Pada menu utama, pilih Pilihan > Peranti. Ini membuka kotak dialog Pemilihan Peranti.

- Pilih peranti ISP ATF15xx yang sesuai. Lihat jadual berikut untuk senarai semua jenis peranti ATF15xx yang disokong oleh WinCUPL.

- Pilih OK untuk menutup menu pemilihan peranti.

- Nota: Kaedah alternatif ialah memilih jenis peranti ATF15xx yang sesuai daripada jadual berikut dan masukkannya dalam bahagian pengepala sumber CUPL file.

- Pada menu utama WinCUPL, pilih Run> Device Dependent Compile.

- WinCUPL menyusun reka bentuk dan melahirkan pelengkap peranti Atmel. Jika reka bentuk sesuai, JEDEC file dibuat secara automatik.

- Apabila JEDEC file diprogramkan ke dalam peranti, JTAG antara muka, pilihan tarik TMS dalaman dan TDI, dan litar penjaga pin pilihan didayakan.

Nota: Memilih jenis peranti Atmel ISP secara automatik membolehkan JTAG antara muka secara lalai apabila Atmel WinCUPL menjalankan pemasangan peranti Atmel.

Jika reka bentuk menghalang tempahan sumber untuk JTAG antara muka atau ISP secara pilihan tidak digunakan, jenis peranti bukan ISP Atmel mesti dipilih. Lihat jadual di bawah untuk senarai peranti. Peranti itu kemudiannya boleh diprogramkan semula menggunakan pengaturcara peranti luaran. Jadual di bawah menyenaraikan jenis peranti Atmel ISP dan Atmel bukan ISP untuk WinCUPL.

Jadual 3-2 Jenis Peranti WinCUPL ATF15xx

| Nama Peranti | Jenis Pakej | Jenis Peranti WinCUPL | |

| JTAG Didayakan | JTAG Dilumpuhkan | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Dayakan JTAG Antara muka dengan Atmel ProChip Designer

Untuk membolehkan JTAG antara muka dengan ProChip Designer:

- Buka projek ProChip Designer yang sesuai.

- Buka tetingkap Fitter Options dengan mengklik pada butang Atmel Fitter di bawah Device Fitter.

- Pilih tab Peranti Global dan kemudian semak JTAG Kotak pelabuhan. Perintang tarik dalaman TMS dan TDI juga boleh didayakan dengan menandakan kotak Tarik TDI dan Tarik TMS. Kotak semak ini ditunjukkan dalam rajah di bawah.

Rajah 3-1 Antara Muka Pengguna Pilihan Pengisi Pereka ProChip

Dayakan JTAG Antara muka dengan POF2JED

Dalam POF2JED, JTAG Pilihan mod boleh ditetapkan kepada Auto untuk membenarkan POF2JED menentukan sama ada JTAG ciri dalam ATF15xx harus didayakan atau tidak, dan ia berdasarkan sama ada JTAG disokong dalam CPLD pesaing. Untuk menghidupkan JTAG dalam ATF15xx CPLD tanpa mengira sama ada JTAG disokong dalam CPLD pesaing atau tidak, JTAG Pilihan mod hendaklah ditetapkan kepada Hidup. Apabila JTAG didayakan dalam ATF15xx, perintang tarik naik dalaman TDI dan TMS boleh didayakan dengan menandakan Dayakan

TDI_PULLUP dan Dayakan kotak TMS_PULLUP dalam POF2JED. Lihat rajah di bawah.

Rajah 3-2 Antara Muka Pengguna POF2JED

Garis Panduan dan Syor

Perhatian: Perhatian tambahan kepada bahagian ini hendaklah dibuat semasa menjalankan operasi ISP pada CPLD ATF15xx. Bahagian ini membincangkan beberapa JTAG Garis panduan, maklumat dan cadangan ISP yang harus diambil perhatian dengan baik.

- Pastikan JTAG port untuk semua peranti dalam JTAG rantai didayakan.

- Untuk CPLD ATF15xx, JTAG port didayakan jika peranti kosong/dipadamkan atau diprogramkan dengan JTAG didayakan.

- Semua peranti Atmel ATF15xx dihantar dalam keadaan kosong/terpadam; oleh itu, JTAG port didayakan untuk semua peranti baharu dan sedia untuk ISP.

- Peranti ATF15xx dengan JTAG orang kurang upaya perlu dipadamkan menggunakan pengaturcara peranti bukan ISP untuk mendayakan semula JTAG pelabuhan.

- Pastikan VCC voltage digunakan pada setiap peranti dalam JTAG rantai.

- ATF15xxAS/ASL CPLD dalam jenis pakej 84-PLCC, 100-TQFP dan 100-PQFP: VCCINT mestilah antara 4.5V dan 5.5V manakala VCCIO boleh antara 3.0V dan 3.6V atau 4.5V dan 5.5V.

- ATF15xxAS/ASL CPLD dalam jenis pakej 44-PLCC dan 44-TQFP: VCC mestilah antara 4.5V hingga 5.5V.

- CPLD ATF15xxASV/ASVL: VCC (VCCIO dan VCCINT) mestilah antara 3.0V hingga 3.6V.

- VCC untuk peranti dalam JTAG rantai mesti dikawal dan ditapis dengan betul.

- Untuk CPLD ATF15xx yang digunakan dalam kebanyakan aplikasi, adalah disyorkan untuk menggunakan satu kapasitor penyahgandingan 0.22µF untuk setiap pasangan VCC/GND.

- Adalah disyorkan untuk menggunakan asas yang sama untuk semua peranti dalam JTAG rantai dan JTAG perkakasan antara muka (iaitu Kabel Muat Turun ISP ATDH1150USB).

- Adalah disyorkan untuk mengelakkan panjang (tidak lebih daripada lima peranti) JTAG rantai.

- Jika J panjangTAG rantai adalah perlu, menampan isyarat TMS dan TCK selepas setiap peranti kelima. Penggunaan penimbal pencetus Schmitt lebih diutamakan.

- Penampan membentuk semula masa naik dan turun isyarat TMS dan TCK.

- Perlu mengambil kira kelewatan tambahan yang ditanggung oleh penimbal.

- Adalah disyorkan untuk menggunakan perintang tarik-up (4.7KΩ hingga 10KΩ) untuk isyarat TMS dan TDI dan perintang tarik-turun untuk isyarat TCK pada JTAG pengepala untuk menghalang isyarat ini daripada terapung apabila ia tidak didorong oleh perkakasan antara muka.

- Tarik ke atas dalaman pilihan pada TMS dan TDI tersedia untuk CPLD ATF15xx.

- Adalah disyorkan untuk menamatkan JTAG isyarat di JTAG pengepala.

- Kedua-dua penamatan aktif dan pasif boleh diterima; bagaimanapun, penamatan pasif lebih diutamakan.

- Ia mengurangkan deringan kerana panjang surih kabel/PCB.

- Penamatan adalah paling kritikal untuk TMS dan TCK.

- Adalah disyorkan bahawa semua input dan I/O peranti dalam JTAG rantai, kecuali JTAG pin, hendaklah dalam keadaan statik apabila CPLD ATF15xx sedang diprogramkan untuk meminimumkan hingar.

- Apabila menggunakan salah satu papan pembangunan/pengaturcara Atmel ATF15xx, kuasa ke papan mesti dimatikan apabila kedudukan pelompat pemilihan VCC sedang ditukar.

- Untuk CPLD ATF15xx, JTAG ISP tersedia apabila bahagian tersebut berada dalam mod Kuasa turun terkawal Pin atau apabila peranti "kuasa rendah" sedang tidur.

- Keadaan peranti selepas gangguan ISP:

- Jika ISP terganggu, semua pin I/O dinyatakan tiga kali tanpa mengira keadaan litar Pin-keeper.

- Menghalang peranti yang diprogramkan separa daripada menyebabkan perbalahan bas dengan peranti lain pada papan litar.

- Semasa pengaturcaraan ISP, semua pin I/O berada dalam salah satu daripada syarat berikut:

- Keadaan impedans tinggi:

- Apabila peranti kosong/terpadam diprogramkan.

- Apabila peranti diprogramkan semula dengan litar Pin-keeper dilumpuhkan.

- Menghalang perbalahan bas dengan peranti luaran yang berantaramuka dengan ATF15xx CPLD pada papan litar.

- Diselak lemah ke keadaan sebelumnya:

- Apabila peranti yang diprogramkan diprogramkan semula dengan litar Penjaga Pin didayakan.

- Pin I/O mengekalkan tahap logik sebelumnya sebelum ISP.

- Menghalang ISP daripada menjejaskan operasi peranti lain pada papan sistem.

- Penggunaan pelbagai JTAG rantai pada satu papan tidak disyorkan.

- Peranti mungkin berinteraksi antara JTAG rantai.

- Papan berfungsi hanya apabila semua peranti dalam semua JTAG rantai diprogramkan dengan jayanya.

- Jika pengaturcaraan gagal untuk sekurang-kurangnya satu peranti dalam rantai manakala J yang lainTAG rantai berjaya diprogramkan:

- Sama ada Atmel atau peranti lain di atas kapal boleh rosak disebabkan kemungkinan masalah pertikaian bas untuk output tiga keadaan.

- Keadaan operasi papan sistem tidak ditentukan; dan oleh itu, operasi berfungsi yang salah mungkin berlaku.

- Memasukkan litar aktif antara JTAG pengepala dan JTAG peranti dalam rantai tidak disyorkan. Jika litar aktif tidak berfungsi, ia boleh menyebabkan masalah pengaturcaraan/sahkan.

- Penggunaan vol bercampurtage peranti JTAG rantai tidak disyorkan.

- Ini adalah JTAG rantai dengan peranti yang menggunakan VCC voltages dan/atau antara muka voltages.

- Antara muka voltagtahap e (VIL, VIH, VOL, VOH) untuk peranti 5.0V mungkin tidak serasi dengan antara muka voltagtahap e untuk peranti 3.0V.

- Jika ATMISP mempunyai masalah untuk berkomunikasi dengan JTAG rantaian perkakasan peranti, cuba jalankan Self Calibrate atau Manually Calibrate untuk menurunkan frekuensi JTAG isyarat.

- Pastikan LED pada kabel ATDH1150USB dihidupkan dan ia berwarna hijau sebelum pengaturcaraan bermula. Pastikan kabel muat turun ISP dapat berkomunikasi dengan betul dengan perisian ATMISP.

- Pastikan VCC voltage digunakan pada kabel ATDH1150USB.

- VCC yang digunakan oleh peranti pertama dalam JTAG rantai mesti dibekalkan kepada kabel ATDH1150USB melalui pin 4 10-pin JTAG pengepala.

- Untuk CPLD ATF15xx dengan VCCINT dan VCCIO yang berasingan, VCCIO harus digunakan untuk kabel ATDH1150USB.

Maklumat Pesanan

| Kod Pesanan | Penerangan |

| ATF15xx-DK3-U | Kit Pembangunan/Pengaturcara CPLD (termasuk ATF15xxDK3-SAA44 dan ATDH1150USB atau ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | Papan Penyesuai Soket TQFP 100-pin untuk Papan DK3 |

| ATF15xxDK3-SAJ44 | Papan Penyesuai Soket PLCC 44-pin untuk Papan DK3 |

| ATF15xxDK3-SAJ84 | Papan Penyesuai Soket PLCC 84-pin untuk Papan DK3 |

| ATF15xxDK3-SAA44 | Papan Penyesuai Soket TQFP 44-pin untuk Papan DK3 |

| ATDH1150USB | Atmel ATF15xx CPLD berasaskan USB JTAG Kabel Muat Turun ISP |

Sejarah Semakan

| Doc. Rev. | tarikh | Komen |

| A | 12/2015 | Keluaran dokumen awal. |

MAKLUMAT HUBUNGI

Atmel Corporation

- 1600 Technology Drive, San Jose, CA 95110 USA

- T: (+1)(408) 441.0311

- F: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_Panduan Pengguna-12/2015

Atmel®, logo Atmel dan gabungannya, Enabling Unlimited Possibilities®, dan lain-lain ialah tanda dagangan berdaftar atau tanda dagangan Atmel Corporation di AS dan negara lain. Terma dan nama produk lain mungkin merupakan tanda dagangan orang lain.

PENAFIAN: Maklumat dalam dokumen ini disediakan berkaitan dengan produk Atmel. Tiada lesen, nyata atau tersirat, melalui estoppel atau sebaliknya, kepada mana-mana hak harta intelek yang diberikan oleh dokumen ini atau berkaitan dengan penjualan produk Atmel. KECUALI YANG DITETAPKAN DALAM TERMA DAN SYARAT JUALAN ATMEL YANG TERLETAK DI ATMEL WEBTAPAK, ATMEL TIADA TANGGUNGJAWAB APA SAHAJA DAN MENAFIKAN SEBARANG WARANTI TERSURAT, TERSIRAT ATAU BERKANUN BERKAITAN PRODUKNYA TERMASUK, TETAPI TIDAK TERHAD KEPADA, WARANTI TERSIRAT KEBOLEHPERDAGANGAN, KESESUAIAN UNTUK PENGGUNAAN NEGARA TERTENTU. ATMEL TIDAK AKAN BERTANGGUNGJAWAB ATAS SEBARANG KEROSAKAN LANGSUNG, TIDAK LANGSUNG, AKIBAT, HUKUMAN, KHAS, ATAU SAMPINGAN (TERMASUK, TANPA HAD, ROSAK UNTUK KERUGIAN DAN KEUNTUNGAN, GANGGUAN PERNIAGAAN, ATAU KEHILANGAN MAKLUMAT PENGGUNAAN) GUNA INI DOKUMEN, WALAUPUN ATMEL TELAH DIMAKLUMKAN TENTANG KEMUNGKINAN KEROSAKAN TERSEBUT. Atmel tidak membuat pernyataan atau jaminan berkenaan dengan ketepatan atau kesempurnaan kandungan dokumen ini dan berhak untuk membuat perubahan pada spesifikasi dan penerangan produk pada bila-bila masa tanpa notis. Atmel tidak membuat sebarang komitmen untuk mengemas kini maklumat yang terkandung di sini. Melainkan diperuntukkan sebaliknya secara khusus, produk Atmel tidak sesuai untuknya, dan tidak boleh digunakan dalam aplikasi automotif. Produk Atmel tidak dimaksudkan, dibenarkan atau dijamin untuk digunakan sebagai komponen dalam aplikasi yang bertujuan untuk menyokong atau mengekalkan kehidupan. PENAFIAN APLIKASI KRITIKAL KESELAMATAN, KETENTERAAN DAN AUTOMOTIF: Produk Atmel tidak direka untuk dan tidak akan digunakan berkaitan dengan mana-mana aplikasi di mana kegagalan produk tersebut secara munasabah dijangka mengakibatkan kecederaan peribadi atau kematian yang ketara ("Kritikal Keselamatan Permohonan”) tanpa kebenaran bertulis khusus pegawai Atmel. Aplikasi kritikal keselamatan termasuk, tanpa had, peranti dan sistem sokongan hayat, peralatan atau sistem untuk pengendalian kemudahan nuklear dan sistem senjata. Produk Atmel tidak direka bentuk dan tidak dimaksudkan untuk digunakan dalam aplikasi atau persekitaran ketenteraan atau aeroangkasa melainkan ditetapkan secara khusus oleh Atmel sebagai gred tentera. Produk Atmel tidak direka bentuk dan tidak dimaksudkan untuk digunakan dalam aplikasi automotif melainkan ditetapkan secara khusus oleh Atmel sebagai gred automotif.

Dokumen / Sumber

|

Peranti Logik Boleh Aturcara Kompleks Atmel ATF15xx [pdf] Panduan Pengguna ATF15xx, Peranti Logik Boleh Aturcara Kompleks ATF15xx, Peranti Logik Boleh Aturcara Kompleks, Peranti Logik Boleh Aturcara, Peranti Logik, Peranti |