Dispositivo lógico programable complejo Atmel ATF15xx

Presupuesto

- Nombre del producto: Programación en el sistema Atmel ATF15xx

- Modelo: ATF15xx

- Tipo: Dispositivo lógico programable complejo (CPLD)

- Método de programación: Programación en el sistema (ISP)

- Interfaz: JTAG Interfaz del ISP

- Fabricante: Atmel

Preguntas frecuentes

P: ¿Puedo utilizar software de programación de terceros con los CPLD ATF15xx?

R: Sí, siempre que el software admita el algoritmo de programación y JTAG instrucciones necesarias para los CPLD ATF15xx.

P: ¿Es posible programar varios CPLD ATF15xx simultáneamente?

A: Sí, la JTAG La interfaz ISP admite la programación de múltiples dispositivos para una programación eficiente de múltiples CPLD a la vez.

Introducción

- Los dispositivos lógicos programables complejos (CPLD) Atmel® ATF15xx con arquitectura Logic Doubling® admiten la programación en el sistema (ISP) a través del estándar IEEE 1149.1 Joint Test Action Group (JTAG). Esta característica mejora la flexibilidad de programación y brinda beneficios en varias fases: desarrollo de productos, producción y uso en campo. Esta guía del usuario describe los métodos de diseño y los requisitos para implementar ISP en los CPLD ATF15xx con soporte para ISP, como se indica a continuación:

- ATF1502AS/ASL/ASV

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

Características y beneficios

La programación en el sistema permite programar y reprogramar los dispositivos ISP después de montarlos en las placas de circuito impreso (PCB). Esto elimina el paso de manipulación adicional que se requiere en el proceso de fabricación para programar los dispositivos en un programador de dispositivos externo antes de montarlos en las PCB. La eliminación de este paso reduce la posibilidad de dañar los delicados cables de los dispositivos de montaje en superficie con un gran número de pines o de dañar el dispositivo mediante una descarga electrostática (ESD) durante el flujo de programación. La programación en el sistema también permite a los usuarios realizar cambios de diseño y actualizaciones de campo sin tener que quitar los dispositivos ISP de las PCB. Además, también permite el uso de un microcontrolador integrado o un comprobador en el circuito para realizar operaciones de programación en el sistema en los dispositivos ISP e integrar estas operaciones de programación en el flujo de producción de las placas de circuito.

Sistemas de programación en el sistema

Los tres componentes esenciales de un sistema ISP para los CPLD ATF15xx son:

Software

Implementación del algoritmo de programación, así como la generación del JTAG Instrucciones y datos para los dispositivos ISP de destino. Puede ser un programa de software que se ejecuta en una PC, un microcontrolador integrado o un equipo de prueba en circuito.

Hardware de interfaz

Un canal de comunicación entre el software ISP y los dispositivos ISP en la placa de destino. Puede ser un cable de descarga ISP o un programador de Atmel o de un proveedor externo, un equipo de prueba en circuito o las conexiones entre un microcontrolador integrado y los dispositivos ISP en la PCB

Tablero de objetivos

Placa de circuito que contiene los dispositivos ISP en el JTAG cadena. Puede ser la placa de desarrollo/programación CPLD ATF15xx de Atmel o una placa de circuito diseñada a medida con el conector J apropiado.TAG Conexiones al hardware de la interfaz.

Además de estos tres componentes, un JEDEC file Es necesario programar un CPLD ATF15xx. Este JEDEC file se puede crear compilando un diseño file utilizando software de desarrollo que admita los CPLD ATF15xx, como Atmel WinCUPL y Atmel ProChip Designer. Atmel también ofrece una utilidad de software traductor, POF2JED.exe, que convierte la salida file Del formato de programación del competidor a un JEDEC file compatible con el CPLD ATF15xx. Para obtener más información sobre esta utilidad, consulte la nota de aplicación de Atmel, “Conversión de la familia de productos ATF15xx”, disponible en el sitio web de Atmel. websitio. Después del JEDEC fileSe crean para todos los CPLD ATF15xx y se pueden programar en la placa de destino. Los CPLD ATF15xx se pueden programar mediante los siguientes sistemas de programación en el sistema:

- Sistema de programación en el sistema ATF15xx

- Microcontroladores integrados

- Probadores en circuito

Sistema de programación en el sistema Atmel ATF15xx

Para la programación dentro del sistema de los CPLD ATF15xx, el software ISP, el cable de descarga y el kit de desarrollo/programación están disponibles en Atmel y se describen en las secciones siguientes.

Software de proveedor de servicios de Internet

El software ISP Atmel ATF15xx, ATMISP, es el medio principal para implementar JTAG Programación en el sistema de los CPLD ATF15xx. ATMISP se ejecuta en una PC host con Windows e implementa la programación en el sistema de los CPLD ATF15xx en el sistema de hardware del ISP de destino o genera un formato de vector serial (.SVF) file Para que lo utilice el equipo de prueba automático (ATE) para programar los CPLD ATF15xx en el sistema de destino, ATMISP primero adquiere toda la información necesaria de los usuarios sobre el JTAG cadena de dispositivos en el sistema de destino. Luego ejecuta el J apropiadoTAG Instrucciones del ISP en el JTAG Cadena de dispositivos en el sistema de destino según JTAG Información de la cadena de dispositivos especificada por los usuarios a través del puerto USB o LPT de la PC. Hay más información sobre el software ATMISP de Atmel disponible en www.atmel.com/tools/ATMISP.aspx.

Cable de descarga del ISP

El cable de descarga ISP basado en USB Atmel ATF15xx, ATDH1150USB, se conecta a un puerto USB estándar de una computadora host en un lado y a un puerto JTAG En el otro lado, se encuentra el encabezado de la placa de circuito de destino. Transfiere la señal JTAG instrucciones y datos generados por ATMISP que se ejecutan en la PC anfitriona a los dispositivos ISP en la placa de circuito de destino. Hay más información sobre el cable ATDH1150USB disponible en www.atmel.com/tools/ATDH1150USB.aspx.

Desarrollo/Programador

El kit de desarrollo/programación Atmel ATF15xx, ATF15xx-DK3-U, es un sistema de desarrollo completo y un programador ISP para los CPLD ATF15xx. Este kit ofrece a los diseñadores una forma muy rápida y sencilla de desarrollar prototipos y evaluar nuevos diseños con un CPLD ISP ATF15xx. Con la disponibilidad de diferentes placas adaptadoras de zócalo para admitir la mayoría de los tipos de encapsulado ofrecidos en los CPLD ATF15xx, este kit se puede utilizar como un programador ISP para programar los CPLD ISP ATF15xx en la mayoría de los tipos de encapsulado disponibles a través de JTAG Interfaz. Más información sobre el kit Atmel ATF15xx-DK3-U está disponible en www.atmel.com/tools/ATF15XX-DK3-U.aspx.

Sistema de microcontrolador integrado

El algoritmo de programación y JTAG Las instrucciones para los CPLD ATF15xx se pueden implementar en un microcontrolador o microprocesador, que luego se puede utilizar para programar los CPLD ATF15xx en la placa de destino. Un método posible es extraer todos los JTAG información del protocolo (es decir, JTAG instrucciones y datos) del SVF file generado por el software ATMISP y luego usar esta información para implementar código para el microcontrolador o microprocesador que generaría el JTAG señales para los dispositivos ISP en el JTAG cadena. Este enfoque es más adecuado para sistemas que ya tienen un microcontrolador o microprocesador incorporado, y elimina el uso de software de programación externo dentro del sistema y herramientas de hardware.

Sistema de prueba en circuito

Los CPLD ATF15xx se pueden programar en la placa de circuito de destino a través del conector JTAG interfaz durante la prueba de la placa de circuito con un comprobador en circuito. Generalmente, el SVF file generado por ATMISP debe contener todos los J pertinentesTAG Información de programación en el sistema que los probadores en circuito necesitan para programar los CPLD ATF15xx en la placa de circuito de destino. Este enfoque permite la integración del paso de programación en el proceso de prueba.tage del flujo de producción.

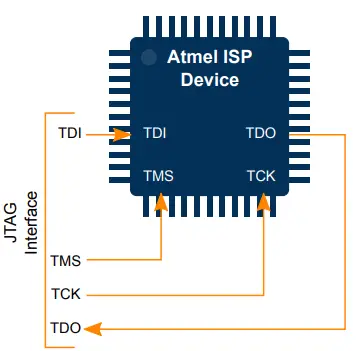

JTAG Interfaz del ISP

El ISP para los CPLD ATF15xx se implementa utilizando el estándar IEEE 1149.1 Std. JTAG Interfaz. Esta interfaz se puede utilizar para borrar, programar y verificar los CPLD ATF15xx. La JTAG La interfaz es una interfaz serial que consta de las señales TCK, TMS, TDI y TDO y un JTAG Controlador del puerto de acceso de prueba (TAP). El pin TCK es la entrada de reloj para el puerto J.TAG Controlador TAP y para cambiar hacia dentro o hacia fuera el JTAG instrucciones y datos. El pin TDI es la entrada de datos en serie. Se utiliza para transferir instrucciones y datos de programación a los dispositivos ISP. El pin TDO es la salida de datos en serie. Se utiliza para transferir datos desde los dispositivos ISP. El pin TMS es un pin de selección de modo. Controla el estado del JTAG Controlador TAP. El JTAG Los pines de interfaz del CPLD ATF15xx en la placa de destino ISP deben estar conectados al hardware de interfaz ISP (es decir, el cable de descarga ISP) generalmente a través de un conector de 10 pines. El hardware de interfaz ISP también debe estar conectado a la PC host que ejecuta el software ISP. El hardware de interfaz ISP establece comunicación entre el software ISP y los dispositivos ISP, y permite que el software ISP transfiera las instrucciones de programación y los datos desde la PC host a los CPLD ATF15xx. CPLD ATF15xx con JTAG Las funciones habilitadas están completamente JTAG compatible y también admite las operaciones de prueba de escaneo de límites (BST) requeridas especificadas en JTAG Estándar. Los CPLD ATF15xx se pueden configurar para ser parte de un JTAG Cadena BST con otros JTAG Dispositivos para pruebas en circuito de la placa del sistema. Con esta función, los CPLD ATF15xx se pueden probar en la placa de circuito junto con otros JTAG-dispositivos compatibles sin recurrir a pruebas de lecho de clavos.

Programación de un solo dispositivo

La jTAG La interfaz ISP se puede configurar para programar un solo CPLD ATF15xx.TAG La siguiente figura muestra la configuración para un solo dispositivo. Cuando se configura un CPLD ATF15xx de esta manera, aparece un registro entre los pines TDI y TDO del dispositivo. El tamaño del registro depende del JTAG Ancho de instrucción y datos que se desplazan para esa instrucción. Figura 2-1 JTAG Dispositivo

Programación de múltiples dispositivos

Los CPLD ATF15xx se pueden configurar como parte de una conexión en cadena de múltiples JTAG-dispositivos compatibles como se describe a continuación y también se muestra en la siguiente figura.

- Conecte el pin TMS y TCK de cada dispositivo en el JTAG cadena a los pines TMS y TCK del JTAG encabezado de interfaz en la placa de circuito.

- Conecte el pin TDI del primer dispositivo al pin TDI del JTAG encabezado de interfaz.

- Conecte el pin TDO del primer dispositivo al pin TDI del siguiente dispositivo. Continúe este proceso hasta que todos los dispositivos, excepto el último, estén conectados.

- Conecte el pin TDO del último dispositivo al pin TDO del JTAG encabezado de interfaz.

Figura 2-2 Dispositivo Múltiple JTAG Configuración

Para programar varios dispositivos en un JTAG En la cadena de suministro, los usuarios deben utilizar herramientas de software de ISP que admitan dichas funciones. En el software de ISP, los usuarios deben especificar:

- Número de dispositivos en el JTAG cadena.

- Números de piezas de los dispositivos y posiciones dentro del JTAG cadena.

- JTAG operaciones para cada uno de los dispositivos.

- Otros JTAG-información relacionada como la JTAG ancho de instrucción para cada uno de los dispositivos.

Una vez que el JTAG La conexión en cadena está configurada correctamente en la placa de destino del ISP y en el software del ISP, los dispositivos en JTAG La cadena se puede programar al mismo tiempo.

Consideraciones de diseño

Para realizar ISP en un CPLD ATF15xx, se necesitan recursos para JTAG La interfaz en el ATF15xx debe reservarse. Por lo tanto, los cuatro pines de E/S para los pines TMS, TDI, TDO y TCK deben reservarse para JTAG y no se pueden utilizar como E/S de usuario. Los números de pines para estos pines dependen del CPLD ATF15xx que se utilice y de su tipo de encapsulado. Consulte la siguiente tabla para obtener información sobre la distribución de pines.TAG La norma recomienda que los pines TMS y TDI se extraigan para cada dispositivo en el JTAG Los CPLD ATF15xx tienen una función pull-up interna para estos pines que, cuando está habilitada, ahorra la necesidad de resistencias pull-up externas. Además, el JTAG La función de interfaz debe estar habilitada para poder realizar ISP en los CPLD ATF15xx. Habilitar la función JTAG La interfaz requiere la elección de tipos de dispositivos Atmel específicos o configuraciones de opciones antes de compilar el diseño ATF15xx. Estos procedimientos se describen para WinCUPL, ProChip Designer y POF2JED en esta guía. De manera predeterminada, todos los CPLD ATF15xx nuevos se envían con el JTAG Interfaz habilitada. Una vez que se hayan habilitado los recursos lógicos para JTAG Las interfaces están reservadas, los usuarios pueden programar, verificar y borrar cualquier CPLD ATF15xx en la placa de destino utilizando el software ATMISP.

Consejo:Aunque las cuatro JTAG Los pines están reservados para una JTAG Interfaz, los usuarios pueden implementar funciones lógicas enterradas en las macroceldas asociadas con estos pines.

Tabla 3-1 CPLD ATF15xxTAG Números PIN

| JTAG Alfiler | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| EMT | 7 | 13 | 23 | 15 | 17 |

| TCC | 26 | 32 | 62 | 62 | 64 |

Habilitar JTAG Interfaz con WinCUPL

Para habilitar el JTAG Para la interfaz con WinCUPL, se debe especificar el tipo de dispositivo ISP ATF15xx adecuado antes de compilar un diseño. Una vez compilado correctamente un diseño, se genera un JEDEC file con la JTAG Se genera la función de interfaz habilitada. Cuando este JEDEC file está programado en un ATF15xxCPLD, su JTAG La interfaz está habilitada. Los usuarios también pueden habilitar las resistencias pull-up internas TDI y TMS al incluir las siguientes declaraciones de propiedades en el diseño CUPL file.

- PROPIEDAD ATMEL {TDI_PULLUP = ON};

- PROPIEDAD ATMEL {TMS_PULLUP = ON};

Aviso:Si se utiliza un tipo de dispositivo ISP ATF15xx para un diseño que utiliza JTAG pines de interfaz como pines de E/S lógicas, WinCUPL genera un error.

Los siguientes pasos explican cómo abrir un diseño existente en WinCUPL, especificar el tipo de dispositivo y compilar el diseño.

- En el menú principal de WinCUPL, seleccione File > Abrir. Seleccionar la fuente CUPL (.pld) file desde el directorio de trabajo apropiado.

- Seleccione Aceptar para abrir la fuente PLD file.

- En el menú principal de WinCUPL, seleccione File > Guardar. Esto guarda los cambios realizados en el código fuente. file.

- En el menú principal, seleccione Opciones > Dispositivos. Se abrirá el cuadro de diálogo Selección de dispositivos.

- Seleccione el dispositivo ISP ATF15xx adecuado. Consulte la siguiente tabla para obtener una lista de todos los tipos de dispositivos ATF15xx compatibles con WinCUPL.

- Seleccione Aceptar para cerrar el menú de selección de dispositivos.

- Nota: Un método alternativo es elegir un tipo de dispositivo ATF15xx apropiado de la siguiente tabla e incluirlo en la sección de encabezado de la fuente CUPL file.

- En el menú principal de WinCUPL, seleccione Ejecutar > Compilación dependiente del dispositivo.

- WinCUPL compila el diseño y genera el dispositivo Atmel. Si el diseño se ajusta, se genera un JEDEC. file se crea automáticamente.

- Cuando el JEDEC file está programado en el dispositivo, el JTAG La interfaz, los pull-ups internos TMS y TDI opcionales y los circuitos pin-keeper opcionales están habilitados.

Nota:Al seleccionar un tipo de dispositivo ISP de Atmel se habilita automáticamente el JTAG interfaz por defecto cuando Atmel WinCUPL ejecuta el instalador de dispositivos Atmel.

Si los diseños impiden reservar recursos para el JTAG Si no se utiliza una interfaz o un ISP, se debe seleccionar un tipo de dispositivo Atmel que no sea ISP. Consulte la tabla a continuación para obtener una lista de dispositivos. Luego, el dispositivo se puede reprogramar utilizando un programador de dispositivos externo. La siguiente tabla enumera los tipos de dispositivos Atmel ISP y Atmel que no son ISP para WinCUPL.

Tabla 3-2 Tipo de dispositivo WinCUPL ATF15xx

| Nombre del dispositivo | Tipo de paquete | Tipo de dispositivo WinCUPL | |

| JTAG Activado | JTAG Desactivado | ||

| ATF1502AS/ASL/ASV | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASL/ASV | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PQFP100 | F1508ISPQFP100 | F1508QFP100 |

Habilitar JTAG Interfaz con Atmel ProChip Designer

Para habilitar el JTAG Interfaz con ProChip Designer:

- Abra el proyecto ProChip Designer apropiado.

- Abra la ventana Opciones de Fitter haciendo clic en el botón Atmel Fitter debajo de Device Fitter.

- Seleccione la pestaña Dispositivo global y luego marque la casilla JTAG Cuadro de puerto. Las resistencias pull-up internas TMS y TDI también se pueden habilitar marcando las casillas Pull-up TDI y Pull-up TMS. Estas casillas de verificación se muestran en la siguiente figura.

Figura 3-1 Interfaz de usuario de opciones de ajuste de ProChip Designer

Habilitar JTAG Interfaz con POF2JED

En POF2JED, la JTAG La opción de modo se puede configurar en Automático para permitir que POF2JED determine si JTAG La función en el ATF15xx debe estar habilitada o no, y depende de si JTAG es compatible con el CPLD del competidor. Para activar JTAG en el CPLD ATF15xx independientemente de si JTAG es compatible con el CPLD del competidor o no, el JTAG La opción de modo debe estar configurada en Activado. Cuando JTAG está habilitado en el ATF15xx, las resistencias pull-up internas TDI y TMS se pueden habilitar marcando la casilla Habilitar

Cuadros TDI_PULLUP y Habilitar TMS_PULLUP en POF2JED. Vea la figura a continuación.

Figura 3-2 Interfaz de usuario de POF2JED

Directrices y Recomendaciones

Atención:Se debe prestar especial atención a esta sección al realizar operaciones de ISP en CPLD ATF15xx. En esta sección se analizan algunas de las JTAG Pautas, información y recomendaciones del ISP que conviene tener bien en cuenta.

- Asegúrese de que la JTAG puerto para todos los dispositivos en el JTAG Las cadenas están habilitadas.

- Para los CPLD ATF15xx, el JTAG El puerto está habilitado si los dispositivos están en blanco/borrados o programados con JTAG activado.

- Todos los dispositivos Atmel ATF15xx se envían en estado en blanco/borrado; por lo tanto, la JTAG El puerto está habilitado para todos los dispositivos nuevos y listo para el ISP.

- Dispositivos ATF15xx con JTAG Los deshabilitados deben borrarse utilizando un programador de dispositivo que no sea ISP para volver a habilitar el JTAG puerto.

- Asegúrese de que el volumen VCC sea adecuadotage se aplica a cada uno de los dispositivos en el JTAG cadena.

- CPLD ATF15xxAS/ASL en tipos de paquete 84-PLCC, 100-TQFP y 100-PQFP: VCCINT debe estar entre 4.5 V y 5.5 V, mientras que VCCIO puede estar entre 3.0 V y 3.6 V o entre 4.5 V y 5.5 V.

- CPLD ATF15xxAS/ASL en tipos de paquete 44-PLCC y 44-TQFP: VCC debe estar entre 4.5 V y 5.5 V.

- CPLD ATF15xxASV/ASVL: VCC (VCCIO y VCCINT) debe estar entre 3.0 V y 3.6 V.

- El VCC para los dispositivos en el JTAG La cadena debe estar adecuadamente regulada y filtrada.

- Para los CPLD ATF15xx utilizados en la mayoría de las aplicaciones, se recomienda utilizar un condensador de desacoplamiento de 0.22 µF para cada uno de los pares VCC/GND.

- Se recomienda utilizar una conexión a tierra común para todos los dispositivos en el JTAG cadena y la JTAG hardware de interfaz (es decir, cable de descarga ISP ATDH1150USB).

- Se recomienda evitar largos períodos de tiempo (no más de cinco dispositivos) JTAG cadenas.

- Si una J largaTAG Es necesario almacenar en búfer las señales TMS y TCK después de cada quinto dispositivo. Se prefiere el uso del búfer de disparo Schmitt.

- Los buffers remodelan los tiempos de subida y bajada de las señales TMS y TCK.

- Es necesario tener en cuenta el retraso adicional que suponen los buffers.

- Se recomienda utilizar resistencias pull-up (4.7 KΩ a 10 KΩ) para las señales TMS y TDI y resistencia pull-down para la señal TCK en JTAG encabezado para evitar que estas señales floten cuando no están siendo controladas por el hardware de la interfaz.

- Hay pull-ups internos opcionales en TMS y TDI disponibles para los CPLD ATF15xx.

- Se recomienda terminar JTAG señales en el JTAG encabezamiento.

- Se aceptan tanto terminaciones activas como pasivas; sin embargo, se prefiere la terminación pasiva.

- Reduce el zumbido causado por longitudes largas de cables o pistas de PCB.

- La terminación es lo más crítico para TMS y TCK.

- Se recomienda que todas las entradas y E/S de los dispositivos en el JTAG cadena, excepto la JTAG Los pines deben estar en estado estático cuando se programan los CPLD ATF15xx para minimizar el ruido.

- Al utilizar una de las placas de desarrollo/programación Atmel ATF15xx, se debe apagar la placa cuando se cambian las posiciones de los puentes de selección VCC.

- Para los CPLD ATF15xx, JTAG El ISP está disponible cuando la pieza está en modo de apagado controlado por PIN o cuando el dispositivo de “bajo consumo” está inactivo.

- Estado del dispositivo después de la interrupción del ISP:

- Si se interrumpe el ISP, todos los pines de E/S se triestado independientemente del estado de los circuitos Pin-keeper.

- Evita que los dispositivos parcialmente programados provoquen contención de bus con otros dispositivos en la placa de circuito.

- Durante la programación ISP, todos los pines de E/S están en una de las siguientes condiciones:

- Estado de alta impedancia:

- Cuando se programa un dispositivo en blanco/borrado.

- Cuando se reprograma un dispositivo con los circuitos Pin-keeper deshabilitados.

- Evita la contención del bus con dispositivos externos que interactúan con los CPLD ATF15xx en la placa de circuito.

- Débilmente aferrado al estado anterior:

- Cuando se reprograma un dispositivo programado con los circuitos Pin-keeper habilitados.

- Los pines de E/S mantienen niveles lógicos anteriores al ISP.

- Evita que el ISP afecte el funcionamiento de otros dispositivos en la placa del sistema.

- El uso de múltiples JTAG No se recomienda colocar cadenas en un mismo tablero.

- Los dispositivos pueden interactuar entre diferentes JTAG cadenas.

- La placa solo es funcional cuando todos los dispositivos están en JTAG Las cadenas están programadas con éxito.

- Si la programación falla para al menos un dispositivo en una cadena mientras que otros JTAG Las cadenas se programaron con éxito:

- Tanto Atmel como otros dispositivos a bordo pueden resultar dañados debido a un posible problema de contención de bus en salidas triestatables.

- El estado operativo de la placa del sistema no está definido y, por lo tanto, puede ocurrir una operación funcional incorrecta.

- Inserción de circuitos activos entre JTAG encabezado y la JTAG No se recomienda conectar dispositivos en cadena. Si el circuito activo funciona mal, puede causar problemas de programación o verificación.

- El uso de volúmenes mixtostagEl dispositivo JTAG No se recomiendan cadenas.

- Estos son JTAG Cadenas con dispositivos que utilizan diferentes volúmenes VCC.tages y/o interfaz voltages.

- Volumen de la interfaztagLos niveles (VIL, VIH, VOL, VOH) para dispositivos de 5.0 V podrían no ser compatibles con el volumen de la interfaz.tagNiveles e para dispositivos de 3.0 V.

- Si ATMISP tiene problemas para comunicarse con el JTAG cadena de hardware del dispositivo, intente ejecutar Calibración automática o Calibración manual para reducir las frecuencias del JTAG señales.

- Asegúrese de que el LED del cable ATDH1150USB esté encendido y en verde antes de comenzar la programación. Asegúrese de que el cable de descarga del ISP pueda comunicarse correctamente con el software ATMISP.

- Asegúrese de que el volumen VCC sea adecuadotage se aplica al cable ATDH1150USB.

- El VCC utilizado por el primer dispositivo en el JTAG La cadena debe suministrarse al cable ATDH1150USB a través del pin 4 del conector J de 10 pines.TAG encabezamiento.

- Para los CPLD ATF15xx con VCCINT y VCCIO separados, se debe utilizar VCCIO para el cable ATDH1150USB.

Información de pedidos

| Código de pedido | Descripción |

| ATF15xx-DK3-U | Kit de desarrollo/programación de CPLD (incluye ATF15xxDK3-SAA44 y ATDH1150USB o ATDH1150USB-K) |

| ATF15xxDK3-SAA100 | Placa adaptadora de enchufe TQFP de 100 pines para placa DK3 |

| ATF15xxDK3-SAJ44 | Placa adaptadora de enchufe PLCC de 44 pines para placa DK3 |

| ATF15xxDK3-SAJ84 | Placa adaptadora de enchufe PLCC de 84 pines para placa DK3 |

| ATF15xxDK3-SAA44 | Placa adaptadora de enchufe TQFP de 44 pines para placa DK3 |

| ATDH1150USB | CPLD Atmel ATF15xx basado en USB JTAG Cable de descarga del ISP |

Historial de revisiones

| Doc. Rdo. | Fecha | Comentarios |

| A | 12/2015 | Publicación inicial del documento. |

INFORMACIÓN DEL CONTACTO

Corporación Atmel

- 1600 Technology Drive, San José, CA 95110 EE. UU.

- Teléfono: (+1)(408) 441.0311

- Teléfono: (+1)(408) 436.4200

- www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_Guía del usuario-12/2015

Atmel®, el logotipo de Atmel y sus combinaciones, Enabling Unlimited Possibilities® y otros son marcas comerciales registradas o marcas comerciales de Atmel Corporation en los EE. UU. y otros países. Otros términos y nombres de productos pueden ser marcas comerciales de terceros.

DESCARGO DE RESPONSABILIDAD: La información de este documento se proporciona en relación con los productos Atmel. No se otorga ninguna licencia, expresa o implícita, por impedimento legal o de otro modo, a ningún derecho de propiedad intelectual mediante este documento o en relación con la venta de productos Atmel. EXCEPTO LO ESTABLECIDO EN LOS TÉRMINOS Y CONDICIONES DE VENTAS DE ATMEL UBICADOS EN EL ATMEL WEBSITIO, ATMEL NO ASUME NINGUNA RESPONSABILIDAD Y RENUNCIA A CUALQUIER GARANTÍA EXPRESA, IMPLÍCITA O ESTATUTARIA RELACIONADA CON SUS PRODUCTOS, INCLUYENDO, PERO SIN LIMITARSE A, LA GARANTÍA IMPLÍCITA DE COMERCIABILIDAD, IDONEIDAD PARA UN PROPÓSITO PARTICULAR O NO INFRACCIÓN. ATMEL NO SERÁ RESPONSABLE EN NINGÚN CASO POR DAÑOS DIRECTOS, INDIRECTOS, CONSECUENTES, PUNITIVOS, ESPECIALES O INCIDENTALES (INCLUIDOS, SIN LIMITACIÓN, DAÑOS POR PÉRDIDAS Y GANANCIAS, INTERRUPCIÓN COMERCIAL O PÉRDIDA DE INFORMACIÓN) QUE SURJAN DEL USO O LA INCAPACIDAD DE USAR ESTE DOCUMENTO, AUNQUE ATMEL HAYA SIDO ADVERTIDO DE LA POSIBILIDAD DE DICHOS DAÑOS. Atmel no hace declaraciones ni garantías con respecto a la precisión o integridad del contenido de este documento y se reserva el derecho de realizar cambios en las especificaciones y descripciones de productos en cualquier momento sin previo aviso. Atmel no asume ningún compromiso de actualizar la información contenida en este documento. A menos que se indique específicamente lo contrario, los productos de Atmel no son adecuados para aplicaciones automotrices y no se deben utilizar en ellas. Los productos de Atmel no están diseñados, autorizados ni garantizados para su uso como componentes en aplicaciones destinadas a respaldar o sostener la vida. DESCARGO DE RESPONSABILIDAD PARA APLICACIONES MILITARES Y AUTOMOTRICES CRÍTICAS PARA LA SEGURIDAD: Los productos de Atmel no están diseñados para, y no se utilizarán en relación con, ninguna aplicación en la que se esperaría razonablemente que la falla de dichos productos provoque lesiones personales significativas o la muerte ("Aplicaciones críticas para la seguridad") sin el consentimiento específico por escrito de un funcionario de Atmel. Las aplicaciones críticas para la seguridad incluyen, sin limitación, dispositivos y sistemas de soporte vital, equipos o sistemas para el funcionamiento de instalaciones nucleares y sistemas de armas. Los productos de Atmel no están diseñados ni destinados para su uso en aplicaciones o entornos militares o aeroespaciales a menos que Atmel los designe específicamente como de grado militar. Los productos de Atmel no están diseñados ni pensados para usarse en aplicaciones automotrices a menos que Atmel los designe específicamente como de grado automotriz.

Documentos / Recursos

|

Dispositivo lógico programable complejo Atmel ATF15xx [pdf] Guía del usuario ATF15xx, Dispositivo lógico programable complejo ATF15xx, Dispositivo lógico programable complejo, Dispositivo lógico programable, Dispositivo lógico, Dispositivo |