Atmel ATF15xx 複合プログラマブルロジックデバイス

仕様

- 製品名: Atmel ATF15xx インシステムプログラミング

- モデル: ATF15xx

- タイプ: 複合プログラマブルロジックデバイス (CPLD)

- プログラミング方式: インシステムプログラミング (ISP)

- インターフェース: JTAG ISP インターフェース

- メーカー: アトメル

よくある質問

Q: ATF15xx CPLD でサードパーティのプログラミング ソフトウェアを使用できますか?

A: はい、ソフトウェアがプログラミングアルゴリズムとJをサポートしている限り、TAG ATF15xx CPLD に必要な命令。

Q: 複数の ATF15xx CPLD を同時にプログラムすることは可能ですか?

A: はい、JTAG ISP インターフェイスは、複数の CPLD を一度に効率的にプログラミングするための複数のデバイス プログラミングをサポートします。

導入

- Logic Doubling®アーキテクチャを備えたAtmel® ATF15xx Complex Programmable Logic Devices (CPLD)は、IEEE Std. 1149.1 Joint Test Action Group (JTAG) インターフェイスです。この機能によりプログラミングの柔軟性が向上し、製品開発、生産、現場での使用など、さまざまな段階でメリットが得られます。このユーザー ガイドでは、以下に示す ISP サポートを備えた ATF15xx CPLD に ISP を実装するための設計方法と要件について説明します。

- ATF1502AS/ASV は、

- ATF1504AS/ASL/ASV/ASVL

- ATF1508AS/ASL/ASV/ASVL

機能と利点

インシステム プログラミングを使用すると、プリント基板 (PCB) に実装した後で ISP デバイスをプログラミングおよび再プログラミングできます。これにより、デバイスを PCB に実装する前に外部デバイス プログラマでデバイスをプログラミングするという製造プロセスで必要な余分な処理手順が不要になります。この手順が不要になることで、多ピン表面実装デバイスの繊細なリードが損傷したり、プログラミング フロー中に静電気放電 (ESD) によってデバイスが損傷する可能性が減ります。ISP を使用すると、ユーザーは ISP デバイスを PCB から取り外すことなく、設計変更やフィールド アップグレードを行うことができます。さらに、組み込みマイクロコントローラまたはインサーキット テスターを使用して ISP デバイスでインシステム プログラミング操作を実行し、これらのプログラミング操作を回路基板の製造フローに統合することもできます。

インシステムプログラミングシステム

ATF15xx CPLD の ISP システムの XNUMX つの必須コンポーネントは次のとおりです。

ソフトウェア

プログラミングアルゴリズムの実装とJの生成TAG ターゲット ISP デバイスの命令とデータ。これは、PC 上で実行されるソフトウェア プログラム、組み込みマイクロコントローラ、またはインサーキット テスト機器である可能性があります。

インターフェースハードウェア

ISP ソフトウェアとターゲット ボード上の ISP デバイス間の通信チャネル。これは、Atmel またはサードパーティ ベンダーの ISP ダウンロード ケーブルまたはプログラマ、インサーキット テスト機器、または PCB 上の組み込みマイクロコントローラと ISP デバイス間の接続である可能性があります。

ターゲットボード

JのISPデバイスを搭載した回路基板TAG チェーン。これは、AtmelのATF15xx CPLD開発/プログラマーボード、または適切なJを備えたカスタム設計の回路基板になります。TAG インターフェース ハードウェアへの接続。

これら3つのコンポーネントに加えて、JEDEC file ATF15xx CPLDをプログラムするにはこれが必要です。このJEDEC file デザインをコンパイルすることで作成できます file Atmel WinCUPLやAtmel ProChip DesignerなどのATF15xx CPLDをサポートする開発ソフトウェアを使用します。Atmelは、出力を変換するトランスレータソフトウェアユーティリティPOF2JED.exeも提供しています。 file 競合他社のプログラミングフォーマットからJEDEC file ATF15xx CPLDと互換性があります。このユーティリティの詳細については、Atmelのアプリケーションノート「ATF15xx製品ファミリー変換」を参照してください。これはAtmelのWebサイトから入手できます。 webサイト。JEDEC fileすべての ATF15xx CPLD 用に が作成され、ターゲット ボード上でプログラムできます。ATF15xx CPLD は、次のインシステム プログラミング システムによってプログラムできます。

- ATF15xx インシステムプログラミングシステム

- 組み込みマイクロコントローラ

- インサーキットテスター

Atmel ATF15xx インシステムプログラミングシステム

ATF15xx CPLD のインシステム プログラミングについては、ISP ソフトウェア、ダウンロード ケーブル、開発/プログラマー キットが Atmel から提供されており、以下のセクションで説明します。

ISP ソフトウェア

Atmel ATF15xx ISPソフトウェア、ATMISPは、Jを実装するための主な手段です。TAG ATF15xx CPLD のインシステムプログラミング。ATMISP は Windows ベースのホスト PC 上で実行され、ターゲット ISP ハードウェア システム上の ATF15xx CPLD のインシステムプログラミングを実装するか、シリアルベクター形式 (.SVF) を生成します。 file 自動テスト装置(ATE)がターゲットシステム上のATF15xx CPLDをプログラムするために使用される。ATMISPはまず、ユーザーからJに関する必要な情報をすべて取得する。TAG ターゲットシステム内のデバイスチェーン。次に適切なJTAG ISPの指示をJにTAG Jに従ってターゲットシステム内のデバイスチェーンTAG ユーザーがPCのUSBまたはLPTポート経由で指定したデバイスチェーン情報。Atmel ATMISPソフトウェアの詳細については、 www.atmel.com/tools/ATMISP.aspx.

ISP ダウンロード ケーブル

Atmel ATF15xx USBベースのISPダウンロードケーブル、ATDH1150USBは、片側をホストコンピュータの標準USBポートに接続し、もう片側をJTAG 反対側のターゲット回路基板のヘッダー。これはJTAG ホストPC上で動作するATMISPによって生成された命令とデータを、ターゲット回路基板上のISPデバイスに送信します。ATDH1150USBケーブルの詳細については、 www.atmel.com/tools/ATDH1150USB.aspx.

開発/プログラマー

Atmel ATF15xx 開発/プログラマー キット、ATF15xx-DK3-U は、ATF15xx CPLD 用の完全な開発システムおよび ISP プログラマーです。このキットは、設計者に ATF15xx ISP CPLD を使用したプロトタイプの開発と新しい設計の評価を非常に迅速かつ容易に提供します。ATF15xx CPLD で提供されるほとんどのパッケージ タイプをサポートするさまざまなソケット アダプター ボードが用意されているため、このキットは ISP プログラマーとして使用でき、J を通じて利用可能なほとんどのパッケージ タイプで ATF15xx ISP CPLD をプログラムできます。TAG インターフェース。Atmel ATF15xx-DK3-Uキットの詳細については、 www.atmel.com/tools/ATF15XX-DK3-U.aspx.

組み込みマイクロコントローラシステム

プログラミングアルゴリズムとJTAG ATF15xx CPLDの命令はマイクロコントローラまたはマイクロプロセッサに実装することができ、それを使用してターゲットボード上のATF15xx CPLDをプログラムすることができます。XNUMXつの可能な方法は、関連するJTAG プロトコル情報(例:JTAG SVFからの指示とデータ file ATMISPソフトウェアによって生成され、この情報を使用して、Jを生成するマイクロコントローラまたはマイクロプロセッサのコードを実装します。TAG JのISPデバイス用の信号TAG チェーン。このアプローチは、すでにマイクロコントローラまたはマイクロプロセッサが組み込まれているシステムに最適であり、外部のシステム内プログラミング ソフトウェアおよびハードウェア ツールを使用する必要がありません。

インサーキットテストシステム

ATF15xx CPLDは、Jを介してターゲット回路基板上でプログラムすることができます。TAG インサーキットテスターを使用して回路基板をテストする際に、SVF file ATMISPによって生成されたものには、関連するJがすべて含まれている必要があります。TAG インサーキットテスターがターゲット回路基板上のATF15xx CPLDをプログラムするために必要なインシステムプログラミング情報。このアプローチにより、プログラミングステップをテストシステムに統合できます。tag生産フローのe。

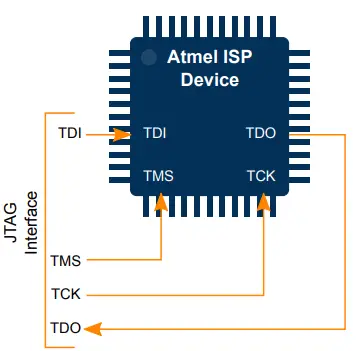

JTAG ISP インターフェース

ATF15xx CPLDのISPはIEEE 1149.1 Std. Jを使用して実装されています。TAG インターフェース。このインターフェースは、ATF15xx CPLDの消去、プログラム、検証に使用できます。JTAG インターフェースは、TCK、TMS、TDI、TDO信号とJで構成されるシリアルインターフェースです。TAG テストアクセスポート(TAP)コントローラ。TCKピンはJTAG TAPコントローラとJのシフトイン/アウトTAG 命令とデータ。TDIピンはシリアルデータ入力です。プログラミング命令とデータをISPデバイスにシフトするために使用されます。TDOピンはシリアルデータ出力です。ISPデバイスからデータをシフトアウトするために使用されます。TMSピンはモード選択ピンです。Jの状態を制御します。TAG TAPコントローラ。JTAG ISP ターゲット ボード上の ATF15xx CPLD のインターフェイス ピンは、通常 10 ピン ヘッダーを介して ISP インターフェイス ハードウェア (ISP ダウンロード ケーブルなど) に接続する必要があります。ISP インターフェイス ハードウェアは、ISP ソフトウェアを実行しているホスト PC にも接続する必要があります。ISP インターフェイス ハードウェアは、ISP ソフトウェアと ISP デバイス間の通信を確立し、ISP ソフトウェアがホスト PC から ATF15xx CPLD にプログラミング命令とデータを転送できるようにします。JTAG 機能が有効になっているのは完全にJTAG 互換性があり、Jで規定されている必要な境界スキャンテスト(BST)操作もサポートしています。TAG 標準。ATF15xx CPLDはJの一部として構成できます。TAG 他のJとのBSTチェーンTAG システムボードのインサーキットテスト用のデバイス。この機能により、ATF15xx CPLDは他のJTAGベッド・オブ・ネイルズ・テストに頼ることなく、サポートされているデバイスをテストします。

単一デバイスプログラミング

JTAG ISPインターフェースは、単一のATF15xx CPLDをプログラムするように構成できます。JTAG 単一デバイスの構成は下図の通りです。ATF15xx CPLDをこのように構成すると、デバイスのTDIピンとTDOピンの間にレジスタが現れます。レジスタのサイズはJTAG 命令幅とその命令でシフトインされるデータ。図2-1 JTAG デバイス

複数デバイスプログラミング

ATF15xx CPLDは、複数のJのデイジーチェーンの一部として構成できます。TAGサポートされているデバイスについては、以下に説明し、次の図も参照してください。

- Jの各デバイスのTMSピンとTCKピンを接続します。TAG JのTMSおよびTCKピンへのチェーンTAG 回路基板上のインターフェース ヘッダー。

- 最初のデバイスのTDIピンをJのTDIピンに接続します。TAG インターフェース ヘッダー。

- 最初のデバイスの TDO ピンを次のデバイスの TDI ピンに接続します。最後のデバイスを除くすべてのデバイスが接続されるまで、このプロセスを続けます。

- 最後のデバイスのTDOピンをJのTDOピンに接続します。TAG インターフェース ヘッダー。

図2-2 複数のデバイスJTAG 構成

J内の複数のデバイスをプログラムするにはTAG チェーンでは、ユーザーはそのような機能をサポートする ISP ソフトウェア ツールを使用する必要があります。ISP ソフトウェアでは、ユーザーは以下を指定する必要があります。

- J内のデバイスの数TAG 鎖。

- デバイスの部品番号とJ内の位置TAG 鎖。

- JTAG 各デバイスの操作。

- その他JTAGJなどの関連情報TAG 各デバイスの命令幅。

JがTAG ISPターゲットボードとISPソフトウェアでデイジーチェーンが適切に設定されている場合は、JTAG チェーンを同時にプログラムできます。

設計上の考慮事項

ATF15xx CPLDでISPを実行するには、JTAG ATF15xxのインターフェースは予約されている必要があります。したがって、TMS、TDI、TDO、およびTCKピンのXNUMXつのI/OピンはJ用に予約されている必要があります。TAG ユーザーI/Oとして使用することはできません。これらのピンのピン番号は、使用されているATF15xx CPLDとそのパッケージタイプによって異なります。ピン配置情報については、下の表を参照してください。JTAG 標準では、Jの各デバイスに対してTMSピンとTDIピンをプルアップすることを推奨しています。TAG チェーン。ATF15xx CPLDにはこれらのピン用のプルアップ機能が内蔵されており、これを有効にすると外部プルアップ抵抗が不要になります。さらに、JTAG ATF15xx CPLDでISPを実行するには、JTAG インターフェースでは、ATF15xxデザインをコンパイルする前に、特定のAtmelデバイスタイプまたはオプション設定を選択する必要があります。これらの手順は、このガイドでWinCUPL、ProChip Designer、およびPOF2JEDについて概説されています。デフォルトでは、すべての新品のATF15xx CPLDはJTAG インターフェースが有効になります。JのロジックリソースがTAG インターフェイスは予約されているため、ユーザーは ATMISP ソフトウェアを使用して、ターゲット ボード上の任意の ATF15xx CPLD をプログラム、検証、消去できます。

ヒント: 4つのJTAG ピンはJ用に予約されていますTAG インターフェースにより、ユーザーはこれらのピンに関連付けられたマクロセルに埋め込みロジック機能を実装できます。

表3-1 ATF15xx CPLD JTAG ピン番号

| JTAG ピン | 44-TQFP | 44-PLCC | 84-PLCC | 100-TQFP | 100-PQFP |

| TDI | 1 | 7 | 14 | 4 | 6 |

| TDO | 32 | 38 | 71 | 73 | 75 |

| テレメトリ | 7 | 13 | 23 | 15 | 17 |

| TCK | 26 | 32 | 62 | 62 | 64 |

Jを有効にするTAG WinCUPLとのインターフェース

Jを有効にするにはTAG WinCUPLとのインターフェースでは、デザインをコンパイルする前に適切なATF15xx ISPデバイスタイプを指定する必要があります。デザインが正常にコンパイルされると、JEDEC file JとTAG インターフェース機能が有効になっている場合、このJEDEC file ATF15xxCPLDにプログラムされており、そのJTAG インターフェースが有効になっています。ユーザーは、CUPL設計に次のプロパティステートメントを含めることで、TDIおよびTMSの内部プルアップ抵抗を有効にすることもできます。 file.

- プロパティ ATMEL {TDI_PULLUP = ON};

- プロパティ ATMEL {TMS_PULLUP = ON};

知らせ: Jを使用する設計にATF15xx ISPデバイスタイプが使用される場合TAG インターフェース ピンをロジック I/O ピンとして使用すると、WinCUPL はエラーを生成します。

次の手順では、WinCUPL で既存のデザインを開き、デバイス タイプを指定して、デザインをコンパイルする方法について説明します。

- WinCUPLのメインメニューで、 File > 開く。CUPL (.pld) ソースを選択 file 適切な作業ディレクトリから。

- [OK]を選択してPLDソースを開きます file.

- WinCUPLのメインメニューで、 File > 保存。これによりソースに加えられた変更が保存されます file.

- メイン メニューで、[オプション] > [デバイス] を選択します。これにより、[デバイスの選択] ダイアログ ボックスが開きます。

- 適切な ATF15xx ISP デバイスを選択します。WinCUPL でサポートされているすべての ATF15xx デバイス タイプの一覧については、次の表を参照してください。

- [OK] を選択して、デバイス選択メニューを閉じます。

- 注: 別の方法としては、次の表から適切なATF15xxデバイスタイプを選択し、それをCUPLソースのヘッダーセクションに含めることです。 file.

- WinCUPL メイン メニューで、[実行] > [デバイス依存コンパイル] を選択します。

- WinCUPLは設計をコンパイルし、Atmelデバイスフィッターを起動します。設計が適合すれば、JEDEC file 自動的に作成されます。

- JEDECが file デバイスにプログラムされているJTAG インターフェイス、オプションの内部 TMS および TDI プルアップ、およびオプションのピンキーパー回路が有効になります。

注記: Atmel ISPデバイスタイプを選択すると、Jが自動的に有効になります。TAG Atmel WinCUPL が Atmel デバイス フィッターを実行するときにデフォルトでインターフェイスが使用されます。

設計上、J用のリソースを確保できない場合TAG インターフェイスまたは ISP がオプションで使用されていない場合は、Atmel 非 ISP デバイス タイプを選択する必要があります。デバイスの一覧については、下の表を参照してください。デバイスは、外部デバイス プログラマを使用して再プログラムできます。下の表は、WinCUPL の Atmel ISP および Atmel 非 ISP デバイス タイプの一覧です。

表3-2 WinCUPL ATF15xxデバイスタイプ

| デバイス名 | パッケージタイプ | WinCUPL デバイスタイプ | |

| JTAG 有効 | JTAG 無効 | ||

| ATF1502AS/ASV は、 | PLCC44 | F1502ISPPLCC44 | F1502PLCC44 |

| ATF1502AS/ASV は、 | TQFP44 | F1502ISPTQFP44 | F1502TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC44 | F1504ISPPLCC44 | F1504PLCC44 |

| ATF1504AS/ASL/ASV/ASVL | TQFP44 | F1504ISPTQFP44 | F1504TQFP44 |

| ATF1504AS/ASL/ASV/ASVL | PLCC84 | F1504ISPPLCC84 | F1504PLCC84 |

| ATF1504AS/ASL/ASV/ASVL | TQFP100 | F1504ISPTQFP100 | F1504TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | PLCC84 | F1508ISPPLCC84 | F1508PLCC84 |

| ATF1508AS/ASL/ASV/ASVL | TQFP100 | F1508ISPTQFP100 | F1508TQFP100 |

| ATF1508AS/ASL/ASV/ASVL | 型番 | F1508ISPQFP100 | F1508QFP100 |

Jを有効にするTAG Atmel ProChip Designerとのインターフェース

Jを有効にするにはTAG ProChip Designerとのインターフェース:

- 適切な ProChip Designer プロジェクトを開きます。

- デバイス フィッターの下にある Atmel フィッター ボタンをクリックして、フィッター オプション ウィンドウを開きます。

- グローバルデバイスタブを選択し、JTAG ポート ボックス。TMS および TDI 内部プルアップ抵抗は、TDI Pullup および TMS Pullup ボックスをチェックすることでも有効にできます。これらのチェック ボックスは、下の図に示されています。

図3-1 ProChip Designerフィッターオプションユーザーインターフェース

Jを有効にするTAG POF2JEDとのインターフェース

POF2JEDでは、JTAG モードオプションを自動に設定すると、POF2JEDがJTAG ATF15xxの機能を有効にするかどうかは、JTAG 競合他社のCPLDではサポートされています。JをオンにするにはTAG ATF15xx CPLDでは、JTAG 競合他社のCPLDでサポートされているかどうかは、JTAG モードオプションはオンに設定する必要があります。JTAG ATF15xxでTDIとTMSの内部プルアップ抵抗を有効にするには、Enableをチェックします。

POF2JED の TDI_PULLUP および TMS_PULLUP ボックスを有効にします。下の図を参照してください。

図3-2 POF2JEDユーザーインターフェース

ガイドラインと推奨事項

注意: ATF15xx CPLDでISP操作を実行する場合は、このセクションに特に注意する必要があります。このセクションでは、JTAG よく注意すべき ISP のガイドライン、情報、推奨事項。

- Jを確認してくださいTAG J内のすべてのデバイス用のポートTAG チェーンが有効になります。

- ATF15xx CPLDの場合、JTAG デバイスが空白/消去されているか、Jでプログラムされている場合、ポートは有効になります。TAG 有効になりました。

- すべてのAtmel ATF15xxデバイスは空白/消去された状態で出荷されるため、JTAG ポートはすべての新しいデバイスに対して有効化されており、ISP に対応しています。

- ATF15xxデバイス(J付き)TAG 無効にした場合は、ISP以外のデバイスプログラマを使用して消去し、Jを再度有効にする必要があります。TAG ポート。

- 適切なVCCボリュームを確認してくださいtageはJの各デバイスに適用されますTAG 鎖。

- 15-PLCC、84-TQFP、および 100-PQFP パッケージ タイプの ATF100xxAS/ASL CPLD: VCCINT は 4.5V ~ 5.5V の範囲でなければなりませんが、VCCIO は 3.0V ~ 3.6V または 4.5V ~ 5.5V の範囲でかまいません。

- 15-PLCC および 44-TQFP パッケージ タイプの ATF44xxAS/ASL CPLD: VCC は 4.5V ~ 5.5V の範囲でなければなりません。

- ATF15xxASV/ASVL CPLD: VCC (VCCIO および VCCINT) は 3.0V ~ 3.6V の範囲にする必要があります。

- J内のデバイスのVCCTAG チェーンは適切に規制され、フィルタリングされる必要があります。

- ほとんどのアプリケーションで使用される ATF15xx CPLD では、VCC/GND ペアごとに 0.22µF のデカップリング コンデンサを XNUMX つ使用することをお勧めします。

- J内のすべてのデバイスに共通のアースを使用することをお勧めします。TAG チェーンとJTAG インターフェース ハードウェア (例: ATDH1150USB ISP ダウンロード ケーブル)。

- 長時間(5台以内)の使用は避けることをお勧めします。TAG チェーン。

- 長いJの場合TAG チェーンが必要な場合は、5 つ目のデバイスごとに TMS 信号と TCK 信号をバッファリングします。シュミット トリガー バッファの使用が推奨されます。

- バッファは、TMS 信号と TCK 信号の立ち上がり時間と立ち下がり時間を再形成します。

- バッファによって発生する追加の遅延を考慮する必要があります。

- TMSおよびTDI信号にはプルアップ抵抗(4.7KΩ~10KΩ)を使用し、TCK信号にはプルダウン抵抗をJで使用することをお勧めします。TAG ヘッダーは、これらの信号がインターフェース ハードウェアによって駆動されていないときにフローティング状態になるのを防ぎます。

- ATF15xx CPLD では、TMS および TDI のオプションの内部プルアップが利用できます。

- Jを終了することをお勧めしますTAG Jの信号TAG ヘッダ。

- アクティブ終端とパッシブ終端の両方が許容されますが、パッシブ終端が推奨されます。

- ケーブル/PCB トレースの長さが長いことによるリンギングを軽減します。

- TMS と TCK の場合、終了は最も重要です。

- J内のデバイスのすべての入力とI/OをTAG チェーン(Jを除く)TAG ノイズを最小限に抑えるために、ATF15xx CPLD をプログラムしているときは、ピンは静的状態である必要があります。

- Atmel ATF15xx 開発/プログラマー ボードのいずれかを使用する場合、VCC 選択ジャンパーの位置を変更するときは、ボードの電源をオフにする必要があります。

- ATF15xx CPLDの場合、JTAG ISP は、部品がピン制御のパワーダウン モードにあるとき、または「低電力」デバイスがスリープ状態のときに使用できます。

- ISP 中断後のデバイスの状態:

- ISP が中断されると、ピンキーパー回路の状態に関係なく、すべての I/O ピンがトライステートになります。

- 部分的にプログラムされたデバイスが回路基板上の他のデバイスとバス競合を起こすのを防ぎます。

- ISP プログラミング中、すべての I/O ピンは次のいずれかの状態になります。

- ハイインピーダンス状態:

- 空白/消去済みのデバイスがプログラムされる場合。

- ピンキーパー回路を無効にしてデバイスを再プログラムした場合。

- 回路基板上の ATF15xx CPLD とインターフェースする外部デバイスとのバス競合を防止します。

- 以前の状態に弱くラッチされます:

- プログラムされたデバイスが、ピンキーパー回路を有効にして再プログラムされる場合。

- I/O ピンは ISP 前のロジック レベルを保持します。

- ISP がシステム ボード上の他のデバイスの動作に影響を与えないようにします。

- 複数のJの使用TAG 1 つのボード上でチェーンを張ることはお勧めしません。

- デバイスは異なるJ間で相互作用する可能性があるTAG チェーン。

- ボードは、すべてのJのすべてのデバイスが機能している場合にのみ機能します。TAG チェーンは正常にプログラムされました。

- チェーン内の少なくとも1つのデバイスでプログラミングが失敗し、他のJTAG チェーンは正常にプログラムされました:

- トライステート出力のバス競合問題により、Atmel またはボード上の他のデバイスが損傷する可能性があります。

- システム ボードの動作状態が未定義であるため、誤った機能動作が発生する可能性があります。

- J間にアクティブ回路を挿入するTAG ヘッダーとJTAG チェーン内のデバイスは推奨されません。アクティブ回路が誤動作した場合、プログラミング/検証の問題が発生する可能性があります。

- 混合ボリュームの使用tageデバイスJTAG チェーンは推奨されません。

- これらはJTAG 異なるVCCボリュームを使用するデバイスとのチェーンtagesおよび/またはインターフェースボリュームtages。

- インターフェースボリュームtag5.0Vデバイスの電圧レベル(VIL、VIH、VOL、VOH)は、インターフェース電圧と互換性がない可能性があります。tag3.0V デバイスの e レベル。

- ATMISPがJとの通信に問題がある場合TAG デバイスのハードウェアチェーンの場合は、セルフキャリブレーションまたは手動キャリブレーションを実行してJの周波数を下げてみてください。TAG 信号。

- プログラミングを開始する前に、ATDH1150USB ケーブルの LED がオンになっていて緑色になっていることを確認してください。ISP ダウンロード ケーブルが ATMISP ソフトウェアと適切に通信できることを確認してください。

- 適切なVCCボリュームを確認してくださいtagATDH1150USBケーブルにeが適用されます。

- Jの最初のデバイスで使用されるVCCTAG チェーンは1150ピンJのピン4を介してATDH10USBケーブルに供給される必要がある。TAG ヘッダ。

- VCCINT と VCCIO が別々になっている ATF15xx CPLD の場合、ATDH1150USB ケーブルには VCCIO を使用する必要があります。

注文情報

| 注文コード | 説明 |

| ATF15xx-DK3-U | CPLD 開発/プログラマー キット (ATF15xxDK3-SAA44 および ATDH1150USB または ATDH1150USB-K を含む) |

| ATF15xxDK3-SAA100 | DK100 ボード用 3 ピン TQFP ソケット アダプタ ボード |

| ATF15xxDK3-SAJ44 | DK44 ボード用 3 ピン PLCC ソケット アダプタ ボード |

| ATF15xxDK3-SAJ84 | DK84 ボード用 3 ピン PLCC ソケット アダプタ ボード |

| ATF15xxDK3-SAA44 | DK44 ボード用 3 ピン TQFP ソケット アダプタ ボード |

| ATDH1150USB | Atmel ATF15xx CPLD USBベースJTAG ISP ダウンロード ケーブル |

改訂履歴

| Doc。 牧師 | 日付 | コメント |

| A | 12/2015 | 最初のドキュメントリリース。 |

連絡先

アトメル株式会社

- 1600 Technology Drive、サンノゼ、CA 95110 USA

- T:(+1)(408)441.0311

- ファックス: (+1)(408) 436.4200

- ウェブサイト

© 2015 Atmel Corporation. / Rev.: Atmel-8968A-CPLD-ATF-ISP_ユーザーガイド-12/2015

Atmel®、Atmel のロゴとその組み合わせ、Enabling Unlimited Possibilities® などは、米国およびその他の国における Atmel Corporation の登録商標または商標です。その他の用語および製品名は他社の商標である場合があります。

免責事項: この文書の情報は、Atmel 製品に関連して提供されています。 禁反言またはその他の方法による明示的または黙示的なライセンスは、この文書によって、または Atmel 製品の販売に関連して付与されるものではありません。 ATMEL での販売に関する ATMEL 利用規約に規定されている場合を除きます。 WEB当サイトに関して、ATMEL はいかなる責任も負わず、商品性、特定目的への適合性、非侵害に対する黙示の保証を含むがこれに限定されない、その製品に関する明示、黙示、法定の保証を否認します。いかなる場合も、ATMEL は、このドキュメントの使用または使用不能から生じる直接的、間接的、結果的、懲罰的、特別、または偶発的な損害 (逸失利益、事業中断、または情報損失を含むがこれに限定されない) について、たとえ ATMEL がそのような損害の可能性を知らされていたとしても、一切の責任を負いません。Atmel は、このドキュメントの内容の正確性または完全性に関していかなる表明または保証も行いません。また、仕様および製品の説明を予告なくいつでも変更する権利を留保します。Atmel は、ここに含まれる情報を更新する義務を負いません。特に別途規定がない限り、Atmel 製品は自動車用途には適しておらず、自動車用途で使用しないでください。 Atmel 製品は、生命の支援または持続を目的としたアプリケーションのコンポーネントとして使用することを意図しておらず、承認も保証もされていません。安全性が極めて重要な、軍事および自動車アプリケーションに関する免責事項: Atmel 製品は、Atmel 役員の明確な書面による同意がない限り、製品の故障が重大な人身傷害または死亡につながることが合理的に予想されるアプリケーション (「安全性が極めて重要なアプリケーション」) 向けには設計されておらず、そのようなアプリケーションに関連して使用されることはありません。安全性が極めて重要なアプリケーションには、生命維持装置およびシステム、原子力施設および兵器システムの運用のための装置またはシステムが含まれますが、これらに限定されません。Atmel 製品は、Atmel によって軍事グレードとして明示的に指定されていない限り、軍事または航空宇宙アプリケーションまたは環境での使用を目的として設計されていません。Atmel 製品は、Atmel によって自動車グレードとして明示的に指定されていない限り、自動車アプリケーションでの使用を目的として設計されていません。

ドキュメント / リソース

|

Atmel ATF15xx 複合プログラマブルロジックデバイス [pdf] ユーザーガイド ATF15xx、ATF15xx 複合プログラマブル ロジック デバイス、複合プログラマブル ロジック デバイス、プログラマブル ロジック デバイス、ロジック デバイス、デバイス |