MICROCHIP SAMRH71 – Programmierung der Evaluierungskits für die externe Speicherfamilie

Technische Daten

- Produktname: Evaluierungskits der SAMRH-Familie

- Externer Speicher: Flash-Speicher

- Speichergeräte:

- SAMRH71F20-EK:

- Speichergerät: SST39VF040

- Größe: 4 Mbit

- Organisiert als: 512K x 8

- Zugeordnet von: 0x6000_0000 bis 0x6007_FFFF

- SAMRH71F20-TFBGA-EK:

- Speichergerät: SST38VF6401

- Größe: 64 Mbit

- Organisiert als: 4M x 16

- Zugeordnet von: 0x6000_0000 bis 0x607F_FFFF

- SAMRH707F18-EK:

- Speichergerät: SST39VF040

- Größe: 4 Mbit

- Organisiert als: 512K x 8

- Zugeordnet von: 0x6007_FFFF

- SAMRH71F20-EK:

Anweisungen zur Produktverwendung

Voraussetzungen

Dieses Example läuft auf den unten aufgeführten Versionen:

Implementierung des externen Startspeichers

Die SAMRH-Evaluierungsplatinen enthalten externe Flash-Speicher, die mit den NCS0-Chip-Select-Signalen verbunden sind. NCS0 wird im HEMC beim Zurücksetzen auf den Speicherbereich 0x6000_0000 konfiguriert. Dieser Speicherbereich kann über BOOT_MODE-Auswahlpins auf die Boot-Speicheradresse gespiegelt werden.

Speichergerätefunktionen

In der folgenden Tabelle finden Sie Einzelheiten zum externen Flash-Speicher für jedes Evaluierungskit:

| Evaluierungskits | Speichergeräte | Größe | Organisiert als | Zugeordnet von | Zugeordnet zu |

|---|---|---|---|---|---|

| SAMRH71F20-EK | SST39VF040 | 4 Mbit | 512K x 8 | 0x6000_0000 | 0x6007_FFFF |

Hardwareeinstellungen

Dieser Abschnitt enthält die DIP-Schalterkonfigurationen für den Prozessor zum Booten vom externen Speicher.

SAMRH71F20-EK DIP-Schalterkonfiguration

Der Prozessor bootet vom externen Flash-Speicher mit einer konfigurierbaren Datenbusbreite von 8 Bit.

Häufig gestellte Fragen

F: Woher weiß ich, ob meine Karte so konfiguriert ist, dass sie vom externen Speicher bootet?

A: Überprüfen Sie die DIP-Schaltereinstellungen entsprechend den im Benutzerhandbuch angegebenen Konfigurationen. Stellen Sie sicher, dass die Datenbusbreite für Ihr Evaluierungskit richtig eingestellt ist.

Programmieren des externen Speichers von Evaluierungskits der SAMRH-Familie mit MPLAB-X und SAMBA-Speicherhandlern

Einführung

In diesem Anwendungshinweis wird erläutert, wie MPLAB-X IDE in die Lage versetzt wird, den in den Evaluierungskits der SAMRH-Familie eingebetteten externen Boot-Speicher zu programmieren und zu debuggen. Diese Funktion wird durch SAMBA-Speicherhandler bereitgestellt, die von MPLAB-X IDE aufgerufen werden.

In diesem Dokument werden kurz die Schritte zum Einrichten von MPLAB-X IDE-Projekten beschrieben, die vom externen Speicher ausgeführt werden müssen. Projekte können von Grund auf neu erstellt oder aus vorhandenen Projekten aufgebaut werden.

Voraussetzungen

Dieses Example läuft auf den unten aufgeführten Versionen:

- MPLAB v6.15 oder spätere Versionen

- SAMRH71 DFP-Pakete v2.6.253 oder spätere Versionen

- SAMRH707 DFP-Paket v1.2.156 oder spätere Versionen

Implementierung des externen Startspeichers

Die SAMRH-Evaluierungskarten enthalten externe Flash-Speicher, die mit den NCS0-Chip-Select-Signalen verbunden sind. NCS0 wird im HEMC beim Zurücksetzen auf den Speicherbereich 0x6000_0000 konfiguriert. Dieser Speicherbereich 0x6000_0000 kann beim Zurücksetzen über die BOOT_MODE-Auswahlpins so ausgewählt werden, dass er auf die Boot-Speicheradresse 0x0000_0000 gespiegelt wird, siehe die entsprechenden Gerätedatenblätter.

In der folgenden Tabelle finden Sie Einzelheiten zum externen Flash-Speicher für jedes Evaluierungskit.

Tabelle 2-1. Speichergerätefunktionen

| Evaluierungskits | SAMRH71F20-EK | SAMRH71F20-TFBGA-EK | SAMRH707F18-EK |

| Speichergeräte | SST39VF040 | SST38VF6401 | SST39VF040 |

| Größe | 4 Mbit | 64 Mbit | 4 Mbit |

| Organisiert als | 512K x 8 | 4M x 16 | 512K x 8 |

| Zugeordnet von | 0x6000_0000 | ||

| Zu | 0x6007_FFFF | 0x607F_FFFF | 0x6007_FFFF |

Die mitgelieferten SAMBA-Speicherhandler wurden entwickelt, um Daten und Code in diese externen Flash-Speichergeräte zu laden und dabei die in der obigen Tabelle aufgeführten Bedingungen zu erfüllen.

Hardwareeinstellungen

In diesem Abschnitt finden Sie die DIP-Schalterkonfigurationen, die auf den Karten angewendet werden müssen, damit der Prozessor vom externen Speicher booten kann. Die DIP-Schalterkonfiguration wurde gemäß der folgenden Konvention implementiert:

- Die Stellung OFF erzeugt eine logische 1

- Die Position ON erzeugt eine logische 0

SAMRH71F20-EK

Bei diesem Kit bootet der Prozessor vom externen Flash-Speicher mit einer konfigurierbaren Datenbusbreite, die auf 8 Bit eingestellt werden muss.

Die folgende Tabelle enthält Einzelheiten zur vollständigen Einstellung des DIP-Schalters.

Tabelle 3-1. SAMRH71F20-EK-Einstellungen

| SAMRH71F20 Prozessor | SAMRH71F20 EK | ||||

| PIN-Nummern | Pin-Namen | Funktion | Optionen | Auswahl | Erforderliche Konfiguration |

| PF24 | Boot-Modus | Wählt den Speicherstart | 0: Interner Flash | Externer Blitz | SW5-1 = 1 (AUS) |

| 1: Externer Blitz | |||||

| PG24 | CFG0 | Wählt die Datenbusbreite nur für die NSC0-Chipauswahl | CFG[1:0] = 00: 8 Bit | 8 Bit | SW5-2 = 0 (EIN) |

| CFG[1:0] = 01: 16 Bit | |||||

| PG25 | CFG1 | CFG[1:0] = 10: 32 Bit | SW5-3 = 0 (EIN) | ||

| CFG[1:0] = 11:

reserviert |

|||||

| PG26 | CFG2 | Wählt die HECC Aktivierung/Deaktivierung für alle NCSx | 0: HECC aus | HECC aus | SW5-4 = 0 (EIN) |

| 1: HECC Ein | |||||

| PC27 | CFG3 | Wählt den angewendeten HECC-Codekorrektor aus für alle NCSx | 0: Hamming | Hamming | SW5-5 = 0 (EIN) |

| 1: BCH | |||||

| Nicht verbunden | SW5-6 = „Ist mir egal“ | ||||

SAMRH71F20 – TFBGA – EK

Bei diesem Kit bootet der Prozessor von einem externen Flash-Speicher mit einer konfigurierbaren Datenbusbreite, die fest auf 16 Bit eingestellt ist.

Die folgende Tabelle enthält Einzelheiten zur vollständigen Einstellung des DIP-Schalters.

Tabelle 3-2. SAMRH71F20-TFBGA-EK-Einstellungen

| SAMRH71F20 Prozessor | SAMRH71F20-TFBGA EK | |||||

| PIN-Nummern | Pin-Namen | Funktion | Optionen | Auswahl | Erforderliche Konfiguration | |

| PF24 | Boot-Modus | Wählt den Speicherstart | 0: Interner Flash | Externer Blitz | SW4-1 = 1 (AUS) | |

| 1: Externer Blitz | ||||||

| PG26 | CFG2 | Wählt die HECC Aktivierung/Deaktivierung für alle NCSx | 0: HECC aus | HECC aus | SW4-2 = 0 (EIN) | |

| 1: HECC Ein | ||||||

| PC27 | CFG3 | Wählt den angewendeten HECC-Codekorrektor aus für alle NCSx | 0: Hamming | Hamming | SW4-3 = 0 (EIN) | |

| 1: BCH | ||||||

| PG24 | CFG0 | Wählt die Datenbusbreite nur für die NSC0-Chipauswahl | CFG[1:0] = 00: 8 Bit | 16 Bit |

Fest verdrahtet |

PG24 = 1 (AUS) |

| CFG[1:0] = 01: 16

bisschen |

||||||

| PG25 | CFG1 | CFG[1:0] = 10: 32

bisschen |

PG25 = 0 (Ein) | |||

Notiz:

Notiz:

„1“ und „0“ sind auf dem Siebdruck der Platine vertauscht.

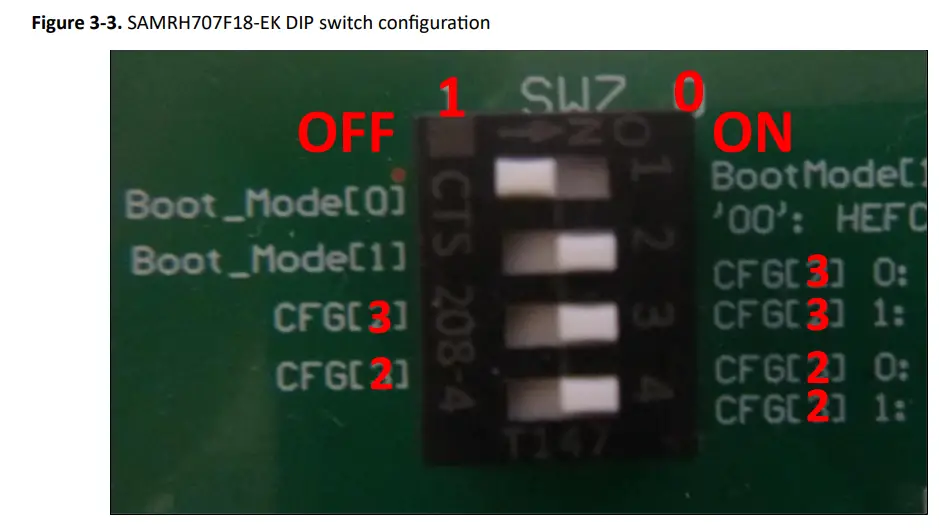

SAMRH707F18 – EK

Bei diesem Kit bootet der Prozessor von einem externen Flash-Speicher mit einer festen 8-Bit-Datenbusbreite. Die folgende Tabelle enthält Einzelheiten zur vollständigen Einstellung des DIP-Schalters.

Tabelle 3-3. SAMRH707F18-EK-Einstellungen

| SAMRH707F18 Prozessor | SAMRH707F18-EK | |||||

| PIN-Nummern | Pin-Namen | Funktion | Optionen | Auswahl | Erforderliche Konfiguration | |

| PC30 | Boot-Modus 0 | Wählt den Boot-Speicher aus | Boot-Modus [1:0] = 00: Interner Flash (HEFC) | Externer Blitz | SW7-1 = 1 (AUS) | |

| Boot-Modus [1:0 ] = 01: Externer Flash (HEMC) | ||||||

| PC29 | Boot-Modus 1 | Boot-Modus [1:0] = 1X: Internes ROM | SW7-2 = 0 (EIN) | |||

| PA19 | CFG3 | Boot-Modus [1:0] = 01 (Externer Flash) | N / A | SW7-3 = „Ist mir egal“ | ||

| Hamming-Code standardmäßig als HECC-Code-Korrektor ausgewählt für alle NCSx | Intern auf '0' gefahren | |||||

| Boot-Modus [1:0] = 1X (Internes ROM) | ||||||

| Wählt die aktive Phase aus, wenn das interne ROM aktiv ist | 0: Laufphase | |||||

| 1: Wartungsphase | ||||||

| PA25 | CFG2 | Boot-Modus [1:0] = 01 (Externer Flash) | HECC aus | SW7-4 = 0 (EIN) | ||

| Wählt die HECC Aktivierung / Deaktivierung für alle NCSx, wenn externer Blitz aktiv ist | 0: HECC aus | |||||

| 1: HECC Ein | ||||||

| Boot-Modus [1:0] = 1X (Internes ROM) | ||||||

| Wählt den Kommunikationsmodus, wenn das interne ROM aktiv ist | 0: UART-Modus | |||||

| 1: SpaceWire-Modus | Boot-Modus 0 = 0 | |||||

| LVDS-Schnittstelle | ||||||

| Boot-Modus 0 = 1 | ||||||

| TTL-Modus | ||||||

Notiz:

Notiz:

„CFG[2]“ und „CFG[3]“ sind auf dem Siebdruck der Platine invertiert.

Softwareeinstellungen

Im folgenden Abschnitt wird erläutert, wie Sie MPLAB X-Projekte für die Ausführung vom externen Speicher konfigurieren.

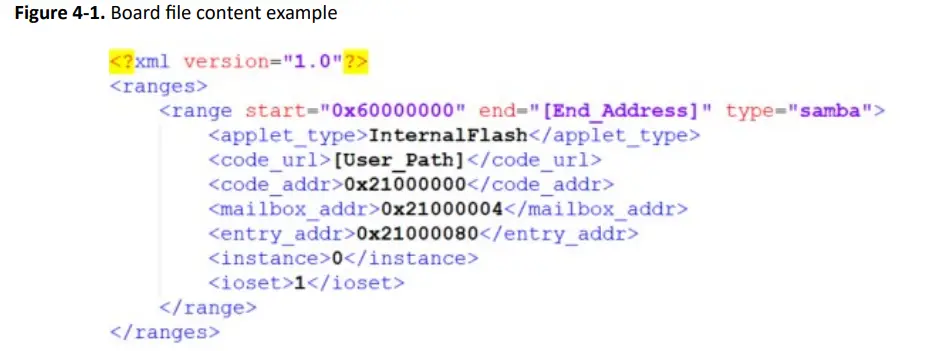

Planke file

Der Vorstand file ist ein XML file mit der Erweiterung (*.xboard), die die an SAMBA-Speicherhandler übergebenen Parameter beschreibt. Es muss im MPLAB-X-Projektordner des Benutzers abgelegt werden.

Für die SAMRH-Evaluierungskits lautet der Standardname der Platine file lautet „board.xboard“ und sein Standardspeicherort ist der Stammordner des Projekts: „ProjectDir.X“

Zwei Parameter im Board enthalten file muss vom Benutzer konfiguriert werden, damit die file kompatibel mit der Struktur der Anwendung des Benutzers.

Diese beiden Parameter sind:

- [End_Address]: Dieser Parameter bezieht sich auf die Größe des externen Boot-Speichers und definiert die letzte Adresse des Speichers.

- [User_Path]: Dieser Parameter definiert den absoluten Pfad zum Speicherort der SAMBA-Speicherhandler.

Die anderen Parameter hängen von der Implementierung des SAMBA-Speicherhandlers ab und können auf ihren Standardwerten belassen werden.

Die folgende Abbildung zeigt eine Struktur, z. B.amplinks vom Brett file.

Abbildung 4-1. Tafel file Inhalt example

Die folgende Tabelle enthält die Standardbenutzerparameter der Karte files werden mit den SAMRH-Evaluierungskits mitgeliefert.

Die folgende Tabelle enthält die Standardbenutzerparameter der Karte files werden mit den SAMRH-Evaluierungskits mitgeliefert.

Tabelle 4-1. Vorstand File Parameter

| SAMRH-Evaluierungskit | [Ende_Adresse] | [Benutzerpfad] |

| SAMRH71F20-EK | 6007_FFFFh | ${ProjectDir}\sst39vf040_loader_samba_sam_rh71_ek_sram.bin |

| SAMRH71F20-TFGBA EK | 607F_FFFFh | ${ProjectDir}\sst38vf6401_loader_samba_sam_rh71_tfbga_sram.bin |

| SAMRH707F18-EK | 6007_FFFFh | ${ProjectDir}\sst39vf040_loader_samba_sam_rh707_ek_sram.bin |

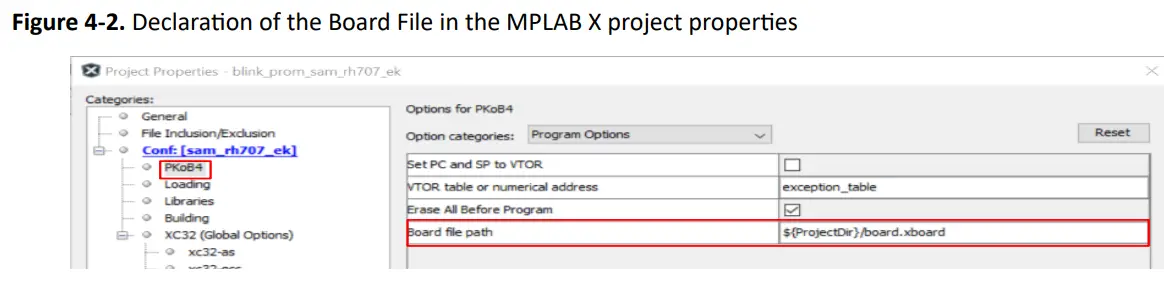

Projektkonfiguration

Planke File

Der Vorstand file muss im „Board file path“-Feld der Projekteigenschaften von MPLAB X-Projekten, wie in der folgenden Abbildung dargestellt. „Board file Das Feld „Pfad“ ist über die Optionen des Debugger-Tools zugänglich (PKoB4 in unserem Beispielample), dann wird „Programmoptionen“ aus dem Menü „Optionskategorien“ ausgewählt.

Standardmäßig ist das Board file Das Pfadfeld ist wie folgt eingestellt: ${ProjectDir}/board.xboard Wenn das Board file nicht im Ordner vorhanden ist, werden SAMBA-Speicherhandler ignoriert.

Abbildung 4-2. Erklärung des Vorstands File in den MPLAB X-Projekteigenschaften

Externer Speicher

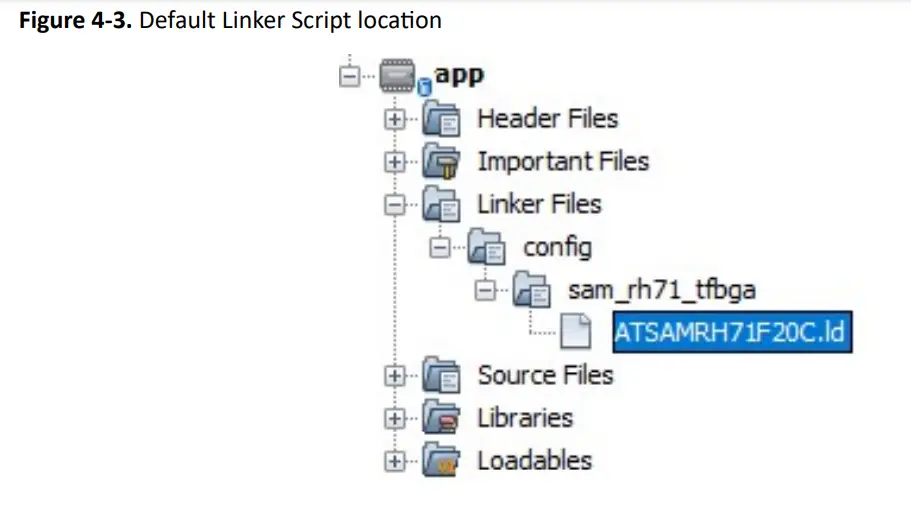

MPLAB-X Harmony 3 (MH3) sample-Projekte verwenden ein Standard-Linker-Skript, das die Anwendung so konfiguriert, dass sie vom internen Startspeicher aus ausgeführt wird.

Standardmäßig wird das Linker-Skript file „ATSAMRH71F20C.ld“ ist in Harmony-Projekten implementiert, wie in der folgenden Abbildung dargestellt.

Abbildung 4-3. Standardspeicherort des Linker-Skripts

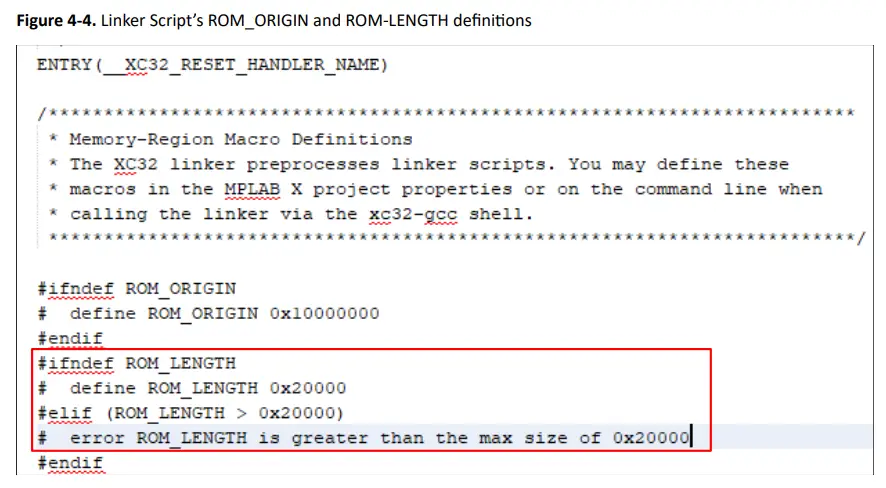

Das Linker-Skript verwendet die internen Parameter ROM_ORIGIN und ROM_LENGTH, wie in der folgenden Abbildung dargestellt, um den Speicherort und die Länge des Startspeichers zu definieren. Die Anwendung ist auf diese Parameter angewiesen, um die ausführbare Datei zu erstellen.

Die sampDas obige Linker-Skript begrenzt den Parameter ROM_LENGTH auf 0x0002_0000, was der Länge des internen Flashs entspricht, und generiert einen Kompilierungsfehler, wenn diese Bedingung nicht erfüllt ist.

Die sampDas obige Linker-Skript begrenzt den Parameter ROM_LENGTH auf 0x0002_0000, was der Länge des internen Flashs entspricht, und generiert einen Kompilierungsfehler, wenn diese Bedingung nicht erfüllt ist.

Diese Einschränkung ist jedoch möglicherweise nicht mit der Verwendung des externen Flash-Speichers vereinbar, da seine Länge größer als 0x0002_0000 sein kann.

Wenn der im externen Speicher programmierte Code kleiner als 0x0002_0000 ist, muss das Linker-Skript nicht aktualisiert werden fileWenn diese Länge jedoch überschritten wird, sollte der Parameter ROM_LENGTH aktualisiert werden, um die tatsächliche Länge des externen Speichers widerzuspiegeln.

Der Parameter ROM_ORIGIN kann auch überschrieben werden, ohne das Linker-Skript zu ändern. file.

Bevor der ROM_LENGTH-Parameter überschrieben wird, muss das Linker-Skript so bearbeitet werden, dass es Ihrer Hardwarekonfiguration entspricht.

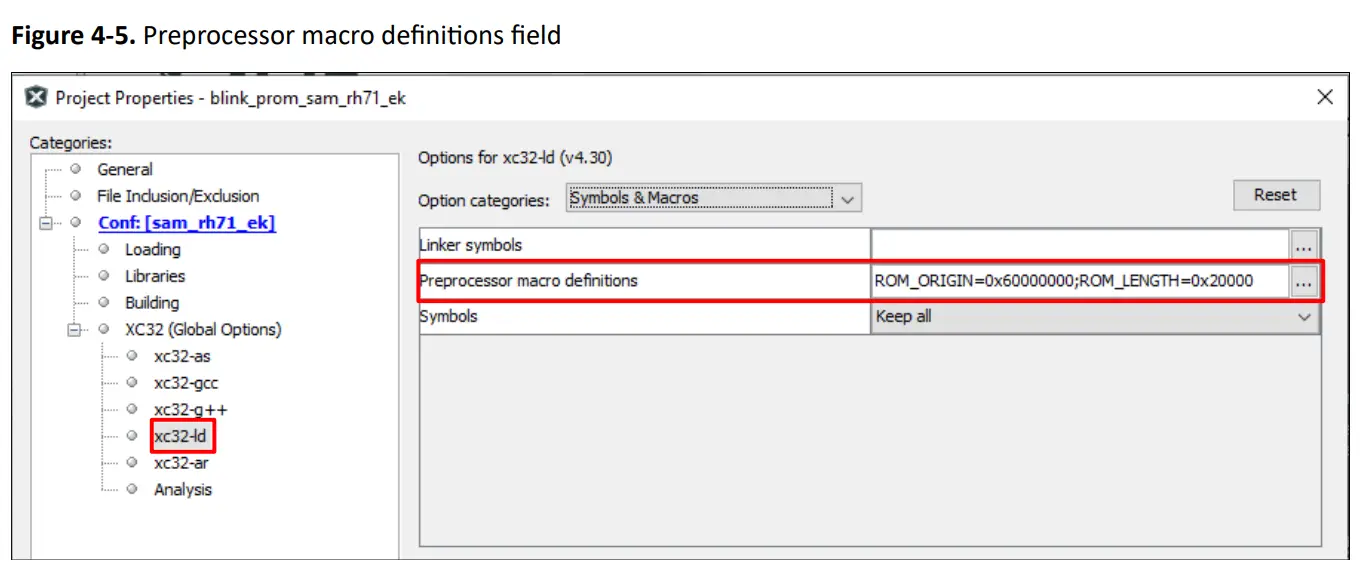

Um den ROM_LENGTH-Parameter zu überschreiben, können Sie das Feld „Präprozessor-Makrodefinitionen“ in den MPLAB-X-Projekteigenschaften verwenden. Dieses Feld kann über das Element „XC32-ld“ aufgerufen werden.

„Symbole & Makros“ können aus dem Menü „Optionskategorien“ ausgewählt werden, wie in der folgenden Abbildung gezeigt.

Zum Beispielample, für das Flash-Speichergerät SST39VF040:

Wenn ROM_LENGTH nicht geändert wurde, sollte die Länge des erstellten Codes kleiner als 0x0002_0000 sein.

- ROM_LENGTH=0x20000

- ROM_ORIGIN = 0x60000000

Wenn ROM_LENGTH auf 0x0008_0000 aktualisiert wurde, sollte die erstellte Codelänge kleiner als 0x0005_0000 sein.

- ROM_LENGTH=0x50000

- ROM_ORIGIN = 0x60000000

Softwarelieferungen

Der Mechanismus der SAMBA-Speicherhandler basiert auf binären Applets, die sich je nach Prozessorversion und implementiertem externen Boot-Speicher unterscheiden. Es gibt drei binäre Applets, die speziell für die SAMRH-Evaluierungskits verfügbar sind:

- sst39vf040_loader_samba_sam_rh71_ek_sram.bin

- sst39vf040_loader_samba_sam_rh707_ek_sram.bin

- sst38vf6401_loader_samba_sam_rh71_tfbga_sram.bin

Diese Applets werden im internen RAM des Prozessors ausgeführt und umfassen sowohl die SAMBA-Schnittstelle zur Kommunikation mit Debug-Skripten als auch die Routinen, die Programmiervorgänge (Löschen, Schreiben usw.) im externen Startspeicher ausführen.

Zur Unterstützung der SAMRH-Evaluierungskits werden drei komprimierte Softwarepakete mitgeliefert. Jedes Paket enthält:

- Das engagierte Board file

- Das dedizierte Binär-Applet file.

Kompilieren, Programmieren und Debuggen aus dem externen Boot-Speicher

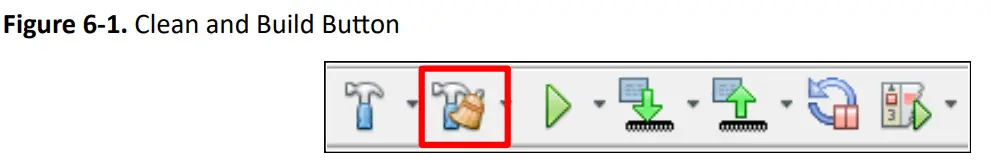

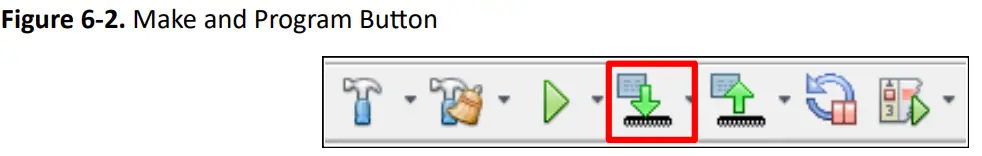

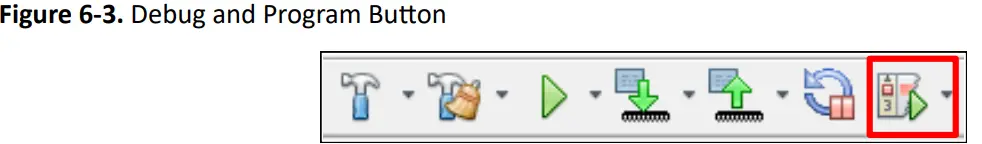

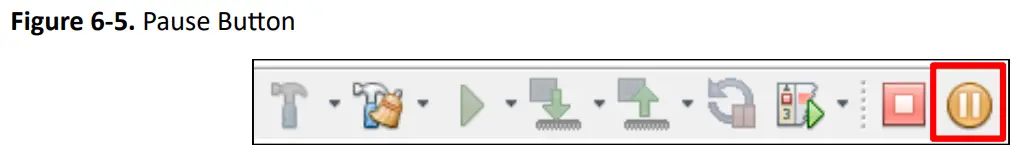

Sobald das MPLAB X-Projekt vollständig mit einem gültigen SAMBA-Speicherhandler eingerichtet wurde, kann der Benutzer dieses Projekt mithilfe der Schaltflächen und der Symbolleiste im oberen Menü im externen Startspeicher kompilieren, programmieren und debuggen, wie in den folgenden Abbildungen gezeigt.

- Klicken Sie auf „Bereinigen und erstellen“, um das Projekt zu bereinigen und zu kompilieren.

- Um die Anwendung auf dem Gerät zu programmieren, klicken Sie auf „Erstellen und Programmieren“.

- Klicken Sie zum Ausführen des Codes auf „Projekt debuggen“.

- Um den Code zu stoppen, klicken Sie auf „Debuggersitzung beenden“.

- Oder klicken Sie auf „Pause“, um es anzuhalten.

- Oder klicken Sie auf „Pause“, um es anzuhalten.

Referenz

In diesem Abschnitt sind Dokumente aufgeführt, die weitere Informationen zu den Geräten MPLAB X, SAMRH71 und SAMRH707 enthalten.

MPLAB X

MPLAB X IDE-Benutzerhandbuch, DS50002027D. https://www.microchip.com/en-us/tools-resources/develop/mplab-x-ide#tabs

SAMRH71-Gerät

- SAMRH71F20 Gerätedatenblatt, DS60001593 ww1.microchip.com/downloads/en/DeviceDoc/SAMRH71_Datasheet_DS60001593F.pdf

- SAMRH71F20-Evaluierungskit – Benutzerhandbuch, DS50002910. https://ww1.microchip.com/downloads/en/DeviceDoc/SAMRH71F20-EK-Evaluation-Kit-User-Guide-DS50002910A.pdf

- SAMRH71-TFBGA-EK Evaluierungskit – Benutzerhandbuch, DS50003449A https://ww1.microchip.com/downloads/aemDocuments/documents/AERO/ProductDocuments/UserGuides/50003449.pdf

- Erste Schritte mit dem SAMRH71F20 Evaluation Kit, DS00004008. https://ww1.microchip.com/downloads/en/Appnotes/

- Erste_Schritte_mit_dem_SAMRH71F20_Evaluation_Kit_DS00004008A.pdf

- SST38LF6401RT und SAMRH71 Referenzdesign, DS0004274 https://ww1.microchip.com/downloads/aemDocuments/documents/AERO/ApplicationNotes/ApplicationNotes/AN4274_SST38LF6401RT_SAMRH71_Reference_Design_00004274.pdf

SAMRH707-Gerät

SAMRH707F18 Gerätedatenblatt, DS60001634 https://ww1.microchip.com/downloads/aemDocuments/documents/AERO/ProductDocuments/DataSheets/SAMRH707_Datasheet_DS60001634.pdf

Erste Schritte mit dem Mikrocontroller SAMRH707F18 unter Verwendung von MPLAB-X IDE und MCC Harmony Framework, DS00004478 https://ww1.microchip.com/downloads/aemDocuments/documents/AERO/ApplicationNotes/ApplicationNotes/00004478.pdf

SAMRH707-EK Evaluierungskit – Benutzerhandbuch, DS60001744

https://ww1.microchip.com/downloads/aemDocuments/documents/AERO/ProductDocuments/UserGuides/SAMRH707_EK_Evaluation_Kit_User_Guide_60001744.pdf

SST38LF6401RT und SAMRH707 Referenzdesign, DS00004583 ww1.microchip.com/downloads/aemDocuments/documents/AERO/ApplicationNotes/ApplicationNotes/SAMRH707-SST38LF6401RT-Reference-Design-00004583.pdf

Änderungsverlauf

Der Revisionsverlauf beschreibt die Änderungen, die im Dokument vorgenommen wurden. Die Änderungen werden nach Revision aufgelistet, beginnend mit der aktuellsten Veröffentlichung.

| Revision | Datum | Beschreibung |

| A | 04/2024 | Erstrevision |

Mikrochip-Informationen

Der Mikrochip WebWebsite

Microchip bietet Online-Support über unsere webSeite unter www.microchip.com/. Das webWebsite wird verwendet, um files und Informationen für Kunden leicht zugänglich. Einige der verfügbaren Inhalte umfassen:

- Produktsupport – Datenblätter und Errata, Anwendungshinweise und sampDateiprogramme, Designressourcen, Benutzerhandbücher und Hardware-Supportdokumente, neueste Softwareversionen und archivierte Software

- Allgemeiner technischer Support – Häufig gestellte Fragen (FAQs), Anfragen zum technischen Support, Online-Diskussionsgruppen, Mitgliederliste des Microchip-Designpartnerprogramms

- Geschäft von Microchip – Produktauswahl- und Bestellleitfäden, neueste Pressemitteilungen von Microchip, Auflistung von Seminaren und Veranstaltungen, Auflistung von Microchip-Vertriebsbüros, Distributoren und Fabrikvertretern

Benachrichtigungsservice für Produktänderungen

Der Benachrichtigungsservice für Produktänderungen von Microchip hilft Kunden, die Produkte von Microchip auf dem Laufenden zu halten. Abonnenten erhalten E-Mail-Benachrichtigungen, wenn Änderungen, Aktualisierungen, Überarbeitungen oder Errata in Bezug auf eine bestimmte Produktfamilie oder ein Entwicklungstool von Interesse vorliegen.

Um sich zu registrieren, gehen Sie zu www.microchip.com/pcn und folgen Sie den Registrierungsanweisungen.

Kundenservice

Benutzer von Microchip-Produkten können über mehrere Kanäle Unterstützung erhalten:

- Vertriebshändler oder Vertreter

- Lokales Verkaufsbüro

- Ingenieur für eingebettete Lösungen (ESE)

- Technische Unterstützung

Kunden sollten sich für Unterstützung an ihren Händler, Vertreter oder ESE wenden. Lokale Verkaufsbüros stehen den Kunden ebenfalls zur Verfügung. Eine Liste der Verkaufsbüros und Standorte finden Sie in diesem Dokument.

Technischen Support erhalten Sie über die webWebsite unter: www.microchip.com/support

Codeschutzfunktion von Microchip Devices

Beachten Sie die folgenden Details zur Codeschutzfunktion bei Microchip-Produkten:

- Mikrochipprodukte erfüllen die in ihrem jeweiligen Mikrochip-Datenblatt enthaltenen Spezifikationen.

- Microchip ist davon überzeugt, dass seine Produktfamilie sicher ist, wenn sie bestimmungsgemäß, innerhalb der Betriebsspezifikationen und unter normalen Bedingungen verwendet wird.

- Microchip schätzt und schützt seine geistigen Eigentumsrechte aggressiv. Versuche, die Codeschutzfunktionen von Microchip-Produkten zu verletzen, sind streng verboten und können gegen das Digital Millennium Copyright Act verstoßen.

- Weder Microchip noch ein anderer Halbleiterhersteller kann die Sicherheit seines Codes garantieren. Codeschutz bedeutet nicht, dass wir garantieren, dass das Produkt „unknackbar“ ist. Der Codeschutz entwickelt sich ständig weiter. Microchip ist bestrebt, die Codeschutzfunktionen unserer Produkte kontinuierlich zu verbessern.

Rechtliche Hinweise

Diese Veröffentlichung und die darin enthaltenen Informationen dürfen nur mit Microchip-Produkten verwendet werden, einschließlich zum Entwerfen, Testen und Integrieren von Microchip-Produkten in Ihre Anwendung. Die Verwendung dieser Informationen auf andere Weise verstößt gegen diese Bedingungen. Informationen zu Geräteanwendungen werden nur zu Ihrer Bequemlichkeit bereitgestellt und können durch Updates ersetzt werden. Es liegt in Ihrer Verantwortung sicherzustellen, dass Ihre Anwendung Ihren Spezifikationen entspricht. Wenden Sie sich an Ihr lokales Microchip-Vertriebsbüro, um weitere Unterstützung zu erhalten, oder erhalten Sie zusätzliche Unterstützung unter www.microchip.com/en-us/support/design-help/client-support-services.

DIESE INFORMATIONEN WERDEN VON MICROCHIP „WIE BESEHEN“ BEREITGESTELLT. MICROCHIP GIBT KEINE ZUSICHERUNGEN ODER GARANTIEN JEGLICHER ART, WEDER AUSDRÜCKLICH NOCH STILLSCHWEIGEND, SCHRIFTLICH ODER MÜNDLICH, GESETZLICH ODER ANDERWEITIG, IN BEZUG AUF DIE INFORMATIONEN, EINSCHLIESSLICH, ABER NICHT BESCHRÄNKT AUF STILLSCHWEIGENDE GARANTIEN DER NICHTVERLETZUNG, MARKTGÄNGIGKEIT UND EIGNUNG FÜR EINEN BESTIMMTEN ZWECK ODER GARANTIEN IN BEZUG AUF IHREN ZUSTAND, IHRE QUALITÄT ODER LEISTUNG.

MICROCHIP HAFTET IN KEINEM FALL FÜR INDIREKTE, SPEZIELLE, STRAFENDE, ZUFÄLLIGE ODER FOLGESCHÄDEN, VERLUSTE, SCHÄDEN, KOSTEN ODER AUFWENDUNGEN JEGLICHER ART IM ZUSAMMENHANG MIT DEN INFORMATIONEN ODER IHRER VERWENDUNG, UNGEACHTET DEREN URSACHE, SELBST WENN MICROCHIP AUF DIE MÖGLICHKEIT HINGEWIESEN WURDE ODER DIE SCHÄDEN VORHERSEHBAR SIND. SOWEIT GESETZLICH ZULÄSSIG, ÜBERSTEIGT DIE GESAMTHAFTUNG VON MICROCHIP FÜR ALLE ANSPRÜCHE, DIE IN IRGENDEINER WEISE MIT DEN INFORMATIONEN ODER IHRER VERWENDUNG ZUSAMMENHÄNGEN, NICHT DEN SUMMEN DER GEBÜHREN, DIE SIE GEGEBENENFALLS DIREKT AN MICROCHIP FÜR DIE INFORMATIONEN BEZAHLT HABEN.

Die Verwendung von Microchip-Geräten in lebenserhaltenden und/oder sicherheitsrelevanten Anwendungen erfolgt ausschließlich auf Risiko des Käufers. Der Käufer verpflichtet sich, Microchip von allen Schäden, Ansprüchen, Klagen oder Kosten freizustellen, die sich aus einer solchen Verwendung ergeben. Sofern nicht anders angegeben, werden keine Lizenzen im Rahmen der geistigen Eigentumsrechte von Microchip übertragen, weder implizit noch anderweitig.

Handelsmarken

Der Name und das Logo von Microchip, das Microchip-Logo, Adaptec, AVR, AVR-Logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi-Logo, MOST, MOST-Logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32-Logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST-Logo, SuperFlash, Symmetricom , SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron und XMEGA sind eingetragene Warenzeichen von Microchip Technology Incorporated in den USA und anderen Ländern.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus-Logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider und ZL sind eingetragene Marken von Microchip Technology Incorporated in den USA.

Unterdrückung benachbarter Tasten, AKS, Analog für das digitale Zeitalter, Jeder Kondensator, AnyIn, AnyOut, Erweitertes Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamisches Durchschnittsmatching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge,

IGaT, In-Circuit-Serielles Programmieren, ICSP, INICnet, Intelligente Parallelisierung, IntelliMOS, Inter-Chip-Konnektivität, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB-zertifiziertes Logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Allwissende Codegenerierung, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serielles Quad-E/A, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-IS, storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect und ZENA sind Marken von Microchip Technology Incorporated in den USA und anderen Ländern.

SQTP ist eine Dienstleistungsmarke von Microchip Technology Incorporated in den USA

Das Adaptec-Logo, Frequency on Demand, Silicon Storage Technology und Symmcom sind eingetragene Warenzeichen von Microchip Technology Inc. in anderen Ländern.

GestIC ist in anderen Ländern eine eingetragene Marke der Microchip Technology Germany II GmbH & Co. KG, einer Tochtergesellschaft der Microchip Technology Inc.

Alle anderen hier erwähnten Marken sind Eigentum der jeweiligen Unternehmen.

© 2024, Microchip Technology Incorporated und seine Tochtergesellschaften. Alle Rechte vorbehalten.

ISBN: 978-1-6683-4401-9

Qualitätsmanagementsystem

Informationen zu den Qualitätsmanagementsystemen von Microchip finden Sie unter www.microchip.com/quality.

Weltweiter Vertrieb und Service

| AMERIKA | ASIEN/PAZIFIK | ASIEN/PAZIFIK | EUROPA |

| Firmensitz

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technische Unterstützung: www.microchip.com/support Web Adresse: www.microchip.com Atlanta Duluth, Georgia Tel: 678-957-9614 Fax: 678-957-1455 Austin, Texas Tel: 512-257-3370 Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088 Chicago Itasca, Illinois Tel: 630-285-0071 Fax: 630-285-0075 Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924 Detroit Novi, Michigan Tel: 248-848-4000 Houston, Texas (Bundesstaat) Tel: 281-894-5983 Indianapolis Noblesville, IN Tel.: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380 Los Angeles Mission Viejo, CA Tel.: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800 Raleigh, North Carolina Tel: 919-844-7510 New York, NY Tel: 631-435-6000 San Jose, Kalifornien Tel: 408-735-9110 Tel: 408-436-4270 Kanada – Toronto Tel: 905-695-1980 Fax: 905-695-2078 |

Australien – Sydney

Tel: 61-2-9868-6733 China – Peking Tel: 86-10-8569-7000 China – Chengdu Tel: 86-28-8665-5511 China – Chongqing Tel: 86-23-8980-9588 China – Dongguan Tel: 86-769-8702-9880 China – Guangzhou Tel: 86-20-8755-8029 China – Hangzhou Tel: 86-571-8792-8115 China – Sonderverwaltungszone Hongkong Tel: 852-2943-5100 China – Nanjing Tel: 86-25-8473-2460 China – Qingdao Tel: 86-532-8502-7355 China – Shanghai Tel: 86-21-3326-8000 China – Shenyang Tel: 86-24-2334-2829 China – Shenzhen Tel: 86-755-8864-2200 China – Suzhou Tel: 86-186-6233-1526 China – Wuhan Tel: 86-27-5980-5300 China – Xi’an Tel: 86-29-8833-7252 China – Xiamen Tel: 86-592-2388138 China – Zhuhai Tel: 86-756-3210040 |

Indien – Bangalore

Tel: 91-80-3090-4444 Indien – Neu-Delhi Tel: 91-11-4160-8631 Indien – Pune Tel: 91-20-4121-0141 Japan – Ōsaka Tel: 81-6-6152-7160 Japan – Tokio Tel: 81-3-6880-3770 Korea – Daegu Tel: 82-53-744-4301 Korea – Seoul Tel: 82-2-554-7200 Malaysia - Kuala Lumpur Tel: 60-3-7651-7906 Malaysia – Penang Tel: 60-4-227-8870 Philippinen – Manila Tel: 63-2-634-9065 Singapur Tel: 65-6334-8870 Taiwan – Hsin Chu Tel: 886-3-577-8366 Taiwan – Kaohsiung Tel: 886-7-213-7830 Taiwan – Taipeh Tel: 886-2-2508-8600 Thailand – Bangkok Tel: 66-2-694-1351 Vietnam – Ho Chi Minh Tel: 84-28-5448-2100 |

Österreich – Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Dänemark – Kopenhagen Tel: 45-4485-5910 Fax: 45-4485-2829 Finnland – Espoo Tel: 358-9-4520-820 Frankreich – Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Deutschland – Garching Tel: 49-8931-9700 Deutschland – Haan Tel: 49-2129-3766400 Deutschland – Heilbronn Tel: 49-7131-72400 Deutschland – Karlsruhe Tel: 49-721-625370 Deutschland – München Tel: 49-89-627-144-0 Fax: 49-89-627-144-44 Deutschland – Rosenheim Tel: 49-8031-354-560 Israel – Ra’anana Tel: 972-9-744-7705 Italien – Mailand Tel: 39-0331-742611 Fax: 39-0331-466781 Italien – Padua Tel: 39-049-7625286 Niederlande – Drunen Tel: 31-416-690399 Fax: 31-416-690340 Norwegen – Trondheim Tel: 47-72884388 Polen – Warschau Tel: 48-22-3325737 Rumänien – Bukarest Tel: 40-21-407-87-50 Spanien – Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 Schweden – Göteborg Tel: 46-31-704-60-40 Schweden – Stockholm Tel: 46-8-5090-4654 Großbritannien – Wokingham Tel: 44-118-921-5800 Fax: 44-118-921-5820 |

Anwendungshinweis

© 2024 Microchip Technology Inc. und seine Tochtergesellschaften

Dokumente / Ressourcen

|

MICROCHIP SAMRH71 – Programmierung der Evaluierungskits für die externe Speicherfamilie [pdf] Benutzerhandbuch SAMRH71, SAMRH71 Programmierung der externen Speicherfamilie Evaluierungskits, Programmierung der externen Speicherfamilie Evaluierungskits, Externer Speicherfamilie Evaluierungskits, Familie Evaluierungskits, Evaluierungskits, Kits |