MICROCHIP SAMRH71 Programming the External Memory Family Evaluation Kits

# MICROCHIP SAMRH71 Programming the External Memory Family Evaluation Kits User Guide

Home » MICROCHIP SAMRH71 Programming the External Memory Family Evaluation Kits User Guide ♥

#### **Contents**

- 1 MICROCHIP SAMRH71 Programming the External Memory Family Evaluation Kits

- **2 Product Usage Instructions**

- 3 Introduction

- **4 Prerequisites**

- **5 External Boot Memory Implementation**

- 6 Hardware Settings

- 7 Software Settings

- **8 Software Deliveries**

- 9 Reference

- 10 Revision History

- 11 Microchip Information

- 12 Worldwide Sales and Service

- 13 Documents / Resources

- 13.1 References

- **14 Related Posts**

MICROCHIP SAMRH71 Programming the External Memory Family Evaluation Kits

# **Specifications**

• Product Name: SAMRH Family Evaluation Kits

• External Memory: Flash Memory

• Memory Devices:

• SAMRH71F20-EK:

Memory Device: SST39VF040

• Size: 4 Mbit

o Organized as: 512K x 8

Mapped from: 0x6000\_0000 to 0x6007\_FFFF

• SAMRH71F20-TFBGA-EK:

Memory Device: SST38VF6401

• Size: 64 Mbit

o Organized as: 4M x 16

Mapped from: 0x6000\_0000 to 0x607F\_FFFF

• SAMRH707F18-EK:

Memory Device: SST39VF040

• Size: 4 Mbit

o Organized as: 512K x 8

Mapped from: 0x6007\_FFFF

# **Product Usage Instructions**

#### **Prerequisites**

This example runs on the versions listed below:

#### **External Boot Memory Implementation**

The SAMRH evaluation boards contain external flash memories connected to the NCS0 chip-select signals. NCS0 is configured in the HEMC to the 0x6000\_0000 memory area at reset. This memory area can be mirrored to the Boot memory address via BOOT MODE selection pins.

#### **Memory Devices Features**

The following table provides details about external flash memory for each evaluation kit:

| Evaluation Kits | Memory Devices | Size   | Organised as | Mapped from | Mapped to   |

|-----------------|----------------|--------|--------------|-------------|-------------|

| SAMRH71F20-EK   | SST39VF040     | 4 Mbit | 512K x 8     | 0x6000_0000 | 0x6007_FFFF |

#### **Hardware Settings**

This section provides the DIP switch configurations for the processor to boot from external memory.

#### SAMRH71F20-EK DIP Switch Configuration

The processor boots from external flash memory with a configurable data bus width set to 8-bit.

#### **FAQ**

#### Q: How do I know if my board is configured to boot from external memory?

A: Check the DIP switch settings according to the provided configurations in the user manual. Ensure the data bus width is correctly set for your evaluation kit.

Programming the External Memory of SAMRH Family Evaluation Kits using MPLAB-X with SAMBA Memory Handlers

#### Introduction

This application note explains how to make MPLAB-X IDE capable of programing and debugging the external boot memory embedded in the SAMRH family evaluation kits. This capability is provided by SAMBA Memory Handlers that are called from MPLAB-X IDE.

This document briefly describes the steps to set up MPLAB-X IDE projects that need to run from the external memory. Projects can be created from scratch or built from existing ones.

## **Prerequisites**

This example runs on the versions listed below:

- MPLAB v6.15, or later versions

- SAMRH71 DFP packs v2.6.253, or later versions

- SAMRH707 DFP pack v1.2.156, or later versions

## **External Boot Memory Implementation**

The SAMRH evaluation boards contain external flash memories which are connected to the NCS0 chip-select signals. NCS0 is configured in the HEMC to the 0x6000\_0000 memory area at reset. This 0x6000\_0000 memory area can be selected to be mirrored to the 0x0000\_0000 Boot memory address via the BOOT\_MODE selection pins at reset, see the relevant device datasheets.

The following table provides details about external flash memory for each evaluation kit.

**Table 2-1. Memory Devices Features**

| Evaluation Kits | SAMRH71F20-EK | SAMRH71F20-TFBGA-E<br>K | SAMRH707F18-EK |  |

|-----------------|---------------|-------------------------|----------------|--|

| Memory Devices  | SST39VF040    | SST38VF6401             | SST39VF040     |  |

| Size            | 4 Mbit        | 64 Mbit                 | 4 Mbit         |  |

| Organised as    | 512K x 8      | 4M x 16                 | 512K x 8       |  |

| Mapped from     | 0x6000_0000   |                         |                |  |

| То              | 0x6007_FFFF   |                         | 0x6007_FFFF    |  |

The supplied SAMBA memory handlers have been developed to load data and code into these external flash memory devices while complying with the conditions exposed in the table above.

# **Hardware Settings**

This section provides the DIP switch configurations that must be applied to the boards for the processor to boot from the external memory. The DIP switch configuration has been implemented according to the following convention:

- The OFF position generates a logic 1

- The ON position generates a logic 0

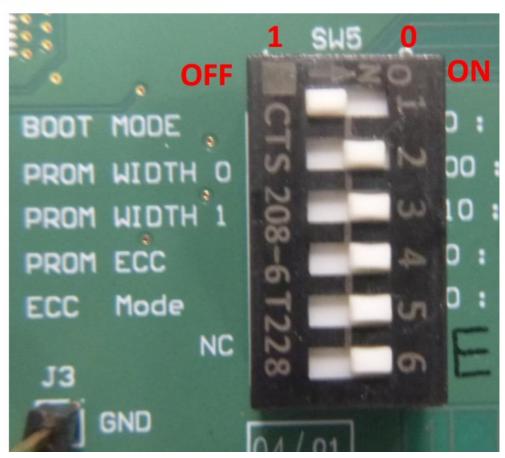

## SAMRH71F20-EK

On this kit the processor boots from external flash memory with a configurable data bus width that must be set to 8-bit.

The following table provides details about complete setting of the DIP switch.

## Table 3-1. SAMRH71F20-EK Settings

| SAMRH71F        | 20 Process    | SAMRH71F20 EK                                                     |                           |                  |                            |

|-----------------|---------------|-------------------------------------------------------------------|---------------------------|------------------|----------------------------|

| Pin Numb<br>ers | Pin Nam<br>es | Function                                                          | Options                   | Selection        | Required Confi<br>guration |

| PF24            | Boot Mo       | Soot Mo Selects the memory boot                                   | 0: Internal Flash         | External Flas    | SW5-1 = 1 (OFF)            |

| 1127            | de            | Selects the memory boot                                           | 1: External Flash         | h                | 3003-1 - 1 (011)           |

| PG24 CFC        | CECO          | Selects the data bus width just for NSC0 chip select              | CFG[1:0] = 00: 8<br>bit   | 8 bit            | SW5-2 = 0 (ON)             |

|                 | Ol Go         |                                                                   | CFG[1:0] = 01: 1<br>6 bit |                  |                            |

|                 | CFG1          |                                                                   | CFG[1:0] = 10: 3<br>2 bit |                  | SW5-3 = 0 (ON)             |

| PG25            |               |                                                                   | CFG[1:0] = 11:            |                  |                            |

|                 |               |                                                                   | reserved                  |                  |                            |

| PG26            | CFG2          | Selects the HECC activation/ d                                    | 0: HECC Off               | 11500.0%         | SW5-4 = 0 (ON)             |

| PG26            | GFG2          | eactivation for all NCSx                                          | 1: HECC On                | HECC Off         |                            |

| PC27            | CEC2          | CFG3 Selects the HECC code correct or applied <b>for all</b> NCSx | 0: Hamming                | - Hamming        | SW5-5 = 0 (ON)             |

| 7021            | GFG3          |                                                                   | 1: BCH                    |                  |                            |

|                 |               |                                                                   |                           | Not<br>Connected | SW5-6 = "Don't c are"      |

Figure 3-1. SAMRH71F20-EK DIP switch configuration

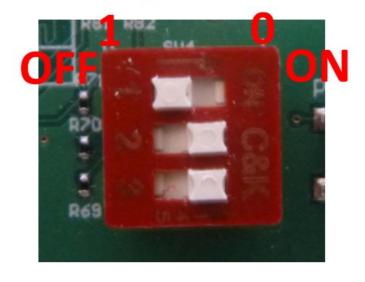

#### SAMRH71F20 - TFBGA - EK

On this kit the processor boots from external flash memory with a configurable data bus width that has been hardwired to 16-bit.

The following table provides details about complete setting of the DIP switch.

Table 3-2. SAMRH71F20-TFBGA-EK Settings

| SAMRH71F20 Processor |         |                                                                 | SAMRH71F20-TFBGA EK     |                         |                        |                    |

|----------------------|---------|-----------------------------------------------------------------|-------------------------|-------------------------|------------------------|--------------------|

| Pin Numb<br>ers      | Pin Nam | Function                                                        | Options                 | Selection               | Required Configuration |                    |

|                      | Boot Mo |                                                                 | 0: Internal Flash       | Enternal El             |                        |                    |

| PF24 Boot Mo         |         | Selects the memory boot                                         | 1: External Flas<br>h   | External FI<br>ash      | SW4-1 = 1 (OFF)        |                    |

| PG26                 | CFG2    | Selects the HECC activation                                     | 0: HECC Off             | HECC Off SW4-2 = 0 (ON) |                        | ) (ON)             |

| PG26 CFG2            |         | / deactivation for all NCSx                                     | 1: HECC On              | TILOG OII               | SW4-2 = 0 (ON)         |                    |

| PC27                 | CFG3    | Selects the HECC code corr<br>ector applied <b>for all</b> NCSx | 0: Hamming              | Hamming                 | SW4-3 = 0 (ON)         |                    |

| 1 021                | or do   |                                                                 | 1: BCH                  |                         |                        |                    |

|                      |         | Selects the data bus width just for NSC0 chip select            | CFG[1:0] = 00:<br>8 bit | 16 bit                  |                        |                    |

| PG24                 | CFG0    |                                                                 | CFG[1:0] = 01:<br>16    |                         |                        | PG24 = 1 (<br>OFF) |

|                      |         |                                                                 | bit                     |                         | Hard Wir               |                    |

|                      | CFG1    | CFG[1:0] = 10:<br>32                                            |                         | ed                      | PG25 = 0 (             |                    |

| PG25                 |         |                                                                 | bit                     |                         | ON)                    | ,                  |

Figure 3-2. SAMRH71F20-TFBGA-EK DIP switch configuration

# Note:

"1" and "0" are inverted on the silkscreen of the board.

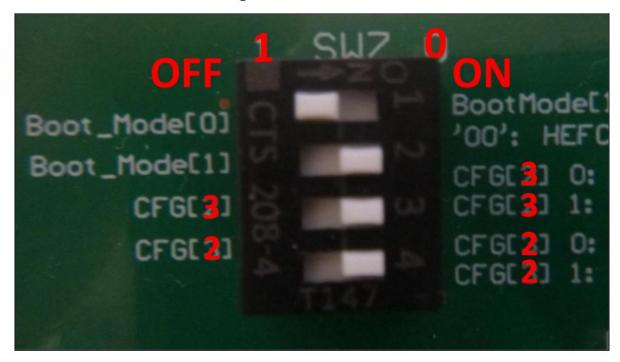

# SAMRH707F18 - EK

On this kit the processor boots from external flash memory with a fixed 8-bit data bus width. The following table provides details about complete setting of the DIP switch.

Table 3-3. SAMRH707F18-EK Settings

| SAMRH           | SAMRH707F18 Processor |                                                                                 |                                     | SAMRH               | SAMRH707F18-EK     |                         |

|-----------------|-----------------------|---------------------------------------------------------------------------------|-------------------------------------|---------------------|--------------------|-------------------------|

| Pin Nu<br>mbers | Pin Name<br>s         | Function                                                                        | Options                             |                     | Selecti<br>on      | Required Config uration |

| PC30 Boot       |                       | Boot Mode [1:0] =<br>(HEFC)                                                     | [1:0] = 00: Internal Flash          |                     | SW7.1 1 (OFF)      |                         |

| FC30            | Mode 0                | Selects the boot m emory                                                        | Boot Mode [1:0] =<br>h (HEMC)       | = 01: External Flas | Externa<br>I Flash | SW7-1 = 1 (OFF)         |

| PC29            | Boot<br>Mode 1        |                                                                                 | Boot Mode [1:0] =                   | : 1X: Internal ROM  |                    | SW7-2 = 0 (ON)          |

|                 |                       | Boot Mode [1:0] = 01                                                            | (External Flash)                    |                     |                    |                         |

| PA19 CFG3       | CFG3                  | Hamming code sel<br>ected by default as<br>HECC code correct<br>or for all NCSx | Internally driven to                | o '0'               | N/A                | SW7-3 = "Don't          |

|                 |                       | Boot Mode [1:0] = 1X (Internal ROM)                                             |                                     |                     |                    | SW7-3 = "Don't care"    |

|                 |                       | Selects the active p                                                            | 0: Run Phase                        |                     |                    |                         |

|                 |                       | hase when the inte rnal ROM is active                                           | 1: Maintenance P                    | hase                |                    |                         |

|                 |                       | Boot Mode [1:0] = 01                                                            | )1 (External Flash)                 |                     |                    | SW7-4 = 0 (ON)          |

|                 |                       | Selects the HECC                                                                | 0: HECC Off                         |                     |                    |                         |

|                 |                       | activation / deactivation for all NCSx when Extern al Flash is active           |                                     |                     |                    |                         |

| PA25            | CFG2                  | Boot Mode [1:0] = 1>                                                            | Boot Mode [1:0] = 1X (Internal ROM) |                     | HECC               |                         |

| TALS OF GL      | 0. 5.2                |                                                                                 | 0: UART Mode                        |                     | Off                |                         |

|                 |                       | Selects the commu                                                               |                                     | Boot Mode 0 = 0     |                    |                         |

|                 |                       | nication mode whe<br>n the Internal ROM<br>is active                            | 1: SpaceWire M ode                  | LVDS Interface      |                    |                         |

|                 |                       |                                                                                 |                                     | Boot Mode 0 = 1     |                    |                         |

|                 |                       |                                                                                 |                                     | TTL Mode            |                    |                         |

Figure 3-3. SAMRH707F18-EK DIP switch configuration

#### Note:

"CFG[2]" and "CFG[3]" are inverted on the silkscreen of the board.

# **Software Settings**

The following section explains how to configure MPLAB X projects to run from external memory.

#### **Board file**

The board file is an XML file with the extension (\*.xboard) that describes the parameters passed to SAMBA memory handlers. It must be placed in the user's MPLAB-X project folder.

For the SAMRH evaluation kits, the default name of the board file is "board.xboard", and its default location is the root folder of the project: "ProjectDir.X"

Two parameters contained in the board file must be configured by the user to make the file compliant with the structure of the user's application.

These two parameters are:

- [End\_Address]: This parameter is related to the external boot memory size and defines the memory's last address.

- [User\_Path]: This parameter defines the absolute path of SAMBA memory handlers' location.

The other parameters depend on SAMBA memory handler's implementation and can be kept at their default values.

The following figure provides a structure example of the board file.

#### Figure 4-1. Board file content example

Figure 4-1. Board file content example

The following table provides the default user parameters of the board files supplied for the SAMRH evaluation kits.

Table 4-1. Board File Parameters

| SAMRH Evaluation Ki    | [End_Addres<br>s] | [User_Path]                                                     |

|------------------------|-------------------|-----------------------------------------------------------------|

| SAMRH71F20-EK          | 6007_FFFFh        | \${ProjectDir}\sst39vf040_loader_samba_sam_rh71_ek_sram.bin     |

| SAMRH71F20-TFGBA<br>EK | 607F_FFFFh        | \${ProjectDir}\sst38vf6401_loader_samba_sam_rh71_tfbga_sram.bin |

| SAMRH707F18-EK         | 6007_FFFFh        | \${ProjectDir}\sst39vf040_loader_samba_sam_rh707_ek_sram.bin    |

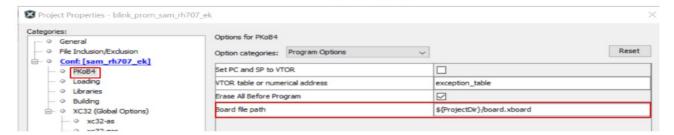

## **Project Configuration**

#### **Board File**

The board file must be defined in the "Board file path" field of the project properties of MPLAB X projects, as shown in the following figure. "Board file path" field is accessible from the debugger tool options (PKoB4 in our example), then "Program Options" is selected from the "Option Categories" menu.

By default, the board file path field is set to: \${ProjectDir}/board.xboard If the board file is not present in the folder, SAMBA memory handlers are ignored.

Figure 4-2. Declaration of the Board File in the MPLAB X project properties

Figure 4-2. Declaration of the Board File in the MPLAB X project properties

## **External Memory**

MPLAB-X Harmony 3 (MH3) sample projects use a default linker script that configures the application to run from internal boot memory.

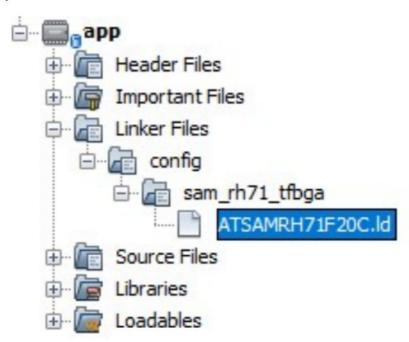

By default, the linker script file "ATSAMRH71F20C.ld" is implemented in harmony projects, as shown in the following figure.

Figure 4-3. Default Linker Script location

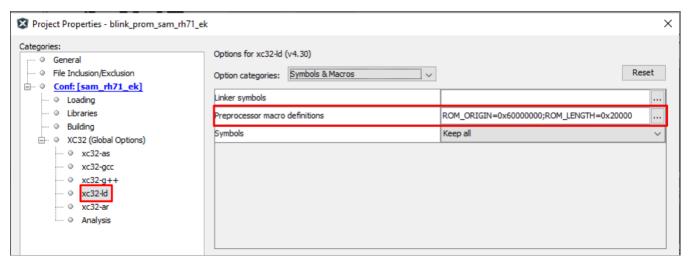

The linker script uses the internal parameters ROM\_ORIGIN and ROM\_LENGTH, as shown in the following figure, to define the location and length of the boot memory. The application depends on these parameters to create the executable.

Figure 4-4. Linker Script's ROM\_ORIGIN and ROM-LENGTH definitions

The sample linker script above limits the parameter ROM\_LENGTH to 0x0002\_0000 which is the length of the internal flash and generates a compilation error if this condition is not met.

However, this limitation may not be compliant with the use of the external flash memory, as its length could be greater than 0x0002 0000.

If the code programmed in the external memory is smaller than 0x0002\_0000, there is no need to update the linker script file. However, if it exceeds this length, the ROM\_LENGTH parameter should be updated to reflect the actual length of the external memory.

The ROM\_ORIGIN parameter can also be overridden without modifying the linker script file.

Before overriding the ROM\_LENGTH parameter, the linker script must be edited to match your hardware configuration.

To override the ROM\_LENGTH parameter, you can use the "Preprocessor macro definitions" field in the MPLAB-X project properties. This field can be accessed from the "XC32-Id" item, and then

"Symbols & Macros" can be selected from the "Options Categories" menu, as shown in the following figure.

Figure 4-5. Preprocessor macro definitions field

For example, for the SST39VF040 flash memory device:

If the ROM LENGTH has not been modified and the built code length should be smaller than 0x0002 0000.

- ROM\_LENGTH=0x20000

- ROM\_ORIGIN=0x60000000

If the ROM\_LENGTH has been updated to  $0x0008\_0000$  and the built code length should be smaller than  $0x0005\_0000$ .

- ROM\_LENGTH=0x50000

- ROM\_ORIGIN=0x60000000

#### **Software Deliveries**

SAMBA memory handlers' mechanism is based on binary applets, which differ according to the processor version and the external boot memory implemented. There are three binary applets specific to the SAMRH evaluation kits:

- sst39vf040\_loader\_samba\_sam\_rh71\_ek\_sram.bin

- sst39vf040\_loader\_samba\_sam\_rh707\_ek\_sram.bin

- sst38vf6401\_loader\_samba\_sam\_rh71\_tfbga\_sram.bin

These applets run in the processor's internal RAM and include both the SAMBA interface for communicating with debug scripts and the routines that perform programming operations (erase, write, and so on) on external boot memory.

Three zipped software packages are supplied to support the SAMRH evaluation kits. Each package includes:

- · The dedicated board file

- The dedicated binary applet file.

#### Compiling, Programming, and Debugging from the External Boot Memory

Once the MPLAB X project has been completely setup with a valid SAMBA memory handler, user can compile, program, and debug this project in the external boot memory using the buttons and icon bar from the top menu, as shown in the following figures.

1. To clean and compile the project, click the Clean and Build.

# Figure 6-1. Clean and Build Button

2. To program the application to the device, click the Make and Program.

# Figure 6-2. Make and Program Button

3. To run the code, click the Debug Project.

# Figure 6-3. Debug and Program Button

4. To stop the code, click the Finish Debugger Session.

Figure 6-4. Finish Debugger Session Button

1. Or to pause it, click the Pause.

Figure 6-5. Pause Button

#### Reference

This section lists documents that provide more information about the MPLAB X, SAMRH71 and SAMRH707 devices.

### **MPLAB X**

MPLAB X IDE User's Guide, DS50002027D. <a href="https://www.microchip.com/en-us/tools-resources/develop/mplab-x-ide#tabs">https://www.microchip.com/en-us/tools-resources/develop/mplab-x-ide#tabs</a>

#### **SAMRH71 Device**

- SAMRH71F20 Device Datasheet, DS60001593

ww1.microchip.com/downloads/en/DeviceDoc/SAMRH71\_Datasheet\_DS60001593F.pdf

- SAMRH71F20 Evaluation Kit User Guide, DS50002910.

https://ww1.microchip.com/downloads/en/DeviceDoc/SAMRH71F20-EK-Evaluation-Kit-User-Guide-DS50002910A.pdf

• SAMRH71-TFBGA-EK Evaluation Kit User Guide, DS50003449A

https://ww1.microchip.com/downloads/aemDocuments/documents/AERO/ProductDocuments/UserGuides

• Getting started with SAMRH71F20 Evaluation Kit, DS00004008.

https://ww1.microchip.com/downloads/en/Appnotes/

- Getting\_Started\_with\_the\_SAMRH71F20\_Evaluation\_Kit\_DS00004008A.pdf

- SST38LF6401RT and SAMRH71 Reference Design, DS0004274

https://ww1.microchip.com/downloads/aemDocuments/documents/AERO/ApplicationNotes/ApplicationNo

#### **SAMRH707 Device**

SAMRH707F18 Device Datasheet, DS60001634

$\frac{https://ww1.microchip.com/downloads/aemDocuments/documents/AERO/ProductDocuments/DataSheets/SAMRH707\_Datasheet\_DS60001634.pdf$

Getting Started with SAMRH707F18 Microcontroller using MPLAB-X IDE and MCC Harmony Framework, DS00004478

$\underline{https://ww1.microchip.com/downloads/aemDocuments/documents/AERO/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/ApplicationNotes/Applic$

SAMRH707-EK Evaluation Kit User Guide, DS60001744

https://ww1.microchip.com/downloads/aemDocuments/documents/AERO/ProductDocuments/UserGuides/S AMRH707 EK Evaluation Kit User Guide 60001744.pdf

SST38LF6401RT and SAMRH707 Reference Design, DS00004583

<u>ww1.microchip.com/downloads/aemDocuments/documents/AERO/ApplicationNotes/ApplicationNotes/SAMRH707-SST38LF6401RT-Reference-Design-00004583.pdf</u>

# **Revision History**

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

| Revision | Date    | Description      |

|----------|---------|------------------|

| Α        | 04/2024 | Initial Revision |

## **Microchip Information**

#### The Microchip Website

Microchip provides online support via our website at <a href="www.microchip.com/">www.microchip.com/</a>. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

### **Customer Support**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: <a href="https://www.microchip.com/support">www.microchip.com/support</a>

#### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code

protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright

Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly

evolving. Microchip is committed to continuously improving the code protection features of our products.

#### **Legal Notice**

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE. IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual

property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge,

IGaT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies. © 2024, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved.

ISBN: 978-1-6683-4401-9

#### **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# Worldwide Sales and Service

| AMERICAS                                            | ASIA/PACIFIC        | ASIA/PACIFIC | EUROPE                |

|-----------------------------------------------------|---------------------|--------------|-----------------------|

|                                                     |                     |              | Austria – Wels        |

|                                                     |                     |              | Tel: 43-7242-2244-39  |

| Corporate Office                                    |                     |              | Fax: 43-7242-2244-393 |

| 2355 West Chandler Blvd.<br>Chandler, AZ 85224-6199 |                     |              | Denmark – Copenhagen  |

| Tel: <u>480-792-7200</u>                            |                     |              | Tel: 45-4485-5910     |

| Fax: 480-792-7277                                   |                     |              | Fax: 45-4485-2829     |

| Technical Support: www.                             | Australia – Sydney  |              | Finland – Espoo       |

| microchip.com/support                               |                     |              | Tel: 358-9-4520-820   |

| Web Address: www.micr                               | Tel: 61-2-9868-6733 |              |                       |

| ochip.com                                      | China – Beijing                             | India – Bangalore      | France – Paris        |

|------------------------------------------------|---------------------------------------------|------------------------|-----------------------|

| Atlanta                                        | Tel: 86-10-8569-7000                        | Tel: 91-80-3090-4444   | Tel: 33-1-69-53-63-20 |

| Duluth, GA                                     | China – Chengdu                             | India – New Delhi      | Fax: 33-1-69-30-90-79 |

| Tel: <u>678-957-9614</u>                       | Tel: 86-28-8665-5511                        | Tel: 91-11-4160-8631   | Germany – Garching    |

| Fax: <u>678-957-1455</u>                       | China – Chongqing                           | India – Pune           | Tel: 49-8931-9700     |

| Austin, TX                                     | Tel: 86-23-8980-9588                        | Tel: 91-20-4121-0141   | Germany – Haan        |

| Tel: <u>512-257-3370</u>                       | China – Dongguan                            | Japan – Osaka          | Tel: 49-2129-3766400  |

| Boston Westborough, M<br>A Tel: 774-760-0087   | Tel: 86-769-8702-9880                       | Tel: 81-6-6152-7160    | Germany – Heilbronn   |

|                                                | China – Guangzhou                           | Japan – Tokyo          | Tel: 49-7131-72400    |

| Fax: 774-760-0088                              | Tel: 86-20-8755-8029                        | Tel: 81-3-6880- 3770   | Germany – Karlsruhe   |

| Chicago<br>Itasca, IL                          | China – Hangzhou                            | Korea – Daegu          | Tel: 49-721-625370    |

| Tel: 630-285-0071                              | Tel: 86-571-8792-8115                       | Tel: 82-53-744-4301    | Germany – Munich      |

| Fax: 630-285-0075                              | China – Hong Kong                           | Korea – Seoul          | Tel: 49-89-627-144-0  |

| Dallas                                         | <b>SAR</b> Tel: 852-2943-5100               | Tel: 82-2-554-7200     | Fax: 49-89-627-144-44 |

| Addison, TX                                    |                                             | Malaysia – Kuala Lumpu | Germany – Rosenheim   |

| Tel: 972-818-7423                              | <b>China – Nanjing</b> Tel: 86-25-8473-2460 | r                      | Tel: 49-8031-354-560  |

| Fax: 972-818-2924                              |                                             | Tel: 60-3-7651-7906    | Israel – Ra'anana     |

| Detroit                                        | China – Qingdao                             | Malaysia – Penang      | Tel: 972-9-744-7705   |

|                                                | Tel: 86-532-8502-7355                       | Tel: 60-4-227-8870     | Italy – Milan         |

| Novi, MI                                       | China – Shanghai                            | Philippines – Manila   | Tel: 39-0331-742611   |

| Tel: <u>248-848-4000</u>                       | Tel: 86-21-3326-8000                        | Tel: 63-2-634-9065     | Fax: 39-0331-466781   |

| Houston, TX                                    | China – Shenyang                            | Singapore              | Italy – Padova        |

| Tel: <u>281-894-5983</u>                       | Tel: 86-24-2334-2829                        | Tel: 65-6334-8870      | Tel: 39-049-7625286   |

| Indianapolis Noblesville, IN Tel: 317-773-8323 | China – Shenzhen                            | Taiwan – Hsin Chu      | Netherlands – Drunen  |

| Fax: <u>317-773-5453</u>                       | Tel: 86-755-8864-2200                       | Tel: 886-3-577-8366    | Tel: 31-416-690399    |

| Tel: <u>317-536-2380</u>                       | China – Suzhou                              | Taiwan – Kaohsiung     | Fax: 31-416-690340    |

| Los Angeles Mission Viej                       | Tel: 86-186-6233-1526                       | Tel: 886-7-213-7830    | Norway – Trondheim    |

| o, CA Tel: <u>949-462-9523</u>                 | China – Wuhan                               | Taiwan – Taipei        | Tel: 47-72884388      |

| Fax: <u>949-462-9608</u>                       | Tel: 86-27-5980-5300                        | Tel: 886-2-2508-8600   | Poland – Warsaw       |

| Tel: <u>951-273-7800</u>                       | China – Xian                                | Thailand – Bangkok     | Tel: 48-22-3325737    |

| Raleigh, NC                                    | Tel: 86-29-8833-7252                        | Tel: 66-2-694-1351     | Romania – Bucharest   |

| Tel: <u>919-844-7510</u>                       | China – Xiamen                              | Vietnam – Ho Chi Minh  | Tel: 40-21-407-87-50  |

| New York, NY                                   | Tel: 86-592-2388138                         | Tel: 84-28-5448-2100   | Spain – Madrid        |

| Tel: <u>631-435-6000</u>                       | China – Zhuhai                              |                        | Tel: 34-91-708-08-90  |

| San Jose, CA             | Tel: 86-756-3210040 | Fax: 34-91-708-08-91 |

|--------------------------|---------------------|----------------------|

| Tel: 408-735-9110        |                     | Sweden – Gothenberg  |

| Tel: <u>408-436-4270</u> |                     | Tel: 46-31-704-60-40 |

| Canada – Toronto         |                     | Sweden – Stockholm   |

| Tel: <u>905-695-1980</u> |                     | Tel: 46-8-5090-4654  |

| Fax: <u>905-695-2078</u> |                     | UK – Wokingham       |

|                          |                     | Tel: 44-118-921-5800 |

|                          |                     | Fax: 44-118-921-5820 |

# **Application Note**

© 2024 Microchip Technology Inc. and its subsidiaries

#### **Documents / Resources**

MICROCHIP SAMRH71 Programming the External Memory Family Evaluation Kits [pdf] Us er Guide

SAMRH71, SAMRH71 Programming the External Memory Family Evaluation Kits, Programming the External Memory Family Evaluation Kits, External Memory Family Evaluation Kits, Family Evaluation Kits, Family Evaluation Kits, Evaluation Kits, Kits

#### References

- Design Help and Other Services | Microchip Technology

- Microchip Lightning Support

- <u>Sempowering Innovation | Microchip Technology</u>

- <u>Sempowering Innovation | Microchip Technology</u>

- <u>Sempowering Innovation | Microchip Technology</u>

- \( \square\) Client Support Services | Microchip Technology

- Microchip Lightning Support

- User Manual

#### Manuals+, Privacy Policy

This website is an independent publication and is neither affiliated with nor endorsed by any of the trademark owners. The "Bluetooth®" word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. The "Wi-Fi®" word mark and logos are registered trademarks owned by the Wi-Fi Alliance. Any use of these marks on this website does not imply any affiliation with or endorsement.