Rhaglenwyr Dadfygiwr ICE

Rhaglenwyr Dadfygiwr ICE

Canllaw Defnyddiwr Rhaglenwyr a Dadfygwyr

Rhaglenwyr a Dadfygwyr

Atmel- ICE

CANLLAWIAU DEFNYDDWYR

Y Dadleuwr Atmel-ICE

Mae Atmel-ICE yn offeryn datblygu pwerus ar gyfer dadfygio a rhaglennu microreolwyr Atmel ®SAM ac Atmel AVR yn seiliedig ar ARM® Cortex®-M gyda gallu Dadfygio Ar-Sglodion ®.

Mae'n cefnogi:

- Rhaglennu a dadfygio ar sglodion holl ficroreolwyr 32-did Atmel AVR ar y ddau JTAG a rhyngwynebau aWire

- Rhaglennu a dadfygio ar sglodion holl ddyfeisiau teulu Atmel AVR XMEGA® ar y ddau JTAG a rhyngwynebau 2-wifren PDI

- Rhaglennu (JTAG, SPI, UPDI) a dadfygio holl ficroreolwyr 8-did Atmel AVR gyda chefnogaeth OCD ar y naill J neu'r llallTAG, rhyngwynebau debugWIRE neu UPDI

- Rhaglennu a dadfygio holl ficroreolyddion Atmel SAM ARM Cortex-M ar SWD a JTAG rhyngwynebau

- Rhaglennu (TPI) holl ficroreolyddion 8-bit Atmel tinyAVR® gyda chefnogaeth ar gyfer y rhyngwyneb hwn

Ymgynghorwch â'r rhestr dyfeisiau a gefnogir yn y Canllaw Defnyddiwr Stiwdio Atmel am restr lawn o ddyfeisiau a rhyngwynebau a gefnogir gan y datganiad firmware hwn.

Rhagymadrodd

1.1. Rhagymadrodd i'r Atmel-ICE

Mae Atmel-ICE yn offeryn datblygu pwerus ar gyfer dadfygio a rhaglennu microreolwyr Atmel SAM ac Atmel AVR sy'n seiliedig ar ARM Cortex-M gyda gallu Debug On-Chip.

Mae'n cefnogi:

- Rhaglennu a dadfygio ar sglodion holl ficroreolwyr Atmel AVR UC3 ar y ddau JTAG a rhyngwynebau aWire

- Rhaglennu a dadfygio ar sglodion holl ddyfeisiau teulu AVR XMEGA ar y ddau JTAG a rhyngwynebau PDI 2wire

- Rhaglennu (JTAG a SPI) a dadfygio pob microreolydd AVR 8-did gyda chefnogaeth OCD ar y ddau JTAG neu ryngwynebau debugWIRE

- Rhaglennu a dadfygio holl ficroreolyddion Atmel SAM ARM Cortex-M ar SWD a JTAG rhyngwynebau

- Rhaglennu (TPI) holl ficroreolyddion 8-did Atmel tinyAVR gyda chefnogaeth ar gyfer y rhyngwyneb hwn

1.2. Nodweddion Atmel-ICE

- Cwbl gydnaws â Stiwdio Atmel

- Yn cefnogi rhaglennu a dadfygio holl ficroreolyddion 3-did Atmel AVR UC32

- Yn cefnogi rhaglennu a dadfygio holl ddyfeisiau AVR XMEGA 8-did

- Yn cefnogi rhaglennu a dadfygio holl ddyfeisiau Atmel megaAVR® 8-did a tinyAVR gydag OCD

- Yn cefnogi rhaglennu a dadfygio holl ficroreolwyr SAM ARM Cortex-M

- Targed gweithredu cyftage ystod o 1.62V i 5.5V

- Yn tynnu llai na 3mA o VTref targed wrth ddefnyddio rhyngwyneb debugWIRE a llai nag 1mA ar gyfer pob rhyngwyneb arall

- Yn cefnogi JTAG amleddau cloc o 32kHz i 7.5MHz

- Yn cefnogi amleddau cloc PDI o 32kHz i 7.5MHz

- Yn cefnogi cyfraddau baud debugWIRE o 4kbit yr eiliad i 0.5Mbit yr eiliad

- Yn cefnogi cyfraddau baud aWire o 7.5kbit yr eiliad i 7Mbit yr eiliad

- Yn cefnogi amleddau cloc SPI o 8kHz i 5MHz

- Yn cefnogi cyfraddau baud UPDI o hyd at 750kbit yr eiliad

- Yn cefnogi amleddau cloc SWD o 32kHz i 10MHz

- USB 2.0 rhyngwyneb gwesteiwr cyflym

- Dal olrhain cyfresol ITM hyd at 3MB/s

- Yn cefnogi rhyngwynebau DGI SPI ac USART pan nad ydynt yn dadfygio neu'n rhaglennu

- Yn cefnogi 10-pin 50-mil JTAG cysylltydd gyda pinouts AVR a Cortex. Mae'r cebl stiliwr safonol yn cefnogi penawdau AVR 6-pin ISP/PDI/TPI 100-mil yn ogystal â 10-pin 50-mil. Mae addasydd ar gael i gefnogi penawdau 6-pin 50-mil, 10-pin 100-mil, ac 20-pin 100-mil. Mae sawl opsiwn cit ar gael gyda gwahanol geblau ac addaswyr.

1.3. Gofynion System

Mae'r uned Atmel-ICE yn mynnu bod amgylchedd dadfygio pen blaen Atmel Studio fersiwn 6.2 neu ddiweddarach yn cael ei osod ar eich cyfrifiadur.

Dylai'r Atmel-ICE gael ei gysylltu â'r cyfrifiadur gwesteiwr gan ddefnyddio'r cebl USB a ddarperir, neu gebl Micro-USB ardystiedig.

Cychwyn ar yr Atmel-ICE

2.1. Cynnwys Pecyn Llawn

Mae pecyn llawn Atmel-ICE yn cynnwys yr eitemau hyn:

- Uned Atmel-ICE

- Cebl USB (1.8m, cyflymder uchel, Micro-B)

- Bwrdd addasydd yn cynnwys 50-mil AVR, 100-mil AVR/SAM, ac addaswyr SAM 100-mil 20-pin

- Cebl fflat IDC gyda chysylltydd 10-pin 50-mil a chysylltydd 6-pin 100-mil

- Cebl sgwid mini 50-mil 10-pin gyda socedi 10 x 100-mil

Ffigur 2-1. Cynnwys Pecyn Llawn Atmel-ICE 2.2. Cynnwys Pecyn Sylfaenol

2.2. Cynnwys Pecyn Sylfaenol

Mae pecyn sylfaenol Atmel-ICE yn cynnwys yr eitemau hyn:

- Uned Atmel-ICE

- Cebl USB (1.8m, cyflymder uchel, Micro-B)

- Cebl fflat IDC gyda chysylltydd 10-pin 50-mil a chysylltydd 6-pin 100-mil

Ffigur 2-2. Cynnwys Pecyn Sylfaenol Atmel-ICE 2.3. Cynnwys Pecyn PCBA

2.3. Cynnwys Pecyn PCBA

Mae pecyn Atmel-ICE PCBA yn cynnwys yr eitemau hyn:

- Uned Atmel-ICE heb amgáu plastig

Ffigur 2-3. Cynnwys Pecyn PCBA Atmel-ICE 2.4. Pecynnau Rhannau Sbâr

2.4. Pecynnau Rhannau Sbâr

Mae'r pecynnau darnau sbâr canlynol ar gael:

- Pecyn addasydd

- Pecyn cebl

Ffigur 2-4. Cynnwys Pecyn Addasydd Atmel-ICE 2.5. Kit Drosoddview

2.5. Kit Drosoddview

Dangosir opsiynau cit Atmel-ICE ar ffurf diagram yma:

Ffigur 2-6. Atmel-ICE Kit Overview 2.6. Cynnull yr Atmel- ICE

2.6. Cynnull yr Atmel- ICE

Mae'r uned Atmel-ICE yn cael ei gludo heb unrhyw geblau ynghlwm. Darperir dau opsiwn cebl yn y pecyn llawn:

- Cebl fflat IDC 50-mil 10-pin gyda chysylltwyr ISP 6-pin a 10-pin

- Cebl sgwid mini 50-mil 10-pin gyda socedi 10 x 100-mil

Ffigur 2-7. Ceblau Atmel-ICE Ar gyfer y rhan fwyaf o ddibenion, gellir defnyddio'r cebl fflat IDC 50-mil 10-pin, gan gysylltu naill ai'n frodorol â'i gysylltwyr 10-pin neu 6-pin, neu gysylltu trwy'r bwrdd addasydd. Darperir tri addasydd ar un PCBA bach. Mae'r addaswyr canlynol wedi'u cynnwys:

Ar gyfer y rhan fwyaf o ddibenion, gellir defnyddio'r cebl fflat IDC 50-mil 10-pin, gan gysylltu naill ai'n frodorol â'i gysylltwyr 10-pin neu 6-pin, neu gysylltu trwy'r bwrdd addasydd. Darperir tri addasydd ar un PCBA bach. Mae'r addaswyr canlynol wedi'u cynnwys:

- 100-mil 10-pin JTAGaddasydd / SWD

- 100-mil 20-pin SAM JTAGaddasydd / SWD

- Addasydd SPI / debugWIRE / PDI / aWire 50-mil 6-pin

Ffigur 2-8. Addasyddion Atmel-ICE Nodyn:

Nodyn:

Mae J 50-milTAG ni ddarparwyd addasydd - mae hyn oherwydd y gellir defnyddio'r cebl IDC 50-mil 10-pin i gysylltu'n uniongyrchol â J 50-milTAG pennyn. Am rif rhan y gydran a ddefnyddir ar gyfer y cysylltydd 50-mil 10-pin, gweler Rhifau Rhan Cysylltwyr Targed Atmel-ICE.

Mae'r pennawd ISP/PDI 6-pin wedi'i gynnwys fel rhan o'r cebl IDC 10-pin. Gellir torri i ffwrdd y terfyniad hwn os nad oes ei angen.

I gydosod eich Atmel-ICE yn ei ffurfweddiad diofyn, cysylltwch y cebl IDC 10-pin 50-mil i'r uned fel y dangosir isod. Gwnewch yn siŵr eich bod yn cyfeirio'r cebl fel bod y wifren goch (pin 1) ar y cebl yn cyd-fynd â'r dangosydd trionglog ar wregys glas yr amgaead. Dylai'r cebl gysylltu i fyny o'r uned. Gwnewch yn siŵr eich bod yn cysylltu â'r porthladd sy'n cyfateb i pinout eich targed - AVR neu SAM.

Ffigur 2-9. Cysylltiad Cebl Atmel-ICE Ffigur 2-10. Cysylltiad Probe Atmel-ICE AVR

Ffigur 2-10. Cysylltiad Probe Atmel-ICE AVR

Ffigur 2-11. Cysylltiad Probe SAM Atmel-ICE

Ffigur 2-11. Cysylltiad Probe SAM Atmel-ICE 2.7. Agor yr Atmel-ICE

2.7. Agor yr Atmel-ICE

Nodyn:

Ar gyfer gweithrediad arferol, ni ddylid agor yr uned Atmel-ICE. Mae agor yr uned yn cael ei wneud ar eich menter eich hun.

Dylid cymryd rhagofalon gwrth-statig.

Mae lloc Atmel-ICE yn cynnwys tair cydran blastig ar wahân - gorchudd uchaf, gorchudd gwaelod, a gwregys glas - sy'n cael eu torri gyda'i gilydd yn ystod y cynulliad. I agor yr uned, rhowch sgriwdreifer fflat fawr yn yr agoriadau yn y gwregys glas, rhowch rywfaint o bwysau i mewn a throelli'n ysgafn. Ailadroddwch y broses ar y tyllau snapper eraill, a bydd y clawr uchaf yn popio i ffwrdd.

Ffigur 2-12. Agor yr Atmel-ICE (1)

Ffigur 2-13. Agor yr Atmel-ICE (2)

Ffigur 2-13. Agor yr Atmel-ICE (2)

Ffigur 2-14. Agor yr Atmel-ICE(3)

Ffigur 2-14. Agor yr Atmel-ICE(3) I gau'r uned eto, aliniwch y gorchuddion uchaf a gwaelod yn gywir, a gwasgwch yn gadarn gyda'i gilydd.

I gau'r uned eto, aliniwch y gorchuddion uchaf a gwaelod yn gywir, a gwasgwch yn gadarn gyda'i gilydd.

2.8. Pweru yr Atmel-ICE

Mae'r Atmel-ICE yn cael ei bweru gan y bws USB cyftage. Mae angen llai na 100mA i weithredu, ac felly gellir ei bweru trwy ganolbwynt USB. Bydd y LED pŵer yn goleuo pan fydd yr uned wedi'i phlygio i mewn. Pan nad yw wedi'i chysylltu mewn sesiwn rhaglennu neu ddadfygio gweithredol, bydd yr uned yn mynd i mewn i fodd defnydd pŵer isel i gadw batri eich cyfrifiadur. Ni ellir gyrru'r Atmel-ICE i lawr - dylid ei ddad-blygio pan nad yw'n cael ei ddefnyddio.

2.9. Cysylltu â'r Cyfrifiadur Gwesteiwr

Mae'r Atmel-ICE yn cyfathrebu'n bennaf gan ddefnyddio rhyngwyneb HID safonol, ac nid oes angen gyrrwr arbennig ar y cyfrifiadur gwesteiwr. I ddefnyddio ymarferoldeb Porth Data datblygedig yr Atmel-ICE, gwnewch yn siŵr eich bod yn gosod y gyrrwr USB ar y cyfrifiadur gwesteiwr. Gwneir hyn yn awtomatig wrth osod y meddalwedd pen blaen a ddarperir am ddim gan Atmel. Gwel www.atmel.com am ragor o wybodaeth neu i lawrlwytho'r meddalwedd pen blaen diweddaraf.

Rhaid i'r Atmel-ICE gael ei gysylltu â phorthladd USB sydd ar gael ar y cyfrifiadur gwesteiwr gan ddefnyddio'r cebl USB a ddarperir, neu gebl micro ardystiedig USB addas. Mae'r Atmel-ICE yn cynnwys rheolydd sy'n cydymffurfio â USB 2.0, a gall weithredu mewn moddau cyflymder llawn a chyflymder uchel. I gael y canlyniadau gorau, cysylltwch yr Atmel-ICE yn uniongyrchol â chanolbwynt cyflymder uchel sy'n cydymffurfio â USB 2.0 ar y cyfrifiadur gwesteiwr gan ddefnyddio'r cebl a ddarperir.

2.10. Gosod Gyrrwr USB

2.10.1. Ffenestri

Wrth osod yr Atmel-ICE ar gyfrifiadur sy'n rhedeg Microsoft® Windows® , mae'r gyrrwr USB yn cael ei lwytho pan fydd yr Atmel-ICE wedi'i blygio i mewn gyntaf.

Nodyn:

Gwnewch yn siŵr eich bod yn gosod y pecynnau meddalwedd pen blaen cyn plygio'r uned i mewn am y tro cyntaf.

Ar ôl ei osod yn llwyddiannus, bydd yr Atmel-ICE yn ymddangos yn rheolwr y ddyfais fel “Dyfais Rhyngwyneb Dynol”.

Cysylltu yr Atmel-ICE

3.1. Cysylltu â Dyfeisiau Targed AVR a SAM

Mae gan yr Atmel-ICE ddau 50-mil 10-pin JTAG cysylltwyr. Mae'r ddau gysylltydd wedi'u cysylltu'n uniongyrchol â thrydan, ond maent yn cydymffurfio â dau binout gwahanol; yr AVR JTAG pennawd a phennawd ARM Cortex Debug. Dylid dewis y cysylltydd ar sail pinout y bwrdd targed, ac nid y math MCU targed - ar gyfer exampDylai dyfais SAM sydd wedi'i gosod mewn pentwr AVR STK® 600 ddefnyddio'r pennawd AVR.

Mae ceblau ac addaswyr amrywiol ar gael yn y gwahanol gitiau Atmel-ICE. Mae drosoddview o opsiynau cysylltiad yn cael ei ddangos.

Ffigur 3-1. Opsiynau Cysylltiad Atmel-ICE Mae'r wifren goch yn nodi pin 1 o'r cysylltydd 10-pin 50-mil. Gosodir pin 1 y cysylltydd 6-pin 100-mil i'r dde o'r byselliad pan welir y cysylltydd o'r cebl. Mae pin 1 pob cysylltydd ar yr addasydd wedi'i farcio â dot gwyn. Mae'r ffigur isod yn dangos pinout y cebl dadfygio. Mae'r cysylltydd sydd wedi'i farcio A yn plygio i mewn i'r dadfygiwr tra bod ochr B yn plygio i mewn i'r bwrdd targed.

Mae'r wifren goch yn nodi pin 1 o'r cysylltydd 10-pin 50-mil. Gosodir pin 1 y cysylltydd 6-pin 100-mil i'r dde o'r byselliad pan welir y cysylltydd o'r cebl. Mae pin 1 pob cysylltydd ar yr addasydd wedi'i farcio â dot gwyn. Mae'r ffigur isod yn dangos pinout y cebl dadfygio. Mae'r cysylltydd sydd wedi'i farcio A yn plygio i mewn i'r dadfygiwr tra bod ochr B yn plygio i mewn i'r bwrdd targed.

Ffigur 3-2. Pinout Cebl Dadfygio

3.2. Yn cysylltu â JTAG Targed

3.2. Yn cysylltu â JTAG Targed

Mae gan yr Atmel-ICE ddau 50-mil 10-pin JTAG cysylltwyr. Mae'r ddau gysylltydd wedi'u cysylltu'n uniongyrchol â thrydan, ond maent yn cydymffurfio â dau binout gwahanol; yr AVR JTAG pennawd a phennawd ARM Cortex Debug. Dylid dewis y cysylltydd ar sail pinout y bwrdd targed, ac nid y math MCU targed - ar gyfer exampDylai dyfais SAM sydd wedi'i gosod mewn pentwr AVR STK600 ddefnyddio'r pennawd AVR.

Y pinout a argymhellir ar gyfer yr AVR J 10-pinTAG dangosir y cysylltydd yn Ffigur 4-6. Dangosir y pinout a argymhellir ar gyfer y cysylltydd ARM Cortex Debug 10-pin yn Ffigur 4-2.

Cysylltiad uniongyrchol â phennawd safonol 10-pin 50-mil

Defnyddiwch y cebl fflat 50-mil 10-pin (wedi'i gynnwys mewn rhai citiau) i gysylltu'n uniongyrchol â bwrdd sy'n cefnogi'r math hwn o bennawd. Defnyddiwch y porthladd cysylltydd AVR ar yr Atmel-ICE ar gyfer penawdau gyda'r pinout AVR, a'r porthladd cysylltydd SAM ar gyfer penawdau sy'n cydymffurfio â pinout pennawd ARM Cortex Debug.

Mae'r pinouts ar gyfer y ddau borth cysylltydd 10-pin i'w gweld isod.

Cysylltiad â phennawd safonol 10-pin 100-mil

Defnyddiwch addasydd safonol 50-mil i 100-mil i gysylltu â phenawdau 100-mil. Gellir defnyddio bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) at y diben hwn, neu fel arall y JTAGGellir defnyddio addasydd ICE3 ar gyfer targedau AVR.

![]() Pwysig:

Pwysig:

Mae'r J.TAGNi ellir defnyddio addasydd ICE3 100-mil gyda'r porthladd cysylltydd SAM, gan fod pinnau 2 a 10 (AVR GND) ar yr addasydd wedi'u cysylltu.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Os nad oes gan eich bwrdd targed J 10-pin sy'n cydymffurfioTAG pennawd mewn 50- neu 100-mil, gallwch fapio i binout arferol gan ddefnyddio'r cebl “mini-squid” 10-pin (wedi'i gynnwys mewn rhai citiau), sy'n rhoi mynediad i ddeg soced 100-mil unigol.

Cysylltiad â phennawd 20-pin 100-milr

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â thargedau gyda phennawd 20-pin 100-mil.

Tabl 3-1. Atmel- ICE JTAG Disgrifiad Pin

| Enw | AVR pin porthladd | SAM pin porthladd | Disgrifiad |

| TCK | 1 | 4 | Cloc Prawf (signal cloc o'r Atmel-ICE i'r ddyfais darged). |

| TMS | 5 | 2 | Dewis Modd Prawf (signal rheoli o'r Atmel-ICE i'r ddyfais darged). |

| TDI | 9 | 8 | Prawf Data Mewn (data a drosglwyddir o'r Atmel-ICE i'r ddyfais darged). |

| TDO | 3 | 6 | Profi Data Allan (data a drosglwyddir o'r ddyfais darged i'r Atmel-ICE). |

| nTRST | 8 | – | Ailosod Prawf (dewisol, dim ond ar rai dyfeisiau AVR). Fe'i defnyddir i ailosod y JTAG Rheolydd TAP. |

| nSRST | 6 | 10 | Ailosod (dewisol). Fe'i defnyddir i ailosod y ddyfais targed. Argymhellir cysylltu'r pin hwn gan ei fod yn caniatáu i'r Atmel-ICE ddal y ddyfais darged mewn cyflwr ailosod, a all fod yn hanfodol i ddadfygio mewn rhai senarios. |

| VTG | 4 | 1 | Cyfrol targedtage cyfeiriad. Yr Atmel-ICE samples y targed cyftage ar y pin hwn er mwyn pweru'r trawsnewidyddion lefel yn gywir. Mae'r Atmel-ICE yn tynnu llai na 3mA o'r pin hwn yn y modd debugWIRE a llai nag 1mA mewn moddau eraill. |

| GND | 2, 10 | 3, 5, 9 | Ground. Rhaid cysylltu pob un i sicrhau bod yr Atmel-ICE a'r ddyfais darged yn rhannu'r un cyfeirnod daear. |

3.3. Cysylltu â Tharged aWire

Dim ond un llinell ddata sydd ei hangen ar ryngwyneb aWire yn ogystal â VCC a GND. Ar y targed y llinell hon yw'r llinell nRESET, er bod y dadfygiwr yn defnyddio'r JTAG Llinell TDO fel y llinell ddata.

Dangosir y pinout a argymhellir ar gyfer y cysylltydd aWire 6-pin yn Ffigur 4-8.

Cysylltiad â phennawd 6-pin 100-mil aWire

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd safonol 100-mil aWire.

Cysylltiad â phennawd 6-pin 50-mil aWire

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd safonol 50-mil aWire.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen tri chysylltiad, fel y disgrifir yn y tabl isod.

Tabl 3-2. Mapio Pin aWire Atmel-ICE

|

Pinnau porthladd AVR Atmel-ICE |

Pinnau targed | Pin sgwid bach |

aWire pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (Ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.4. Cysylltu â Tharged PDI

Dangosir y pinout a argymhellir ar gyfer y cysylltydd PDI 6-pin yn Ffigur 4-11.

Cysylltiad â phennawd PDI 6-pin 100-mil

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd PDI safonol 100-mil.

Cysylltiad â phennawd PDI 6-pin 50-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd PDI safonol 50-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen pedwar cysylltiad, fel y disgrifir yn y tabl isod.

![]() Pwysig:

Pwysig:

Mae'r pinout sydd ei angen yn wahanol i'r JTAGICE mkII JTAG stiliwr, lle mae PDI_DATA wedi'i gysylltu â phin 9. Mae'r Atmel-ICE yn gydnaws â'r pinout a ddefnyddir gan yr Atmel-ICE, JTAGCynhyrchion ICE3, AVR ONE!, ac AVR Dragon™.

Tabl 3-3. Mapio Pin PDI Atmel-ICE

| Pinnau porthladd AVR Atmel-ICE | Pinnau targed | Pin sgwid bach |

aWire pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (Ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.4 Cysylltu â Tharged PDI

Dangosir y pinout a argymhellir ar gyfer y cysylltydd PDI 6-pin yn Ffigur 4-11.

Cysylltiad â phennawd PDI 6-pin 100-mil

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd PDI safonol 100-mil.

Cysylltiad â phennawd PDI 6-pin 50-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd PDI safonol 50-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen pedwar cysylltiad, fel y disgrifir yn y tabl isod.

![]() Pwysig:

Pwysig:

Mae'r pinout sydd ei angen yn wahanol i'r JTAGICE mkII JTAG stiliwr, lle mae PDI_DATA wedi'i gysylltu â phin 9. Mae'r Atmel-ICE yn gydnaws â'r pinout a ddefnyddir gan yr Atmel-ICE, JTAGICE3, AVR ONE!, ac AVR Dragon™ cynnyrch.

Tabl 3-3. Mapio Pin PDI Atmel-ICE

| Pin porthladd AVR Atmel-ICE | Pinnau targed | Pin sgwid bach | Atmel STK600 PDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | PDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.5 Cysylltu â Tharged UPDI

Dangosir y pinout a argymhellir ar gyfer y cysylltydd UPDI 6-pin yn Ffigur 4-12.

Cysylltiad â phennawd UPDI 6-pin 100-mil

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd UPDI safonol 100-mil.

Cysylltiad â phennawd UPDI 6-pin 50-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd UPDI safonol 50-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen tri chysylltiad, fel y disgrifir yn y tabl isod.

Tabl 3-4. Mapio Pin Atmel-ICE UPDI

| Pin porthladd AVR Atmel-ICE | Pinnau targed | Pin sgwid bach |

Atmel STK600 UPDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | [/AILOSOD synnwyr] | 6 | 5 |

| Pin 7 (Ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.6 Cysylltu â Tharged debugWIRE

Dangosir y pinout a argymhellir ar gyfer y cysylltydd debugWIRE (SPI) 6-pin yn Nhabl 3-6.

Cysylltiad â phennawd SPI 6-pin 100-mil

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd SPI 100-mil safonol.

Cysylltiad â phennawd SPI 6-pin 50-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd SPI safonol 50-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen tri chysylltiad, fel y disgrifir yn Nhabl 3-5.

Er mai dim ond un llinell signal (AILSET) sydd ei hangen ar y rhyngwyneb debugWIRE, VCC a GND i weithredu'n gywir, fe'ch cynghorir i gael mynediad i'r cysylltydd SPI llawn fel y gellir galluogi'r rhyngwyneb debugWIRE a'i analluogi gan ddefnyddio rhaglennu SPI.

Pan fydd y ffiws DWEN wedi'i alluogi mae'r rhyngwyneb SPI yn cael ei ddiystyru'n fewnol er mwyn i'r modiwl OCD gael rheolaeth dros y pin AILOSOD. Mae'r debugWIRE OCD yn gallu analluogi ei hun dros dro (gan ddefnyddio'r botwm ar y tab dadfygio yn yr ymgom priodweddau yn Atmel Studio), gan ryddhau rheolaeth ar y llinell AILOSOD. Yna mae'r rhyngwyneb SPI ar gael eto (dim ond os yw'r ffiws SPIEN wedi'i raglennu), gan ganiatáu i'r ffiws DWEN fod heb ei raglennu gan ddefnyddio'r rhyngwyneb SPI. Os caiff pŵer ei doglo cyn i'r ffiws DWEN gael ei ddad-raglennu, bydd y modiwl debugWIRE unwaith eto yn rheoli'r pin AILOSOD.

Nodyn:

Fe'ch cynghorir yn gryf i adael i Stiwdio Atmel drin gosod a chlirio ffiws DWEN.

Nid yw'n bosibl defnyddio'r rhyngwyneb debugWIRE os yw'r cloeon ar y ddyfais AVR darged wedi'u rhaglennu. Gwnewch yn siŵr bob amser bod y lockbits yn cael eu clirio cyn rhaglennu'r ffiws DWEN a pheidiwch byth â gosod y lockbits tra bod ffiws DWEN wedi'i raglennu. Os yw'r ffiws galluogi debugWIRE (DWEN) a'r darnau clo wedi'u gosod, gall un ddefnyddio High Voltage Rhaglennu i ddileu sglodion, ac felly clirio'r cloeon.

Pan fydd y cloeon yn cael eu clirio bydd y rhyngwyneb debugWIRE yn cael ei ail-alluogi. Dim ond pan fydd ffiws DWEN heb ei raglennu y gall y Rhyngwyneb SPI ddarllen ffiwsiau, darllen llofnod a pherfformio dilead sglodion.

Tabl 3-5. Mapio Pin debugWIRE Atmel-ICE

| Pin porthladd AVR Atmel-ICE | Pinnau targed |

Pin sgwid bach |

| Pin 1 (TCK) | 1 | |

| Pin 2 (GND) | GND | 2 |

| Pin 3 (TDO) | 3 | |

| Pin 4 (VTG) | VTG | 4 |

| Pin 5 (TMS) | 5 | |

| Pin 6 (nSRST) | AILOSOD | 6 |

| Pin 7 (Ddim yn gysylltiedig) | 7 | |

| Pin 8 (nTRST) | 8 | |

| Pin 9 (TDI) | 9 | |

| Pin 10 (GND) | 0 |

3.7 Cysylltu â Tharged SPI

Dangosir y pinout a argymhellir ar gyfer y cysylltydd SPI 6-pin yn Ffigur 4-10.

Cysylltiad â phennawd SPI 6-pin 100-mil

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd SPI 100-mil safonol.

Cysylltiad â phennawd SPI 6-pin 50-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd SPI safonol 50-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen chwe chysylltiad, fel y disgrifir yn y tabl isod.

![]() Pwysig:

Pwysig:

Mae'r rhyngwyneb SPI wedi'i analluogi i bob pwrpas pan fydd y ffiws galluogi debugWIRE (DWEN) wedi'i raglennu, hyd yn oed os yw ffiws SPIEN hefyd wedi'i raglennu. I ail-alluogi'r rhyngwyneb SPI, rhaid cyhoeddi'r gorchymyn 'analluogi debugWIRE' tra mewn sesiwn dadfygio debugWIRE. Mae analluogi debugWIRE yn y modd hwn yn gofyn bod y ffiws SPIEN eisoes wedi'i raglennu. Os bydd Atmel Studio yn methu ag analluogi debugWIRE, mae'n debygol oherwydd NID yw'r ffiws SPIEN wedi'i raglennu. Os yw hyn yn wir, mae angen defnyddio cyfaint ucheltage rhyngwyneb rhaglennu i raglennu'r ffiws SPIEN.

![]() Gwybodaeth:

Gwybodaeth:

Cyfeirir yn aml at y rhyngwyneb SPI fel “ISP”, gan mai hwn oedd y rhyngwyneb Mewn Rhaglennu System cyntaf ar gynhyrchion Atmel AVR. Mae rhyngwynebau eraill bellach ar gael ar gyfer Rhaglennu Mewn System.

Tabl 3-6. Mapio Pin SPI Atmel-ICE

| Pinnau porthladd AVR Atmel-ICE | Pinnau targed | Pin sgwid bach |

SPI pinout |

| Pin 1 (TCK) | SCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | MISO | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | /AIL GYCHWYN | 6 | 5 |

| Pin 7 (ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | MOSI | 9 | 4 |

| Pin 10 (GND) | 0 |

3.8 Cysylltu â Tharged TPI

Dangosir y pinout a argymhellir ar gyfer y cysylltydd TPI 6-pin yn Ffigur 4-13.

Cysylltiad â phennawd TPI 6-pin 100-mil

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd TPI safonol 100-mil.

Cysylltiad â phennawd TPI 6-pin 50-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd TPI safonol 50-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen chwe chysylltiad, fel y disgrifir yn y tabl isod.

Tabl 3-7. Mapio Pin TPI Atmel-ICE

| Pinnau porthladd AVR Atmel-ICE | Pinnau targed | Pin sgwid bach |

TPI pinout |

| Pin 1 (TCK) | CLOC | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 |

| Pin 6 (nSRST) | /AIL GYCHWYN | 6 | 5 |

| Pin 7 (ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.9 Cysylltu â Tharged SWD

Mae rhyngwyneb ARM SWD yn is-set o system JTAG rhyngwyneb, gan ddefnyddio'r pinnau TCK a TMS, sy'n golygu, wrth gysylltu â dyfais SWD, y 10-pin JTAG gellir defnyddio cysylltydd yn dechnegol. Yr ARM JTAG ac AVR JTAG fodd bynnag, nid yw cysylltwyr yn gydnaws â pin, felly mae hyn yn dibynnu ar gynllun y bwrdd targed a ddefnyddir. Wrth ddefnyddio STK600 neu fwrdd gan ddefnyddio'r AVR JTAG pinout, rhaid defnyddio'r porthladd cysylltydd AVR ar yr Atmel-ICE. Wrth gysylltu â bwrdd, sy'n defnyddio'r ARM JTAG pinout, rhaid defnyddio'r porthladd cysylltydd SAM ar yr Atmel-ICE.

Dangosir y pinout a argymhellir ar gyfer y cysylltydd Cortex Debug 10-pin yn Ffigur 4-4.

Cysylltiad â phennawd Cortecs 10-pin 50-mil

Defnyddiwch y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd Cortex safonol 50-mil.

Cysylltiad â phennawd gosodiad Cortecs 10-pin 100-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd pinout Cortecs 100-mil.

Cysylltiad â phennawd SAM 20-pin 100-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd SAM 20-pin 100-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd Atmel-ICE AVR neu SAM a'r bwrdd targed. Mae angen chwe chysylltiad, fel y disgrifir yn y tabl isod.

Tabl 3-8. Mapio Pin SWD Atmel-ICE

| Enw | AVR pin porthladd | SAM pin porthladd | Disgrifiad |

| SWDC LK | 1 | 4 | Cloc Dadfygio Wire Cyfresol. |

| SWDIO | 5 | 2 | Mewnbwn/Allbwn Data Dadfygio Wire Cyfresol. |

| SWO | 3 | 6 | Allbwn Wire Cyfresol (dewisol - heb ei weithredu ar bob dyfais). |

| nSRST | 6 | 10 | Ailosod. |

| VTG | 4 | 1 | Cyfrol targedtage cyfeiriad. |

| GND | 2, 10 | 3, 5, 9 | Daear. |

3.10 Cysylltu â Rhyngwyneb Porth Data

Mae'r Atmel-ICE yn cefnogi Rhyngwyneb Porth Data cyfyngedig (DGI) pan nad yw dadfygio a rhaglennu yn cael eu defnyddio. Mae ymarferoldeb yn union yr un fath â'r hyn a geir ar gitiau Atmel Xplained Pro sy'n cael eu pweru gan ddyfais EDBG Atmel.

Mae'r Rhyngwyneb Porth Data yn rhyngwyneb ar gyfer ffrydio data o'r ddyfais darged i gyfrifiadur. Mae hyn yn cael ei olygu fel cymorth wrth debugging cais yn ogystal ag ar gyfer arddangos nodweddion yn y cais yn rhedeg ar y ddyfais targed.

Mae DGI yn cynnwys sawl sianel ar gyfer ffrydio data. Mae'r Atmel-ICE yn cefnogi'r dulliau canlynol:

- USART

- SPI

Tabl 3-9. Atmel-ICE DGI USART Pinout

|

porthladd AVR |

porthladd SAM | Pin DGI USART |

Disgrifiad |

| 3 | 6 | TX | Pin trosglwyddo o Atmel-ICE i'r ddyfais darged |

| 4 | 1 | VTG | Cyfrol targedtage (cyfeirnod cyftage) |

| 8 | 7 | RX | Derbyn pin o'r ddyfais darged i Atmel-ICE |

| 9 | 8 | CLK | cloc USART |

| 2, 10 | 3, 5, 9 | GND | Daear |

Tabl 3-10. Atmel-ICE DGI SPI Pinout

|

porthladd AVR |

porthladd SAM | Pin SPI DGI |

Disgrifiad |

| 1 | 4 | SCK | Cloc SPI |

| 3 | 6 | MISO | Meistr Mewn Caethwas Allan |

| 4 | 1 | VTG | Cyfrol targedtage (cyfeirnod cyftage) |

| 5 | 2 | nCS | Sglodion dewis gweithredol isel |

| 9 | 8 | MOSI | Meistr Caethwas Allan |

| 2, 10 | 3, 5, 9 | GND | Daear |

![]() Pwysig: Ni ellir defnyddio rhyngwynebau SPI ac USART ar yr un pryd.

Pwysig: Ni ellir defnyddio rhyngwynebau SPI ac USART ar yr un pryd.

![]() Pwysig: Ni ellir defnyddio DGI a rhaglennu neu ddadfygio ar yr un pryd.

Pwysig: Ni ellir defnyddio DGI a rhaglennu neu ddadfygio ar yr un pryd.

Dadfygio ar sglodion

4.1 Rhagymadrodd

Dadfygio ar sglodion

Mae modiwl dadfygio ar sglodion yn system sy'n caniatáu i ddatblygwr fonitro a rheoli gweithrediad ar ddyfais o lwyfan datblygu allanol, fel arfer trwy ddyfais a elwir yn addasydd dadfygiwr neu ddadfygio.

Gyda system OCD gellir gweithredu'r cais tra'n cynnal union nodweddion trydanol ac amseru yn y system darged, tra'n gallu atal gweithredu yn amodol neu â llaw ac archwilio llif a chof y rhaglen.

Modd Rhedeg

Pan yn y modd Run, mae gweithredu cod yn gwbl annibynnol ar yr Atmel-ICE. Bydd yr Atmel-ICE yn monitro'r ddyfais darged yn barhaus i weld a oes cyflwr torri wedi digwydd. Pan fydd hyn yn digwydd bydd y system OCD yn holi'r ddyfais trwy ei rhyngwyneb dadfygio, gan ganiatáu i'r defnyddiwr wneud hynny view cyflwr mewnol y ddyfais.

Modd Wedi'i Stopio

Pan gyrhaeddir torbwynt, caiff gweithrediad y rhaglen ei atal, ond gall rhai I/O barhau i redeg fel pe na bai torbwynt wedi digwydd. Am gynample, cymerwch fod trosglwyddiad USART newydd ei gychwyn pan gyrhaeddir torbwynt. Yn yr achos hwn mae'r USART yn parhau i redeg ar gyflymder llawn gan gwblhau'r trosglwyddiad, er bod y craidd yn y modd stopio.

Torbwyntiau Caledwedd

Mae'r modiwl OCD targed yn cynnwys nifer o gymaryddion cownter rhaglen a weithredir yn y caledwedd. Pan fydd rhifydd y rhaglen yn cyfateb i'r gwerth sydd wedi'i storio yn un o'r cofrestrau cymharydd, mae'r OCD yn mynd i mewn i'r modd stopio. Gan fod angen caledwedd pwrpasol ar y modiwl OCD ar gyfer torbwyntiau caledwedd, mae nifer y torbwyntiau sydd ar gael yn dibynnu ar faint y modiwl OCD a weithredir ar y targed. Fel arfer mae un cymharydd caledwedd o'r fath yn cael ei 'gadw' gan y dadfygiwr ar gyfer defnydd mewnol.

Torbwyntiau Meddalwedd

Mae torbwynt meddalwedd yn gyfarwyddyd BREAK a osodir yng nghof rhaglen ar y ddyfais darged. Pan fydd y cyfarwyddyd hwn wedi'i lwytho, bydd gweithrediad y rhaglen yn torri a bydd yr OCD yn mynd i mewn i'r modd stopio. Er mwyn parhau i weithredu mae'n rhaid rhoi gorchymyn “cychwyn” o'r OCD. Nid oes gan bob dyfais Atmel fodiwlau OCD sy'n cefnogi'r cyfarwyddyd BREAK.

4.2 Dyfeisiau SAM gyda JTAG/SWD

Mae pob dyfais SAM yn cynnwys y rhyngwyneb SWD ar gyfer rhaglennu a dadfygio. Yn ogystal, mae rhai dyfeisiau SAM yn cynnwys JTAG rhyngwyneb gyda swyddogaeth union yr un fath. Gwiriwch y daflen ddata dyfais ar gyfer rhyngwynebau a gefnogir y ddyfais honno.

4.2.1.Cydrannau CoreSight ARM

Mae microreolwyr seiliedig ar Atmel ARM Cortex-M yn gweithredu cydrannau OCD sy'n cydymffurfio â CoreSight. Gall nodweddion y cydrannau hyn amrywio o ddyfais i ddyfais. Am ragor o wybodaeth edrychwch ar daflen ddata'r ddyfais yn ogystal â dogfennaeth CoreSight a ddarperir gan ARM.

4.2.1. JTAG Rhyngwyneb Corfforol

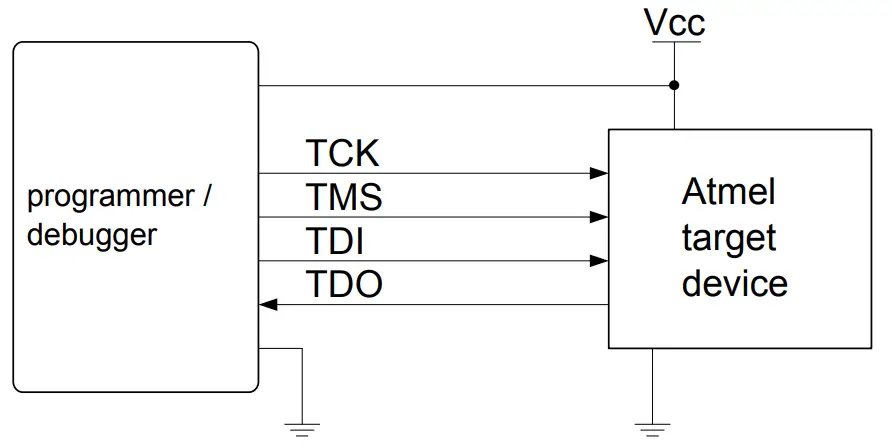

Mae'r J.TAG Mae'r rhyngwyneb yn cynnwys rheolydd Porthladd Mynediad Prawf 4-wifren (TAP) sy'n cydymffurfio â'r IEEE® 1149.1 safonol. Datblygwyd y safon IEEE i ddarparu ffordd o safon diwydiant i brofi cysylltedd bwrdd cylched yn effeithlon (Sganio Ffiniau). Mae dyfeisiau Atmel AVR a SAM wedi ymestyn y swyddogaeth hon i gynnwys cymorth Rhaglennu a Dadfygio Ar-sglodion llawn.

Ffigur 4-1. JTAG Hanfodion Rhyngwyneb

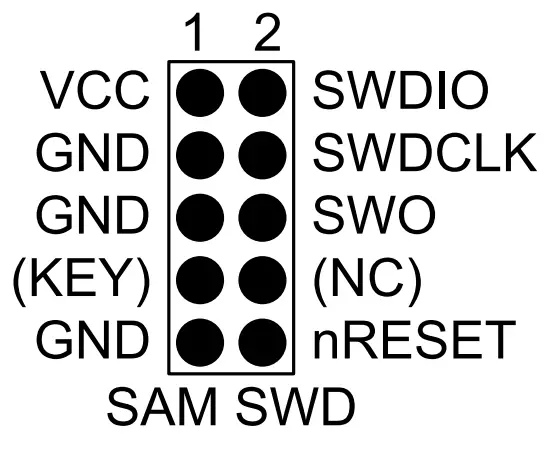

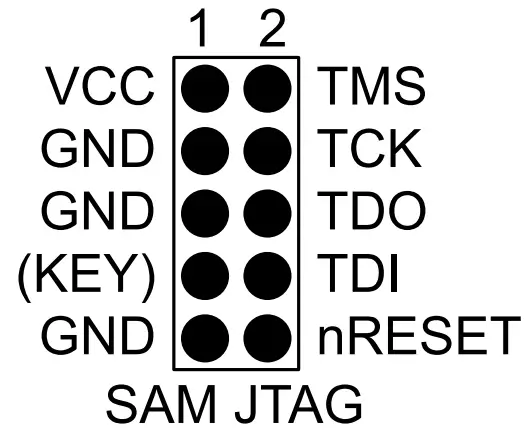

4.2.2.1 SAM JTAG Pinout (cysylltydd dadfygio Cortex-M)

Wrth ddylunio PCB cais sy'n cynnwys SAM Atmel gyda'r JTAG rhyngwyneb, argymhellir defnyddio'r pinout fel y dangosir yn y ffigur isod. Cefnogir amrywiadau 100-mil a 50-mil o'r pinout hwn, yn dibynnu ar y ceblau a'r addaswyr sydd wedi'u cynnwys gyda'r cit penodol.

Ffigur 4-2. SAM JTAG Pennawd Pinout

Tabl 4-1. SAM JTAG Disgrifiad Pin

| Enw | Pin |

Disgrifiad |

| TCK | 4 | Cloc Prawf (signal cloc o'r Atmel-ICE i'r ddyfais darged). |

| TMS | 2 | Dewis Modd Prawf (signal rheoli o'r Atmel-ICE i'r ddyfais darged). |

| TDI | 8 | Prawf Data Mewn (data a drosglwyddir o'r Atmel-ICE i'r ddyfais darged). |

| TDO | 6 | Profi Data Allan (data a drosglwyddir o'r ddyfais darged i'r Atmel-ICE). |

| nRESET | 10 | Ailosod (dewisol). Fe'i defnyddir i ailosod y ddyfais targed. Argymhellir cysylltu'r pin hwn gan ei fod yn caniatáu i'r Atmel-ICE ddal y ddyfais darged mewn cyflwr ailosod, a all fod yn hanfodol i ddadfygio mewn rhai senarios. |

| VTG | 1 | Cyfrol targedtage cyfeiriad. Yr Atmel-ICE samples y targed cyftage ar y pin hwn er mwyn pweru'r trawsnewidyddion lefel yn gywir. Mae'r Atmel-ICE yn tynnu llai nag 1mA o'r pin hwn yn y modd hwn. |

| GND | 3, 5, 9 | Ground. Rhaid cysylltu pob un i sicrhau bod yr Atmel-ICE a'r ddyfais darged yn rhannu'r un cyfeirnod daear. |

| ALLWEDD | 7 | Wedi'i gysylltu'n fewnol â'r pin TRST ar y cysylltydd AVR. Argymhellir gan nad yw'n gysylltiedig. |

![]() Awgrym: Cofiwch gynnwys cynhwysydd datgysylltu rhwng pin 1 a GND.

Awgrym: Cofiwch gynnwys cynhwysydd datgysylltu rhwng pin 1 a GND.

4.2.2.2 JTAG Llygad y dydd Cadwynu

Mae'r J.TAG rhyngwyneb yn caniatáu ar gyfer sawl dyfais i gael eu cysylltu â rhyngwyneb sengl mewn cyfluniad cadwyn llygad y dydd. Rhaid i'r dyfeisiau targed i gyd gael eu pweru gan yr un cyflenwad cyftage, rhannu nod tir cyffredin, a rhaid ei gysylltu fel y dangosir yn y ffigur isod.

Ffigur 4-3. JTAG Cadwyn llygad y dydd

Wrth gysylltu dyfeisiau mewn cadwyn llygad y dydd, rhaid ystyried y pwyntiau canlynol:

- Rhaid i bob dyfais rannu tir cyffredin, wedi'i gysylltu â GND ar y chwiliedydd Atmel-ICE

- Rhaid i bob dyfais fod yn gweithredu ar yr un targed cyftage. Rhaid cysylltu VTG ar yr Atmel-ICE â'r gyfrol hontage.

- Mae TMS a TCK wedi'u cysylltu yn gyfochrog; Mae TDI a TDO wedi'u cysylltu mewn cyfres

- Rhaid cysylltu nSRST ar y stiliwr Atmel-ICE ag AILOSOD ar y dyfeisiau os yw unrhyw un o'r dyfeisiau yn y gadwyn yn analluogi ei JTAG porthladd

- Mae “Dyfeisiau o'r blaen” yn cyfeirio at nifer JTAG dyfeisiau y mae'n rhaid i'r signal TDI basio drwyddynt yn y gadwyn llygad y dydd cyn cyrraedd y ddyfais darged. Yn yr un modd “dyfeisiau ar ôl” yw nifer y dyfeisiau y mae'n rhaid i'r signal basio trwyddynt ar ôl y ddyfais darged cyn cyrraedd y TDO Atmel-ICE

- Mae “darnau cyfarwyddyd “cyn” ac “ar ôl” yn cyfeirio at gyfanswm yr holl JTAG hyd cofrestr cyfarwyddiadau dyfeisiau, sy'n cael eu cysylltu cyn ac ar ôl y ddyfais darged yn y gadwyn llygad y dydd

- Mae cyfanswm hyd yr IR (darnau cyfarwyddyd cyn + hyd IR dyfais darged Atmel + darnau cyfarwyddyd ar ôl) wedi'i gyfyngu i uchafswm o 256 did. Mae nifer y dyfeisiau yn y gadwyn wedi'i gyfyngu i 15 cyn a 15 ar ôl.

![]() Awgrym:

Awgrym:

Daisy chaining example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Er mwyn cysylltu â'r Atmel AVR XMEGA® dyfais, gosodiadau cadwyn llygad y dydd yw:

- Dyfeisiau o'r blaen: 1

- Dyfeisiau ar ôl: 1

- Darnau cyfarwyddyd o'r blaen: 4 (mae gan ddyfeisiau AVR 8-did 4 did IR)

- Darnau cyfarwyddyd ar ôl: 5 (mae gan ddyfeisiau AVR 32-did 5 did IR)

Tabl 4-2. IR Hyd MCUs Atmel

| Math o ddyfais | hyd IR |

| AVR 8-did | 4 did |

| AVR 32-did | 5 did |

| SAM | 4 did |

4.2.3. Yn cysylltu â JTAG Targed

Mae gan yr Atmel-ICE ddau 50-mil 10-pin JTAG cysylltwyr. Mae'r ddau gysylltydd wedi'u cysylltu'n uniongyrchol â thrydan, ond maent yn cydymffurfio â dau binout gwahanol; yr AVR JTAG pennawd a phennawd ARM Cortex Debug. Dylid dewis y cysylltydd ar sail pinout y bwrdd targed, ac nid y math MCU targed - ar gyfer exampDylai dyfais SAM sydd wedi'i gosod mewn pentwr AVR STK600 ddefnyddio'r pennawd AVR.

Y pinout a argymhellir ar gyfer yr AVR J 10-pinTAG dangosir y cysylltydd yn Ffigur 4-6.

Dangosir y pinout a argymhellir ar gyfer y cysylltydd ARM Cortex Debug 10-pin yn Ffigur 4-2.

Cysylltiad uniongyrchol â phennawd safonol 10-pin 50-mil

Defnyddiwch y cebl fflat 50-mil 10-pin (wedi'i gynnwys mewn rhai citiau) i gysylltu'n uniongyrchol â bwrdd sy'n cefnogi'r math hwn o bennawd. Defnyddiwch y porthladd cysylltydd AVR ar yr Atmel-ICE ar gyfer penawdau gyda'r pinout AVR, a'r porthladd cysylltydd SAM ar gyfer penawdau sy'n cydymffurfio â pinout pennawd ARM Cortex Debug.

Mae'r pinouts ar gyfer y ddau borth cysylltydd 10-pin i'w gweld isod.

Cysylltiad â phennawd safonol 10-pin 100-mil

Defnyddiwch addasydd safonol 50-mil i 100-mil i gysylltu â phenawdau 100-mil. Gellir defnyddio bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) at y diben hwn, neu fel arall y JTAGGellir defnyddio addasydd ICE3 ar gyfer targedau AVR.

![]() Pwysig:

Pwysig:

Mae'r J.TAGNi ellir defnyddio addasydd ICE3 100-mil gyda'r porthladd cysylltydd SAM, gan fod pinnau 2 a 10 (AVR GND) ar yr addasydd wedi'u cysylltu.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Os nad oes gan eich bwrdd targed J 10-pin sy'n cydymffurfioTAG pennawd mewn 50- neu 100-mil, gallwch fapio i binout arferol gan ddefnyddio'r cebl “mini-squid” 10-pin (wedi'i gynnwys mewn rhai citiau), sy'n rhoi mynediad i ddeg soced 100-mil unigol.

Cysylltiad â phennawd 20-pin 100-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â thargedau gyda phennawd 20-pin 100-mil.

Tabl 4-3. Atmel- ICE JTAG Disgrifiad Pin

| Enw | AVR pin porthladd | SAM pin porthladd | Disgrifiad |

| TCK | 1 | 4 | Cloc Prawf (signal cloc o'r Atmel-ICE i'r ddyfais darged). |

| TMS | 5 | 2 | Dewis Modd Prawf (signal rheoli o'r Atmel-ICE i'r ddyfais darged). |

| TDI | 9 | 8 | Prawf Data Mewn (data a drosglwyddir o'r Atmel-ICE i'r ddyfais darged). |

| TDO | 3 | 6 | Profi Data Allan (data a drosglwyddir o'r ddyfais darged i'r Atmel-ICE). |

| nTRST | 8 | – | Ailosod Prawf (dewisol, dim ond ar rai dyfeisiau AVR). Fe'i defnyddir i ailosod y JTAG Rheolydd TAP. |

| nSRST | 6 | 10 | Ailosod (dewisol). Fe'i defnyddir i ailosod y ddyfais targed. Argymhellir cysylltu'r pin hwn gan ei fod yn caniatáu i'r Atmel-ICE ddal y ddyfais darged mewn cyflwr ailosod, a all fod yn hanfodol i ddadfygio mewn rhai senarios. |

| VTG | 4 | 1 | Cyfrol targedtage cyfeiriad. Yr Atmel-ICE samples y targed cyftage ar y pin hwn er mwyn pweru'r trawsnewidyddion lefel yn gywir. Mae'r Atmel-ICE yn tynnu llai na 3mA o'r pin hwn yn y modd debugWIRE a llai nag 1mA mewn moddau eraill. |

| GND | 2, 10 | 3, 5, 9 | Ground. Rhaid cysylltu pob un i sicrhau bod yr Atmel-ICE a'r ddyfais darged yn rhannu'r un cyfeirnod daear. |

4.2.4. Rhyngwyneb Corfforol SWD

Mae rhyngwyneb ARM SWD yn is-set o system JTAG rhyngwyneb, gan ddefnyddio pinnau TCK a TMS. Yr ARM JTAG ac AVR JTAG Fodd bynnag, nid yw cysylltwyr yn gydnaws â pin, felly wrth ddylunio PCB cymhwysiad, sy'n defnyddio dyfais SAM gyda SWD neu JTAG rhyngwyneb, argymhellir defnyddio'r pinout ARM a ddangosir yn y ffigur isod. Gall y porthladd cysylltydd SAM ar yr Atmel-ICE gysylltu'n uniongyrchol â'r pinout hwn.

Ffigur 4-4. Argymhellir ARM SWD/JTAG Pennawd Pinout

Mae'r Atmel-ICE yn gallu ffrydio olrhain ITM fformat UART i'r cyfrifiadur gwesteiwr. Mae Trace yn cael ei ddal ar y pin TRACE/SWO yn y pennawd 10-pin (JTAG TDO pin). Mae data'n cael ei glustogi'n fewnol ar yr Atmel-ICE ac yn cael ei anfon dros y rhyngwyneb HID i'r cyfrifiadur gwesteiwr. Y gyfradd ddata ddibynadwy uchaf yw tua 3MB/s.

4.2.5. Cysylltu â Tharged SWD

Mae rhyngwyneb ARM SWD yn is-set o system JTAG rhyngwyneb, gan ddefnyddio'r pinnau TCK a TMS, sy'n golygu, wrth gysylltu â dyfais SWD, y 10-pin JTAG gellir defnyddio cysylltydd yn dechnegol. Yr ARM JTAG ac AVR JTAG fodd bynnag, nid yw cysylltwyr yn gydnaws â pin, felly mae hyn yn dibynnu ar gynllun y bwrdd targed a ddefnyddir. Wrth ddefnyddio STK600 neu fwrdd gan ddefnyddio'r AVR JTAG pinout, rhaid defnyddio'r porthladd cysylltydd AVR ar yr Atmel-ICE. Wrth gysylltu â bwrdd, sy'n defnyddio'r ARM JTAG pinout, rhaid defnyddio'r porthladd cysylltydd SAM ar yr Atmel-ICE.

Dangosir y pinout a argymhellir ar gyfer y cysylltydd Cortex Debug 10-pin yn Ffigur 4-4.

Cysylltiad â phennawd Cortecs 10-pin 50-mil

Defnyddiwch y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd Cortex safonol 50-mil.

Cysylltiad â phennawd gosodiad Cortecs 10-pin 100-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd pinout Cortecs 100-mil.

Cysylltiad â phennawd SAM 20-pin 100-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd SAM 20-pin 100-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd Atmel-ICE AVR neu SAM a'r bwrdd targed. Mae angen chwe chysylltiad, fel y disgrifir yn y tabl isod.

Tabl 4-4. Mapio Pin SWD Atmel-ICE

| Enw | AVR pin porthladd | SAM pin porthladd | Disgrifiad |

| SWDC LK | 1 | 4 | Cloc Dadfygio Wire Cyfresol. |

| SWDIO | 5 | 2 | Mewnbwn/Allbwn Data Dadfygio Wire Cyfresol. |

| SWO | 3 | 6 | Allbwn Wire Cyfresol (dewisol - heb ei weithredu ar bob dyfais). |

| nSRST | 6 | 10 | Ailosod. |

| VTG | 4 | 1 | Cyfrol targedtage cyfeiriad. |

| GND | 2, 10 | 3, 5, 9 | Daear. |

4.2.6 Ystyriaethau Arbennig

DILEU pin

Mae rhai dyfeisiau SAM yn cynnwys pin ERASE sy'n cael ei honni i berfformio dilead sglodion cyflawn a datgloi dyfeisiau y mae'r did diogelwch wedi'i osod arnynt. Mae'r nodwedd hon wedi'i chysylltu â'r ddyfais ei hun yn ogystal â'r rheolydd fflach ac nid yw'n rhan o'r craidd ARM.

NID yw'r pin ERASE yn rhan o unrhyw bennawd dadfygio, ac felly ni all yr Atmel-ICE haeru'r signal hwn i ddatgloi dyfais. Mewn achosion o'r fath dylai'r defnyddiwr gyflawni'r dileu â llaw cyn dechrau sesiwn dadfygio.

Rhyngwynebau ffisegol JTAG rhyngwyneb

Dylid cysylltu'r llinell AILOSOD bob amser fel y gall yr Atmel-ICE alluogi'r JTAG rhyngwyneb.

Rhyngwyneb SWD

Dylid cysylltu'r llinell AILOSOD bob amser fel y gall yr Atmel-ICE alluogi'r rhyngwyneb SWD.

4.3 Dyfeisiau AVR UC3 gyda JTAG/aWire

Mae pob dyfais AVR UC3 yn cynnwys y JTAG rhyngwyneb ar gyfer rhaglennu a dadfygio. Yn ogystal, mae rhai dyfeisiau AVR UC3 yn cynnwys y rhyngwyneb aWire gyda swyddogaeth union yr un fath gan ddefnyddio un wifren. Gwiriwch y daflen ddata dyfais ar gyfer rhyngwynebau a gefnogir y ddyfais honno

4.3.1 System Dadfygio Ar-sglodion Atmel AVR UC3

Mae system Atmel AVR UC3 OCD wedi'i dylunio yn unol â safon Nexus 2.0 (IEEE-ISTO 5001™-2003), sy'n safon dadfygio ar-sglodyn agored hynod hyblyg a phwerus ar gyfer microreolwyr 32-did. Mae'n cefnogi'r nodweddion canlynol:

- Datrysiad dadfygio sy'n cydymffurfio â Nexus

- Mae OCD yn cefnogi unrhyw gyflymder CPU

- Chwe thorbwynt caledwedd cownter rhaglen

- Dau dorbwynt data

- Gellir ffurfweddu torbwyntiau fel mannau gwylio

- Gellir cyfuno torbwyntiau caledwedd i roi toriad ar ystodau

- Nifer anghyfyngedig o dorbwyntiau rhaglen defnyddiwr (gan ddefnyddio BREAK)

- Olrhain cangen cownter rhaglen amser real, olrhain data, olrhain proses (a gefnogir gan ddadfygwyr yn unig gyda phorthladd dal olrhain cyfochrog)

I gael rhagor o wybodaeth am system AVR UC3 OCD, edrychwch ar Lawlyfrau Cyfeirio Technegol AVR32UC, sydd wedi'u lleoli ar www.atmel.com/uc3.

4.3.2. JTAG Rhyngwyneb Corfforol

Mae'r J.TAG Mae'r rhyngwyneb yn cynnwys rheolydd Porthladd Mynediad Prawf 4-wifren (TAP) sy'n cydymffurfio â'r IEEE® 1149.1 safonol. Datblygwyd y safon IEEE i ddarparu ffordd o safon diwydiant i brofi cysylltedd bwrdd cylched yn effeithlon (Sganio Ffiniau). Mae dyfeisiau Atmel AVR a SAM wedi ymestyn y swyddogaeth hon i gynnwys cymorth Rhaglennu a Dadfygio Ar-sglodion llawn.

Ffigur 4-5. JTAG Hanfodion Rhyngwyneb

4.3.2.1 AVR JTAG Pinout

Wrth ddylunio PCB cais, sy'n cynnwys AVR Atmel gyda'r JTAG rhyngwyneb, argymhellir defnyddio'r pinout fel y dangosir yn y ffigur isod. Cefnogir amrywiadau 100-mil a 50-mil o'r pinout hwn, yn dibynnu ar y ceblau a'r addaswyr sydd wedi'u cynnwys gyda'r cit penodol.

Ffigur 4-6. AVR JTAG Pennawd Pinout

Tabl 4-5. AVR JTAG Disgrifiad Pin

| Enw | Pin |

Disgrifiad |

| TCK | 1 | Cloc Prawf (signal cloc o'r Atmel-ICE i'r ddyfais darged). |

| TMS | 5 | Dewis Modd Prawf (signal rheoli o'r Atmel-ICE i'r ddyfais darged). |

| TDI | 9 | Prawf Data Mewn (data a drosglwyddir o'r Atmel-ICE i'r ddyfais darged). |

| TDO | 3 | Profi Data Allan (data a drosglwyddir o'r ddyfais darged i'r Atmel-ICE). |

| nTRST | 8 | Ailosod Prawf (dewisol, dim ond ar rai dyfeisiau AVR). Fe'i defnyddir i ailosod y JTAG Rheolydd TAP. |

| nSRST | 6 | Ailosod (dewisol). Fe'i defnyddir i ailosod y ddyfais targed. Argymhellir cysylltu'r pin hwn gan ei fod yn caniatáu i'r Atmel-ICE ddal y ddyfais darged mewn cyflwr ailosod, a all fod yn hanfodol i ddadfygio mewn rhai senarios. |

| VTG | 4 | Cyfrol targedtage cyfeiriad. Yr Atmel-ICE samples y targed cyftage ar y pin hwn er mwyn pweru'r trawsnewidyddion lefel yn gywir. Mae'r Atmel-ICE yn tynnu llai na 3mA o'r pin hwn yn y modd debugWIRE a llai nag 1mA mewn moddau eraill. |

| GND | 2, 10 | Daear. Rhaid cysylltu'r ddau i sicrhau bod yr Atmel-ICE a'r ddyfais darged yn rhannu'r un cyfeiriad daear. |

![]() Awgrym: Cofiwch gynnwys cynhwysydd datgysylltu rhwng pin 4 a GND.

Awgrym: Cofiwch gynnwys cynhwysydd datgysylltu rhwng pin 4 a GND.

4.3.2.2 JTAG Llygad y dydd Cadwynu

Mae'r J.TAG rhyngwyneb yn caniatáu ar gyfer sawl dyfais i gael eu cysylltu â rhyngwyneb sengl mewn cyfluniad cadwyn llygad y dydd. Rhaid i'r dyfeisiau targed i gyd gael eu pweru gan yr un cyflenwad cyftage, rhannu nod tir cyffredin, a rhaid ei gysylltu fel y dangosir yn y ffigur isod.

Ffigur 4-7. JTAG Cadwyn llygad y dydd

Wrth gysylltu dyfeisiau mewn cadwyn llygad y dydd, rhaid ystyried y pwyntiau canlynol:

- Rhaid i bob dyfais rannu tir cyffredin, wedi'i gysylltu â GND ar y chwiliedydd Atmel-ICE

- Rhaid i bob dyfais fod yn gweithredu ar yr un targed cyftage. Rhaid cysylltu VTG ar yr Atmel-ICE â'r gyfrol hontage.

- Mae TMS a TCK wedi'u cysylltu yn gyfochrog; Mae TDI a TDO wedi'u cysylltu mewn cadwyn gyfresol.

- Rhaid cysylltu nSRST ar y stiliwr Atmel-ICE ag AILOSOD ar y dyfeisiau os yw unrhyw un o'r dyfeisiau yn y gadwyn yn analluogi ei JTAG porthladd

- Mae “Dyfeisiau o'r blaen” yn cyfeirio at nifer JTAG dyfeisiau y mae'n rhaid i'r signal TDI basio drwyddynt yn y gadwyn llygad y dydd cyn cyrraedd y ddyfais darged. Yn yr un modd “dyfeisiau ar ôl” yw nifer y dyfeisiau y mae'n rhaid i'r signal basio trwyddynt ar ôl y ddyfais darged cyn cyrraedd y TDO Atmel-ICE

- Mae “darnau cyfarwyddyd “cyn” ac “ar ôl” yn cyfeirio at gyfanswm yr holl JTAG hyd cofrestr cyfarwyddiadau dyfeisiau, sy'n cael eu cysylltu cyn ac ar ôl y ddyfais darged yn y gadwyn llygad y dydd

- Mae cyfanswm hyd yr IR (darnau cyfarwyddyd cyn + hyd IR dyfais darged Atmel + darnau cyfarwyddyd ar ôl) wedi'i gyfyngu i uchafswm o 256 did. Mae nifer y dyfeisiau yn y gadwyn wedi'i gyfyngu i 15 cyn a 15 ar ôl.

Awgrym:

Daisy chaining example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Er mwyn cysylltu â'r Atmel AVR XMEGA® dyfais, gosodiadau cadwyn llygad y dydd yw:

- Dyfeisiau o'r blaen: 1

- Dyfeisiau ar ôl: 1

- Darnau cyfarwyddyd o'r blaen: 4 (mae gan ddyfeisiau AVR 8-did 4 did IR)

- Darnau cyfarwyddyd ar ôl: 5 (mae gan ddyfeisiau AVR 32-did 5 did IR)

Tabl 4-6. IR Hyd Atmel MCUS

| Math o ddyfais | hyd IR |

| AVR 8-did | 4 did |

| AVR 32-did | 5 did |

| SAM | 4 did |

4.3.3.Cysylltu â JTAG Targed

Mae gan yr Atmel-ICE ddau 50-mil 10-pin JTAG cysylltwyr. Mae'r ddau gysylltydd wedi'u cysylltu'n uniongyrchol â thrydan, ond maent yn cydymffurfio â dau binout gwahanol; yr AVR JTAG pennawd a phennawd ARM Cortex Debug. Dylid dewis y cysylltydd ar sail pinout y bwrdd targed, ac nid y math MCU targed - ar gyfer exampDylai dyfais SAM sydd wedi'i gosod mewn pentwr AVR STK600 ddefnyddio'r pennawd AVR.

Y pinout a argymhellir ar gyfer yr AVR J 10-pinTAG dangosir y cysylltydd yn Ffigur 4-6.

Dangosir y pinout a argymhellir ar gyfer y cysylltydd ARM Cortex Debug 10-pin yn Ffigur 4-2.

Cysylltiad uniongyrchol â phennawd safonol 10-pin 50-mil

Defnyddiwch y cebl fflat 50-mil 10-pin (wedi'i gynnwys mewn rhai citiau) i gysylltu'n uniongyrchol â bwrdd sy'n cefnogi'r math hwn o bennawd. Defnyddiwch y porthladd cysylltydd AVR ar yr Atmel-ICE ar gyfer penawdau gyda'r pinout AVR, a'r porthladd cysylltydd SAM ar gyfer penawdau sy'n cydymffurfio â pinout pennawd ARM Cortex Debug.

Mae'r pinouts ar gyfer y ddau borth cysylltydd 10-pin i'w gweld isod.

Cysylltiad â phennawd safonol 10-pin 100-mil

Defnyddiwch addasydd safonol 50-mil i 100-mil i gysylltu â phenawdau 100-mil. Gellir defnyddio bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) at y diben hwn, neu fel arall y JTAGGellir defnyddio addasydd ICE3 ar gyfer targedau AVR.

![]() Pwysig:

Pwysig:

Mae'r J.TAGNi ellir defnyddio addasydd ICE3 100-mil gyda'r porthladd cysylltydd SAM, gan fod pinnau 2 a 10 (AVR GND) ar yr addasydd wedi'u cysylltu.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Os nad oes gan eich bwrdd targed J 10-pin sy'n cydymffurfioTAG pennawd mewn 50- neu 100-mil, gallwch fapio i binout arferol gan ddefnyddio'r cebl “mini-squid” 10-pin (wedi'i gynnwys mewn rhai citiau), sy'n rhoi mynediad i ddeg soced 100-mil unigol.

Cysylltiad â phennawd 20-pin 100-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â thargedau gyda phennawd 20-pin 100-mil.

Tabl 4-7. Atmel- ICE JTAG Disgrifiad Pin

|

Enw |

Pin porthladd AVR | Pin porthladd SAM |

Disgrifiad |

| TCK | 1 | 4 | Cloc Prawf (signal cloc o'r Atmel-ICE i'r ddyfais darged). |

| TMS | 5 | 2 | Dewis Modd Prawf (signal rheoli o'r Atmel-ICE i'r ddyfais darged). |

| TDI | 9 | 8 | Prawf Data Mewn (data a drosglwyddir o'r Atmel-ICE i'r ddyfais darged). |

| TDO | 3 | 6 | Profi Data Allan (data a drosglwyddir o'r ddyfais darged i'r Atmel-ICE). |

| nTRST | 8 | – | Ailosod Prawf (dewisol, dim ond ar rai dyfeisiau AVR). Fe'i defnyddir i ailosod y JTAG Rheolydd TAP. |

| nSRST | 6 | 10 | Ailosod (dewisol). Fe'i defnyddir i ailosod y ddyfais targed. Argymhellir cysylltu'r pin hwn gan ei fod yn caniatáu i'r Atmel-ICE ddal y ddyfais darged mewn cyflwr ailosod, a all fod yn hanfodol i ddadfygio mewn rhai senarios. |

| VTG | 4 | 1 | Cyfrol targedtage cyfeiriad. Yr Atmel-ICE samples y targed cyftage ar y pin hwn er mwyn pweru'r trawsnewidyddion lefel yn gywir. Mae'r Atmel-ICE yn tynnu llai na 3mA o'r pin hwn yn y modd debugWIRE a llai nag 1mA mewn moddau eraill. |

| GND | 2, 10 | 3, 5, 9 | Ground. Rhaid cysylltu pob un i sicrhau bod yr Atmel-ICE a'r ddyfais darged yn rhannu'r un cyfeirnod daear. |

4.3.4 Rhyngwyneb Corfforol Wire

Mae'r rhyngwyneb aWire yn defnyddio gwifren AILOSOD y ddyfais AVR i ganiatáu swyddogaethau rhaglennu a dadfygio. Mae dilyniant galluogi arbennig yn cael ei drosglwyddo gan yr Atmel-ICE, sy'n analluogi ymarferoldeb AILOSOD diofyn y pin.Wrth ddylunio PCB cais, sy'n cynnwys AVR Atmel gyda'r rhyngwyneb aWire, argymhellir defnyddio'r pinout fel y dangosir yn Ffigur 4 -8. Cefnogir amrywiadau 100-mil a 50-mil o'r pinout hwn, yn dibynnu ar y ceblau a'r addaswyr sydd wedi'u cynnwys gyda'r cit penodol.

Ffigur 4-8. aWire Pinout Pennawd

![]() Awgrym:

Awgrym:

Gan fod aWire yn ryngwyneb hanner dwplecs, argymhellir gosod gwrthydd tynnu i fyny ar y llinell AILOSOD tua 47kΩ er mwyn osgoi canfod cam cychwyn ffug wrth newid cyfeiriad.

Gellir defnyddio'r rhyngwyneb aWire fel rhyngwyneb rhaglennu a dadfygio. Mae holl nodweddion y system OCD ar gael trwy'r 10-pin JTAG gellir cyrchu'r rhyngwyneb hefyd gan ddefnyddio aWire.

4.3.5 Cysylltu â Tharged aWire

Dim ond un llinell ddata yn ogystal â V sydd ei hangen ar ryngwyneb aWireCC a GND. Ar y targed y llinell hon yw'r llinell nRESET, er bod y dadfygiwr yn defnyddio'r JTAG Llinell TDO fel y llinell ddata.

Dangosir y pinout a argymhellir ar gyfer y cysylltydd aWire 6-pin yn Ffigur 4-8.

Cysylltiad â phennawd 6-pin 100-mil aWire

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd safonol 100-mil aWire.

Cysylltiad â phennawd 6-pin 50-mil aWire

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd safonol 50-mil aWire.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen tri chysylltiad, fel y disgrifir yn y tabl isod.

Tabl 4-8. Mapio Pin aWire Atmel-ICE

| Pinnau porthladd AVR Atmel-ICE | Pinnau targed | Pin sgwid bach |

aWire pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (Ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.3.6. Ystyriaethau Arbennig

JTAG rhyngwyneb

Ar rai dyfeisiau Atmel AVR UC3 mae'r JTAG nid yw'r porth wedi'i alluogi yn ddiofyn. Wrth ddefnyddio'r dyfeisiau hyn mae'n hanfodol cysylltu'r llinell AILOSOD fel y gall yr Atmel-ICE alluogi'r JTAG rhyngwyneb.

rhyngwyneb aWire

Mae cyfradd baud cyfathrebiadau aWire yn dibynnu ar amlder cloc y system, gan fod yn rhaid cydamseru data rhwng y ddau barth hyn. Bydd yr Atmel-ICE yn canfod yn awtomatig bod cloc y system wedi'i ostwng, ac yn ail-raddnodi ei gyfradd baud yn unol â hynny. Mae'r graddnodi awtomatig ond yn gweithio i lawr i amledd cloc system o 8kHz. Gall newid i gloc system is yn ystod sesiwn dadfygio achosi i gysylltiad â'r targed gael ei golli.

Os oes angen, gellir cyfyngu ar gyfradd baud aWire trwy osod paramedr cloc aWire. Bydd canfod awtomatig yn dal i weithio, ond gosodir gwerth nenfwd ar y canlyniadau.

Rhaid datgysylltu unrhyw gynhwysydd sefydlogi sy'n gysylltiedig â'r pin AILOSOD wrth ddefnyddio aWire gan y bydd yn ymyrryd â gweithrediad cywir y rhyngwyneb. Argymhellir pullup allanol gwan (10kΩ neu uwch) ar y llinell hon.

Modd cysgu diffodd

Mae gan rai dyfeisiau AVR UC3 reoleiddiwr mewnol y gellir ei ddefnyddio yn y modd cyflenwi 3.3V gyda llinellau I / O wedi'u rheoleiddio 1.8V. Mae hyn yn golygu bod y rheolydd mewnol yn pweru'r I/O craidd a'r rhan fwyaf o'r I/O. Dim ond Atmel AVR UN! mae dadfygiwr yn cefnogi dadfygio wrth ddefnyddio dulliau cysgu lle mae'r rheolydd hwn wedi'i gau i ffwrdd.

4.3.7. Defnydd EVTI / EVTO

Nid yw'r pinnau EVTI ac EVTO yn hygyrch ar yr Atmel-ICE. Fodd bynnag, gellir eu defnyddio o hyd ar y cyd ag offer allanol eraill.

Gellir defnyddio EVTI at y dibenion canlynol:

- Gellir gorfodi'r targed i roi'r gorau i weithredu mewn ymateb i ddigwyddiad allanol. Os yw'r darnau Digwyddiad Mewn Rheolaeth (EIC) yn y gofrestr DC yn cael eu hysgrifennu i 0b01, bydd trawsnewid uchel i isel ar y pin EVTI yn cynhyrchu cyflwr torbwynt. Rhaid i EVTI aros yn isel ar gyfer un cylch cloc CPU i warantu mai torbwynt yw Mae'r did Torbwynt Allanol (EXB) yn DS yn cael ei osod pan fydd hyn yn digwydd.

- Cynhyrchu negeseuon synchronization olrhain. Heb ei ddefnyddio gan yr Atmel-ICE.

Gellir defnyddio EVTO at y dibenion canlynol:

- Yn nodi bod y CPU wedi mynd i mewn i ddadfygio Mae gosod y darnau EOS yn DC i 0b01 yn achosi i'r pin EVTO gael ei dynnu'n isel ar gyfer un cylch cloc CPU pan fydd y ddyfais darged yn mynd i mewn i'r modd dadfygio. Gellir defnyddio'r signal hwn fel ffynhonnell sbardun ar gyfer osgilosgop allanol.

- Yn dangos bod y CPU wedi cyrraedd torbwynt neu bwynt gwylio. Trwy osod y did EOC mewn Cofrestr Rheoli Torribwynt/Gwylfan gyfatebol, nodir statws y torbwynt neu'r pwynt gwylio ar y pin EVTO. Rhaid gosod y darnau EOS yn DC i 0xb10 i alluogi'r nodwedd hon. Yna gellir cysylltu'r pin EVTO ag osgilosgop allanol er mwyn archwilio man gwylio

- Cynhyrchu signalau amseru olrhain. Heb ei ddefnyddio gan yr Atmel-ICE.

4.4 Dyfeisiau tinyAVR, megaAVR, a XMEGA

Mae dyfeisiau AVR yn cynnwys rhyngwynebau rhaglennu a dadfygio amrywiol. Gwiriwch y daflen ddata dyfais ar gyfer rhyngwynebau a gefnogir y ddyfais honno.

- Rhai bachAVR® dyfeisiau TPI Gellir defnyddio TPI ar gyfer rhaglennu'r ddyfais yn unig, ac nid oes gan y dyfeisiau hyn allu dadfygio ar sglodion o gwbl.

- Mae gan rai dyfeisiau tinyAVR a rhai dyfeisiau megaAVR y rhyngwyneb debugWIRE, sy'n cysylltu â system dadfygio ar sglodion a elwir yn tinyOCD. Mae gan bob dyfais â debugWIRE ryngwyneb SPI ar gyfer yn y system hefyd

- Mae gan rai dyfeisiau megaAVR JTAG rhyngwyneb ar gyfer rhaglennu a dadfygio, gyda system dadfygio ar sglodion a elwir hefyd yn Pob dyfais gyda JTAG hefyd yn cynnwys y rhyngwyneb SPI fel rhyngwyneb amgen ar gyfer rhaglennu yn y system.

- Mae gan bob dyfais AVR XMEGA y rhyngwyneb PDI ar gyfer rhaglennu ac mae gan rai dyfeisiau AVR XMEGA hefyd JTAG rhyngwyneb gyda swyddogaeth union yr un fath.

- Mae gan ddyfeisiau tinyAVR newydd ryngwyneb UPDI, a ddefnyddir ar gyfer rhaglennu a dadfygio

Tabl 4-9. Crynodeb Rhyngwynebau Rhaglennu a Dadfygio

|

|

UPDI | TPI | SPI | debugWIR E | JTAG | PDI | aWire |

SWD |

| bachAVR | Dyfeisiau newydd | Rhai dyfeisiau | Rhai dyfeisiau | Rhai dyfeisiau | ||||

| megaAV R | Pob dyfais | Rhai dyfeisiau | Rhai dyfeisiau | |||||

| AVR XMEGA | Rhai dyfeisiau | Pob dyfais | ||||||

| AVR UC | Pob dyfais | Rhai dyfeisiau | ||||||

| SAM | Rhai dyfeisiau | Pob dyfais |

4.4.1. JTAG Rhyngwyneb Corfforol

Mae'r J.TAG Mae'r rhyngwyneb yn cynnwys rheolydd Porthladd Mynediad Prawf 4-wifren (TAP) sy'n cydymffurfio â'r IEEE® 1149.1 safonol. Datblygwyd y safon IEEE i ddarparu ffordd o safon diwydiant i brofi cysylltedd bwrdd cylched yn effeithlon (Sganio Ffiniau). Mae dyfeisiau Atmel AVR a SAM wedi ymestyn y swyddogaeth hon i gynnwys cymorth Rhaglennu a Dadfygio Ar-sglodion llawn.

Ffigur 4-9. JTAG Hanfodion Rhyngwyneb 4.4.2. Yn cysylltu â JTAG Targed

4.4.2. Yn cysylltu â JTAG Targed

Mae gan yr Atmel-ICE ddau 50-mil 10-pin JTAG cysylltwyr. Mae'r ddau gysylltydd wedi'u cysylltu'n uniongyrchol â thrydan, ond maent yn cydymffurfio â dau binout gwahanol; yr AVR JTAG pennawd a phennawd ARM Cortex Debug. Dylid dewis y cysylltydd ar sail pinout y bwrdd targed, ac nid y math MCU targed - ar gyfer exampDylai dyfais SAM sydd wedi'i gosod mewn pentwr AVR STK600 ddefnyddio'r pennawd AVR.

Y pinout a argymhellir ar gyfer yr AVR J 10-pinTAG dangosir y cysylltydd yn Ffigur 4-6.

Dangosir y pinout a argymhellir ar gyfer y cysylltydd ARM Cortex Debug 10-pin yn Ffigur 4-2.

Cysylltiad uniongyrchol â phennawd safonol 10-pin 50-mil

Defnyddiwch y cebl fflat 50-mil 10-pin (wedi'i gynnwys mewn rhai citiau) i gysylltu'n uniongyrchol â bwrdd sy'n cefnogi'r math hwn o bennawd. Defnyddiwch y porthladd cysylltydd AVR ar yr Atmel-ICE ar gyfer penawdau gyda'r pinout AVR, a'r porthladd cysylltydd SAM ar gyfer penawdau sy'n cydymffurfio â pinout pennawd ARM Cortex Debug.

Mae'r pinouts ar gyfer y ddau borth cysylltydd 10-pin i'w gweld isod.

Cysylltiad â phennawd safonol 10-pin 100-mil

Defnyddiwch addasydd safonol 50-mil i 100-mil i gysylltu â phenawdau 100-mil. Gellir defnyddio bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) at y diben hwn, neu fel arall y JTAGGellir defnyddio addasydd ICE3 ar gyfer targedau AVR.

![]() Pwysig:

Pwysig:

Mae'r J.TAGNi ellir defnyddio addasydd ICE3 100-mil gyda'r porthladd cysylltydd SAM, gan fod pinnau 2 a 10 (AVR GND) ar yr addasydd wedi'u cysylltu.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Os nad oes gan eich bwrdd targed J 10-pin sy'n cydymffurfioTAG pennawd mewn 50- neu 100-mil, gallwch fapio i binout arferol gan ddefnyddio'r cebl “mini-squid” 10-pin (wedi'i gynnwys mewn rhai citiau), sy'n rhoi mynediad i ddeg soced 100-mil unigol.

Cysylltiad â phennawd 20-pin 100-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â thargedau gyda phennawd 20-pin 100-mil.

Tabl 4-10. Atmel- ICE JTAG Disgrifiad Pin

| Enw | AVR pin porthladd | SAM pin porthladd | Disgrifiad |

| TCK | 1 | 4 | Cloc Prawf (signal cloc o'r Atmel-ICE i'r ddyfais darged). |

| TMS | 5 | 2 | Dewis Modd Prawf (signal rheoli o'r Atmel-ICE i'r ddyfais darged). |

| TDI | 9 | 8 | Prawf Data Mewn (data a drosglwyddir o'r Atmel-ICE i'r ddyfais darged). |

| TDO | 3 | 6 | Profi Data Allan (data a drosglwyddir o'r ddyfais darged i'r Atmel-ICE). |

| nTRST | 8 | – | Ailosod Prawf (dewisol, dim ond ar rai dyfeisiau AVR). Fe'i defnyddir i ailosod y JTAG Rheolydd TAP. |

| nSRST | 6 | 10 | Ailosod (dewisol). Fe'i defnyddir i ailosod y ddyfais targed. Argymhellir cysylltu'r pin hwn gan ei fod yn caniatáu i'r Atmel-ICE ddal y ddyfais darged mewn cyflwr ailosod, a all fod yn hanfodol i ddadfygio mewn rhai senarios. |

| VTG | 4 | 1 | Cyfrol targedtage cyfeiriad. Yr Atmel-ICE samples y targed cyftage ar y pin hwn er mwyn pweru'r trawsnewidyddion lefel yn gywir. Mae'r Atmel-ICE yn tynnu llai na 3mA o'r pin hwn yn y modd debugWIRE a llai nag 1mA mewn moddau eraill. |

| GND | 2, 10 | 3, 5, 9 | Ground. Rhaid cysylltu pob un i sicrhau bod yr Atmel-ICE a'r ddyfais darged yn rhannu'r un cyfeirnod daear. |

4.4.3.SPI Rhyngwyneb Corfforol

Mae Rhaglennu Mewn-System yn defnyddio SPI mewnol targed Atmel AVR (Rhyngwyneb Ymylol Cyfresol) i lawrlwytho cod i'r fflach ac atgofion EEPROM. Nid yw'n rhyngwyneb debugging. Wrth ddylunio PCB cais, sy'n cynnwys AVR gyda'r rhyngwyneb SPI, dylid defnyddio'r pinout fel y dangosir yn y ffigur isod.

Ffigur 4-10. Pennawd SPI Pinout 4.4.4. Cysylltu â Tharged SPI

4.4.4. Cysylltu â Tharged SPI

Dangosir y pinout a argymhellir ar gyfer y cysylltydd SPI 6-pin yn Ffigur 4-10.

Cysylltiad â phennawd SPI 6-pin 100-mil

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd SPI 100-mil safonol.

Cysylltiad â phennawd SPI 6-pin 50-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd SPI safonol 50-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen chwe chysylltiad, fel y disgrifir yn y tabl isod.

![]() Pwysig:

Pwysig:

Mae'r rhyngwyneb SPI wedi'i analluogi i bob pwrpas pan fydd y ffiws galluogi debugWIRE (DWEN) wedi'i raglennu, hyd yn oed os yw ffiws SPIEN hefyd wedi'i raglennu. I ail-alluogi'r rhyngwyneb SPI, rhaid cyhoeddi'r gorchymyn 'analluogi debugWIRE' tra mewn sesiwn dadfygio debugWIRE. Mae analluogi debugWIRE yn y modd hwn yn gofyn bod y ffiws SPIEN eisoes wedi'i raglennu. Os bydd Atmel Studio yn methu ag analluogi debugWIRE, mae'n debygol oherwydd NID yw'r ffiws SPIEN wedi'i raglennu. Os yw hyn yn wir, mae angen defnyddio cyfaint ucheltage rhyngwyneb rhaglennu i raglennu'r ffiws SPIEN.

![]() Gwybodaeth:

Gwybodaeth:

Cyfeirir yn aml at y rhyngwyneb SPI fel “ISP”, gan mai hwn oedd y rhyngwyneb Mewn Rhaglennu System cyntaf ar gynhyrchion Atmel AVR. Mae rhyngwynebau eraill bellach ar gael ar gyfer Rhaglennu Mewn System.

Tabl 4-11. Mapio Pin SPI Atmel-ICE

| Pinnau porthladd AVR Atmel-ICE | Pinnau targed | Pin sgwid bach |

SPI pinout |

| Pin 1 (TCK) | SCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | MISO | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | /AIL GYCHWYN | 6 | 5 |

| Pin 7 (ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | MOSI | 9 | 4 |

| Pin 10 (GND) | 0 |

4.4.5. PDI

Mae'r Rhyngwyneb Rhaglen a Dadfygio (PDI) yn rhyngwyneb perchnogol Atmel ar gyfer rhaglennu allanol a dadfygio dyfais ar sglodion. Mae PDI Physical yn rhyngwyneb 2-pin sy'n darparu cyfathrebiad cydamserol hanner-dwplecs deugyfeiriadol â'r ddyfais darged.

Wrth ddylunio PCB cais, sy'n cynnwys AVR Atmel gyda'r rhyngwyneb PDI, dylid defnyddio'r pinout a ddangosir yn y ffigur isod. Yna gellir defnyddio un o'r addaswyr 6-pin a ddarperir gyda'r pecyn Atmel-ICE i gysylltu'r stiliwr Atmel-ICE â PCB y cais.

Ffigur 4-11. PDI Pennawd Pinout 4.4.6.Cysylltu â Tharged PDI

4.4.6.Cysylltu â Tharged PDI

Dangosir y pinout a argymhellir ar gyfer y cysylltydd PDI 6-pin yn Ffigur 4-11.

Cysylltiad â phennawd PDI 6-pin 100-mil

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd PDI safonol 100-mil.

Cysylltiad â phennawd PDI 6-pin 50-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd PDI safonol 50-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen pedwar cysylltiad, fel y disgrifir yn y tabl isod.

![]() Pwysig:

Pwysig:

Mae'r pinout sydd ei angen yn wahanol i'r JTAGICE mkII JTAG stiliwr, lle mae PDI_DATA wedi'i gysylltu â phin 9. Mae'r Atmel-ICE yn gydnaws â'r pinout a ddefnyddir gan yr Atmel-ICE, JTAGICE3, AVR ONE!, ac AVR Dragon™ cynnyrch.

Tabl 4-12. Mapio Pin PDI Atmel-ICE

|

Pin porthladd AVR Atmel-ICE |

Pinnau targed | Pin sgwid bach |

Atmel STK600 PDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | PDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.7. Rhyngwyneb Corfforol UPDI

Mae'r Rhaglen Unedig a Rhyngwyneb Dadfygio (UPDI) yn rhyngwyneb perchnogol Atmel ar gyfer rhaglennu allanol a dadfygio dyfais ar sglodion. Mae'n olynydd i'r rhyngwyneb corfforol PDI 2-wifren, sydd i'w gael ar bob dyfais AVR XMEGA. Mae UPDI yn rhyngwyneb un weiren sy'n darparu cyfathrebiad asyncronig hanner-dwplecs deugyfeiriadol â'r ddyfais darged at ddibenion rhaglennu a dadfygio.

Wrth ddylunio PCB cymhwysiad, sy'n cynnwys AVR Atmel gyda'r rhyngwyneb UPDI, dylid defnyddio'r pinout a ddangosir isod. Yna gellir defnyddio un o'r addaswyr 6-pin a ddarperir gyda'r pecyn Atmel-ICE i gysylltu'r stiliwr Atmel-ICE â PCB y cais.

Ffigur 4-12. Pinout Pennawd UPDI 4.4.7.1 UPDI ac /AILOSOD

4.4.7.1 UPDI ac /AILOSOD

Gall rhyngwyneb un-wifren UPDI fod yn bin pwrpasol neu'n bin a rennir, yn dibynnu ar y ddyfais AVR targed. Edrychwch ar daflen ddata'r ddyfais am ragor o wybodaeth.

Pan fydd y rhyngwyneb UPDI ar bin a rennir, gellir ffurfweddu'r pin i fod naill ai UPDI, / RESET, neu GPIO trwy osod y ffiwsiau RSTPINCFG[1:0].

Mae gan ffiwsiau RSTPNCFG[1:0] y ffurfweddiadau canlynol, fel y disgrifir yn y daflen ddata. Rhoddir goblygiadau ymarferol pob dewis yma.

Tabl 4-13. RSTPINCFG[1:0] Ffurfweddu Ffiwsiau

| RSTPNCFG[1:0] | Cyfluniad |

Defnydd |

| 00 | GPIO | Pin I/O pwrpas cyffredinol. Er mwyn cyrchu UPDI, rhaid rhoi pwls 12V ar y pin hwn. Nid oes ffynhonnell ailosod allanol ar gael. |

| 01 | UPDI | Pin rhaglennu a dadfygio pwrpasol. Nid oes ffynhonnell ailosod allanol ar gael. |

| 10 | Ailosod | Ailosod mewnbwn signal. Er mwyn cyrchu UPDI, rhaid rhoi pwls 12V ar y pin hwn. |

| 11 | Wedi'i gadw | NA |

Nodyn: Mae gan ddyfeisiau AVR hŷn ryngwyneb rhaglennu, a elwir yn “High-Voltage Rhaglennu” (mae amrywiadau cyfresol a chyfochrog yn bodoli.) Yn gyffredinol mae'r rhyngwyneb hwn yn ei gwneud yn ofynnol i 12V gael ei roi ar y pin / RESET trwy gydol y sesiwn raglennu. Mae'r rhyngwyneb UPDI yn rhyngwyneb hollol wahanol. Pin rhaglennu a dadfygio yw'r pin UPDI yn bennaf, y gellir ei asio i gael swyddogaeth amgen (/AILOSOD neu GPIO). Os dewisir y ffwythiant amgen yna mae angen pwls 12V ar y pin hwnnw er mwyn ail-actifadu'r swyddogaeth UPDI.

Nodyn: Os yw dyluniad yn gofyn am rannu'r signal UPDI oherwydd cyfyngiadau pin, rhaid cymryd camau i sicrhau y gellir rhaglennu'r ddyfais. Er mwyn sicrhau y gall y signal UPDI weithredu'n gywir, yn ogystal ag osgoi difrod i gydrannau allanol o'r pwls 12V, argymhellir datgysylltu unrhyw gydrannau ar y pin hwn wrth geisio dadfygio neu raglennu'r ddyfais. Gellir gwneud hyn gan ddefnyddio gwrthydd 0Ω, sy'n cael ei osod yn ddiofyn a'i dynnu neu ei ddisodli gan bennawd pin wrth ddadfygio. Mae'r cyfluniad hwn i bob pwrpas yn golygu y dylid gwneud rhaglennu cyn gosod y ddyfais.

![]() Pwysig: Nid yw'r Atmel-ICE yn cefnogi 12V ar y llinell UPDI. Mewn geiriau eraill, os yw'r pin UPDI wedi'i ffurfweddu fel GPIO neu AILOSOD ni fydd yr Atmel-ICE yn gallu galluogi'r rhyngwyneb UPDI.

Pwysig: Nid yw'r Atmel-ICE yn cefnogi 12V ar y llinell UPDI. Mewn geiriau eraill, os yw'r pin UPDI wedi'i ffurfweddu fel GPIO neu AILOSOD ni fydd yr Atmel-ICE yn gallu galluogi'r rhyngwyneb UPDI.

4.4.8.Cysylltu â Tharged UPDI

Dangosir y pinout a argymhellir ar gyfer y cysylltydd UPDI 6-pin yn Ffigur 4-12.

Cysylltiad â phennawd UPDI 6-pin 100-mil

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd UPDI safonol 100-mil.

Cysylltiad â phennawd UPDI 6-pin 50-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd UPDI safonol 50-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen tri chysylltiad, fel y disgrifir yn y tabl isod.

Tabl 4-14. Mapio Pin Atmel-ICE UPDI

| Pin porthladd AVR Atmel-ICE | Pinnau targed | Pin sgwid bach |

Atmel STK600 UPDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | [/AILOSOD synnwyr] | 6 | 5 |

| Pin 7 (Ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.9 Rhyngwyneb Corfforol TPI

Mae TPI yn rhyngwyneb rhaglennu yn unig ar gyfer rhai dyfeisiau AVR ATtiny. Nid yw'n rhyngwyneb dadfygio, ac nid oes gan y dyfeisiau hyn allu OCD. Wrth ddylunio PCB cais sy'n cynnwys AVR gyda'r rhyngwyneb TPI, dylid defnyddio'r pinout a ddangosir yn y ffigur isod.

Ffigur 4-13. Pinout Pennawd TPI 4.4.10.Cysylltu â Tharged TPI

4.4.10.Cysylltu â Tharged TPI

Dangosir y pinout a argymhellir ar gyfer y cysylltydd TPI 6-pin yn Ffigur 4-13.

Cysylltiad â phennawd TPI 6-pin 100-mil

Defnyddiwch y tap 6-pin 100-mil ar y cebl fflat (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd TPI safonol 100-mil.

Cysylltiad â phennawd TPI 6-pin 50-mil

Defnyddiwch y bwrdd addasydd (wedi'i gynnwys mewn rhai citiau) i gysylltu â phennawd TPI safonol 50-mil.

Cysylltiad â phennawd 100-mil wedi'i deilwra

Dylid defnyddio'r cebl sgwid mini 10-pin i gysylltu rhwng porthladd cysylltydd AVR Atmel-ICE a'r bwrdd targed. Mae angen chwe chysylltiad, fel y disgrifir yn y tabl isod.

Tabl 4-15. Mapio Pin TPI Atmel-ICE

| Pinnau porthladd AVR Atmel-ICE | Pinnau targed | Pin sgwid bach |

TPI pinout |

| Pin 1 (TCK) | CLOC | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | /AIL GYCHWYN | 6 | 5 |

| Pin 7 (ddim yn gysylltiedig) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.11. Dadfygio Uwch (AVR JTAG dyfeisiau /debugWIRE)

I/O Perifferolion

Bydd y rhan fwyaf o berifferolion I/O yn parhau i redeg er bod gweithrediad y rhaglen yn cael ei atal gan dorbwynt. Example: Os cyrhaeddir torbwynt yn ystod trosglwyddiad UART, bydd y trosglwyddiad yn cael ei gwblhau a bydd y darnau cyfatebol yn cael eu gosod. Bydd baner TXC (trosglwyddiad cyflawn) yn cael ei gosod a bydd ar gael ar gam sengl nesaf y cod er y byddai fel arfer yn digwydd yn ddiweddarach mewn dyfais wirioneddol.

Bydd pob modiwl I/O yn parhau i redeg yn y modd stopio gyda'r ddau eithriad canlynol:

- Amserydd/Cyfrifwyr (gellir eu ffurfweddu gan ddefnyddio pen blaen y feddalwedd)

- Amserydd corff gwarchod (bob amser wedi'i stopio i atal ailosodiadau yn ystod dadfygio)

Mynediad I/O Stepping Sengl

Gan fod yr I/O yn parhau i redeg yn y modd stopio, dylid cymryd gofal i osgoi rhai materion amseru. Am gynample, y cod:

Wrth redeg y cod hwn fel arfer, ni fyddai'r gofrestr TEMP yn darllen 0xAA yn ôl oherwydd ni fyddai'r data eto wedi'u cysylltu'n gorfforol i'r pin erbyn ei fod yn s.ampdan arweiniad gweithrediad IN. Rhaid gosod cyfarwyddyd NOP rhwng yr OUT a'r cyfarwyddyd IN i sicrhau bod y gwerth cywir yn bresennol yn y gofrestr PIN.

Fodd bynnag, wrth gamu'n unigol â'r swyddogaeth hon drwy'r OCD, bydd y cod hwn bob amser yn rhoi 0xAA yn y gofrestr PIN gan fod yr I/O yn rhedeg ar gyflymder llawn hyd yn oed pan fydd y craidd yn cael ei stopio yn ystod y cam sengl.

Camu sengl ac amseru

Mae angen darllen neu ysgrifennu rhai cofrestrau o fewn nifer benodol o gylchoedd ar ôl galluogi signal rheoli. Gan fod y cloc I/O a'r perifferolion yn parhau i redeg ar gyflymder llawn yn y modd stopio, ni fydd camu sengl trwy god o'r fath yn bodloni'r gofynion amseru. Rhwng dau gam sengl, efallai bod y cloc I/O wedi rhedeg miliynau o gylchoedd. Er mwyn darllen neu ysgrifennu cofrestrau â gofynion amseru o'r fath yn llwyddiannus, dylid perfformio'r dilyniant darllen neu ysgrifennu cyfan fel gweithrediad atomig sy'n rhedeg y ddyfais ar gyflymder llawn. Gellir gwneud hyn trwy ddefnyddio macro neu alwad ffwythiant i weithredu'r cod, neu ddefnyddio'r ffwythiant rhedeg-i-cyrchwr yn yr amgylchedd dadfygio

Cyrchu cofrestrau 16-did

Mae perifferolion Atmel AVR fel arfer yn cynnwys nifer o gofrestrau 16-did y gellir eu cyrchu trwy'r bws data 8-did (ee: TCNTn o amserydd 16-did). Rhaid cyrchu'r gofrestr 16-did trwy ddefnyddio dwy weithred darllen neu ysgrifennu. Gall torri yng nghanol mynediad 16-did neu gamu sengl drwy'r sefyllfa hon arwain at werthoedd gwallus.

Mynediad cyfyngedig i'r gofrestr I/O

Ni ellir darllen rhai cofrestri heb effeithio ar eu cynnwys. Mae cofrestrau o'r fath yn cynnwys y rhai sy'n cynnwys fflagiau sy'n cael eu clirio trwy ddarllen, neu gofrestrau data byffer (ee: UDR). Bydd pen blaen y feddalwedd yn atal darllen y cofrestrau hyn pan fyddant yn y modd stopio er mwyn cadw natur anymwthiol arfaethedig dadfygio OCD. Yn ogystal, ni ellir ysgrifennu rhai cofrestri'n ddiogel heb i sgil-effeithiau ddigwydd - mae'r cofrestrau hyn yn rhai darllen-yn-unig. Am gynample:

- Cofrestrau baneri, lle mae baner yn cael ei chlirio trwy ysgrifennu '1' i unrhyw Mae'r cofrestrau hyn yn ddarllen-yn-unig.

- Ni ellir darllen cofrestrau UDR a SPDR heb effeithio ar gyflwr y modiwl. Nid yw'r cofrestrau hyn

4.4.12. megaAVR Ystyriaethau Arbennig

Torbwyntiau meddalwedd

Gan ei fod yn cynnwys fersiwn cynnar o'r modiwl OCD, nid yw ATmega128[A] yn cefnogi'r defnydd o'r cyfarwyddyd BREAK ar gyfer torbwyntiau meddalwedd.

JTAG cloc

Rhaid nodi amledd y cloc targed yn gywir ym mhen blaen y feddalwedd cyn dechrau sesiwn dadfygio. Am resymau cydamseru, mae'r JTAG Rhaid i signal TCK fod yn llai nag un pedwerydd o'r amledd cloc targed ar gyfer dadfygio dibynadwy. Wrth raglennu trwy'r JTAG rhyngwyneb, mae amlder TCK wedi'i gyfyngu gan raddfa amlder uchaf y ddyfais darged, ac nid yr amlder cloc gwirioneddol sy'n cael ei ddefnyddio.

Wrth ddefnyddio'r osgiliadur RC mewnol, byddwch yn ymwybodol y gall yr amledd amrywio o ddyfais i ddyfais ac mae tymheredd a V yn effeithio arno.CC newidiadau. Byddwch yn geidwadol wrth nodi amledd y cloc targed.

JTAGffiwsiau EN ac OCDEN

Mae'r J.TAG mae'r rhyngwyneb wedi'i alluogi gan ddefnyddio'r JTAGEN ffiws, sy'n cael ei raglennu yn ddiofyn. Mae hyn yn caniatáu mynediad i'r JTAG rhyngwyneb rhaglennu. Trwy'r mecanwaith hwn, gellir rhaglennu ffiws OCDEN (yn ddiofyn nid yw OCDEN wedi'i raglennu). Mae hyn yn caniatáu mynediad i'r OCD er mwyn hwyluso dadfygio'r ddyfais. Bydd pen blaen y meddalwedd bob amser yn sicrhau bod ffiws OCDEN yn cael ei adael heb ei raglennu wrth derfynu sesiwn, gan gyfyngu ar y defnydd pŵer diangen gan y modiwl OCD. Os bydd y JTAGMae ffiws EN yn anfwriadol anabl, dim ond trwy ddefnyddio SPI neu High Vol y gellir ei ail-alluogitage dulliau rhaglennu.