ICE Debugger Programmaturi

ICE Debugger Programmaturi

Gwida għall-Utent Programmaturi u Debuggers

Programmaturi u Debuggers

Atmel-ICE

GWIDA GĦALL-UTENT

Id-Debugger Atmel-ICE

Atmel-ICE hija għodda qawwija ta 'żvilupp għad-debugging u l-ipprogrammar ta' mikrokontrolluri Atmel ®SAM u Atmel AVR ibbażati fuq ARM® Cortex®-M b'kapaċità ® On-Chip Debug.

Huwa jappoġġa:

- Ipprogrammar u debugging fuq iċ-ċippa tal-mikrokontrolluri Atmel AVR 32-bit kollha fuq iż-żewġ JTAG u aWire interfaces

- Programmazzjoni u debugging fuq iċ-ċippa tal-apparati kollha tal-familja Atmel AVR XMEGA® fuq iż-żewġ JTAG u PDI 2-wire interfaces

- Programmazzjoni (JTAG, SPI, UPDI) u debugging tal-mikrokontrolluri Atmel AVR 8-bit kollha b'appoġġ OCD fuq jew JTAG, debugWIRE jew interfaces UPDI

- Programmazzjoni u debugging tal-mikrokontrolluri kollha bbażati fuq Atmel SAM ARM Cortex-M kemm fuq SWD kif ukoll fuq JTAG interfaces

- Programmazzjoni (TPI) tal-mikrokontrolluri kollha Atmel tinyAVR® 8-bit b'appoġġ għal din l-interface

Ikkonsulta l-lista ta 'apparati appoġġjati fil-Gwida għall-Utent ta' Atmel Studio għal lista sħiħa ta 'apparati u interfaces appoġġjati minn dan ir-rilaxx tal-firmware.

Introduzzjoni

1.1. Introduzzjoni għall-Atmel-ICE

Atmel-ICE hija għodda ta 'żvilupp b'saħħitha għad-debugging u l-ipprogrammar ta' mikrokontrolluri Atmel SAM u Atmel AVR bbażati fuq ARM Cortex-M b'kapaċità ta 'Debug On-Chip.

Huwa jappoġġa:

- Programmazzjoni u debugging fuq iċ-ċippa tal-mikrokontrolluri Atmel AVR UC3 kollha fuq iż-żewġ JTAG u aWire interfaces

- Programmazzjoni u debugging fuq iċ-ċippa tal-apparati kollha tal-familja AVR XMEGA fuq iż-żewġ JTAG u PDI 2wire interfaces

- Programmazzjoni (JTAG u SPI) u debugging tal-mikrokontrolluri AVR 8-bit kollha b'appoġġ OCD fuq iż-żewġ JTAG jew interfaces debugWIRE

- Programmazzjoni u debugging tal-mikrokontrolluri kollha bbażati fuq Atmel SAM ARM Cortex-M kemm fuq SWD kif ukoll fuq JTAG interfaces

- Programmazzjoni (TPI) tal-mikrokontrolluri Atmel tinyAVR 8-bit kollha b'appoġġ għal din l-interface

1.2. Atmel-ICE Karatteristiċi

- Kompatibbli bis-sħiħ ma 'Atmel Studio

- Jappoġġja l-ipprogrammar u d-debugging tal-mikrokontrolluri Atmel AVR UC3 32-bit kollha

- Jappoġġja l-ipprogrammar u d-debugging tal-apparati AVR XMEGA kollha ta '8-bit

- Jappoġġja l-ipprogrammar u d-debugging tat-tagħmir kollu Atmel megaAVR® u tinyAVR ta' 8-bit b'OCD

- Jappoġġja l-ipprogrammar u d-debugging tal-mikrokontrolluri kollha bbażati fuq SAM ARM Cortex-M

- Vol operattiv fil-miratage firxa ta '1.62V sa 5.5V

- Jiġbed inqas minn 3mA mill-mira VTref meta tuża interface debugWIRE u inqas minn 1mA għall-interfaces l-oħra kollha

- Jappoġġja JTAG frekwenzi tal-arloġġ minn 32kHz sa 7.5MHz

- Jappoġġja frekwenzi tal-arloġġ PDI minn 32kHz sa 7.5MHz

- Jappoġġja debugWIRE baud rates minn 4kbit/s sa 0.5Mbit/s

- Jappoġġja rati baud aWire minn 7.5kbit/s sa 7Mbit/s

- Jappoġġja frekwenzi tal-arloġġ SPI minn 8kHz sa 5MHz

- Jappoġġja rati baud UPDI sa 750kbit/s

- Jappoġġja frekwenzi tal-arloġġ SWD minn 32kHz sa 10MHz

- USB 2.0 interface host ta 'veloċità għolja

- Qbid ta 'traċċa tas-serje ITM sa 3MB/s

- Jappoġġja interfaces DGI SPI u USART meta ma tiddibaggjax jew ipprogrammar

- Jappoġġja 10-pin 50-mil JTAG konnettur kemm bl-AVR kif ukoll bil-pinouts tal-Cortex. Il-kejbil tas-sonda standard jappoġġja AVR 6-pin ISP/PDI/TPI 100-mil headers kif ukoll 10-pin 50-mil. Adapter huwa disponibbli biex jappoġġja headers ta '6-pin 50-mil, 10-pin 100-mil, u 20-pin 100-mil. Diversi għażliet ta 'kit huma disponibbli b'kejbils u adapters differenti.

1.3. Rekwiżiti tas-Sistema

L-unità Atmel-ICE teħtieġ li ambjent ta 'debugging front-end Atmel Studio verżjoni 6.2 jew aktar tard ikun installat fuq il-kompjuter tiegħek.

L-Atmel-ICE għandu jkun imqabbad mal-kompjuter ospitanti bl-użu tal-kejbil USB provdut, jew kejbil Mikro-USB iċċertifikat.

Nibdew bl-Atmel-ICE

2.1. Kontenut tal-Kit Sħiħ

Il-kit sħiħ Atmel-ICE fih dawn l-oġġetti:

- Unità Atmel-ICE

- Kejbil USB (1.8m, veloċità għolja, Mikro-B)

- Bord ta 'l-adapter li fih adapters ta' 50-mil AVR, 100-mil AVR/SAM, u 100-mil 20-pin SAM

- Kejbil ċatt IDC b'konnettur 10-pin 50-mil u konnettur 6-pin 100-mil

- Kejbil tal-klamari mini 50-mil 10-pin b'10 x 100-mil sockets

Figura 2-1. Atmel-ICE Kontenut tal-Kit Sħiħ 2.2. Kontenut tal-Kit Bażiku

2.2. Kontenut tal-Kit Bażiku

Il-kit bażiku Atmel-ICE fih dawn l-oġġetti:

- Unità Atmel-ICE

- Kejbil USB (1.8m, veloċità għolja, Mikro-B)

- Kejbil ċatt IDC b'konnettur 10-pin 50-mil u konnettur 6-pin 100-mil

Figura 2-2. Kontenut tal-Kit Bażiku Atmel-ICE 2.3. Kontenut tal-Kit PCBA

2.3. Kontenut tal-Kit PCBA

Il-kit PCBA Atmel-ICE fih dawn l-oġġetti:

- Unità Atmel-ICE mingħajr inkapsulament tal-plastik

Figura 2-3. Atmel-ICE PCBA Kit Kontenut 2.4. Spare Parts Kits

2.4. Spare Parts Kits

Il-kits tal-ispare parts li ġejjin huma disponibbli:

- Kit adapter

- Kit tal-kejbil

Figura 2-4. Kontenut tal-Kit tal-Adapter Atmel-ICE 2.5. Kit Overview

2.5. Kit Overview

L-għażliet tal-kit Atmel-ICE huma murija dijagrammatikament hawn:

Figura 2-6. Atmel-ICE Kit Overview 2.6. Armar tal-Atmel-ICE

2.6. Armar tal-Atmel-ICE

L-unità Atmel-ICE tintbagħat mingħajr kejbils imwaħħla. Żewġ għażliet tal-kejbil huma pprovduti fil-kit sħiħ:

- Kejbil ċatt IDC 50-mil 10-pin b'ISP 6-pin u konnetturi 10-pin

- Kejbil mini-klamari 50-mil 10-pin b'10 x 100-mil sockets

Figura 2-7. Kejbils Atmel-ICE Għall-biċċa l-kbira tal-għanijiet, jista 'jintuża l-kejbil ċatt IDC ta' 50-mil 10-pin, li jgħaqqad jew b'mod nattiv mal-konnetturi ta '10-pin jew 6-pin tiegħu, jew konnessjoni permezz tal-bord tal-adapter. Tliet adapters huma pprovduti fuq PCBA żgħir wieħed. L-adapters li ġejjin huma inklużi:

Għall-biċċa l-kbira tal-għanijiet, jista 'jintuża l-kejbil ċatt IDC ta' 50-mil 10-pin, li jgħaqqad jew b'mod nattiv mal-konnetturi ta '10-pin jew 6-pin tiegħu, jew konnessjoni permezz tal-bord tal-adapter. Tliet adapters huma pprovduti fuq PCBA żgħir wieħed. L-adapters li ġejjin huma inklużi:

- 100-mil 10-pin JTAGadapter /SWD

- 100-mil 20-pin SAM JTAGadapter /SWD

- 50-mil 6-pin SPI/debugWIRE/PDI/aWire adapter

Figura 2-8. Adapters Atmel-ICE Nota:

Nota:

A 50-mil JTAG adapter ma ġiex ipprovdut - dan huwa minħabba li l-kejbil IDC 50-mil 10-pin jista 'jintuża biex jikkonnettja direttament ma' 50-mil JTAG header. Għan-numru tal-parti tal-komponent użat għall-konnettur 50-mil 10-pin, ara Atmel-ICE Target Connectors Numri tal-Partijiet.

Il-header ISP/PDI ta '6 pins huwa inkluż bħala parti mill-kejbil IDC ta' 10 pins. Din it-terminazzjoni tista' tinqata' jekk ma tkunx meħtieġa.

Biex tgħaqqad l-Atmel-ICE tiegħek fil-konfigurazzjoni default tagħha, qabbad il-kejbil IDC 10-pin 50-mil mal-unità kif muri hawn taħt. Kun żgur li torjenta l-kejbil sabiex il-wajer aħmar (pin 1) fuq il-kejbil jallinja mal-indikatur trijangolari fuq iċ-ċinturin blu tal-kompartiment. Il-kejbil għandu jgħaqqad 'il fuq mill-unità. Kun żgur li tikkonnettja mal-port li jikkorrispondi għall-pinout tal-mira tiegħek - AVR jew SAM.

Figura 2-9. Konnessjoni tal-Cable Atmel-ICE Figura 2-10. Atmel-ICE AVR Probe Connection

Figura 2-10. Atmel-ICE AVR Probe Connection

Figura 2-11. Konnessjoni tal-Probe Atmel-ICE SAM

Figura 2-11. Konnessjoni tal-Probe Atmel-ICE SAM 2.7. Ftuħ l-Atmel-ICE

2.7. Ftuħ l-Atmel-ICE

Nota:

Għal tħaddim normali, l-unità Atmel-ICE m'għandhiex tinfetaħ. Il-ftuħ tal-unità jsir bir-riskju tiegħek.

Għandhom jittieħdu prekawzjonijiet anti-statiċi.

L-egħluq Atmel-ICE jikkonsisti fi tliet komponenti tal-plastik separati - kopertura ta 'fuq, kopertura ta' isfel, u ċinturin blu - li jinqabdu flimkien waqt l-assemblaġġ. Biex tiftaħ l-unità, sempliċement daħħal tornavit ċatt kbir fil-fetħiet fiċ-ċinturin blu, applika ftit pressjoni 'l ġewwa u dawwar bil-mod. Irrepeti l-proċess fuq it-toqob snapper l-oħra, u l-qoxra ta 'fuq tintefa'.

Figura 2-12. Ftuħ tal-Atmel-ICE (1)

Figura 2-13. Ftuħ tal-Atmel-ICE (2)

Figura 2-13. Ftuħ tal-Atmel-ICE (2)

Figura 2-14. Ftuħ l-Atmel-ICE(3)

Figura 2-14. Ftuħ l-Atmel-ICE(3) Biex tagħlaq l-unità mill-ġdid, sempliċement allinja l-għata ta 'fuq u ta' isfel b'mod korrett, u agħfas sew flimkien.

Biex tagħlaq l-unità mill-ġdid, sempliċement allinja l-għata ta 'fuq u ta' isfel b'mod korrett, u agħfas sew flimkien.

2.8. Li tħaddem l-Atmel-ICE

L-Atmel-ICE huwa mħaddem mill-bus USB voltage. Jeħtieġ inqas minn 100mA biex topera, u għalhekk jista 'jitħaddem permezz ta' hub USB. L-LED tal-qawwa se jdawwal meta l-unità tkun imdaħħla. Meta ma tkunx imqabbda f'sessjoni attiva ta 'programmazzjoni jew debugging, l-unità tidħol fil-mod ta' konsum ta 'enerġija baxxa biex tippreserva l-batterija tal-kompjuter tiegħek. L-Atmel-ICE ma jistax jitwaqqaf - għandu jiġi splaggjat meta ma jkunx qed jintuża.

2.9. Konnessjoni mal-Kompjuter Ospitanti

L-Atmel-ICE jikkomunika primarjament billi juża interface HID standard, u ma jeħtieġx sewwieq speċjali fuq il-kompjuter ospitanti. Biex tuża l-funzjonalità avvanzata tal-Gateway tad-Data tal-Atmel-ICE, kun żgur li tinstalla s-sewwieq USB fuq il-kompjuter ospitanti. Dan isir awtomatikament meta jiġi installat is-software front-end ipprovdut b'xejn minn Atmel. Ara www.atmel.com għal aktar informazzjoni jew biex tniżżel l-aħħar software front-end.

L-Atmel-ICE għandu jkun imqabbad ma 'port USB disponibbli fuq il-kompjuter ospitanti bl-użu tal-kejbil USB provdut, jew kejbil mikro USB ċertifikat xieraq. L-Atmel-ICE fih kontrollur konformi USB 2.0, u jista 'jopera kemm f'modi ta' veloċità sħiħa kif ukoll ta 'veloċità għolja. Għall-aħjar riżultati, qabbad l-Atmel-ICE direttament ma 'hub ta' veloċità għolja konformi USB 2.0 fuq il-kompjuter ospitanti billi tuża l-kejbil ipprovdut.

2.10. Installazzjoni tas-Sewwieq USB

2.10.1. Windows

Meta tinstalla l-Atmel-ICE fuq kompjuter li jħaddem Microsoft® Windows®, is-sewwieq USB jitgħabba meta l-Atmel-ICE jiġi pplaggjat għall-ewwel darba.

Nota:

Kun żgur li tinstalla l-pakketti tas-software front-end qabel ma twaħħal l-unità għall-ewwel darba.

Ladarba jiġi installat b'suċċess, l-Atmel-ICE se jidher fil-maniġer tal-apparat bħala "Apparat tal-Interface Uman".

Konnessjoni tal-Atmel-ICE

3.1. Konnessjoni ma 'AVR u SAM Target Devices

L-Atmel-ICE huwa mgħammar b'żewġ 50-mil 10-pin JTAG konnetturi. Iż-żewġ konnetturi huma direttament konnessi elettrikament, iżda jikkonformaw ma 'żewġ pinouts differenti; l-AVR JTAG header u l-header ARM Cortex Debug. Il-konnettur għandu jintgħażel abbażi tal-pinout tal-bord tal-mira, u mhux it-tip ta 'MCU fil-mira - per eżempjuample apparat SAM immuntat f'munzell AVR STK® 600 għandu juża l-header AVR.

Diversi kejbils u adapters huma disponibbli fil-kits Atmel-ICE differenti. An fuqview ta 'għażliet ta' konnessjoni hija murija.

Figura 3-1. Għażliet ta' Konnessjoni Atmel-ICE Il-wajer aħmar jimmarka l-pin 1 tal-konnettur 10-pin 50-mil. Pin 1 tal-konnettur 6-pin 100-mil jitqiegħed fuq il-lemin tal-keying meta l-konnettur jidher mill-cable. Il-pin 1 ta' kull konnettur fuq l-adapter huwa mmarkat b'tikka bajda. Il-figura hawn taħt turi l-pinout tal-kejbil tad-debug. Il-konnettur immarkat A jwaħħal fid-debugger filwaqt li n-naħa B twaħħal fil-bord tal-mira.

Il-wajer aħmar jimmarka l-pin 1 tal-konnettur 10-pin 50-mil. Pin 1 tal-konnettur 6-pin 100-mil jitqiegħed fuq il-lemin tal-keying meta l-konnettur jidher mill-cable. Il-pin 1 ta' kull konnettur fuq l-adapter huwa mmarkat b'tikka bajda. Il-figura hawn taħt turi l-pinout tal-kejbil tad-debug. Il-konnettur immarkat A jwaħħal fid-debugger filwaqt li n-naħa B twaħħal fil-bord tal-mira.

Figura 3-2. Iddebug Cable Pinout

3.2. Konnessjoni ma 'JTAG Mira

3.2. Konnessjoni ma 'JTAG Mira

L-Atmel-ICE huwa mgħammar b'żewġ 50-mil 10-pin JTAG konnetturi. Iż-żewġ konnetturi huma direttament konnessi elettrikament, iżda jikkonformaw ma 'żewġ pinouts differenti; l-AVR JTAG header u l-header ARM Cortex Debug. Il-konnettur għandu jintgħażel abbażi tal-pinout tal-bord tal-mira, u mhux it-tip ta 'MCU fil-mira - per eżempjuample apparat SAM immuntat fi munzell AVR STK600 għandu juża l-header AVR.

Il-pinout rakkomandat għall-AVR J 10-pinTAG konnettur huwa muri fil-Figura 4-6. Il-pinout rakkomandat għall-konnettur ta '10-pin ARM Cortex Debug jidher fil-Figura 4-2.

Konnessjoni diretta ma 'header standard ta' 10-pin 50-mil

Uża l-kejbil ċatt ta '50-mil 10-pin (inkluż f'xi kits) biex tikkonnettja direttament ma' bord li jappoġġja dan it-tip ta 'header. Uża l-port tal-konnettur AVR fuq l-Atmel-ICE għal headers bil-pinout AVR, u l-port tal-konnettur SAM għal headers li jikkonformaw mal-pinout header ARM Cortex Debug.

Il-pinouts għaż-żewġ portijiet tal-konnettur b'10 pins huma murija hawn taħt.

Konnessjoni ma 'header standard ta' 10-pin 100-mil

Uża adapter standard ta '50-mil għal 100-mil biex tikkonnettja ma' headers ta '100-mil. Bord ta 'l-adapter (inkluż f'xi kits) jista' jintuża għal dan il-għan, jew alternattivament il-JTAGL-adapter ICE3 jista 'jintuża għal miri AVR.

![]() Importanti:

Importanti:

Il-JTAGL-adapter ICE3 100-mil ma jistax jintuża mal-port tal-konnettur SAM, peress li l-pinnijiet 2 u 10 (AVR GND) fuq l-adapter huma konnessi.

Konnessjoni ma' header personalizzat ta' 100-mil

Jekk il-bord fil-mira tiegħek m'għandux J 10-pin konformiTAG header f'50- jew 100-mil, tista 'mappa għal pinout tad-dwana billi tuża l-kejbil "mini-klamari" ta' 10 pin (inkluż f'xi kits), li jagħti aċċess għal għaxar sokits individwali ta '100-mil.

Konnessjoni ma 'heade ta' 20 pin 100-milr

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' miri b'header ta '20-pin 100-mil.

Tabella 3-1. Atmel-ICE JTAG Deskrizzjoni tal-pin

| Isem | AVR pin tal-port | SAM pin tal-port | Deskrizzjoni |

| TCK | 1 | 4 | Test Clock (sinjal tal-arloġġ mill-Atmel-ICE fil-mezz fil-mira). |

| TMS | 5 | 2 | Agħżel il-Modalità tat-Test (sinjal ta 'kontroll mill-Atmel-ICE fil-mezz fil-mira). |

| TDI | 9 | 8 | Test Data In (data trażmessa mill-Atmel-ICE fl-apparat fil-mira). |

| TDO | 3 | 6 | Test Data Out (dejta trażmessa mill-apparat fil-mira fl-Atmel-ICE). |

| nTRST | 8 | – | Test Reset (mhux obbligatorju, biss fuq xi apparati AVR). Użat biex tirrisettja l-JTAG Kontrollur TAP. |

| nSRST | 6 | 10 | Irrisettja (mhux obbligatorju). Użat biex reset l-apparat fil-mira. Il-konnessjoni ta 'dan il-pin hija rakkomandata peress li tippermetti lill-Atmel-ICE li jżomm l-apparat fil-mira fi stat ta' reset, li jista 'jkun essenzjali għad-debugging f'ċerti xenarji. |

| VTG | 4 | 1 | Mira voltage referenza. L-Atmel-ICE samples il-mira voltage fuq dan il-pin sabiex tissaħħaħ il-konvertituri tal-livell b'mod korrett. L-Atmel-ICE jiġbed inqas minn 3mA minn dan il-pin fil-modalità debugWIRE u inqas minn 1mA f'modi oħra. |

| GND | 2, 10 | 3, 5, 9 | Art. Kollha għandhom ikunu konnessi biex jiġi żgurat li l-Atmel-ICE u l-apparat fil-mira jaqsmu l-istess referenza tal-art. |

3.3. Konnessjoni ma' Target aWire

L-interface aWire teħtieġ linja tad-dejta waħda biss minbarra VCC u GND. Fuq il-mira din il-linja hija l-linja nRESET, għalkemm id-debugger juża l-JTAG Linja TDO bħala l-linja tad-dejta.

Il-pinout rakkomandat għall-konnettur aWire b'6 pins jidher fil-Figura 4-8.

Konnessjoni ma 'header aWire ta' 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header standard ta' 100-mil aWire.

Konnessjoni ma 'header aWire ta' 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header standard ta '50-mil aWire.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Huma meħtieġa tliet konnessjonijiet, kif deskritt fit-tabella hawn taħt.

Tabella 3-2. Atmel-ICE aWire Pin Mapping

|

Pinnijiet tal-port Atmel-ICE AVR |

Labar tal-mira | Pin mini-klamari |

aWire pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DEJTA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (Mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.4. Konnessjoni ma 'PDI Target

Il-pinout rakkomandat għall-konnettur PDI b'6 pins jidher fil-Figura 4-11.

Konnessjoni ma 'header PDI ta' 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header PDI standard ta' 100-mil.

Konnessjoni ma 'header PDI ta' 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header PDI standard ta '50-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Huma meħtieġa erba' konnessjonijiet, kif deskritt fit-tabella hawn taħt.

![]() Importanti:

Importanti:

Il-pinout meħtieġ huwa differenti mill-JTAGICE mkII JTAG sonda, fejn PDI_DATA hija konnessa mal-pin 9. L-Atmel-ICE huwa kompatibbli mal-pinout użat mill-Atmel-ICE, JTAGProdotti ICE3, AVR ONE!, u AVR Dragon™.

Tabella 3-3. Atmel-ICE PDI Pin Mapping

| Pinnijiet tal-port Atmel-ICE AVR | Labar tal-mira | Pin mini-klamari |

aWire pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DEJTA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (Mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.4 Konnessjoni ma' Mira PDI

Il-pinout rakkomandat għall-konnettur PDI b'6 pins jidher fil-Figura 4-11.

Konnessjoni ma 'header PDI ta' 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header PDI standard ta' 100-mil.

Konnessjoni ma 'header PDI ta' 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header PDI standard ta '50-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Huma meħtieġa erba' konnessjonijiet, kif deskritt fit-tabella hawn taħt.

![]() Importanti:

Importanti:

Il-pinout meħtieġ huwa differenti mill-JTAGICE mkII JTAG sonda, fejn PDI_DATA hija konnessa mal-pin 9. L-Atmel-ICE huwa kompatibbli mal-pinout użat mill-Atmel-ICE, JTAGICE3, AVR ONE!, u AVR Dragon™ prodotti.

Tabella 3-3. Atmel-ICE PDI Pin Mapping

| Pin tal-port Atmel-ICE AVR | Labar tal-mira | Pin mini-klamari | Atmel STK600 PDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | PDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.5 Konnessjoni ma' Mira UPDI

Il-pinout rakkomandat għall-konnettur UPDI b'6 pins jidher fil-Figura 4-12.

Konnessjoni ma 'header UPDI ta' 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header UPDI standard ta' 100-mil.

Konnessjoni ma 'header UPDI ta' 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header UPDI standard ta '50-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Huma meħtieġa tliet konnessjonijiet, kif deskritt fit-tabella hawn taħt.

Tabella 3-4. Atmel-ICE UPDI Pin Mapping

| Pin tal-port Atmel-ICE AVR | Labar tal-mira | Pin mini-klamari |

Atmel STK600 UPDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | [/RESET sens] | 6 | 5 |

| Pin 7 (Mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.6 Konnessjoni ma 'DebugWIRE Target

Il-pinout rakkomandat għall-konnettur 6-pin debugWIRE (SPI) jidher fit-Tabella 3-6.

Konnessjoni ma 'header SPI 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header SPI standard ta' 100-mil.

Konnessjoni ma 'header SPI 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header SPI standard ta '50-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Huma meħtieġa tliet konnessjonijiet, kif deskritt fit-Tabella 3-5.

Għalkemm l-interface debugWIRE teħtieġ biss linja tas-sinjal waħda (RESET), VCC u GND biex joperaw b'mod korrett, huwa rakkomandat li jkollok aċċess għall-konnettur SPI sħiħ sabiex l-interface debugWIRE tkun tista 'tiġi attivata u diżattivata bl-użu ta' programmar SPI.

Meta l-fjus DWEN ikun attivat, l-interface SPI jinqabeż internament sabiex il-modulu OCD ikollu kontroll fuq il-pin RESET. Id-debugWIRE OCD huwa kapaċi li jiskonnettja lilu nnifsu temporanjament (bl-użu tal-buttuna fuq it-tab tad-debugging fid-djalogu tal-proprjetajiet f'Atmel Studio), u b'hekk jirrilaxxa l-kontroll tal-linja RESET. L-interface SPI mbagħad jerġa 'jkun disponibbli (biss jekk il-fjus SPIEN ikun ipprogrammat), li jippermetti li l-fjus DWEN ma jkunx ipprogrammat bl-użu tal-interface SPI. Jekk l-enerġija tiġi toggled qabel ma l-fjus DWEN ma jkunx ipprogrammat, il-modulu debugWIRE jerġa jieħu l-kontroll tal-pin RESET.

Nota:

Huwa rakkomandat ħafna li sempliċement tħalli lil Atmel Studio jimmaniġġja l-issettjar u l-ikklerjar tal-fjus DWEN.

Mhuwiex possibbli li tuża l-interface debugWIRE jekk il-lockbits fuq l-apparat AVR fil-mira huma pprogrammati. Dejjem kun żgur li l-lockbits jitneħħew qabel ma tipprogramma l-fjus DWEN u qatt ma ssettja l-lockbits waqt li l-fjus DWEN ikun ipprogrammat. Jekk kemm id-debugWIRE enable fuse (DWEN) kif ukoll il-lockbits huma ssettjati, wieħed jista' juża High Voltage Programmazzjoni biex tagħmel ċippa tħassir, u b'hekk ċara l-lockbits.

Meta l-lockbits jitneħħew l-interface debugWIRE se terġa 'tiġi attivata. L-Interface SPI huwa kapaċi biss jaqra fjusis, jaqra l-firma u jwettaq tħassir taċ-ċippa meta l-fjus DWEN ma jkunx ipprogrammat.

Tabella 3-5. Atmel-ICE debugWIRE Pin Mapping

| Pin tal-port Atmel-ICE AVR | Labar tal-mira |

Pin mini-klamari |

| Pin 1 (TCK) | 1 | |

| Pin 2 (GND) | GND | 2 |

| Pin 3 (TDO) | 3 | |

| Pin 4 (VTG) | VTG | 4 |

| Pin 5 (TMS) | 5 | |

| Pin 6 (nSRST) | RESET | 6 |

| Pin 7 (Mhux konness) | 7 | |

| Pin 8 (nTRST) | 8 | |

| Pin 9 (TDI) | 9 | |

| Pin 10 (GND) | 0 |

3.7 Konnessjoni ma' Mira SPI

Il-pinout rakkomandat għall-konnettur SPI 6-pin jidher fil-Figura 4-10.

Konnessjoni ma 'header SPI 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header SPI standard ta' 100-mil.

Konnessjoni ma 'header SPI 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header SPI standard ta '50-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Sitt konnessjonijiet huma meħtieġa, kif deskritt fit-tabella hawn taħt.

![]() Importanti:

Importanti:

L-interface SPI huwa diżattivat b'mod effettiv meta d-debugWIRE enable fuse (DWEN) huwa pprogrammat, anki jekk il-fjus SPIEN huwa pprogrammat ukoll. Biex terġa 'tippermetti l-interface SPI, il-kmand 'disable debugWIRE' għandu jinħareġ waqt li jkun f'sessjoni ta' debugWIRE. Id-diżattivazzjoni ta' debugWIRE b'dan il-mod teħtieġ li l-fjus SPIEN ikun diġà pprogrammat. Jekk Atmel Studio jonqos milli jiskonnettja debugWIRE, huwa probabbli minħabba li l-fjus SPIEN MHUX ipprogrammat. Jekk dan huwa l-każ, huwa meħtieġ li tuża high-voltage interface ta 'programmazzjoni biex tipprogramma l-fjus SPIEN.

![]() Informazzjoni:

Informazzjoni:

L-interface SPI spiss tissejjaħ "ISP", peress li kienet l-ewwel interface ta 'Programmazzjoni tas-Sistema fuq il-prodotti Atmel AVR. Interfaces oħra issa huma disponibbli għall-Ipprogrammar fis-Sistema.

Tabella 3-6. Atmel-ICE SPI Pin Mapping

| Pinnijiet tal-port Atmel-ICE AVR | Labar tal-mira | Pin mini-klamari |

SPI pinout |

| Pin 1 (TCK) | SCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | MISO | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | /RESET | 6 | 5 |

| Pin 7 (mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | MOSI | 9 | 4 |

| Pin 10 (GND) | 0 |

3.8 Konnessjoni ma' Mira TPI

Il-pinout rakkomandat għall-konnettur TPI 6-pin jidher fil-Figura 4-13.

Konnessjoni ma 'header TPI 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header TPI standard ta' 100-mil.

Konnessjoni ma 'header TPI 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header TPI standard ta '50-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Sitt konnessjonijiet huma meħtieġa, kif deskritt fit-tabella hawn taħt.

Tabella 3-7. Atmel-ICE TPI Pin Mapping

| Pinnijiet tal-port Atmel-ICE AVR | Labar tal-mira | Pin mini-klamari |

TPI pinout |

| Pin 1 (TCK) | ARLOĠĠ | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DEJTA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 |

| Pin 6 (nSRST) | /RESET | 6 | 5 |

| Pin 7 (mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.9 Konnessjoni ma' Mira SWD

L-interface ARM SWD huwa subsett tal-JTAG interface, billi tagħmel użu mill-labar TCK u TMS, li jfisser li meta tikkonnettja ma 'apparat SWD, il-J 10-pinTAG konnettur jista 'jintuża teknikament. L-ARM JTAG u AVR JTAG konnetturi, madankollu, mhumiex kompatibbli bil-pin, għalhekk dan jiddependi fuq it-tqassim tal-bord fil-mira li qed jintuża. Meta tuża STK600 jew bord li jagħmel użu mill-AVR JTAG pinout, il-port tal-konnettur AVR fuq l-Atmel-ICE għandu jintuża. Meta tikkonnettja ma 'bord, li jagħmel użu mill-ARM JTAG pinout, il-port tal-konnettur SAM fuq l-Atmel-ICE għandu jintuża.

Il-pinout rakkomandat għall-konnettur Cortex Debug b'10 pins jidher fil-Figura 4-4.

Konnessjoni ma 'header Cortex 10-pin 50-mil

Uża l-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header Cortex standard ta' 50-mil.

Konnessjoni ma 'header ta' tqassim tal-Cortex ta '10-pin 100-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header Cortex-pinout ta '100-mil.

Konnessjoni ma 'header SAM ta' 20-pin 100-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header SAM ta '20-pin 100-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR jew SAM u l-bord tal-mira. Sitt konnessjonijiet huma meħtieġa, kif deskritt fit-tabella hawn taħt.

Tabella 3-8. Atmel-ICE SWD Pin Mapping

| Isem | AVR pin tal-port | SAM pin tal-port | Deskrizzjoni |

| SWDC LK | 1 | 4 | Serial Wire Debug Arloġġ. |

| SWDIO | 5 | 2 | Input/Output tad-Data tad-Debug tal-Wajer Serjali. |

| SWO | 3 | 6 | Output tal-Wajer Serjali (mhux obbligatorju - mhux implimentat fuq l-apparati kollha). |

| nSRST | 6 | 10 | Irrisettja. |

| VTG | 4 | 1 | Mira voltage referenza. |

| GND | 2, 10 | 3, 5, 9 | Art. |

3.10 Konnessjoni mal-Interface Gateway tad-Data

L-Atmel-ICE jappoġġja Data Gateway Interface (DGI) limitat meta d-debugging u l-ipprogrammar ma jkunux qed jintużaw. Il-funzjonalità hija identika għal dik misjuba fuq il-kits Atmel Xplained Pro li jaħdmu bl-apparat Atmel EDBG.

L-Interface Gateway tad-Data hija interface għall-istrimjar tad-dejta mill-apparat fil-mira għal kompjuter. Dan huwa maħsub bħala għajnuna fid-debugging tal-applikazzjoni kif ukoll għad-dimostrazzjoni tal-karatteristiċi fl-applikazzjoni li taħdem fuq it-tagħmir fil-mira.

DGI jikkonsisti minn kanali multipli għall-istrimjar tad-dejta. L-Atmel-ICE jappoġġja l-modi li ġejjin:

- USART

- SPI

Tabella 3-9. Atmel-ICE DGI USART Pinout

|

Port AVR |

Port SAM | pin DGI USART |

Deskrizzjoni |

| 3 | 6 | TX | Ittrasmetti pin minn Atmel-ICE għall-apparat fil-mira |

| 4 | 1 | VTG | Mira voltage (referenza voltage) |

| 8 | 7 | RX | Irċievi pin mill-apparat fil-mira għal Atmel-ICE |

| 9 | 8 | CLK | Arloġġ USART |

| 2, 10 | 3, 5, 9 | GND | Art |

Tabella 3-10. Atmel-ICE DGI SPI Pinout

|

Port AVR |

Port SAM | DGI SPI pin |

Deskrizzjoni |

| 1 | 4 | SCK | Arloġġ SPI |

| 3 | 6 | MISO | Master In Slave Out |

| 4 | 1 | VTG | Mira voltage (referenza voltage) |

| 5 | 2 | nCS | Ċippa tagħżel attiva baxxa |

| 9 | 8 | MOSI | Master Out Slav In |

| 2, 10 | 3, 5, 9 | GND | Art |

![]() Importanti: L-interfaces SPI u USART ma jistgħux jintużaw simultanjament.

Importanti: L-interfaces SPI u USART ma jistgħux jintużaw simultanjament.

![]() Importanti: DGI u l-ipprogrammar jew id-debugging ma jistgħux jintużaw simultanjament.

Importanti: DGI u l-ipprogrammar jew id-debugging ma jistgħux jintużaw simultanjament.

Debugging fuq iċ-ċippa

4.1 Introduzzjoni

Debugging fuq iċ-ċippa

Modulu ta 'debug fuq iċ-ċippa huwa sistema li tippermetti lil żviluppatur jimmonitorja u jikkontrolla l-eżekuzzjoni fuq apparat minn pjattaforma ta' żvilupp esterna, ġeneralment permezz ta 'apparat magħruf bħala debugger jew adapter debug.

B'sistema OCD l-applikazzjoni tista' tiġi eżegwita filwaqt li jinżammu karatteristiċi elettriċi u ta' ħin eżatti fis-sistema fil-mira, filwaqt li tkun tista' twaqqaf l-eżekuzzjoni b'mod kondizzjonali jew manwali u tispezzjona l-fluss u l-memorja tal-programm.

Mexxi Modalità

Meta tkun fil-modalità Run, l-eżekuzzjoni tal-kodiċi hija kompletament indipendenti mill-Atmel-ICE. L-Atmel-ICE se jimmonitorja kontinwament l-apparat fil-mira biex jara jekk seħħitx kundizzjoni ta 'waqfien. Meta jiġri dan is-sistema OCD se tinterroga l-apparat permezz tal-interface tad-debug tagħha, li tippermetti lill-utent view l-istat intern tal-apparat.

Modalità waqfet

Meta jintlaħaq breakpoint, l-eżekuzzjoni tal-programm titwaqqaf, iżda xi I/O jistgħu jkomplu jaħdmu bħallikieku ma kien seħħ l-ebda breakpoint. Per example, jassumu li trażmissjoni USART għadu kif inbeda meta jintlaħaq breakpoint. F'dan il-każ l-USART tkompli taħdem b'veloċità sħiħa u tlesti t-trażmissjoni, anke jekk il-qalba tkun fil-modalità waqfien.

Breakpoints tal-Hardware

Il-modulu OCD fil-mira fih numru ta 'komparaturi tal-kontro tal-programmi implimentati fil-ħardwer. Meta l-counter tal-programm jaqbel mal-valur maħżun f'wieħed mir-reġistri tal-komparatur, l-OCD jidħol fil-mod waqfien. Billi l-breakpoints tal-hardware jeħtieġu ħardwer iddedikat fuq il-modulu OCD, in-numru ta' breakpoints disponibbli jiddependi fuq id-daqs tal-modulu OCD implimentat fuq il-mira. Normalment komparatur tal-ħardwer bħal dan huwa "riservat" mid-debugger għall-użu intern.

Breakpoints tas-Software

A breakpoint tas-softwer huwa istruzzjoni BREAK imqiegħda fil-memorja tal-programm fuq l-apparat fil-mira. Meta din l-istruzzjoni titgħabba, l-eżekuzzjoni tal-programm tinkiser u l-OCD jidħol fil-modalità waqfien. Biex titkompla l-eżekuzzjoni trid tingħata kmand ta' "bidu" mill-OCD. Mhux l-apparati Atmel kollha għandhom moduli OCD li jappoġġjaw l-istruzzjoni BREAK.

4.2 Apparat SAM b'JTAG/SWD

L-apparati SAM kollha għandhom l-interface SWD għall-ipprogrammar u d-debugging. Barra minn hekk, xi apparati SAM għandhom JTAG interface b'funzjonalità identika. Iċċekkja l-iskeda tad-dejta tal-apparat għal interfaces appoġġjati ta' dak l-apparat.

4.2.1.ARM CoreSight Komponenti

Mikrokontrolluri bbażati fuq Atmel ARM Cortex-M jimplimentaw komponenti OCD konformi ma 'CoreSight. Il-karatteristiċi ta 'dawn il-komponenti jistgħu jvarjaw minn apparat għal apparat. Għal aktar informazzjoni ikkonsulta d-datasheet tal-apparat kif ukoll id-dokumentazzjoni CoreSight ipprovduta minn ARM.

4.2.1. JTAG Interface Fiżiku

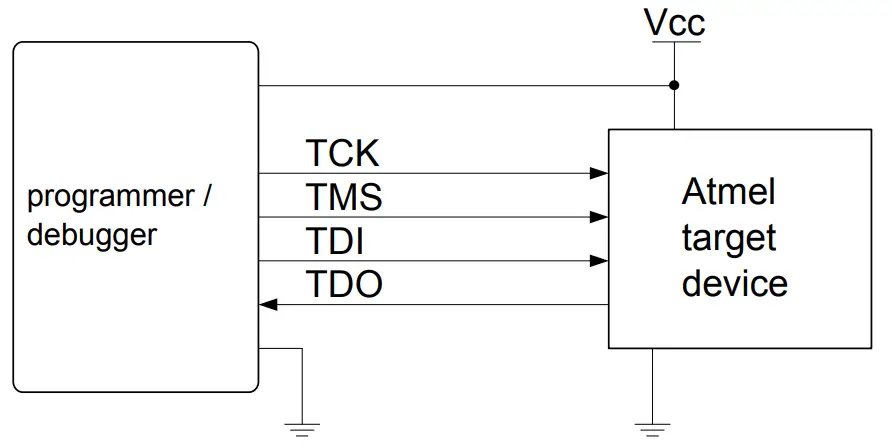

Il-JTAG interface jikkonsisti f'kontrollur ta' 4-wire Test Access Port (TAP) li huwa konformi mal-IEEE® 1149.1 standard. L-istandard IEEE ġie żviluppat biex jipprovdi mod standard tal-industrija biex tittestja b'mod effiċjenti l-konnettività tal-bord taċ-ċirkwit (Booundary Scan). L-apparati Atmel AVR u SAM estendew din il-funzjonalità biex jinkludu appoġġ sħiħ ta 'Programmazzjoni u Debugging On-chip.

Figura 4-1. JTAG Interface Basics

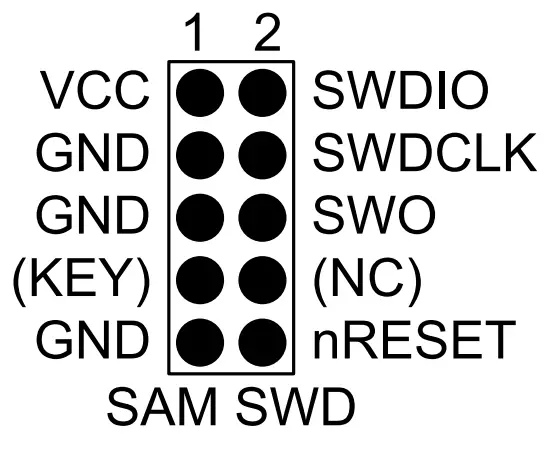

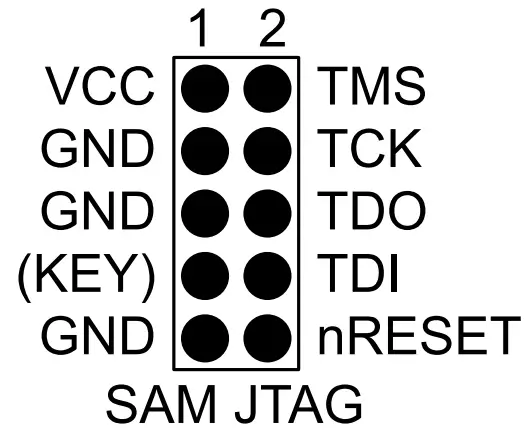

4.2.2.1 SAM JTAG Pinout (konnettur ta' debug Cortex-M)

Meta tfassal PCB ta' applikazzjoni li jinkludi Atmel SAM bil-JTAG interface, huwa rakkomandat li tuża l-pinout kif muri fil-figura hawn taħt. Iż-żewġ varjanti ta '100-mil u 50-mil ta' dan il-pinout huma appoġġjati, skont il-kejbils u l-adapters inklużi mal-kit partikolari.

Figura 4-2. SAM JTAG Header Pinout

Tabella 4-1. SAM JTAG Deskrizzjoni tal-pin

| Isem | Pin |

Deskrizzjoni |

| TCK | 4 | Test Clock (sinjal tal-arloġġ mill-Atmel-ICE fil-mezz fil-mira). |

| TMS | 2 | Agħżel il-Modalità tat-Test (sinjal ta 'kontroll mill-Atmel-ICE fil-mezz fil-mira). |

| TDI | 8 | Test Data In (data trażmessa mill-Atmel-ICE fl-apparat fil-mira). |

| TDO | 6 | Test Data Out (dejta trażmessa mill-apparat fil-mira fl-Atmel-ICE). |

| nRESET | 10 | Irrisettja (mhux obbligatorju). Użat biex reset l-apparat fil-mira. Il-konnessjoni ta 'dan il-pin hija rakkomandata peress li tippermetti lill-Atmel-ICE li jżomm l-apparat fil-mira fi stat ta' reset, li jista 'jkun essenzjali għad-debugging f'ċerti xenarji. |

| VTG | 1 | Mira voltage referenza. L-Atmel-ICE samples il-mira voltage fuq dan il-pin sabiex tissaħħaħ il-konvertituri tal-livell b'mod korrett. L-Atmel-ICE jiġbed inqas minn 1mA minn dan il-pin f'dan il-mod. |

| GND | 3, 5, 9 | Art. Kollha għandhom ikunu konnessi biex jiġi żgurat li l-Atmel-ICE u l-apparat fil-mira jaqsmu l-istess referenza tal-art. |

| EWLENIN | 7 | Imqabbad internament mal-pin TRST fuq il-konnettur AVR. Rakkomandat bħala mhux konness. |

![]() Tip: Ftakar li tinkludi kapaċitatur tad-diżakkoppjar bejn pin 1 u GND.

Tip: Ftakar li tinkludi kapaċitatur tad-diżakkoppjar bejn pin 1 u GND.

4.2.2.2 JTAG Daisy Katina

Il-JTAG interface jippermetti li diversi apparati jiġu konnessi ma 'interface waħda f'konfigurazzjoni ta' katina ta 'daisy. L-apparati fil-mira għandhom ikunu kollha mħaddma bl-istess provvista voltage, jaqsmu node art komuni, u għandhom ikunu konnessi kif muri fil-figura hawn taħt.

Figura 4-3. JTAG Daisy Chain

Meta tgħaqqad tagħmir f'daisy chain, għandhom jitqiesu l-punti li ġejjin:

- L-apparati kollha għandhom jaqsmu art komuni, imqabbda ma 'GND fuq is-sonda Atmel-ICE

- L-apparati kollha għandhom ikunu qed joperaw fuq l-istess mira voltage. VTG fuq l-Atmel-ICE għandhom ikunu konnessi ma 'dan il-voltage.

- TMS u TCK huma konnessi b'mod parallel; TDI u TDO huma konnessi f'serje

- nSRST fuq is-sonda Atmel-ICE għandu jkun imqabbad ma' RESET fuq l-apparati jekk xi wieħed mill-apparati fil-katina jiskonnettja l-J tiegħu.TAG port

- "Tagħmir qabel" tirreferi għan-numru ta' JTAG apparati li s-sinjal TDI irid jgħaddi minnu fil-katina tad-daisy qabel ma jilħaq l-apparat fil-mira. Bl-istess mod "apparati wara" huwa n-numru ta' apparati li s-sinjal irid jgħaddi minnu wara l-apparat fil-mira qabel ma jilħaq it-TDO Atmel-ICE

- "Bits ta' struzzjoni "qabel" u "wara" jirreferu għas-somma totali tal-JTAG tulijiet tar-reġistru tal-istruzzjoni tal-apparati, li huma konnessi qabel u wara l-apparat fil-mira fil-katina tad-daisy

- It-tul totali tal-IR (bits ta 'struzzjoni qabel + tul ta' IR tal-apparat fil-mira Atmel + bits ta 'struzzjoni wara) huwa limitat għal massimu ta' 256 bit. In-numru ta 'apparat fil-katina huwa limitat għal 15 qabel u 15 wara.

![]() Tip:

Tip:

Daisy chaining example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Sabiex tikkonnettja mal-Atmel AVR XMEGA® apparat, is-settings tal-katina tad-daisy huma:

- Apparat qabel: 1

- Apparat wara: 1

- Bits ta 'struzzjoni qabel: 4 (apparati AVR ta' 8 bit għandhom 4 bits IR)

- Bits ta 'struzzjoni wara: 5 (apparati AVR ta' 32 bit għandhom 5 bits IR)

Tabella 4-2. Tulijiet IR ta' Atmel MCUs

| Tip ta' apparat | Tul IR |

| AVR 8-bit | 4 bits |

| AVR 32-bit | 5 bits |

| SAM | 4 bits |

4.2.3. Konnessjoni ma 'JTAG Mira

L-Atmel-ICE huwa mgħammar b'żewġ 50-mil 10-pin JTAG konnetturi. Iż-żewġ konnetturi huma direttament konnessi elettrikament, iżda jikkonformaw ma 'żewġ pinouts differenti; l-AVR JTAG header u l-header ARM Cortex Debug. Il-konnettur għandu jintgħażel abbażi tal-pinout tal-bord tal-mira, u mhux it-tip ta 'MCU fil-mira - per eżempjuample apparat SAM immuntat fi munzell AVR STK600 għandu juża l-header AVR.

Il-pinout rakkomandat għall-AVR J 10-pinTAG konnettur huwa muri fil-Figura 4-6.

Il-pinout rakkomandat għall-konnettur ta '10-pin ARM Cortex Debug jidher fil-Figura 4-2.

Konnessjoni diretta ma 'header standard ta' 10-pin 50-mil

Uża l-kejbil ċatt ta '50-mil 10-pin (inkluż f'xi kits) biex tikkonnettja direttament ma' bord li jappoġġja dan it-tip ta 'header. Uża l-port tal-konnettur AVR fuq l-Atmel-ICE għal headers bil-pinout AVR, u l-port tal-konnettur SAM għal headers li jikkonformaw mal-pinout header ARM Cortex Debug.

Il-pinouts għaż-żewġ portijiet tal-konnettur b'10 pins huma murija hawn taħt.

Konnessjoni ma 'header standard ta' 10-pin 100-mil

Uża adapter standard ta '50-mil għal 100-mil biex tikkonnettja ma' headers ta '100-mil. Bord ta 'l-adapter (inkluż f'xi kits) jista' jintuża għal dan il-għan, jew alternattivament il-JTAGL-adapter ICE3 jista 'jintuża għal miri AVR.

![]() Importanti:

Importanti:

Il-JTAGL-adapter ICE3 100-mil ma jistax jintuża mal-port tal-konnettur SAM, peress li l-pinnijiet 2 u 10 (AVR GND) fuq l-adapter huma konnessi.

Konnessjoni ma' header personalizzat ta' 100-mil

Jekk il-bord fil-mira tiegħek m'għandux J 10-pin konformiTAG header f'50- jew 100-mil, tista 'mappa għal pinout tad-dwana billi tuża l-kejbil "mini-klamari" ta' 10 pin (inkluż f'xi kits), li jagħti aċċess għal għaxar sokits individwali ta '100-mil.

Konnessjoni ma 'header ta' 20 pin 100-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' miri b'header ta '20-pin 100-mil.

Tabella 4-3. Atmel-ICE JTAG Deskrizzjoni tal-pin

| Isem | AVR pin tal-port | SAM pin tal-port | Deskrizzjoni |

| TCK | 1 | 4 | Test Clock (sinjal tal-arloġġ mill-Atmel-ICE fil-mezz fil-mira). |

| TMS | 5 | 2 | Agħżel il-Modalità tat-Test (sinjal ta 'kontroll mill-Atmel-ICE fil-mezz fil-mira). |

| TDI | 9 | 8 | Test Data In (data trażmessa mill-Atmel-ICE fl-apparat fil-mira). |

| TDO | 3 | 6 | Test Data Out (dejta trażmessa mill-apparat fil-mira fl-Atmel-ICE). |

| nTRST | 8 | – | Test Reset (mhux obbligatorju, biss fuq xi apparati AVR). Użat biex tirrisettja l-JTAG Kontrollur TAP. |

| nSRST | 6 | 10 | Irrisettja (mhux obbligatorju). Użat biex reset l-apparat fil-mira. Il-konnessjoni ta 'dan il-pin hija rakkomandata peress li tippermetti lill-Atmel-ICE li jżomm l-apparat fil-mira fi stat ta' reset, li jista 'jkun essenzjali għad-debugging f'ċerti xenarji. |

| VTG | 4 | 1 | Mira voltage referenza. L-Atmel-ICE samples il-mira voltage fuq dan il-pin sabiex tissaħħaħ il-konvertituri tal-livell b'mod korrett. L-Atmel-ICE jiġbed inqas minn 3mA minn dan il-pin fil-modalità debugWIRE u inqas minn 1mA f'modi oħra. |

| GND | 2, 10 | 3, 5, 9 | Art. Kollha għandhom ikunu konnessi biex jiġi żgurat li l-Atmel-ICE u l-apparat fil-mira jaqsmu l-istess referenza tal-art. |

4.2.4. SWD Interface Fiżiku

L-interface ARM SWD huwa subsett tal-JTAG interface, bl-użu tal-labar TCK u TMS. L-ARM JTAG u AVR JTAG konnetturi, madankollu, mhumiex kompatibbli bil-pin, għalhekk meta tiddisinja PCB ta' applikazzjoni, li juża apparat SAM b'SWD jew JTAG interface, huwa rakkomandat li tuża l-pinout ARM murija fil-figura hawn taħt. Il-port tal-konnettur SAM fuq l-Atmel-ICE jista 'jikkonnettja direttament ma' dan il-pinout.

Figura 4-4. ARM SWD/J rakkomandatTAG Header Pinout

L-Atmel-ICE huwa kapaċi li jqassam traċċa ITM fil-format UART lill-kompjuter ospitanti. Traċċa tinqabad fuq il-pin TRACE/SWO tal-header b'10 pinnijiet (JTAG pin TDO). Id-dejta hija buffered internament fuq l-Atmel-ICE u tintbagħat fuq l-interface HID lill-kompjuter ospitanti. Ir-rata massima tad-data affidabbli hija madwar 3MB/s.

4.2.5. Konnessjoni ma' Mira SWD

L-interface ARM SWD huwa subsett tal-JTAG interface, billi tagħmel użu mill-labar TCK u TMS, li jfisser li meta tikkonnettja ma 'apparat SWD, il-J 10-pinTAG konnettur jista 'jintuża teknikament. L-ARM JTAG u AVR JTAG konnetturi, madankollu, mhumiex kompatibbli bil-pin, għalhekk dan jiddependi fuq it-tqassim tal-bord fil-mira li qed jintuża. Meta tuża STK600 jew bord li jagħmel użu mill-AVR JTAG pinout, il-port tal-konnettur AVR fuq l-Atmel-ICE għandu jintuża. Meta tikkonnettja ma 'bord, li jagħmel użu mill-ARM JTAG pinout, il-port tal-konnettur SAM fuq l-Atmel-ICE għandu jintuża.

Il-pinout rakkomandat għall-konnettur Cortex Debug b'10 pins jidher fil-Figura 4-4.

Konnessjoni ma 'header Cortex 10-pin 50-mil

Uża l-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header Cortex standard ta' 50-mil.

Konnessjoni ma 'header ta' tqassim tal-Cortex ta '10-pin 100-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header Cortex-pinout ta '100-mil.

Konnessjoni ma 'header SAM ta' 20-pin 100-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header SAM ta '20-pin 100-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR jew SAM u l-bord tal-mira. Sitt konnessjonijiet huma meħtieġa, kif deskritt fit-tabella hawn taħt.

Tabella 4-4. Atmel-ICE SWD Pin Mapping

| Isem | AVR pin tal-port | SAM pin tal-port | Deskrizzjoni |

| SWDC LK | 1 | 4 | Serial Wire Debug Arloġġ. |

| SWDIO | 5 | 2 | Input/Output tad-Data tad-Debug tal-Wajer Serjali. |

| SWO | 3 | 6 | Output tal-Wajer Serjali (mhux obbligatorju - mhux implimentat fuq l-apparati kollha). |

| nSRST | 6 | 10 | Irrisettja. |

| VTG | 4 | 1 | Mira voltage referenza. |

| GND | 2, 10 | 3, 5, 9 | Art. |

4.2.6 Konsiderazzjonijiet Speċjali

ERASE pin

Uħud mill-apparati SAM jinkludu pin ERASE li huwa affermat li jwettaq tħassir sħiħ taċ-ċippa u sblokka l-apparati li fuqhom ikun issettjat il-bit tas-sigurtà. Din il-karatteristika hija akkoppjata mal-apparat innifsu kif ukoll mal-kontrollur tal-flash u mhix parti mill-qalba ARM.

Il-pin ERASE MHUX parti minn kwalunkwe header ta 'debug, u l-Atmel-ICE għalhekk ma jistax jasserixxi dan is-sinjal biex jinfetaħ apparat. F'każijiet bħal dawn l-utent għandu jwettaq it-tħassir manwalment qabel ma jibda sessjoni ta 'debug.

Interfaċċji fiżiċi JTAG interface

Il-linja RESET għandha dejjem tkun imqabbda sabiex l-Atmel-ICE tkun tista’ tippermetti l-JTAG interface.

Interfaċċja SWD

Il-linja RESET għandha dejjem tkun konnessa sabiex l-Atmel-ICE tkun tista 'tippermetti l-interface SWD.

4.3 Apparat AVR UC3 b'JTAG/aWire

L-apparati AVR UC3 kollha għandhom il-JTAG interface għall-ipprogrammar u debugging. Barra minn hekk, xi apparati AVR UC3 għandhom l-interface aWire b'funzjonalità identika bl-użu ta 'wajer wieħed. Iċċekkja l-iskeda tad-dejta tal-apparat għal interfaces appoġġjati ta' dak l-apparat

4.3.1 Atmel AVR UC3 On-chip Debug System

Is-sistema Atmel AVR UC3 OCD hija ddisinjata skont l-istandard Nexus 2.0 (IEEE-ISTO 5001™-2003), li huwa standard ta 'debug miftuħ fuq iċ-ċippa flessibbli ħafna u qawwi għal mikrokontrolluri ta' 32 bit. Jappoġġja l-karatteristiċi li ġejjin:

- Soluzzjoni ta' debug konformi Nexus

- OCD jappoġġja kwalunkwe veloċità tas-CPU

- Sitt breakpoints tal-hardware tal-counter tal-programm

- Żewġ breakpoints tad-dejta

- Breakpoints jistgħu jiġu kkonfigurati bħala watchpoints

- Il-punti ta 'waqfien tal-ħardwer jistgħu jiġu kkombinati biex jagħtu waqfa fuq firxiet

- Numru illimitat ta' breakpoints tal-programm tal-utent (bl-użu ta' BREAK)

- Traċċar tal-fergħat tal-counter tal-programm f'ħin reali, traċċa tad-dejta, traċċa tal-proċess (sostnjata biss minn debuggers b'port parallel tal-qbid tat-traċċa)

Għal aktar informazzjoni dwar is-sistema AVR UC3 OCD, ikkonsulta l-Manwali ta’ Referenza Teknika AVR32UC, li jinsabu fuq www.atmel.com/uc3.

4.3.2. JTAG Interface Fiżiku

Il-JTAG interface jikkonsisti f'kontrollur ta' 4-wire Test Access Port (TAP) li huwa konformi mal-IEEE® 1149.1 standard. L-istandard IEEE ġie żviluppat biex jipprovdi mod standard tal-industrija biex tittestja b'mod effiċjenti l-konnettività tal-bord taċ-ċirkwit (Booundary Scan). L-apparati Atmel AVR u SAM estendew din il-funzjonalità biex jinkludu appoġġ sħiħ ta 'Programmazzjoni u Debugging On-chip.

Figura 4-5. JTAG Interface Basics

4.3.2.1 AVR JTAG Pinout

Meta tfassal PCB ta 'applikazzjoni, li jinkludi Atmel AVR mal-JTAG interface, huwa rakkomandat li tuża l-pinout kif muri fil-figura hawn taħt. Iż-żewġ varjanti ta '100-mil u 50-mil ta' dan il-pinout huma appoġġjati, skont il-kejbils u l-adapters inklużi mal-kit partikolari.

Figura 4-6. AVR JTAG Header Pinout

Tabella 4-5. AVR JTAG Deskrizzjoni tal-pin

| Isem | Pin |

Deskrizzjoni |

| TCK | 1 | Test Clock (sinjal tal-arloġġ mill-Atmel-ICE fil-mezz fil-mira). |

| TMS | 5 | Agħżel il-Modalità tat-Test (sinjal ta 'kontroll mill-Atmel-ICE fil-mezz fil-mira). |

| TDI | 9 | Test Data In (data trażmessa mill-Atmel-ICE fl-apparat fil-mira). |

| TDO | 3 | Test Data Out (dejta trażmessa mill-apparat fil-mira fl-Atmel-ICE). |

| nTRST | 8 | Test Reset (mhux obbligatorju, biss fuq xi apparati AVR). Użat biex tirrisettja l-JTAG Kontrollur TAP. |

| nSRST | 6 | Irrisettja (mhux obbligatorju). Użat biex reset l-apparat fil-mira. Il-konnessjoni ta 'dan il-pin hija rakkomandata peress li tippermetti lill-Atmel-ICE li jżomm l-apparat fil-mira fi stat ta' reset, li jista 'jkun essenzjali għad-debugging f'ċerti xenarji. |

| VTG | 4 | Mira voltage referenza. L-Atmel-ICE samples il-mira voltage fuq dan il-pin sabiex tissaħħaħ il-konvertituri tal-livell b'mod korrett. L-Atmel-ICE jiġbed inqas minn 3mA minn dan il-pin fil-modalità debugWIRE u inqas minn 1mA f'modi oħra. |

| GND | 2, 10 | Art. It-tnejn għandhom ikunu konnessi biex jiżguraw li l-Atmel-ICE u l-apparat fil-mira jaqsmu l-istess referenza tal-art. |

![]() Tip: Ftakar li tinkludi kapaċitatur tad-diżakkoppjar bejn pin 4 u GND.

Tip: Ftakar li tinkludi kapaċitatur tad-diżakkoppjar bejn pin 4 u GND.

4.3.2.2 JTAG Daisy Katina

Il-JTAG interface jippermetti li diversi apparati jiġu konnessi ma 'interface waħda f'konfigurazzjoni ta' katina ta 'daisy. L-apparati fil-mira għandhom ikunu kollha mħaddma bl-istess provvista voltage, jaqsmu node art komuni, u għandhom ikunu konnessi kif muri fil-figura hawn taħt.

Figura 4-7. JTAG Daisy Chain

Meta tgħaqqad tagħmir f'daisy chain, għandhom jitqiesu l-punti li ġejjin:

- L-apparati kollha għandhom jaqsmu art komuni, imqabbda ma 'GND fuq is-sonda Atmel-ICE

- L-apparati kollha għandhom ikunu qed joperaw fuq l-istess mira voltage. VTG fuq l-Atmel-ICE għandhom ikunu konnessi ma 'dan il-voltage.

- TMS u TCK huma konnessi b'mod parallel; TDI u TDO huma konnessi f'katina serjali.

- nSRST fuq is-sonda Atmel-ICE għandu jkun imqabbad ma' RESET fuq l-apparati jekk xi wieħed mill-apparati fil-katina jiskonnettja l-J tiegħu.TAG port

- "Tagħmir qabel" tirreferi għan-numru ta' JTAG apparati li s-sinjal TDI irid jgħaddi minnu fil-katina tad-daisy qabel ma jilħaq l-apparat fil-mira. Bl-istess mod "apparati wara" huwa n-numru ta' apparati li s-sinjal irid jgħaddi minnu wara l-apparat fil-mira qabel ma jilħaq it-TDO Atmel-ICE

- "Bits ta' struzzjoni "qabel" u "wara" jirreferu għas-somma totali tal-JTAG tulijiet tar-reġistru tal-istruzzjoni tal-apparati, li huma konnessi qabel u wara l-apparat fil-mira fil-katina tad-daisy

- It-tul totali tal-IR (bits ta 'struzzjoni qabel + tul ta' IR tal-apparat fil-mira Atmel + bits ta 'struzzjoni wara) huwa limitat għal massimu ta' 256 bit. In-numru ta 'apparat fil-katina huwa limitat għal 15 qabel u 15 wara.

Tip:

Daisy chaining example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Sabiex tikkonnettja mal-Atmel AVR XMEGA® apparat, is-settings tal-katina tad-daisy huma:

- Apparat qabel: 1

- Apparat wara: 1

- Bits ta 'struzzjoni qabel: 4 (apparati AVR ta' 8 bit għandhom 4 bits IR)

- Bits ta 'struzzjoni wara: 5 (apparati AVR ta' 32 bit għandhom 5 bits IR)

Tabella 4-6. IR Tulijiet ta' Atmel MCUS

| Tip ta' apparat | Tul IR |

| AVR 8-bit | 4 bits |

| AVR 32-bit | 5 bits |

| SAM | 4 bits |

4.3.3.Konnessjoni ma' JTAG Mira

L-Atmel-ICE huwa mgħammar b'żewġ 50-mil 10-pin JTAG konnetturi. Iż-żewġ konnetturi huma direttament konnessi elettrikament, iżda jikkonformaw ma 'żewġ pinouts differenti; l-AVR JTAG header u l-header ARM Cortex Debug. Il-konnettur għandu jintgħażel abbażi tal-pinout tal-bord tal-mira, u mhux it-tip ta 'MCU fil-mira - per eżempjuample apparat SAM immuntat fi munzell AVR STK600 għandu juża l-header AVR.

Il-pinout rakkomandat għall-AVR J 10-pinTAG konnettur huwa muri fil-Figura 4-6.

Il-pinout rakkomandat għall-konnettur ta '10-pin ARM Cortex Debug jidher fil-Figura 4-2.

Konnessjoni diretta ma 'header standard ta' 10-pin 50-mil

Uża l-kejbil ċatt ta '50-mil 10-pin (inkluż f'xi kits) biex tikkonnettja direttament ma' bord li jappoġġja dan it-tip ta 'header. Uża l-port tal-konnettur AVR fuq l-Atmel-ICE għal headers bil-pinout AVR, u l-port tal-konnettur SAM għal headers li jikkonformaw mal-pinout header ARM Cortex Debug.

Il-pinouts għaż-żewġ portijiet tal-konnettur b'10 pins huma murija hawn taħt.

Konnessjoni ma 'header standard ta' 10-pin 100-mil

Uża adapter standard ta '50-mil għal 100-mil biex tikkonnettja ma' headers ta '100-mil. Bord ta 'l-adapter (inkluż f'xi kits) jista' jintuża għal dan il-għan, jew alternattivament il-JTAGL-adapter ICE3 jista 'jintuża għal miri AVR.

![]() Importanti:

Importanti:

Il-JTAGL-adapter ICE3 100-mil ma jistax jintuża mal-port tal-konnettur SAM, peress li l-pinnijiet 2 u 10 (AVR GND) fuq l-adapter huma konnessi.

Konnessjoni ma' header personalizzat ta' 100-mil

Jekk il-bord fil-mira tiegħek m'għandux J 10-pin konformiTAG header f'50- jew 100-mil, tista 'mappa għal pinout tad-dwana billi tuża l-kejbil "mini-klamari" ta' 10 pin (inkluż f'xi kits), li jagħti aċċess għal għaxar sokits individwali ta '100-mil.

Konnessjoni ma 'header ta' 20 pin 100-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' miri b'header ta '20-pin 100-mil.

Tabella 4-7. Atmel-ICE JTAG Deskrizzjoni tal-pin

|

Isem |

Pin tal-port AVR | pin tal-port SAM |

Deskrizzjoni |

| TCK | 1 | 4 | Test Clock (sinjal tal-arloġġ mill-Atmel-ICE fil-mezz fil-mira). |

| TMS | 5 | 2 | Agħżel il-Modalità tat-Test (sinjal ta 'kontroll mill-Atmel-ICE fil-mezz fil-mira). |

| TDI | 9 | 8 | Test Data In (data trażmessa mill-Atmel-ICE fl-apparat fil-mira). |

| TDO | 3 | 6 | Test Data Out (dejta trażmessa mill-apparat fil-mira fl-Atmel-ICE). |

| nTRST | 8 | – | Test Reset (mhux obbligatorju, biss fuq xi apparati AVR). Użat biex tirrisettja l-JTAG Kontrollur TAP. |

| nSRST | 6 | 10 | Irrisettja (mhux obbligatorju). Użat biex reset l-apparat fil-mira. Il-konnessjoni ta 'dan il-pin hija rakkomandata peress li tippermetti lill-Atmel-ICE li jżomm l-apparat fil-mira fi stat ta' reset, li jista 'jkun essenzjali għad-debugging f'ċerti xenarji. |

| VTG | 4 | 1 | Mira voltage referenza. L-Atmel-ICE samples il-mira voltage fuq dan il-pin sabiex tissaħħaħ il-konvertituri tal-livell b'mod korrett. L-Atmel-ICE jiġbed inqas minn 3mA minn dan il-pin fil-modalità debugWIRE u inqas minn 1mA f'modi oħra. |

| GND | 2, 10 | 3, 5, 9 | Art. Kollha għandhom ikunu konnessi biex jiġi żgurat li l-Atmel-ICE u l-apparat fil-mira jaqsmu l-istess referenza tal-art. |

4.3.4 aWire Interface Fiżika

L-interface aWire jagħmel użu mill-wajer RESET tal-apparat AVR biex jippermetti funzjonijiet ta 'programmazzjoni u debugging. Sekwenza ta' attivazzjoni speċjali hija trażmessa mill-Atmel-ICE, li tiddiżattiva l-funzjonalità default RESET tal-pin. Meta tkun qed tiddisinja PCB ta' applikazzjoni, li tinkludi Atmel AVR bl-interface aWire, huwa rakkomandat li tuża l-pinout kif muri fil-Figura 4 -8. Iż-żewġ varjanti ta '100-mil u 50-mil ta' dan il-pinout huma appoġġjati, skont il-kejbils u l-adapters inklużi mal-kit partikolari.

Figura 4-8. aWire Header Pinout

![]() Tip:

Tip:

Peress li aWire huwa interface half-duplex, reżistenza pull-up fuq il-linja RESET fl-ordni ta '47kΩ hija rrakkomandata biex tevita skoperta falza ta' start-bit meta tinbidel id-direzzjoni.

L-interface aWire jista 'jintuża kemm bħala interface ta' programmazzjoni kif ukoll ta 'debugging. Il-karatteristiċi kollha tas-sistema OCD disponibbli permezz tal-JTAG interface jista 'jkun aċċessat wkoll bl-użu ta' aWire.

4.3.5 Konnessjoni ma' Target aWire

L-interface aWire teħtieġ linja tad-dejta waħda biss minbarra VCC u GND. Fuq il-mira din il-linja hija l-linja nRESET, għalkemm id-debugger juża l-JTAG Linja TDO bħala l-linja tad-dejta.

Il-pinout rakkomandat għall-konnettur aWire b'6 pins jidher fil-Figura 4-8.

Konnessjoni ma 'header aWire ta' 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header standard ta' 100-mil aWire.

Konnessjoni ma 'header aWire ta' 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header standard ta '50-mil aWire.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Huma meħtieġa tliet konnessjonijiet, kif deskritt fit-tabella hawn taħt.

Tabella 4-8. Atmel-ICE aWire Pin Mapping

| Pinnijiet tal-port Atmel-ICE AVR | Labar tal-mira | Pin mini-klamari |

aWire pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DEJTA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (Mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.3.6. Konsiderazzjonijiet Speċjali

JTAG interface

Fuq xi apparati Atmel AVR UC3 il-JTAG port mhux attivat awtomatikament. Meta tuża dawn l-apparati huwa essenzjali li tikkonnettja l-linja RESET sabiex l-Atmel-ICE tkun tista’ tippermetti l-JTAG interface.

aWire interface

Ir-rata baud tal-komunikazzjonijiet aWire tiddependi fuq il-frekwenza tal-arloġġ tas-sistema, peress li d-dejta trid tkun sinkronizzata bejn dawn iż-żewġ oqsma. L-Atmel-ICE awtomatikament jiskopri li l-arloġġ tas-sistema tbaxxa, u jerġa 'jikkalibra r-rata baud tiegħu kif xieraq. Il-kalibrazzjoni awtomatika taħdem biss sa frekwenza ta' arloġġ tas-sistema ta' 8kHz. Li taqleb għal arloġġ tas-sistema aktar baxx waqt sessjoni ta' debug jista' jikkawża li jintilef il-kuntatt mal-mira.

Jekk meħtieġ, ir-rata baud aWire tista 'tiġi ristretta billi jiġi stabbilit il-parametru tal-arloġġ aWire. L-iskoperta awtomatika xorta se taħdem, iżda se jiġi impost valur massimu fuq ir-riżultati.

Kwalunkwe capacitor stabilizzanti konness mal-pin RESET għandu jiġi skonnettjat meta tuża aWire peress li se jinterferixxi mat-tħaddim korrett tal-interface. A pullup estern dgħajjef (10kΩ jew ogħla) fuq din il-linja huwa rakkomandat.

Modalità ta 'rqad ta' għeluq

Xi apparati AVR UC3 għandhom regolatur intern li jista 'jintuża fil-mod ta' provvista ta '3.3V b'linji I/O regolati ta' 1.8V. Dan ifisser li r-regolatur intern iħaddem kemm il-qalba kif ukoll il-biċċa l-kbira tal-I/O. Atmel AVR ONE biss! debugger jappoġġja d-debugging waqt li juża modi sleep fejn dan ir-regolatur huwa mitfi.

4.3.7. Użu EVTI / EVTO

Il-brilli EVTI u EVTO mhumiex aċċessibbli fuq l-Atmel-ICE. Madankollu, xorta jistgħu jintużaw flimkien ma 'tagħmir estern ieħor.

EVTI jista' jintuża għall-għanijiet li ġejjin:

- Il-mira tista 'tiġi sfurzata twaqqaf l-eżekuzzjoni bi tweġiba għal avveniment estern. Jekk il-bits tal-Kontroll tal-Avveniment (EIC) fir-reġistru DC jinkitbu f'0b01, transizzjoni minn għoli għal baxx fuq il-pin EVTI se tiġġenera kundizzjoni ta' breakpoint. EVTI għandu jibqa' baxx għal ċiklu wieħed ta' arloġġ tas-CPU biex jiggarantixxi li punt ta' waqfien huwa.

- Ġenerazzjoni ta 'messaġġi ta' sinkronizzazzjoni tat-traċċa. Mhux użat mill-Atmel-ICE.

EVTO jista' jintuża għall-għanijiet li ġejjin:

- L-indikazzjoni li s-CPU daħal fid-debug L-issettjar tal-bits EOS f'DC għal 0b01 jikkawża li l-pin EVTO jinġibed baxx għal ċiklu wieħed tal-arloġġ tas-CPU meta l-apparat fil-mira jidħol fil-modalità tad-debug. Dan is-sinjal jista 'jintuża bħala sors ta' grillu għal oxxilloskopju estern.

- Tindika li s-CPU laħaq breakpoint jew watchpoint. Billi tissettja l-bit EOC f'Reġistru ta' Kontroll ta' Breakpoint/Watchpoint korrispondenti, il-punt ta' waqfien jew l-istatus tal-punt ta' sorveljanza huwa indikat fuq il-pin EVTO. Il-bits EOS f'DC għandhom ikunu ssettjati għal 0xb10 biex jippermettu din il-karatteristika. Il-pin EVTO jista 'mbagħad jiġi mqabbad ma' oxxilloskopju estern sabiex jiġi eżaminat il-punt tal-għassa

- Ġenerazzjoni ta 'sinjali ta' ħin ta 'traċċa. Mhux użat mill-Atmel-ICE.

4.4 Apparat tinyAVR, megaAVR, u XMEGA

L-apparati AVR għandhom diversi interfaces ta 'programmazzjoni u debugging. Iċċekkja l-iskeda tad-dejta tal-apparat għal interfaces appoġġjati ta' dak l-apparat.

- Xi tinyAVR® apparati għandhom TPI TPI jistgħu jintużaw għall-ipprogrammar tal-apparat biss, u dawn l-apparati m'għandhom l-ebda kapaċità ta 'debug fuq iċ-ċippa.

- Xi apparati tinyAVR u xi apparati megaAVR għandhom l-interface debugWIRE, li jgħaqqad ma 'sistema ta' debug fuq iċ-ċippa magħrufa bħala tinyOCD. L-apparati kollha b'debugWIRE għandhom ukoll l-interface SPI għal fis-sistema

- Xi apparati megaAVR għandhom JTAG interface għall-ipprogrammar u debugging, b'sistema ta 'debug fuq iċ-ċippa magħrufa wkoll bħala L-apparati kollha b'JTAG karatteristika wkoll l-interface SPI bħala interface alternattiv għall-ipprogrammar fis-sistema.

- L-apparati AVR XMEGA kollha għandhom l-interface PDI għall-ipprogrammar u Xi apparati AVR XMEGA għandhom ukoll JTAG interface b'funzjonalità identika.

- Apparat tinyAVR ġdid għandu interface UPDI, li jintuża għall-ipprogrammar u d-debugging

Tabella 4-9. Sommarju ta' Interfaces ta' Programmazzjoni u Debugging

|

|

UPDI | TPI | SPI | debugWIR E | JTAG | PDI | aWire |

SWD |

| tinyAVR | Apparati ġodda | Xi apparati | Xi apparati | Xi apparati | ||||

| megaAV R | L-apparati kollha | Xi apparati | Xi apparati | |||||

| AVR XMEGA | Xi apparati | L-apparati kollha | ||||||

| AVR UC | L-apparati kollha | Xi apparati | ||||||

| SAM | Xi apparati | L-apparati kollha |

4.4.1. JTAG Interface Fiżiku

Il-JTAG interface jikkonsisti f'kontrollur ta' 4-wire Test Access Port (TAP) li huwa konformi mal-IEEE® 1149.1 standard. L-istandard IEEE ġie żviluppat biex jipprovdi mod standard tal-industrija biex tittestja b'mod effiċjenti l-konnettività tal-bord taċ-ċirkwit (Booundary Scan). L-apparati Atmel AVR u SAM estendew din il-funzjonalità biex jinkludu appoġġ sħiħ ta 'Programmazzjoni u Debugging On-chip.

Figura 4-9. JTAG Interface Basics 4.4.2. Konnessjoni ma 'JTAG Mira

4.4.2. Konnessjoni ma 'JTAG Mira

L-Atmel-ICE huwa mgħammar b'żewġ 50-mil 10-pin JTAG konnetturi. Iż-żewġ konnetturi huma direttament konnessi elettrikament, iżda jikkonformaw ma 'żewġ pinouts differenti; l-AVR JTAG header u l-header ARM Cortex Debug. Il-konnettur għandu jintgħażel abbażi tal-pinout tal-bord tal-mira, u mhux it-tip ta 'MCU fil-mira - per eżempjuample apparat SAM immuntat fi munzell AVR STK600 għandu juża l-header AVR.

Il-pinout rakkomandat għall-AVR J 10-pinTAG konnettur huwa muri fil-Figura 4-6.

Il-pinout rakkomandat għall-konnettur ta '10-pin ARM Cortex Debug jidher fil-Figura 4-2.

Konnessjoni diretta ma 'header standard ta' 10-pin 50-mil

Uża l-kejbil ċatt ta '50-mil 10-pin (inkluż f'xi kits) biex tikkonnettja direttament ma' bord li jappoġġja dan it-tip ta 'header. Uża l-port tal-konnettur AVR fuq l-Atmel-ICE għal headers bil-pinout AVR, u l-port tal-konnettur SAM għal headers li jikkonformaw mal-pinout header ARM Cortex Debug.

Il-pinouts għaż-żewġ portijiet tal-konnettur b'10 pins huma murija hawn taħt.

Konnessjoni ma 'header standard ta' 10-pin 100-mil

Uża adapter standard ta '50-mil għal 100-mil biex tikkonnettja ma' headers ta '100-mil. Bord ta 'l-adapter (inkluż f'xi kits) jista' jintuża għal dan il-għan, jew alternattivament il-JTAGL-adapter ICE3 jista 'jintuża għal miri AVR.

![]() Importanti:

Importanti:

Il-JTAGL-adapter ICE3 100-mil ma jistax jintuża mal-port tal-konnettur SAM, peress li l-pinnijiet 2 u 10 (AVR GND) fuq l-adapter huma konnessi.

Konnessjoni ma' header personalizzat ta' 100-mil

Jekk il-bord fil-mira tiegħek m'għandux J 10-pin konformiTAG header f'50- jew 100-mil, tista 'mappa għal pinout tad-dwana billi tuża l-kejbil "mini-klamari" ta' 10 pin (inkluż f'xi kits), li jagħti aċċess għal għaxar sokits individwali ta '100-mil.

Konnessjoni ma 'header ta' 20 pin 100-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' miri b'header ta '20-pin 100-mil.

Tabella 4-10. Atmel-ICE JTAG Deskrizzjoni tal-pin

| Isem | AVR pin tal-port | SAM pin tal-port | Deskrizzjoni |

| TCK | 1 | 4 | Test Clock (sinjal tal-arloġġ mill-Atmel-ICE fil-mezz fil-mira). |

| TMS | 5 | 2 | Agħżel il-Modalità tat-Test (sinjal ta 'kontroll mill-Atmel-ICE fil-mezz fil-mira). |

| TDI | 9 | 8 | Test Data In (data trażmessa mill-Atmel-ICE fl-apparat fil-mira). |

| TDO | 3 | 6 | Test Data Out (dejta trażmessa mill-apparat fil-mira fl-Atmel-ICE). |

| nTRST | 8 | – | Test Reset (mhux obbligatorju, biss fuq xi apparati AVR). Użat biex tirrisettja l-JTAG Kontrollur TAP. |

| nSRST | 6 | 10 | Irrisettja (mhux obbligatorju). Użat biex reset l-apparat fil-mira. Il-konnessjoni ta 'dan il-pin hija rakkomandata peress li tippermetti lill-Atmel-ICE li jżomm l-apparat fil-mira fi stat ta' reset, li jista 'jkun essenzjali għad-debugging f'ċerti xenarji. |

| VTG | 4 | 1 | Mira voltage referenza. L-Atmel-ICE samples il-mira voltage fuq dan il-pin sabiex tissaħħaħ il-konvertituri tal-livell b'mod korrett. L-Atmel-ICE jiġbed inqas minn 3mA minn dan il-pin fil-modalità debugWIRE u inqas minn 1mA f'modi oħra. |

| GND | 2, 10 | 3, 5, 9 | Art. Kollha għandhom ikunu konnessi biex jiġi żgurat li l-Atmel-ICE u l-apparat fil-mira jaqsmu l-istess referenza tal-art. |

4.4.3.Interface Fiżika SPI

L-Ipprogrammar fis-Sistema juża l-SPI intern (Serial Peripheral Interface) ta 'Atmel AVR fil-mira biex tniżżel il-kodiċi fil-memorji flash u EEPROM. Mhuwiex interface debugging. Meta tfassal PCB ta 'applikazzjoni, li jinkludi AVR bl-interface SPI, għandu jintuża l-pinout kif muri fil-figura hawn taħt.

Figura 4-10. SPI Header Pinout 4.4.4. Konnessjoni ma 'SPI Target

4.4.4. Konnessjoni ma 'SPI Target

Il-pinout rakkomandat għall-konnettur SPI 6-pin jidher fil-Figura 4-10.

Konnessjoni ma 'header SPI 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header SPI standard ta' 100-mil.

Konnessjoni ma 'header SPI 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header SPI standard ta '50-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Sitt konnessjonijiet huma meħtieġa, kif deskritt fit-tabella hawn taħt.

![]() Importanti:

Importanti:

L-interface SPI huwa diżattivat b'mod effettiv meta d-debugWIRE enable fuse (DWEN) huwa pprogrammat, anki jekk il-fjus SPIEN huwa pprogrammat ukoll. Biex terġa 'tippermetti l-interface SPI, il-kmand 'disable debugWIRE' għandu jinħareġ waqt li jkun f'sessjoni ta' debugWIRE. Id-diżattivazzjoni ta' debugWIRE b'dan il-mod teħtieġ li l-fjus SPIEN ikun diġà pprogrammat. Jekk Atmel Studio jonqos milli jiskonnettja debugWIRE, huwa probabbli minħabba li l-fjus SPIEN MHUX ipprogrammat. Jekk dan huwa l-każ, huwa meħtieġ li tuża high-voltage interface ta 'programmazzjoni biex tipprogramma l-fjus SPIEN.

![]() Informazzjoni:

Informazzjoni:

L-interface SPI spiss tissejjaħ "ISP", peress li kienet l-ewwel interface ta 'Programmazzjoni tas-Sistema fuq il-prodotti Atmel AVR. Interfaces oħra issa huma disponibbli għall-Ipprogrammar fis-Sistema.

Tabella 4-11. Atmel-ICE SPI Pin Mapping

| Pinnijiet tal-port Atmel-ICE AVR | Labar tal-mira | Pin mini-klamari |

SPI pinout |

| Pin 1 (TCK) | SCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | MISO | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | /RESET | 6 | 5 |

| Pin 7 (mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | MOSI | 9 | 4 |

| Pin 10 (GND) | 0 |

4.4.5. PDI

Il-Programm and Debug Interface (PDI) huwa interface proprjetarju ta' Atmel għall-ipprogrammar estern u debugging fuq iċ-ċippa ta' apparat. PDI Physical huwa interface b'2 pin li jipprovdi komunikazzjoni sinkronika bi-direzzjonali half-duplex mal-apparat fil-mira.

Meta tfassal PCB ta 'applikazzjoni, li jinkludi Atmel AVR bl-interface PDI, għandu jintuża l-pinout muri fil-figura hawn taħt. Wieħed mill-adapters 6-pin ipprovdut mal-kit Atmel-ICE jista 'mbagħad jintuża biex jgħaqqad is-sonda Atmel-ICE mal-PCB tal-applikazzjoni.

Figura 4-11. PDI Header Pinout 4.4.6.Konnessjoni ma' Mira PDI

4.4.6.Konnessjoni ma' Mira PDI

Il-pinout rakkomandat għall-konnettur PDI b'6 pins jidher fil-Figura 4-11.

Konnessjoni ma 'header PDI ta' 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header PDI standard ta' 100-mil.

Konnessjoni ma 'header PDI ta' 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header PDI standard ta '50-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Huma meħtieġa erba' konnessjonijiet, kif deskritt fit-tabella hawn taħt.

![]() Importanti:

Importanti:

Il-pinout meħtieġ huwa differenti mill-JTAGICE mkII JTAG sonda, fejn PDI_DATA hija konnessa mal-pin 9. L-Atmel-ICE huwa kompatibbli mal-pinout użat mill-Atmel-ICE, JTAGICE3, AVR ONE!, u AVR Dragon™ prodotti.

Tabella 4-12. Atmel-ICE PDI Pin Mapping

|

Pin tal-port Atmel-ICE AVR |

Labar tal-mira | Pin mini-klamari |

Atmel STK600 PDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | PDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.7. Interface Fiżiku UPDI

Il-Programm Unifikat u l-Interface ta 'Debug (UPDI) huwa interface proprjetarju ta' Atmel għall-ipprogrammar estern u debugging fuq iċ-ċippa ta 'apparat. Huwa suċċessur għall-interface fiżika PDI 2-wire, li tinsab fuq l-apparati AVR XMEGA kollha. UPDI huwa interface b'wajer wieħed li jipprovdi komunikazzjoni asinkronika bi-direzzjonali half-duplex mal-apparat fil-mira għal skopijiet ta 'programmazzjoni u debugging.

Meta tfassal PCB ta 'applikazzjoni, li jinkludi Atmel AVR bl-interface UPDI, għandu jintuża l-pinout muri hawn taħt. Wieħed mill-adapters 6-pin ipprovdut mal-kit Atmel-ICE jista 'mbagħad jintuża biex jgħaqqad is-sonda Atmel-ICE mal-PCB tal-applikazzjoni.

Figura 4-12. UPDI Header Pinout 4.4.7.1 UPDI u /RESET

4.4.7.1 UPDI u /RESET

L-interface ta 'wajer wieħed UPDI jista' jkun pin iddedikat jew pin kondiviż, skont l-apparat AVR fil-mira. Ikkonsulta l-iskeda tad-dejta tal-apparat għal aktar informazzjoni.

Meta l-interface UPDI tkun fuq pin kondiviż, il-pin jista 'jiġi kkonfigurat biex ikun jew UPDI, / RESET, jew GPIO billi jiġu stabbiliti l-fjusis RSTPINCFG[1:0].

Il-fjusis RSTPINCFG[1:0] għandhom il-konfigurazzjonijiet li ġejjin, kif deskritt fid-datasheet. L-implikazzjonijiet prattiċi ta' kull għażla huma mogħtija hawn.

Tabella 4-13. RSTPINCFG[1:0] Konfigurazzjoni tal-Fjus

| RSTPINCFG[1:0] | Konfigurazzjoni |

Użu |

| 00 | GPIO | Pin I/O għal skopijiet ġenerali. Sabiex ikollok aċċess għall-UPDI, irid jiġi applikat polz ta '12V għal dan il-pin. L-ebda sors ta’ reset estern mhu disponibbli. |

| 01 | UPDI | Programmazzjoni dedikata u pin debugging. L-ebda sors ta’ reset estern mhu disponibbli. |

| 10 | Irrisettja | Irrisettja l-input tas-sinjal. Sabiex ikollok aċċess għall-UPDI, irid jiġi applikat polz ta '12V għal dan il-pin. |

| 11 | Riżervat | NA |

Nota: Apparati AVR anzjani għandhom interface ta 'programmazzjoni, magħrufa bħala "High-Voltage Programming” (jeżistu kemm varjanti serjali kif ukoll paralleli.) B'mod ġenerali din l-interface teħtieġ li tiġi applikata 12V fuq il-pin /RESET għat-tul tas-sessjoni ta 'programmar. L-interface UPDI hija interface kompletament differenti. Il-pin UPDI huwa primarjament pin ta 'programmazzjoni u debugging, li jista' jiġi mgħaqqad biex ikollu funzjoni alternattiva (/RESET jew GPIO). Jekk tintgħażel il-funzjoni alternattiva allura huwa meħtieġ polz ta '12V fuq dak il-pin sabiex terġa' tiġi attivata l-funzjonalità UPDI.

Nota: Jekk disinn jeħtieġ il-kondiviżjoni tas-sinjal UPDI minħabba restrizzjonijiet tal-brilli, għandhom jittieħdu passi sabiex jiġi żgurat li l-apparat jista 'jiġi pprogrammat. Biex jiġi żgurat li s-sinjal UPDI jista 'jaħdem b'mod korrett, kif ukoll biex tiġi evitata ħsara lill-komponenti esterni mill-polz ta' 12V, huwa rakkomandat li skonnettja kwalunkwe komponenti fuq dan il-pin meta tipprova tiddibaggja jew tipprogramma l-apparat. Dan jista 'jsir bl-użu ta' resistor ta '0Ω, li huwa mmuntat awtomatikament u mneħħi jew mibdul b'header tal-pin waqt id-debugging. Din il-konfigurazzjoni effettivament tfisser li l-ipprogrammar għandu jsir qabel l-immuntar tal-apparat.

![]() Importanti: L-Atmel-ICE ma jappoġġjax 12V fuq il-linja UPDI. Fi kliem ieħor, jekk il-pin UPDI ġie kkonfigurat bħala GPIO jew RESET l-Atmel-ICE ma jkunx jista 'jippermetti l-interface UPDI.

Importanti: L-Atmel-ICE ma jappoġġjax 12V fuq il-linja UPDI. Fi kliem ieħor, jekk il-pin UPDI ġie kkonfigurat bħala GPIO jew RESET l-Atmel-ICE ma jkunx jista 'jippermetti l-interface UPDI.

4.4.8.Konnessjoni ma' Mira UPDI

Il-pinout rakkomandat għall-konnettur UPDI b'6 pins jidher fil-Figura 4-12.

Konnessjoni ma 'header UPDI ta' 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header UPDI standard ta' 100-mil.

Konnessjoni ma 'header UPDI ta' 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header UPDI standard ta '50-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Huma meħtieġa tliet konnessjonijiet, kif deskritt fit-tabella hawn taħt.

Tabella 4-14. Atmel-ICE UPDI Pin Mapping

| Pin tal-port Atmel-ICE AVR | Labar tal-mira | Pin mini-klamari |

Atmel STK600 UPDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | [/RESET sens] | 6 | 5 |

| Pin 7 (Mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.9 TPI Interface Fiżiku

TPI huwa interface għall-ipprogrammar biss għal xi apparati AVR ATtiny. Mhuwiex interface ta 'debugging, u dawn l-apparati m'għandhomx kapaċità OCD. Meta tfassal PCB ta 'applikazzjoni li jinkludi AVR bl-interface TPI, għandu jintuża l-pinout muri fil-figura hawn taħt.

Figura 4-13. TPI Header Pinout 4.4.10.Konnessjoni ma' Mira TPI

4.4.10.Konnessjoni ma' Mira TPI

Il-pinout rakkomandat għall-konnettur TPI 6-pin jidher fil-Figura 4-13.

Konnessjoni ma 'header TPI 6-pin 100-mil

Uża l-vit 6-pin 100-mil fuq il-kejbil ċatt (inkluż f'xi kits) biex tikkonnettja ma 'header TPI standard ta' 100-mil.

Konnessjoni ma 'header TPI 6-pin 50-mil

Uża l-bord ta 'l-adapter (inkluż f'xi kits) biex tikkonnettja ma' header TPI standard ta '50-mil.

Konnessjoni ma' header personalizzat ta' 100-mil

Il-kejbil mini-klamari 10-pin għandu jintuża biex jgħaqqad bejn il-port tal-konnettur Atmel-ICE AVR u l-bord tal-mira. Sitt konnessjonijiet huma meħtieġa, kif deskritt fit-tabella hawn taħt.

Tabella 4-15. Atmel-ICE TPI Pin Mapping

| Pinnijiet tal-port Atmel-ICE AVR | Labar tal-mira | Pin mini-klamari |

TPI pinout |

| Pin 1 (TCK) | ARLOĠĠ | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DEJTA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | /RESET | 6 | 5 |

| Pin 7 (mhux konness) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.11. Debugging Avvanzat (AVR JTAG apparati /debugWIRE)

I/O Periferali

Ħafna mill-periferali I/O se jkomplu jaħdmu minkejja li l-eżekuzzjoni tal-programm titwaqqaf minn breakpoint. Eżample: Jekk jintlaħaq breakpoint waqt trażmissjoni UART, it-trażmissjoni titlesta u l-bits korrispondenti jiġu stabbiliti. Il-bandiera TXC (trażmissjoni kompluta) se tkun issettjata u tkun disponibbli fuq il-pass uniku li jmiss tal-kodiċi minkejja li normalment jiġri aktar tard f'apparat attwali.

Il-moduli I/O kollha se jkomplu jaħdmu fil-modalità waqfien biż-żewġ eċċezzjonijiet li ġejjin:

- Timer/Counters (konfigurabbli bl-użu tas-software front-end)

- Watchdog Timer (dejjem imwaqqaf biex jipprevjeni resets waqt id-debugging)

Aċċess Uniku Stepping I/O

Peress li l-I/O tkompli taħdem fil-modalità waqfien, għandha tingħata attenzjoni biex jiġu evitati ċerti kwistjonijiet ta 'ħin. Per example, il-kodiċi:

Meta tħaddem dan il-kodiċi b'mod normali, ir-reġistru TEMP ma jaqrax lura 0xAA minħabba li d-data ma tkunx għadha tkun imqabbda fiżikament mal-pin sa meta tkun sampimmexxija mill-operazzjoni IN. Istruzzjoni NOP trid titqiegħed bejn l-istruzzjoni OUT u IN biex jiġi żgurat li l-valur korrett ikun preżenti fir-reġistru PIN.

Madankollu, meta wieħed iżżid din il-funzjoni permezz tal-OCD, dan il-kodiċi dejjem jagħti 0xAA fir-reġistru tal-PIN peress li l-I/O qed jaħdem b'veloċità sħiħa anke meta l-qalba titwaqqaf waqt it-titjib wieħed.

Pass wieħed u ħin

Ċerti reġistri jeħtieġ li jinqraw jew jinkitbu f'numru partikolari ta' ċikli wara li jkun attivat sinjal ta' kontroll. Peress li l-arloġġ I/O u l-periferali jkomplu jaħdmu b'veloċità sħiħa fil-modalità waqfien, pass wieħed minn kodiċi bħal dan mhux se jissodisfa r-rekwiżiti tal-ħin. Bejn żewġ passi waħdieni, l-arloġġ I/O jista’ jkun mexxa miljuni ta’ ċikli. Biex taqra jew tikteb b'suċċess reġistri b'rekwiżiti ta 'ħin bħal dawn, is-sekwenza kollha tal-qari jew tal-kitba għandha titwettaq bħala operazzjoni atomika li tħaddem l-apparat b'veloċità sħiħa. Dan jista 'jsir billi tuża makro jew sejħa ta' funzjoni biex tesegwixxi l-kodiċi, jew tuża l-funzjoni run-to-cursor fl-ambjent tad-debugging

Aċċess reġistri 16-bit

Il-periferali Atmel AVR tipikament fihom diversi reġistri ta '16-bit li jistgħu jiġu aċċessati permezz tal-bus data 8-bit (eż.: TCNTn ta' tajmer ta '16-bit). Ir-reġistru ta' 16-il bit irid ikun aċċessat b'byte bl-użu ta' żewġ operazzjonijiet ta' qari jew kitba. Tkissir fin-nofs ta 'aċċess 16-bit jew pass wieħed minn din is-sitwazzjoni jista' jirriżulta f'valuri żbaljati.

Aċċess ristrett għar-reġistru I/O

Ċerti reġistri ma jistgħux jinqraw mingħajr ma jiġi affettwat il-kontenut tagħhom. Dawn ir-reġistri jinkludu dawk li fihom bnadar li jitneħħew bil-qari, jew reġistri ta' data buffered (eż.: UDR). Il-front-end tas-softwer se jipprevjeni l-qari ta 'dawn ir-reġistri meta jkun fil-modalità waqfien biex jippreserva n-natura mhux intrużiva maħsuba tad-debugging OCD. Barra minn hekk, xi reġistri ma jistgħux jinkitbu mingħajr periklu mingħajr ma jseħħu effetti sekondarji – dawn ir-reġistri jinqraw biss. Per example:

- Reġistri tal-bandiera, fejn bandiera titneħħa billi tikteb '1' ma' kwalunkwe Dawn ir-reġistri huma ta' qari biss.

- Ir-reġistri UDR u SPDR ma jistgħux jinqraw mingħajr ma jaffettwaw l-istat tal-modulu. Dawn ir-reġistri mhumiex

4.4.12. Konsiderazzjonijiet Speċjali megaAVR