Programmatori ICE Debugger

Programmatori ICE Debugger

Guida d'usu Prugrammatori è Debuggers

Prugrammatori è Debuggers

Atmel-ICE

GUIDA D'USU

U Debugger Atmel-ICE

Atmel-ICE hè un putente strumentu di sviluppu per debugging è prugrammazione di microcontrollers Atmel ®SAM è Atmel AVR basatu in ARM® Cortex®-M cù capacità ® On-Chip Debug.

Supporta:

- Programmazione è debugging in chip di tutti i microcontrollers Atmel AVR 32-bit in i dui JTAG e interfacce aWire

- Programmazione è debugging in chip di tutti i dispositi di a famiglia Atmel AVR XMEGA® in i dui JTAG e interfacce PDI a 2 fili

- Programmazione (JTAG, SPI, UPDI) è debugging di tutti i microcontrollers Atmel AVR 8-bit cù supportu OCD in JTAG, interfacce debugWIRE o UPDI

- Programmazione è debugging di tutti i microcontrollers Atmel SAM ARM Cortex-M basatu in SWD è JTAG interfacce

- Programmazione (TPI) di tutti i microcontrollers Atmel tinyAVR® 8-bit cù supportu per questa interfaccia

Cunsultate a lista di i dispositi supportati in a Guida d'Usuariu di Atmel Studio per una lista completa di i dispositi è interfacce supportati da questa versione di firmware.

Introduzione

1.1. Introduzione à l'Atmel-ICE

Atmel-ICE hè un putente strumentu di sviluppu per debugging è prugrammazione ARM Cortex-M basatu Atmel SAM è Atmel AVR microcontrollers cù capacità On-Chip Debug.

Supporta:

- Programmazione è debugging in chip di tutti i microcontrollers Atmel AVR UC3 nantu à i dui JTAG e interfacce aWire

- Programmazione è debugging in chip di tutti i dispositi di a famiglia AVR XMEGA in i dui JTAG e interfacce PDI a 2 fili

- Programmazione (JTAG è SPI) è debugging di tutti i microcontrollers AVR 8-bit cù supportu OCD sia in JTAG o interfacce debugWIRE

- Programmazione è debugging di tutti i microcontrollers Atmel SAM ARM Cortex-M basatu in SWD è JTAG interfacce

- Programmazione (TPI) di tutti i microcontrollers Atmel tinyAVR 8-bit cù supportu per questa interfaccia

1.2. Funzioni Atmel-ICE

- Completamente cumpatibile cù Atmel Studio

- Supporta a prugrammazione è a debugging di tutti i microcontrollers Atmel AVR UC3 32-bit

- Supporta a prugrammazione è a debugging di tutti i dispositi AVR XMEGA 8-bit

- Supporta a prugrammazione è u debugging di tutti i dispositi Atmel megaAVR® è tinyAVR 8-bit cù OCD

- Supporta a prugrammazione è u debugging di tutti i microcontrollers basati SAM ARM Cortex-M

- Volu operativu di destinazionetage gamma di 1.62V à 5.5V

- Aspira menu di 3mA da VTref di destinazione quandu si usa l'interfaccia debugWIRE è menu di 1mA per tutte l'altri interfacce

- Supporta JTAG frequenze di clock da 32kHz à 7.5MHz

- Supporta frequenze di clock PDI da 32kHz à 7.5MHz

- Supporta i baud rates debugWIRE da 4kbit/s à 0.5Mbit/s

- Supporta baud rates aWire da 7.5 kbit/s à 7 Mbit/s

- Supporta frequenze di clock SPI da 8kHz à 5MHz

- Supporta baud rates UPDI finu à 750 kbit/s

- Supporta frequenze di clock SWD da 32kHz à 10MHz

- Interfaccia host USB 2.0 ad alta velocità

- Cattura di traccia seriale ITM finu à 3MB/s

- Supporta l'interfaccia DGI SPI è USART quandu ùn debugging o prugrammazione

- Supporta 10-pin 50-mil JTAG cunnessu cù i pinouts AVR è Cortex. U cable di sonda standard supporta AVR 6-pin ISP/PDI/TPI 100-mil headers è ancu 10-pin 50-mil. Un adattatore hè dispunibule per supportà intestazioni 6-pin 50-mil, 10-pin 100-mil, è 20-pin 100-mil headers. Diversi opzioni di kit sò dispunibili cù diversi cablaggi è adattatori.

1.3. Requisiti di u sistema

L'unità Atmel-ICE richiede chì un ambiente di debugging front-end Atmel Studio versione 6.2 o più tardi hè stallatu in u vostru urdinatore.

L'Atmel-ICE deve esse cunnessu à l'urdinatore òspite cù u cable USB furnitu, o un cable Micro-USB certificatu.

Cumincià cù l'Atmel-ICE

2.1. Cuntinutu cumpletu di u kit

U kit cumpletu Atmel-ICE cuntene questi articuli:

- Unità Atmel-ICE

- Cavu USB (1.8 m, alta velocità, Micro-B)

- Scheda adattatore contenente adattatori 50-mil AVR, 100-mil AVR/SAM è 100-mil 20-pin SAM

- Cavo piatto IDC con connettore 10-pin 50-mil è connettore 6-pin 100-mil

- Cavo mini squid 50-mil 10-pin cù 10 prese x 100-mil

Figura 2-1. Atmel-ICE cuntenuti di u kit cumpletu 2.2. Cuntenutu di u kit di basa

2.2. Cuntenutu di u kit di basa

U kit di basi Atmel-ICE cuntene questi articuli:

- Unità Atmel-ICE

- Cavu USB (1.8 m, alta velocità, Micro-B)

- Cavo piatto IDC con connettore 10-pin 50-mil è connettore 6-pin 100-mil

Figura 2-2. Atmel-ICE Basic Kit Contenutu 2.3. Contenutu di u Kit PCBA

2.3. Contenutu di u Kit PCBA

U kit Atmel-ICE PCBA cuntene questi articuli:

- Unità Atmel-ICE senza incapsulazione plastica

Figura 2-3. Atmel-ICE PCBA Kit Contenutu 2.4. Kit di ricambi

2.4. Kit di ricambi

I seguenti kit di pezzi di ricambio sò dispunibili:

- Kit adattatore

- Kit di cable

Figura 2-4. Cuntenutu di u Kit Adattatore Atmel-ICE 2.5. Kit Overview

2.5. Kit Overview

L'opzioni di kit Atmel-ICE sò mostrate schematicamente quì:

Figura 2-6. Atmel-ICE Kit Overview 2.6. Assembla l'Atmel-ICE

2.6. Assembla l'Atmel-ICE

L'unità Atmel-ICE hè spedita senza cables attaccati. Dui opzioni di cable sò furnite in u kit cumpletu:

- Cavo piatto IDC 50-mil 10-pin cù ISP 6-pin è connettori 10-pin

- Cavo mini-squid 50-mil 10-pin cù 10 prese x 100-mil

Figura 2-7. Cavi Atmel-ICE Per a maiò parte di i scopi, u cable flat IDC 50-mil 10-pin pò esse usatu, cunnetta o nativamente à i so connettori 10-pin o 6-pin, o cunnessu via l'adattatore. Trè adattatori sò furniti nantu à una piccula PCBA. I seguenti adattatori sò inclusi:

Per a maiò parte di i scopi, u cable flat IDC 50-mil 10-pin pò esse usatu, cunnetta o nativamente à i so connettori 10-pin o 6-pin, o cunnessu via l'adattatore. Trè adattatori sò furniti nantu à una piccula PCBA. I seguenti adattatori sò inclusi:

- 100-mil 10-pin JTAG/ adattatore SWD

- 100-mil 20-pin SAM JTAG/ adattatore SWD

- 50-mil 6-pin SPI/debugWIRE/PDI/aWire adattatore

Figura 2-8. Adattatori Atmel-ICE Nota:

Nota:

A 50-mil JTAG L'adattatore ùn hè micca statu furnitu - questu hè perchè u cable IDC 50-mil 10-pin pò esse usatu per cunnette direttamente à un J 50-mil.TAG intestazione. Per u numeru di parte di u cumpunente utilizatu per u connettore 50-mil 10-pin, vede Atmel-ICE Target Connectors Part Numbers.

L'intestazione ISP / PDI 6-pin hè inclusa cum'è parte di u cable IDC 10-pin. Questa terminazione pò esse tagliata s'ellu ùn hè micca necessariu.

Per assemblà u vostru Atmel-ICE in a so cunfigurazione predeterminata, cunnette u cable IDC 10-pin 50-mil à l'unità cum'è mostra quì sottu. Assicuratevi di orientà u cable in modu chì u filu rossu (pin 1) nantu à u cable aligned with the triangular indicator on the blue belt of the enclosure. U cable deve esse cunnessu da l'unità. Assicuratevi di cunnette à u portu chì currisponde à u pinout di u vostru scopu - AVR o SAM.

Figura 2-9. Cunnessione per cable Atmel-ICE Figura 2-10. Cunnessione Atmel-ICE AVR Probe

Figura 2-10. Cunnessione Atmel-ICE AVR Probe

Figura 2-11. Cunnessione Atmel-ICE SAM Probe

Figura 2-11. Cunnessione Atmel-ICE SAM Probe 2.7. Apertura di l'Atmel-ICE

2.7. Apertura di l'Atmel-ICE

Nota:

Per u funziunamentu normale, l'unità Atmel-ICE ùn deve esse apertu. L'apertura di l'unità hè fatta à u vostru propiu risicu.

Precauzioni anti-statica deve esse pigliatu.

L'armadiu Atmel-ICE hè custituitu da trè cumpunenti di plastica separati - coperchio superiore, coperchio inferiore è cinturione blu - chì sò chjappi inseme durante l'assemblea. Per apre l'unità, simpricimenti inserisci un grande cacciavite pianu in l'aperture in u cinturione blu, applicà una pressione interna è torce delicatamente. Repetite u prucessu nantu à l'altri buchi di snapper, è a tappa superiore si sparghjerà.

Figura 2-12. Apertura di l'Atmel-ICE (1)

Figura 2-13. Apertura di l'Atmel-ICE (2)

Figura 2-13. Apertura di l'Atmel-ICE (2)

Figura 2-14. Apertura di l'Atmel-ICE (3)

Figura 2-14. Apertura di l'Atmel-ICE (3) Per chjude di novu l'unità, simpricimenti allineate i coperchi superiori è inferiori currettamente, è appughjà fermamente inseme.

Per chjude di novu l'unità, simpricimenti allineate i coperchi superiori è inferiori currettamente, è appughjà fermamente inseme.

2.8. Alimentazione di l'Atmel-ICE

L'Atmel-ICE hè alimentatu da u bus USB voltage. Hè bisognu di menu di 100mA per operare, è pò dunque esse alimentatu da un hub USB. U LED di putenza s'illuminarà quandu l'unità hè cunnessa. Quandu ùn hè micca cunnessu in una sessione di prugrammazione attiva o di debugging, l'unità entrerà in modu di cunsumu di bassa energia per priservà a bateria di u vostru urdinatore. L'Atmel-ICE ùn pò micca esse spente - deve esse scollegatu quandu ùn hè micca in usu.

2.9. Cunnessu à l'Ordinatore Host

L'Atmel-ICE cumunica principarmenti utilizendu una interfaccia HID standard, è ùn hà micca bisognu di un driver speciale in l'urdinatore host. Per utilizà a funziunalità avanzata di Data Gateway di l'Atmel-ICE, assicuratevi di installà u driver USB in u computer host. Questu hè fattu automaticamente quandu installate u software front-end furnitu gratuitamente da Atmel. Vede www.atmel.com per più infurmazione o per scaricà l'ultimu software front-end.

L'Atmel-ICE deve esse cunnessu à un portu USB dispunibule nantu à l'urdinatore òspite usendu u cable USB furnitu, o un micro cable certificatu USB adattatu. L'Atmel-ICE cuntene un controller USB 2.0 cumpletu, è pò operà sia in modalità full-speed è high-speed. Per u megliu risultati, cunnette l'Atmel-ICE direttamente à un hub d'alta velocità USB 2.0 cumpatibile nantu à l'urdinatore host usendu u cable furnitu.

2.10. Installazione di u Driver USB

2.10.1. Windows

Quandu si stallanu l'Atmel-ICE in un computer chì esegue Microsoft® Windows®, u driver USB hè caricatu quandu l'Atmel-ICE hè prima cunnessu.

Nota:

Assicuratevi di stallà i pacchetti di software front-end prima di cunnette l'unità per a prima volta.

Una volta installatu bè, l'Atmel-ICE appariscerà in u gestore di u dispositivu cum'è "Dispositivu d'interfaccia umana".

Cunnettendu l'Atmel-ICE

3.1. Cunnessione à i Dispositivi Target AVR è SAM

L'Atmel-ICE hè dotatu di dui 50-mil 10-pin JTAG connettori. I dui connettori sò direttamente cunnessi elettricamente, ma cunforme à dui pinouts differenti; l'AVR JTAG header è l'intestazione ARM Cortex Debug. U connettore deve esse sceltu basatu annantu à u pinout di u pianu di destinazione, è micca u tipu MCU di destinazione - per esempiuampun dispositivu SAM muntatu in una pila AVR STK® 600 deve aduprà l'intestazione AVR.

Diversi cablaggi è adattatori sò dispunibili in i diversi kit Atmel-ICE. Un sopraview di opzioni di cunnessione hè mostratu.

Figura 3-1. Opzioni di cunnessione Atmel-ICE U filu rossu marca u pin 1 di u connettore 10-pin 50-mil. Pin 1 di u connettore 6-pin 100-mil hè situatu à a diritta di a chjave quandu u connector hè vistu da u cable. Pin 1 di ogni connettore nantu à l'adattatore hè marcatu cù un puntu biancu. A figura sottu mostra u pinout di u cable di debug. U connettore marcatu A si inserisce in u debugger mentre u latu B si inserisce in a tavula di destinazione.

U filu rossu marca u pin 1 di u connettore 10-pin 50-mil. Pin 1 di u connettore 6-pin 100-mil hè situatu à a diritta di a chjave quandu u connector hè vistu da u cable. Pin 1 di ogni connettore nantu à l'adattatore hè marcatu cù un puntu biancu. A figura sottu mostra u pinout di u cable di debug. U connettore marcatu A si inserisce in u debugger mentre u latu B si inserisce in a tavula di destinazione.

Figura 3-2. Debug Cable Pinout

3.2. Cunnessu à un JTAG Target

3.2. Cunnessu à un JTAG Target

L'Atmel-ICE hè dotatu di dui 50-mil 10-pin JTAG connettori. I dui connettori sò direttamente cunnessi elettricamente, ma cunforme à dui pinouts differenti; l'AVR JTAG header è l'intestazione ARM Cortex Debug. U connettore deve esse sceltu basatu annantu à u pinout di u pianu di destinazione, è micca u tipu MCU di destinazione - per esempiuampun dispositivu SAM muntatu in una pila AVR STK600 deve aduprà l'intestazione AVR.

Il pinout consigliato per l'AVR J a 10 pinTAG u connector hè mostratu in Figura 4-6. U pinout cunsigliatu per u connettore ARM Cortex Debug 10-pin hè mostratu in Figura 4-2.

Cunnessione diretta à un header standard 10-pin 50-mil

Aduprate u cable flat 50-mil 10-pin (cumpresu in certi kit) per cunnette direttamente à una scheda chì sustene stu tipu di header. Aduprate u portu di u connettore AVR nantu à l'Atmel-ICE per l'intestazione cù u pinout AVR, è u portu di u connettore SAM per l'intestazione cumpletu cù u pinout di l'intestazione ARM Cortex Debug.

I pinouts per i dui porti di cunnessu 10-pin sò mostrati quì sottu.

Cunnessione à un header standard 10-pin 100-mil

Aduprate un adattatore standard da 50-mil à 100-mil per cunnette à intestazioni 100-mil. Una scheda adattatore (inclusa in certi kit) pò esse usata per questu scopu, o in alternativa u JTAGL'adattatore ICE3 pò esse usatu per i miri AVR.

![]() Impurtante:

Impurtante:

U JTAGL'adattatore ICE3 100-mil ùn pò micca esse usatu cù u portu di u connector SAM, postu chì i pins 2 è 10 (AVR GND) nantu à l'adattatore sò cunnessi.

Cunnessione à un header persunalizatu 100-mil

Se a vostra tavola di destinazione ùn hà micca un 10-pin JTAG header in 50- o 100-mil, pudete mapà à un pinout persunalizatu utilizendu u cable "mini-squid" 10-pin (cumpresu in certi kit), chì dà accessu à dece sockets individuali 100-mil.

Cunnessione à un capu di 20 pin 100-milr

Aduprate a scheda di l'adattatore (inclusa in certi kits) per cunnette à i miri cù un capu di 20-pin 100-mil.

Table 3-1. Atmel-ICE JTAG Pin Description

| Nome | AVR pin portu | SAM pin portu | Descrizzione |

| TCK | 1 | 4 | Test Clock (signale di clock da l'Atmel-ICE in u dispusitivu di destinazione). |

| TMS | 5 | 2 | Test Mode Select (signale di cuntrollu da l'Atmel-ICE in u dispusitivu di destinazione). |

| TDI | 9 | 8 | Test Data In (dati trasmessi da l'Atmel-ICE à u dispusitivu di destinazione). |

| TDO | 3 | 6 | Test Data Out (dati trasmessi da u dispusitivu di destinazione à l'Atmel-ICE). |

| nTRST | 8 | – | Test Reset (opzionale, solu in certi dispositi AVR). Adupratu per resettà u JTAG Controller TAP. |

| nSRST | 6 | 10 | Reset (opcional). Adupratu per resetten u dispusitivu di destinazione. A cunnessione di stu pin hè cunsigliatu postu chì permette à l'Atmel-ICE di mantene u dispusitivu di destinazione in un statu di reset, chì pò esse essenziale per debugging in certi scenarii. |

| VTG | 4 | 1 | Target voltage riferenza. L'Atmel-ICE samples the target voltage nant'à stu pin in ordine per alimentà i cunvertitori di livellu currettamente. L'Atmel-ICE tira menu di 3mA da stu pin in modu debugWIRE è menu di 1mA in altri modi. |

| GND | 2, 10 | 3, 5, 9 | Terra. Tuttu deve esse cunnessu per assicurà chì l'Atmel-ICE è u dispusitivu di destinazione sparte u listessu riferimentu in terra. |

3.3. Cunnessione à un Target aWire

L'interfaccia aWire richiede una sola linea di dati in più di VCC è GND. Nant'à u scopu, sta linea hè a linea nRESET, anche se u debugger usa u JTAG A linea TDO cum'è a linea di dati.

A pinout consigliata per u connettore aWire 6-pin hè mostrata in Figura 4-8.

Cunnessione à un header aWire 6-pin 100-mil

Aduprate u toccu 6-pin 100-mil nantu à u cable flat (cumpresu in certi kit) per cunnette à un header standard 100-mil aWire.

Cunnessione à un header aWire 6-pin 50-mil

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu standard 50-mil aWire.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Trè cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

Table 3-2. Atmel-ICE aWire Pin Mapping

|

Pin di portu Atmel-ICE AVR |

Pin di destinazione | Mini-squid pin |

a Pinout di u filu |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.4. Cunnessione à un Target PDI

U pinout cunsigliatu per u cunnessu PDI 6-pin hè mostratu in Figura 4-11.

Cunnessione à un header PDI 6-pin 100-mil

Aduprate u 6-pin 100-mil tap nantu à u cable flat (cumpresu in certi kits) per cunnette à un standard 100-mil PDI header.

Cunnessione à un header PDI 6-pin 50-mil

Aduprate a scheda di l'adattatore (inclusa in certi kits) per cunnette à un header PDI standard 50-mil.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Quattru cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

![]() Impurtante:

Impurtante:

U pinout necessariu hè diversu da u JTAGICE mkII JTAG sonda, induve PDI_DATA hè cunnessu à u pin 9. L'Atmel-ICE hè cumpatibile cù u pinout utilizatu da l'Atmel-ICE, JTAGI prudutti ICE3, AVR ONE!, è AVR Dragon™.

Table 3-3. Atmel-ICE PDI Pin Mapping

| Pin di portu Atmel-ICE AVR | Pin di destinazione | Mini-squid pin |

a Pinout di u filu |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.4 Cunnessu à un Target PDI

U pinout cunsigliatu per u cunnessu PDI 6-pin hè mostratu in Figura 4-11.

Cunnessione à un header PDI 6-pin 100-mil

Aduprate u 6-pin 100-mil tap nantu à u cable flat (cumpresu in certi kits) per cunnette à un standard 100-mil PDI header.

Cunnessione à un header PDI 6-pin 50-mil

Aduprate a scheda di l'adattatore (inclusa in certi kits) per cunnette à un header PDI standard 50-mil.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Quattru cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

![]() Impurtante:

Impurtante:

U pinout necessariu hè diversu da u JTAGICE mkII JTAG sonda, induve PDI_DATA hè cunnessu à u pin 9. L'Atmel-ICE hè cumpatibile cù u pinout utilizatu da l'Atmel-ICE, JTAGICE3, AVR ONE!, è AVR Dragon™ prudutti.

Table 3-3. Atmel-ICE PDI Pin Mapping

| Pin di portu Atmel-ICE AVR | Pin di destinazione | Mini-squid pin | Pinout Atmel STK600 PDI |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | PDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.5 Cunnessu à un Target UPDI

U pinout cunsigliatu per u cunnessu UPDI 6-pin hè mostratu in Figura 4-12.

Cunnessione à un header UPDI 6-pin 100-mil

Aduprate u 6-pin 100-mil tap in u cable flat (cumpresu in certi kits) per cunnette à un standard 100-mil UPDI header.

Cunnessione à un header UPDI 6-pin 50-mil

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un header UPDI standard 50-mil.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Trè cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

Table 3-4. Atmel-ICE UPDI Pin Mapping

| Pin di portu Atmel-ICE AVR | Pin di destinazione | Mini-squid pin |

Pinout Atmel STK600 UPDI |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | [/RESET sensu] | 6 | 5 |

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.6 Cunnessu à un debugWIRE Target

U pinout cunsigliatu per u connettore 6-pin debugWIRE (SPI) hè mostratu in a Tabella 3-6.

Cunnessione à un header SPI 6-pin 100-mil

Aduprate u toccu 6-pin 100-mil nantu à u cable flat (cumpresu in certi kit) per cunnette à un header SPI standard 100-mil.

Cunnessione à un header SPI 6-pin 50-mil

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu standard SPI 50-mil.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Trè cunnessione sò necessarii, cum'è descrittu in a Tabella 3-5.

Ancu se l'interfaccia debugWIRE richiede solu una linea di signale (RESET), VCC è GND per operare currettamente, hè cunsigliatu per avè accessu à u cunnessu SPI cumpletu per chì l'interfaccia debugWIRE pò esse attivata è disattivata cù a prugrammazione SPI.

Quandu u fusible DWEN hè attivatu, l'interfaccia SPI hè annullata internamente per chì u modulu OCD hà u cuntrollu di u pin RESET. U debugWIRE OCD hè capaci di disattivà si temporaneamente (usendu u buttone nantu à a tabulazione di debugging in u dialogu di proprietà in Atmel Studio), cusì liberendu u cuntrollu di a linea RESET. L'interfaccia SPI hè allora dispunibule di novu (solu s'ellu hè programatu u fusible SPIEN), chì permette à u fusible DWEN di esse micca programatu cù l'interfaccia SPI. Se u putere hè cambiatu prima chì u fusible DWEN ùn hè micca programatu, u modulu debugWIRE ripiglià u cuntrollu di u pin RESET.

Nota:

Hè assai cunsigliatu di lascià solu chì Atmel Studio gestisce l'impostazione è l'eliminazione di u fusible DWEN.

Ùn hè micca pussibule di utilizà l'interfaccia debugWIRE se i lockbits nantu à u dispusitivu AVR di destinazione sò programati. Assicuratevi sempre chì i lockbits sò sbulicati prima di prugrammà u fusible DWEN è ùn mai stabilisce i lockbits mentre u fusible DWEN hè programatu. Se u fusibile di attivazione di debugWIRE (DWEN) è i lockbits sò impostati, si pò aduprà High Vol.tage Programmazione per fà una cancellazione di chip, è cusì sguassate i lockbits.

Quandu i lockbits sò sbulicati, l'interfaccia debugWIRE serà riattivata. L'interfaccia SPI hè solu capace di leghje i fusibili, leghje a firma è eseguisce una cancellazione di chip quandu u fusible DWEN ùn hè micca programatu.

Table 3-5. Atmel-ICE debugWIRE Pin Mapping

| Pin di portu Atmel-ICE AVR | Pin di destinazione |

Mini-squid pin |

| Pin 1 (TCK) | 1 | |

| Pin 2 (GND) | GND | 2 |

| Pin 3 (TDO) | 3 | |

| Pin 4 (VTG) | VTG | 4 |

| Pin 5 (TMS) | 5 | |

| Pin 6 (nSRST) | RESET | 6 |

| Pin 7 (micca cunnessu) | 7 | |

| Pin 8 (nTRST) | 8 | |

| Pin 9 (TDI) | 9 | |

| Pin 10 (GND) | 0 |

3.7 Cunnessu à un Target SPI

U pinout cunsigliatu per u connettore SPI 6-pin hè mostratu in Figura 4-10.

Cunnessione à un header SPI 6-pin 100-mil

Aduprate u toccu 6-pin 100-mil nantu à u cable flat (cumpresu in certi kit) per cunnette à un header SPI standard 100-mil.

Cunnessione à un header SPI 6-pin 50-mil

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu standard SPI 50-mil.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Sei cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

![]() Impurtante:

Impurtante:

L'interfaccia SPI hè disattivata in modu efficace quandu u fusible di debugWIRE enable (DWEN) hè programatu, ancu s'ellu SPIEN fuse hè ancu programatu. Per riattivare l'interfaccia SPI, u cumandimu "disable debugWIRE" deve esse emessu mentre in una sessione di debugWIRE. A disattivazione di debugWIRE in questu modu richiede chì u fusible SPIEN hè digià programatu. Se Atmel Studio ùn riesce à disattivà debugWIRE, hè prubabile perchè u fusible SPIEN ùn hè micca programatu. Se questu hè u casu, hè necessariu di utilizà un high-voltage interfaccia di prugrammazione per programà u fusible SPIEN.

![]() Info:

Info:

L'interfaccia SPI hè spessu referita cum'è "ISP", postu chì era a prima interfaccia In System Programming nantu à i prudutti Atmel AVR. Altre interfacce sò avà dispunibili per a Programmazione In u Sistema.

Table 3-6. Atmel-ICE SPI Pin Mapping

| Pin di portu Atmel-ICE AVR | Pin di destinazione | Mini-squid pin |

Pinout SPI |

| Pin 1 (TCK) | SCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | MISO | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | / RESET | 6 | 5 |

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | MOSI | 9 | 4 |

| Pin 10 (GND) | 0 |

3.8 Cunnessu à un Target TPI

U pinout cunsigliatu per u cunnessu TPI à 6 pin hè mostratu in Figura 4-13.

Cunnessione à un header 6-pin 100-mil TPI

Aduprate u 6-pin 100-mil tap in u cable flat (cumpresu in certi kits) per cunnette à un standard 100-mil TPI header.

Cunnessione à un header 6-pin 50-mil TPI

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu standard 50-mil TPI.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Sei cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

Table 3-7. Atmel-ICE TPI Pin Mapping

| Pin di portu Atmel-ICE AVR | Pin di destinazione | Mini-squid pin |

Pinout TPI |

| Pin 1 (TCK) | CLOCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 |

| Pin 6 (nSRST) | / RESET | 6 | 5 |

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.9 Cunnessu à un Target SWD

L'interfaccia ARM SWD hè un subset di u JTAG interfaccia, aduprendu i pin TCK è TMS, chì significa chì quandu si cunnette à un dispositivu SWD, u 10-pin JTAG Connettore pò esse usatu tecnicamente. L'ARM JTAG è AVR JTAG I connettori ùn sò, però, micca cumpatibili cù pin, cusì dipende da u layout di u pianu di destinazione in usu. Quandu si usa un STK600 o una scheda chì face usu di l'AVR JTAG pinout, u portu di cunnessu AVR nantu à l'Atmel-ICE deve esse usatu. Quandu si cunnetta à una scheda, chì face usu di l'ARM JTAG pinout, u portu di cunnessu SAM nantu à l'Atmel-ICE deve esse usatu.

U pinout cunsigliatu per u connettore Cortex Debug 10-pin hè mostratu in Figura 4-4.

Cunnessione à un capu Cortex 10-pin 50-mil

Aduprate u cable flat (cumpresu in certi kit) per cunnette à un standard Cortex header 50-mil.

Cunnessione à un 10-pin 100-mil Cortex-layout header

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu di 100-mil Cortex-pinout.

Cunnessione à un capu SAM 20-pin 100-mil

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu SAM 20-pin 100-mil.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR o SAM è a tavula di destinazione. Sei cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

Table 3-8. Atmel-ICE SWD Pin Mapping

| Nome | AVR pin portu | SAM pin portu | Descrizzione |

| SWDC LK | 1 | 4 | Serial Wire Debug Clock. |

| SWDIO | 5 | 2 | Serial Wire Debug Data Input / Output. |

| SWO | 3 | 6 | Output Serial Wire (opcional - micca implementatu in tutti i dispositi). |

| nSRST | 6 | 10 | Resettate. |

| VTG | 4 | 1 | Target voltage riferenza. |

| GND | 2, 10 | 3, 5, 9 | Terra. |

3.10 Cunnessu à l'interfaccia di Gateway di dati

L'Atmel-ICE sustene una Interfaccia Data Gateway limitata (DGI) quandu u debugging è a prugrammazione ùn hè micca in usu. A funziunalità hè identica à quella chì si trova nantu à i kit Atmel Xplained Pro alimentati da u dispusitivu Atmel EDBG.

L'interfaccia Data Gateway hè una interfaccia per streaming di dati da u dispusitivu di destinazione à un urdinatore. Questu hè intesu cum'è un aiutu in u debugging di l'applicazioni è ancu per a dimostrazione di e funziunalità in l'applicazione chì funziona nantu à u dispusitivu di destinazione.

DGI hè custituitu da parechji canali per u streaming di dati. L'Atmel-ICE supporta i seguenti modi:

- USART

- SPI

Table 3-9. Atmel-ICE DGI USART Pinout

|

portu AVR |

portu SAM | Pin DGI USART |

Descrizzione |

| 3 | 6 | TX | Trasmette pin da Atmel-ICE à u dispusitivu di destinazione |

| 4 | 1 | VTG | Target voltage (riferimentu voltage) |

| 8 | 7 | RX | Riceve pin da u dispusitivu di destinazione à Atmel-ICE |

| 9 | 8 | CLK | Clock USART |

| 2, 10 | 3, 5, 9 | GND | Terra |

Table 3-10. Atmel-ICE DGI SPI Pinout

|

portu AVR |

portu SAM | Pin DGI SPI |

Descrizzione |

| 1 | 4 | SCK | SPI clock |

| 3 | 6 | MISO | Maestru In Slave Out |

| 4 | 1 | VTG | Target voltage (riferimentu voltage) |

| 5 | 2 | nCS | Chip select active low |

| 9 | 8 | MOSI | Master Out Slave In |

| 2, 10 | 3, 5, 9 | GND | Terra |

![]() Impurtante: L'interfaccia SPI è USART ùn ponu esse usate simultaneamente.

Impurtante: L'interfaccia SPI è USART ùn ponu esse usate simultaneamente.

![]() Impurtante: DGI è prugrammazione o debugging ùn ponu micca esse usatu simultaneamente.

Impurtante: DGI è prugrammazione o debugging ùn ponu micca esse usatu simultaneamente.

Debugging in chip

4.1 Introduzione

Debugging in chip

Un modulu di debug in chip hè un sistema chì permette à un sviluppatore di monitorà è cuntrullà l'esekzione nantu à un dispositivu da una piattaforma di sviluppu esterna, di solitu attraversu un dispositivu cunnisciutu cum'è debugger o debug adapter.

Cù un sistema OCD, l'applicazione pò esse eseguita mentre mantene e caratteristiche elettriche è di timing esatte in u sistema di destinazione, purtendu esse capace di piantà l'esecuzione in cundizione o manualmente è inspeccionà u flussu di u prugramma è a memoria.

Modu Run

Quandu in u modu Run, l'esekzione di codice hè completamente indipendente da l'Atmel-ICE. L'Atmel-ICE monitorerà continuamente u dispusitivu di destinazione per vede s'ellu hè accadutu una cundizione di rottura. Quandu succede questu, u sistema OCD interrugarà u dispusitivu attraversu a so interfaccia di debug, chì permette à l'utilizatore view u statu internu di u dispusitivu.

Modu arrestatu

Quandu un breakpoint hè ghjuntu, l'esekzione di u prugramma hè arrestata, ma alcuni I / O ponu cuntinuà à eseguisce cum'è s'ellu ùn hè micca accadutu un breakpoint. Per esample, assume chì una trasmissione USART hè stata appena iniziata quandu un breakpoint hè righjuntu. In questu casu, l'USART cuntinueghja à eseguisce à a velocità massima cumpletendu a trasmissione, ancu s'è u core hè in modu fermatu.

Punti di rottura hardware

U modulu OCD di destinazione cuntene una quantità di comparatori di cuntatori di prugramma implementati in u hardware. Quandu u contatore di u prugramma currisponde à u valore guardatu in unu di i registri di comparatore, l'OCD entra in u modu fermatu. Siccomu i punti di rottura hardware necessitanu hardware dedicatu nantu à u modulu OCD, u numeru di punti di rottura dispunibuli dipende da a dimensione di u modulu OCD implementatu nantu à u mira. Di solitu un tali comparatore di hardware hè "riservatu" da u debugger per l'usu internu.

Punti di rottura di u software

Un breakpoint di software hè una struzzione BREAK posta in a memoria di u prugramma nantu à u dispusitivu di destinazione. Quandu sta struzzione hè caricata, l'esekzione di u prugramma si rompe è l'OCD entra in modu fermatu. Per cuntinuà l'esecuzione, un cumandamentu "iniziu" deve esse datu da l'OCD. Micca tutti i dispositi Atmel anu moduli OCD chì supportanu l'istruzzioni BREAK.

4.2 Dispositivi SAM cù JTAG/SWD

Tutti i dispositi SAM presentanu l'interfaccia SWD per a prugrammazione è a debugging. Inoltre, certi dispositi SAM presentanu un JTAG interfaccia cù funziunalità identica. Verificate a datasheet di u dispusitivu per l'interfacce supportate di quellu dispusitivu.

4.2.1.ARM CoreSight Components

I microcontrollers basati Atmel ARM Cortex-M implementanu cumpunenti OCD conformi à CoreSight. I funziunalità di sti cumpunenti pò varià da dispusitivu à dispusitivu. Per più infurmazione cunsultate a datasheet di u dispusitivu è a documentazione CoreSight furnita da ARM.

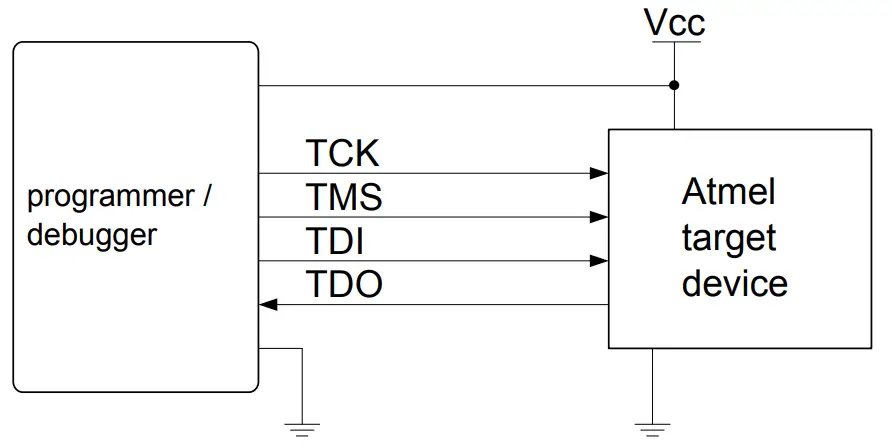

4.2.1. JTAG Interfaccia fisica

U JTAG L'interfaccia hè custituita da un controller di Test Access Port (TAP) à 4 fili chì hè conforme à l'IEEE® 1149.1 standard. U standard IEEE hè statu sviluppatu per furnisce un modu standard di l'industria per pruvà efficacemente a connettività di i circuiti (Boundary Scan). I dispositi Atmel AVR è SAM anu allargatu sta funziunalità per include un supportu cumpletu di Programmazione è Debugging On-chip.

Figura 4-1. JTAG Basi di l'interfaccia

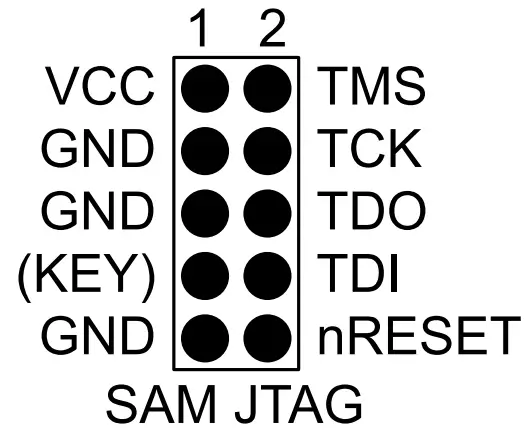

4.2.2.1 SAM JTAG Pinout (connettore di debug Cortex-M)

Quandu si cuncepisce un PCB d'applicazione chì include un SAM Atmel cù u JTAG interfaccia, hè cunsigliatu à aduprà u pinout comu mostra in a figura sottu. E duie varianti 100-mil è 50-mil di stu pinout sò supportati, secondu u cablaggio è l'adattatori inclusi cù u kit particulari.

Figura 4-2. SAM JTAG Pinout di l'intestazione

Table 4-1. SAM JTAG Pin Description

| Nome | Pin |

Descrizzione |

| TCK | 4 | Test Clock (signale di clock da l'Atmel-ICE in u dispusitivu di destinazione). |

| TMS | 2 | Test Mode Select (signale di cuntrollu da l'Atmel-ICE in u dispusitivu di destinazione). |

| TDI | 8 | Test Data In (dati trasmessi da l'Atmel-ICE à u dispusitivu di destinazione). |

| TDO | 6 | Test Data Out (dati trasmessi da u dispusitivu di destinazione à l'Atmel-ICE). |

| nRESET | 10 | Reset (opcional). Adupratu per resetten u dispusitivu di destinazione. A cunnessione di stu pin hè cunsigliatu postu chì permette à l'Atmel-ICE di mantene u dispusitivu di destinazione in un statu di reset, chì pò esse essenziale per debugging in certi scenarii. |

| VTG | 1 | Target voltage riferenza. L'Atmel-ICE samples the target voltage nant'à stu pin in ordine per alimentà i cunvertitori di livellu currettamente. L'Atmel-ICE tira menu di 1mA da stu pin in questu modu. |

| GND | 3, 5, 9 | Terra. Tuttu deve esse cunnessu per assicurà chì l'Atmel-ICE è u dispusitivu di destinazione sparte u listessu riferimentu in terra. |

| CHIAVE | 7 | Cunnessu internamente à u pin TRST in u connettore AVR. Cunsigliatu cum'è micca cunnessu. |

![]() Cunsigliu: Ricurdatevi di include un condensatore di disaccoppiamentu trà u pin 1 è GND.

Cunsigliu: Ricurdatevi di include un condensatore di disaccoppiamentu trà u pin 1 è GND.

4.2.2.2 JTAG Margherita Incatenatu

U JTAG L'interfaccia permette à parechji dispusitivi esse cunnessi à una sola interfaccia in una cunfigurazione di margherita. I dispusitivi di destinazione deve esse tutti alimentati da u listessu supply voltage, sparte un node di terra cumuna, è deve esse cunnessu cum'è mostra in a figura sottu.

Figura 4-3. JTAG Daisy Chain

Quandu si cunnetta i dispositi in una catena di margherita, i seguenti punti deve esse cunsideratu:

- Tutti i dispositi devenu sparte un terrenu cumunu, cunnessu à GND nantu à a sonda Atmel-ICE

- Tutti i dispusitivi deve esse upirari nant'à u listessu scopu voltage. VTG nantu à l'Atmel-ICE deve esse cunnessu à questu voltage.

- TMS è TCK sò cunnessi in parallelu; TDI è TDO sò cunnessi in una seriale

- nSRST nantu à a sonda Atmel-ICE deve esse cunnessu à RESET in i dispositi se qualchissia di i dispositi in a catena disattiva u so J.TAG portu

- "Dispositivi prima" si riferisce à u numeru di JTAG i dispusitivi chì u signale TDI hà da passà in a catena margherita prima di ghjunghje à u dispusitivu di destinazione. In modu simile "dispositivi dopu" hè u numeru di dispusitivi chì u signale deve passà dopu à u dispusitivu di destinazione prima di ghjunghje à l'Atmel-ICE TDO.

- "I bits d'istruzione "prima" è "dopu" si riferisce à a somma tutale di tutti i JTAG lunghezze di registru di istruzzioni di i dispusitivi, chì sò culligati prima è dopu à u dispusitivu di destinazione in a catena margherita

- A lunghezza IR tutale (bits d'istruzzioni prima + lunghezza IR di u dispositivu di destinazione Atmel + bit d'istruzzioni dopu) hè limitata à un massimu di 256 bits. U numaru di dispusitivi in a catena hè limitatu à 15 prima è 15 dopu.

![]() Cunsigliu:

Cunsigliu:

Daisy chaining example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Per cunnette à l'Atmel AVR XMEGA® dispusitivu, i paràmetri di a catena margherita sò:

- Dispositivi prima: 1

- Dispositivi dopu: 1

- Bit di istruzzioni prima: 4 (i dispositi AVR à 8 bit anu 4 bit IR)

- Bit d'istruzione dopu: 5 (i dispositi AVR à 32 bit anu 5 bit IR)

Table 4-2. Lunghezze IR di Atmel MCU

| tipu di dispusitivu | lunghezza IR |

| AVR 8-bit | 4 bits |

| AVR 32-bit | 5 bits |

| SAM | 4 bits |

4.2.3. Cunnessu à un JTAG Target

L'Atmel-ICE hè dotatu di dui 50-mil 10-pin JTAG connettori. I dui connettori sò direttamente cunnessi elettricamente, ma cunforme à dui pinouts differenti; l'AVR JTAG header è l'intestazione ARM Cortex Debug. U connettore deve esse sceltu basatu annantu à u pinout di u pianu di destinazione, è micca u tipu MCU di destinazione - per esempiuampun dispositivu SAM muntatu in una pila AVR STK600 deve aduprà l'intestazione AVR.

Il pinout consigliato per l'AVR J a 10 pinTAG u connector hè mostratu in Figura 4-6.

U pinout cunsigliatu per u connettore ARM Cortex Debug 10-pin hè mostratu in Figura 4-2.

Cunnessione diretta à un header standard 10-pin 50-mil

Aduprate u cable flat 50-mil 10-pin (cumpresu in certi kit) per cunnette direttamente à una scheda chì sustene stu tipu di header. Aduprate u portu di u connettore AVR nantu à l'Atmel-ICE per l'intestazione cù u pinout AVR, è u portu di u connettore SAM per l'intestazione cumpletu cù u pinout di l'intestazione ARM Cortex Debug.

I pinouts per i dui porti di cunnessu 10-pin sò mostrati quì sottu.

Cunnessione à un header standard 10-pin 100-mil

Aduprate un adattatore standard da 50-mil à 100-mil per cunnette à intestazioni 100-mil. Una scheda adattatore (inclusa in certi kit) pò esse usata per questu scopu, o in alternativa u JTAGL'adattatore ICE3 pò esse usatu per i miri AVR.

![]() Impurtante:

Impurtante:

U JTAGL'adattatore ICE3 100-mil ùn pò micca esse usatu cù u portu di u connector SAM, postu chì i pins 2 è 10 (AVR GND) nantu à l'adattatore sò cunnessi.

Cunnessione à un header persunalizatu 100-mil

Se a vostra tavola di destinazione ùn hà micca un 10-pin JTAG header in 50- o 100-mil, pudete mapà à un pinout persunalizatu utilizendu u cable "mini-squid" 10-pin (cumpresu in certi kit), chì dà accessu à dece sockets individuali 100-mil.

Cunnessione à un header 20-pin 100-mil

Aduprate a scheda di l'adattatore (inclusa in certi kits) per cunnette à i miri cù un capu di 20-pin 100-mil.

Table 4-3. Atmel-ICE JTAG Pin Description

| Nome | AVR pin portu | SAM pin portu | Descrizzione |

| TCK | 1 | 4 | Test Clock (signale di clock da l'Atmel-ICE in u dispusitivu di destinazione). |

| TMS | 5 | 2 | Test Mode Select (signale di cuntrollu da l'Atmel-ICE in u dispusitivu di destinazione). |

| TDI | 9 | 8 | Test Data In (dati trasmessi da l'Atmel-ICE à u dispusitivu di destinazione). |

| TDO | 3 | 6 | Test Data Out (dati trasmessi da u dispusitivu di destinazione à l'Atmel-ICE). |

| nTRST | 8 | – | Test Reset (opzionale, solu in certi dispositi AVR). Adupratu per resettà u JTAG Controller TAP. |

| nSRST | 6 | 10 | Reset (opcional). Adupratu per resetten u dispusitivu di destinazione. A cunnessione di stu pin hè cunsigliatu postu chì permette à l'Atmel-ICE di mantene u dispusitivu di destinazione in un statu di reset, chì pò esse essenziale per debugging in certi scenarii. |

| VTG | 4 | 1 | Target voltage riferenza. L'Atmel-ICE samples the target voltage nant'à stu pin in ordine per alimentà i cunvertitori di livellu currettamente. L'Atmel-ICE tira menu di 3mA da stu pin in modu debugWIRE è menu di 1mA in altri modi. |

| GND | 2, 10 | 3, 5, 9 | Terra. Tuttu deve esse cunnessu per assicurà chì l'Atmel-ICE è u dispusitivu di destinazione sparte u listessu riferimentu in terra. |

4.2.4. Interfaccia fisica SWD

L'interfaccia ARM SWD hè un subset di u JTAG interfaccia, utilizendu pin TCK è TMS. L'ARM JTAG è AVR JTAG i connettori ùn sò, però, micca cumpatibili cù pin, cusì quandu si cuncepisce un PCB di l'applicazione, chì usa un dispositivu SAM cù SWD o J.TAG interfaccia, hè cunsigliatu di utilizà u pinout ARM mostratu in a figura sottu. U portu di u connettore SAM in l'Atmel-ICE pò cunnette direttamente à questu pinout.

Figura 4-4. Cunsigliu ARM SWD/JTAG Pinout di l'intestazione

L'Atmel-ICE hè capaci di trasmette traccia ITM in u furmatu UART à l'urdinatore host. A traccia hè catturata nantu à u pin TRACE/SWO di l'intestazione di 10 pin (JTAG pin TDO). I dati sò bufferati internamente in l'Atmel-ICE è sò mandati nantu à l'interfaccia HID à l'urdinatore host. A velocità massima di dati affidabile hè di circa 3MB/s.

4.2.5. Cunnessione à un Target SWD

L'interfaccia ARM SWD hè un subset di u JTAG interfaccia, aduprendu i pin TCK è TMS, chì significa chì quandu si cunnette à un dispositivu SWD, u 10-pin JTAG Connettore pò esse usatu tecnicamente. L'ARM JTAG è AVR JTAG I connettori ùn sò, però, micca cumpatibili cù pin, cusì dipende da u layout di u pianu di destinazione in usu. Quandu si usa un STK600 o una scheda chì face usu di l'AVR JTAG pinout, u portu di cunnessu AVR nantu à l'Atmel-ICE deve esse usatu. Quandu si cunnetta à una scheda, chì face usu di l'ARM JTAG pinout, u portu di cunnessu SAM nantu à l'Atmel-ICE deve esse usatu.

U pinout cunsigliatu per u connettore Cortex Debug 10-pin hè mostratu in Figura 4-4.

Cunnessione à un capu Cortex 10-pin 50-mil

Aduprate u cable flat (cumpresu in certi kit) per cunnette à un standard Cortex header 50-mil.

Cunnessione à un 10-pin 100-mil Cortex-layout header

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu di 100-mil Cortex-pinout.

Cunnessione à un capu SAM 20-pin 100-mil

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu SAM 20-pin 100-mil.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR o SAM è a tavula di destinazione. Sei cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

Table 4-4. Atmel-ICE SWD Pin Mapping

| Nome | AVR pin portu | SAM pin portu | Descrizzione |

| SWDC LK | 1 | 4 | Serial Wire Debug Clock. |

| SWDIO | 5 | 2 | Serial Wire Debug Data Input / Output. |

| SWO | 3 | 6 | Output Serial Wire (opcional - micca implementatu in tutti i dispositi). |

| nSRST | 6 | 10 | Resettate. |

| VTG | 4 | 1 | Target voltage riferenza. |

| GND | 2, 10 | 3, 5, 9 | Terra. |

4.2.6 Considerazioni Speciali

CANCELLA pin

Certi dispusitivi SAM includenu un pin ERASE chì hè affirmatu per fà una cancellazione completa di chip è sbloccare i dispositi nantu à quale u bit di sicurità hè stallatu. Questa funzione hè accumpagnata à u dispusitivu stessu è à u controller flash è ùn hè micca parte di u core ARM.

U pin ERASE ùn hè micca parte di alcun header di debug, è l'Atmel-ICE ùn hè cusì capace di affirmà stu signalu per sbloccare un dispositivu. In tali casi, l'utilizatore deve eseguisce a cancellazione manualmente prima di inizià una sessione di debug.

Interfacce fisiche JTAG interfaccia

A linea RESET deve esse sempre cunnessa in modu chì l'Atmel-ICE pò attivà u JTAG interfaccia.

Interfaccia SWD

A linea RESET deve esse sempre cunnessa per chì l'Atmel-ICE pò attivà l'interfaccia SWD.

4.3 Dispositivi AVR UC3 cù JTAG/aWire

Tutti i dispositi AVR UC3 presentanu u JTAG interfaccia di prugrammazione è debugging. Inoltre, certi dispositi AVR UC3 presentanu l'interfaccia aWire cù funziunalità identica cù un filu unicu. Verificate a datasheet di u dispusitivu per l'interfacce supportate di quellu dispusitivu

4.3.1 Atmel AVR UC3 On-chip Debug System

U sistema Atmel AVR UC3 OCD hè cuncepitu in cunfurmità cù u standard Nexus 2.0 (IEEE-ISTO 5001™-2003), chì hè un standard di debug in chip aperto altamente flessibile è putente per i microcontrollers 32-bit. Supporta e seguenti caratteristiche:

- Soluzione di debug compatible Nexus

- OCD supporta ogni velocità di CPU

- Sei punti di rottura di hardware di contatore di prugramma

- Dui punti di rottura di dati

- Breakpoints ponu esse cunfigurati cum'è watchpoints

- I punti di rottura di l'hardware ponu esse cumminati per dà una pausa in intervalli

- Numero illimitatu di punti di rottura di u prugramma d'utilizatori (usendu BREAK)

- Tracciamentu di ramu di u prugramma in tempu reale, traccia di dati, traccia di prucessu (supportatu solu da i debuggers cù u portu di cattura di traccia parallela)

Per più infurmazione nantu à u sistema AVR UC3 OCD, cunsultate i Manuali di Riferimentu Tecnicu AVR32UC, situatu in www.atmel.com/uc3.

4.3.2. JTAG Interfaccia fisica

U JTAG L'interfaccia hè custituita da un controller di Test Access Port (TAP) à 4 fili chì hè conforme à l'IEEE® 1149.1 standard. U standard IEEE hè statu sviluppatu per furnisce un modu standard di l'industria per pruvà efficacemente a connettività di i circuiti (Boundary Scan). I dispositi Atmel AVR è SAM anu allargatu sta funziunalità per include un supportu cumpletu di Programmazione è Debugging On-chip.

Figura 4-5. JTAG Basi di l'interfaccia

4.3.2.1 AVR JTAG Pinout

Quandu si cuncepisce un PCB d'applicazione, chì include un Atmel AVR cù u JTAG interfaccia, hè cunsigliatu à aduprà u pinout comu mostra in a figura sottu. E duie varianti 100-mil è 50-mil di stu pinout sò supportati, secondu u cablaggio è l'adattatori inclusi cù u kit particulari.

Figura 4-6. AVR JTAG Pinout di l'intestazione

Table 4-5. AVR JTAG Pin Description

| Nome | Pin |

Descrizzione |

| TCK | 1 | Test Clock (signale di clock da l'Atmel-ICE in u dispusitivu di destinazione). |

| TMS | 5 | Test Mode Select (signale di cuntrollu da l'Atmel-ICE in u dispusitivu di destinazione). |

| TDI | 9 | Test Data In (dati trasmessi da l'Atmel-ICE à u dispusitivu di destinazione). |

| TDO | 3 | Test Data Out (dati trasmessi da u dispusitivu di destinazione à l'Atmel-ICE). |

| nTRST | 8 | Test Reset (opzionale, solu in certi dispositi AVR). Adupratu per resettà u JTAG Controller TAP. |

| nSRST | 6 | Reset (opcional). Adupratu per resetten u dispusitivu di destinazione. A cunnessione di stu pin hè cunsigliatu postu chì permette à l'Atmel-ICE di mantene u dispusitivu di destinazione in un statu di reset, chì pò esse essenziale per debugging in certi scenarii. |

| VTG | 4 | Target voltage riferenza. L'Atmel-ICE samples the target voltage nant'à stu pin in ordine per alimentà i cunvertitori di livellu currettamente. L'Atmel-ICE tira menu di 3mA da stu pin in modu debugWIRE è menu di 1mA in altri modi. |

| GND | 2, 10 | Terra. Tramindui deve esse cunnessi per assicurà chì l'Atmel-ICE è u dispusitivu di destinazione sparte u listessu riferimentu in terra. |

![]() Cunsigliu: Ricurdatevi di include un condensatore di disaccoppiamentu trà u pin 4 è GND.

Cunsigliu: Ricurdatevi di include un condensatore di disaccoppiamentu trà u pin 4 è GND.

4.3.2.2 JTAG Margherita Incatenatu

U JTAG L'interfaccia permette à parechji dispusitivi esse cunnessi à una sola interfaccia in una cunfigurazione di margherita. I dispusitivi di destinazione deve esse tutti alimentati da u listessu supply voltage, sparte un node di terra cumuna, è deve esse cunnessu cum'è mostra in a figura sottu.

Figura 4-7. JTAG Daisy Chain

Quandu si cunnetta i dispositi in una catena di margherita, i seguenti punti deve esse cunsideratu:

- Tutti i dispositi devenu sparte un terrenu cumunu, cunnessu à GND nantu à a sonda Atmel-ICE

- Tutti i dispusitivi deve esse upirari nant'à u listessu scopu voltage. VTG nantu à l'Atmel-ICE deve esse cunnessu à questu voltage.

- TMS è TCK sò cunnessi in parallelu; TDI è TDO sò cunnessi in una catena seriale.

- nSRST nantu à a sonda Atmel-ICE deve esse cunnessu à RESET in i dispositi se qualchissia di i dispositi in a catena disattiva u so J.TAG portu

- "Dispositivi prima" si riferisce à u numeru di JTAG i dispusitivi chì u signale TDI hà da passà in a catena margherita prima di ghjunghje à u dispusitivu di destinazione. In modu simile "dispositivi dopu" hè u numeru di dispusitivi chì u signale deve passà dopu à u dispusitivu di destinazione prima di ghjunghje à l'Atmel-ICE TDO.

- "I bits d'istruzione "prima" è "dopu" si riferisce à a somma tutale di tutti i JTAG lunghezze di registru di istruzzioni di i dispusitivi, chì sò culligati prima è dopu à u dispusitivu di destinazione in a catena margherita

- A lunghezza IR tutale (bits d'istruzzioni prima + lunghezza IR di u dispositivu di destinazione Atmel + bit d'istruzzioni dopu) hè limitata à un massimu di 256 bits. U numaru di dispusitivi in a catena hè limitatu à 15 prima è 15 dopu.

Cunsigliu:

Daisy chaining example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Per cunnette à l'Atmel AVR XMEGA® dispusitivu, i paràmetri di a catena margherita sò:

- Dispositivi prima: 1

- Dispositivi dopu: 1

- Bit di istruzzioni prima: 4 (i dispositi AVR à 8 bit anu 4 bit IR)

- Bit d'istruzione dopu: 5 (i dispositi AVR à 32 bit anu 5 bit IR)

Table 4-6. Lunghezze IR di Atmel MCUS

| tipu di dispusitivu | lunghezza IR |

| AVR 8-bit | 4 bits |

| AVR 32-bit | 5 bits |

| SAM | 4 bits |

4.3.3.Connecting à un JTAG Target

L'Atmel-ICE hè dotatu di dui 50-mil 10-pin JTAG connettori. I dui connettori sò direttamente cunnessi elettricamente, ma cunforme à dui pinouts differenti; l'AVR JTAG header è l'intestazione ARM Cortex Debug. U connettore deve esse sceltu basatu annantu à u pinout di u pianu di destinazione, è micca u tipu MCU di destinazione - per esempiuampun dispositivu SAM muntatu in una pila AVR STK600 deve aduprà l'intestazione AVR.

Il pinout consigliato per l'AVR J a 10 pinTAG u connector hè mostratu in Figura 4-6.

U pinout cunsigliatu per u connettore ARM Cortex Debug 10-pin hè mostratu in Figura 4-2.

Cunnessione diretta à un header standard 10-pin 50-mil

Aduprate u cable flat 50-mil 10-pin (cumpresu in certi kit) per cunnette direttamente à una scheda chì sustene stu tipu di header. Aduprate u portu di u connettore AVR nantu à l'Atmel-ICE per l'intestazione cù u pinout AVR, è u portu di u connettore SAM per l'intestazione cumpletu cù u pinout di l'intestazione ARM Cortex Debug.

I pinouts per i dui porti di cunnessu 10-pin sò mostrati quì sottu.

Cunnessione à un header standard 10-pin 100-mil

Aduprate un adattatore standard da 50-mil à 100-mil per cunnette à intestazioni 100-mil. Una scheda adattatore (inclusa in certi kit) pò esse usata per questu scopu, o in alternativa u JTAGL'adattatore ICE3 pò esse usatu per i miri AVR.

![]() Impurtante:

Impurtante:

U JTAGL'adattatore ICE3 100-mil ùn pò micca esse usatu cù u portu di u connector SAM, postu chì i pins 2 è 10 (AVR GND) nantu à l'adattatore sò cunnessi.

Cunnessione à un header persunalizatu 100-mil

Se a vostra tavola di destinazione ùn hà micca un 10-pin JTAG header in 50- o 100-mil, pudete mapà à un pinout persunalizatu utilizendu u cable "mini-squid" 10-pin (cumpresu in certi kit), chì dà accessu à dece sockets individuali 100-mil.

Cunnessione à un header 20-pin 100-mil

Aduprate a scheda di l'adattatore (inclusa in certi kits) per cunnette à i miri cù un capu di 20-pin 100-mil.

Table 4-7. Atmel-ICE JTAG Pin Description

|

Nome |

Pin di u portu AVR | Pin portu SAM |

Descrizzione |

| TCK | 1 | 4 | Test Clock (signale di clock da l'Atmel-ICE in u dispusitivu di destinazione). |

| TMS | 5 | 2 | Test Mode Select (signale di cuntrollu da l'Atmel-ICE in u dispusitivu di destinazione). |

| TDI | 9 | 8 | Test Data In (dati trasmessi da l'Atmel-ICE à u dispusitivu di destinazione). |

| TDO | 3 | 6 | Test Data Out (dati trasmessi da u dispusitivu di destinazione à l'Atmel-ICE). |

| nTRST | 8 | – | Test Reset (opzionale, solu in certi dispositi AVR). Adupratu per resettà u JTAG Controller TAP. |

| nSRST | 6 | 10 | Reset (opcional). Adupratu per resetten u dispusitivu di destinazione. A cunnessione di stu pin hè cunsigliatu postu chì permette à l'Atmel-ICE di mantene u dispusitivu di destinazione in un statu di reset, chì pò esse essenziale per debugging in certi scenarii. |

| VTG | 4 | 1 | Target voltage riferenza. L'Atmel-ICE samples the target voltage nant'à stu pin in ordine per alimentà i cunvertitori di livellu currettamente. L'Atmel-ICE tira menu di 3mA da stu pin in modu debugWIRE è menu di 1mA in altri modi. |

| GND | 2, 10 | 3, 5, 9 | Terra. Tuttu deve esse cunnessu per assicurà chì l'Atmel-ICE è u dispusitivu di destinazione sparte u listessu riferimentu in terra. |

4.3.4 a Interfaccia fisica Wire

L'interfaccia aWire usa u filu RESET di u dispusitivu AVR per permette funzioni di prugrammazione è debugging. Una sequenza di attivazione speciale hè trasmessa da l'Atmel-ICE, chì disattiva a funziunalità RESET predeterminata di u pin. Quandu si cuncepisce un PCB di l'applicazione, chì include un Atmel AVR cù l'interfaccia aWire, hè cunsigliatu di utilizà u pinout cum'è mostra in Figura 4. -8. E duie varianti 100-mil è 50-mil di stu pinout sò supportati, secondu u cablaggio è l'adattatori inclusi cù u kit particulari.

Figura 4-8. a Pinout di l'intestazione Wire

![]() Cunsigliu:

Cunsigliu:

Siccomu aWire hè una interfaccia half-duplex, una resistenza di pull-up in a linea RESET in l'ordine di 47kΩ hè cunsigliatu per evità a rilevazione di falsi start-bit quandu cambia a direzzione.

L'interfaccia aWire pò esse usata cum'è una interfaccia di prugrammazione è di debugging. Tutte e funzioni di u sistema OCD dispunibuli attraversu u 10-pin JTAG L'interfaccia pò ancu esse accessu cù aWire.

4.3.5 Cunnessu à un Target aWire

L'interfaccia aWire richiede una sola linea di dati in più di VCC è GND. Nant'à u scopu, sta linea hè a linea nRESET, anche se u debugger usa u JTAG A linea TDO cum'è a linea di dati.

A pinout consigliata per u connettore aWire 6-pin hè mostrata in Figura 4-8.

Cunnessione à un header aWire 6-pin 100-mil

Aduprate u toccu 6-pin 100-mil nantu à u cable flat (cumpresu in certi kit) per cunnette à un header standard 100-mil aWire.

Cunnessione à un header aWire 6-pin 50-mil

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu standard 50-mil aWire.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Trè cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

Table 4-8. Atmel-ICE aWire Pin Mapping

| Pin di portu Atmel-ICE AVR | Pin di destinazione | Mini-squid pin |

a Pinout di u filu |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.3.6. Considerazioni Speciali

JTAG interfaccia

In certi dispositi Atmel AVR UC3 u JTAG portu ùn hè micca attivatu per difettu. Quandu si usanu sti dispusitivi, hè essenziale per cunnette a linea RESET per chì l'Atmel-ICE pò attivà u JTAG interfaccia.

interfaccia aWire

A baud rate di a cumunicazione aWire dipende da a freccia di u clock di u sistema, postu chì e dati devenu esse sincronizati trà sti dui domini. L'Atmel-ICE detecterà automaticamente chì u clock di u sistema hè statu abbassatu, è ricalibrerà u so baud rate in cunseguenza. A calibrazione automatica funziona solu finu à una frequenza di clock di u sistema di 8kHz. Passà à un clock di u sistema più bassu durante una sessione di debug pò causà a perdita di u cuntattu cù u mira.

Se necessariu, a velocità di baud aWire pò esse ristretta cù u paràmetru di clock aWire. A deteczione automatica hà sempre travagliatu, ma un valore di u tettu serà impostu nantu à i risultati.

Ogni condensatore stabilizzante cunnessu à u pin RESET deve esse disconnected when using aWire postu chì interferiscenu cù u funziunamentu currettu di l'interfaccia. Un pullup esternu debule (10kΩ o più altu) nantu à sta linea hè cunsigliatu.

Spegne u modu di sonnu

Certi dispositi AVR UC3 anu un regulatore internu chì pò esse usatu in modu di furnimentu 3.3V cù linee I / O regulate 1.8V. Questu significa chì u regulatore internu alimenta u core è a maiò parte di l'I / O. Solu Atmel AVR ONE! debugger supporta a debugging mentre usa i modi di sonnu induve stu regulatore hè chjusu.

4.3.7. Utilizzo EVTI / EVTO

I pins EVTI è EVTO ùn sò micca accessibili nantu à l'Atmel-ICE. Tuttavia, ponu ancu esse aduprati in cunjunzione cù altri equipaghji esterni.

EVTI pò esse usatu per i seguenti scopi:

- U mira pò esse furzatu à piantà l'esekzione in risposta à un avvenimentu esternu. Se i bits Event In Control (EIC) in u registru DC sò scritti à 0b01, a transizione alta à bassa nantu à u pin EVTI genererà una cundizione di breakpoint. EVTI deve esse bassu per un ciclu di clock CPU per guarantisci chì un breakpoint hè U bit di Breakpoint Esternu (EXB) in DS hè impostatu quandu questu accade.

- Generazione di missaghji di sincronizazione di traccia. Ùn hè micca usatu da l'Atmel-ICE.

EVTO pò esse usatu per i seguenti scopi:

- Indicà chì u CPU hà intrutu in debug Setting the EOS bits in DC to 0b01 causes the EVTO pin to be pulled low for one CPU clock cycle when the device target enters mode debug. Stu signalu pò esse usatu cum'è una fonte di trigger per un oscilloscope esternu.

- Indicà chì u CPU hà righjuntu un puntu di pausa o un puntu di vigilanza. Fixendu u bit EOC in un registru di cuntrollu di Breakpoint/Watchpoint currispundente, u statu di breakpoint o watchpoint hè indicatu nantu à u pin EVTO. I bits EOS in DC deve esse stabilitu à 0xb10 per attivà sta funzione. U pin EVTO pò esse cunnessu à un oscilloscopiu esternu per esaminà u watchpoint

- Generazione di segnali di timing di traccia. Ùn hè micca usatu da l'Atmel-ICE.

4.4 Dispositivi tinyAVR, megaAVR è XMEGA

I dispositi AVR presentanu diverse interfacce di prugrammazione è debugging. Verificate a datasheet di u dispusitivu per l'interfacce supportate di quellu dispusitivu.

- Un pocu AVR® i dispusitivi anu un TPI TPI pò esse usatu per a prugrammazione di u dispusitivu solu, è questi dispositi ùn anu micca capacità di debug in chip à tutti.

- Certi dispositi tinyAVR è certi dispositi megaAVR anu l'interfaccia debugWIRE, chì cunnetta à un sistema di debug in chip cunnisciutu cum'è tinyOCD. Tutti i dispositi cù debugWIRE anu ancu l'interfaccia SPI per u sistema

- Certi dispositi megaAVR anu un JTAG interfaccia di prugrammazione è debugging, cù un sistema di debug in chip canusciutu macari comu Tutti i dispusitivi cù JTAG presenta ancu l'interfaccia SPI cum'è una interfaccia alternativa per a prugrammazione in u sistema.

- Tutti i dispositi AVR XMEGA anu l'interfaccia PDI per a prugrammazione è Certi apparecchi AVR XMEGA anu ancu un J.TAG interfaccia cù funziunalità identica.

- I novi dispositi tinyAVR anu una interfaccia UPDI, chì hè utilizata per a prugrammazione è u debugging

Table 4-9. Riassuntu di l'interfaccia di prugrammazione è di debugging

|

|

UPDI | TPI | SPI | debugWIR E | JTAG | PDI | un filu |

SWD |

| tinyAVR | Novi dispusitivi | Certi dispusitivi | Certi dispusitivi | Certi dispusitivi | ||||

| megaAV R | Tutti i dispusitivi | Certi dispusitivi | Certi dispusitivi | |||||

| AVR XMEGA | Certi dispusitivi | Tutti i dispusitivi | ||||||

| AVR UC | Tutti i dispusitivi | Certi dispusitivi | ||||||

| SAM | Certi dispusitivi | Tutti i dispusitivi |

4.4.1. JTAG Interfaccia fisica

U JTAG L'interfaccia hè custituita da un controller di Test Access Port (TAP) à 4 fili chì hè conforme à l'IEEE® 1149.1 standard. U standard IEEE hè statu sviluppatu per furnisce un modu standard di l'industria per pruvà efficacemente a connettività di i circuiti (Boundary Scan). I dispositi Atmel AVR è SAM anu allargatu sta funziunalità per include un supportu cumpletu di Programmazione è Debugging On-chip.

Figura 4-9. JTAG Basi di l'interfaccia 4.4.2. Cunnessu à un JTAG Target

4.4.2. Cunnessu à un JTAG Target

L'Atmel-ICE hè dotatu di dui 50-mil 10-pin JTAG connettori. I dui connettori sò direttamente cunnessi elettricamente, ma cunforme à dui pinouts differenti; l'AVR JTAG header è l'intestazione ARM Cortex Debug. U connettore deve esse sceltu basatu annantu à u pinout di u pianu di destinazione, è micca u tipu MCU di destinazione - per esempiuampun dispositivu SAM muntatu in una pila AVR STK600 deve aduprà l'intestazione AVR.

Il pinout consigliato per l'AVR J a 10 pinTAG u connector hè mostratu in Figura 4-6.

U pinout cunsigliatu per u connettore ARM Cortex Debug 10-pin hè mostratu in Figura 4-2.

Cunnessione diretta à un header standard 10-pin 50-mil

Aduprate u cable flat 50-mil 10-pin (cumpresu in certi kit) per cunnette direttamente à una scheda chì sustene stu tipu di header. Aduprate u portu di u connettore AVR nantu à l'Atmel-ICE per l'intestazione cù u pinout AVR, è u portu di u connettore SAM per l'intestazione cumpletu cù u pinout di l'intestazione ARM Cortex Debug.

I pinouts per i dui porti di cunnessu 10-pin sò mostrati quì sottu.

Cunnessione à un header standard 10-pin 100-mil

Aduprate un adattatore standard da 50-mil à 100-mil per cunnette à intestazioni 100-mil. Una scheda adattatore (inclusa in certi kit) pò esse usata per questu scopu, o in alternativa u JTAGL'adattatore ICE3 pò esse usatu per i miri AVR.

![]() Impurtante:

Impurtante:

U JTAGL'adattatore ICE3 100-mil ùn pò micca esse usatu cù u portu di u connector SAM, postu chì i pins 2 è 10 (AVR GND) nantu à l'adattatore sò cunnessi.

Cunnessione à un header persunalizatu 100-mil

Se a vostra tavola di destinazione ùn hà micca un 10-pin JTAG header in 50- o 100-mil, pudete mapà à un pinout persunalizatu utilizendu u cable "mini-squid" 10-pin (cumpresu in certi kit), chì dà accessu à dece sockets individuali 100-mil.

Cunnessione à un header 20-pin 100-mil

Aduprate a scheda di l'adattatore (inclusa in certi kits) per cunnette à i miri cù un capu di 20-pin 100-mil.

Table 4-10. Atmel-ICE JTAG Pin Description

| Nome | AVR pin portu | SAM pin portu | Descrizzione |

| TCK | 1 | 4 | Test Clock (signale di clock da l'Atmel-ICE in u dispusitivu di destinazione). |

| TMS | 5 | 2 | Test Mode Select (signale di cuntrollu da l'Atmel-ICE in u dispusitivu di destinazione). |

| TDI | 9 | 8 | Test Data In (dati trasmessi da l'Atmel-ICE à u dispusitivu di destinazione). |

| TDO | 3 | 6 | Test Data Out (dati trasmessi da u dispusitivu di destinazione à l'Atmel-ICE). |

| nTRST | 8 | – | Test Reset (opzionale, solu in certi dispositi AVR). Adupratu per resettà u JTAG Controller TAP. |

| nSRST | 6 | 10 | Reset (opcional). Adupratu per resetten u dispusitivu di destinazione. A cunnessione di stu pin hè cunsigliatu postu chì permette à l'Atmel-ICE di mantene u dispusitivu di destinazione in un statu di reset, chì pò esse essenziale per debugging in certi scenarii. |

| VTG | 4 | 1 | Target voltage riferenza. L'Atmel-ICE samples the target voltage nant'à stu pin in ordine per alimentà i cunvertitori di livellu currettamente. L'Atmel-ICE tira menu di 3mA da stu pin in modu debugWIRE è menu di 1mA in altri modi. |

| GND | 2, 10 | 3, 5, 9 | Terra. Tuttu deve esse cunnessu per assicurà chì l'Atmel-ICE è u dispusitivu di destinazione sparte u listessu riferimentu in terra. |

4.4.3.SPI Interfaccia fisica

A Programmazione In-System usa l'SPI internu di Atmel AVR di destinazione (Interfaccia Periferica Seriale) per scaricà u codice in i ricordi flash è EEPROM. Ùn hè micca una interfaccia di debugging. Quandu cuncepisce un PCB di l'applicazione, chì include un AVR cù l'interfaccia SPI, u pinout cum'è mostra in a figura sottu deve esse utilizatu.

Figura 4-10. SPI Header Pinout 4.4.4. Cunnessione à un Target SPI

4.4.4. Cunnessione à un Target SPI

U pinout cunsigliatu per u connettore SPI 6-pin hè mostratu in Figura 4-10.

Cunnessione à un header SPI 6-pin 100-mil

Aduprate u toccu 6-pin 100-mil nantu à u cable flat (cumpresu in certi kit) per cunnette à un header SPI standard 100-mil.

Cunnessione à un header SPI 6-pin 50-mil

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu standard SPI 50-mil.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Sei cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

![]() Impurtante:

Impurtante:

L'interfaccia SPI hè disattivata in modu efficace quandu u fusible di debugWIRE enable (DWEN) hè programatu, ancu s'ellu SPIEN fuse hè ancu programatu. Per riattivare l'interfaccia SPI, u cumandimu "disable debugWIRE" deve esse emessu mentre in una sessione di debugWIRE. A disattivazione di debugWIRE in questu modu richiede chì u fusible SPIEN hè digià programatu. Se Atmel Studio ùn riesce à disattivà debugWIRE, hè prubabile perchè u fusible SPIEN ùn hè micca programatu. Se questu hè u casu, hè necessariu di utilizà un high-voltage interfaccia di prugrammazione per programà u fusible SPIEN.

![]() Info:

Info:

L'interfaccia SPI hè spessu referita cum'è "ISP", postu chì era a prima interfaccia In System Programming nantu à i prudutti Atmel AVR. Altre interfacce sò avà dispunibili per a Programmazione In u Sistema.

Table 4-11. Atmel-ICE SPI Pin Mapping

| Pin di portu Atmel-ICE AVR | Pin di destinazione | Mini-squid pin |

Pinout SPI |

| Pin 1 (TCK) | SCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | MISO | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | / RESET | 6 | 5 |

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | MOSI | 9 | 4 |

| Pin 10 (GND) | 0 |

4.4.5. PDI

L'interfaccia di prugramma è debug (PDI) hè una interfaccia proprietaria Atmel per a prugrammazione esterna è u debugging in chip di un dispositivu. PDI Physical hè una interfaccia 2-pin chì furnisce una cumunicazione sincrona bidirezionale half-duplex cù u dispusitivu di destinazione.

Quandu cuncepisce un PCB di l'applicazione, chì include un Atmel AVR cù l'interfaccia PDI, u pinout mostratu in a figura sottu deve esse utilizatu. Unu di l'adattatori 6-pin furniti cù u kit Atmel-ICE pò esse usatu per cunnette a sonda Atmel-ICE à u PCB di l'applicazione.

Figura 4-11. Pinout di l'intestazione PDI 4.4.6.Connecting à un Target PDI

4.4.6.Connecting à un Target PDI

U pinout cunsigliatu per u cunnessu PDI 6-pin hè mostratu in Figura 4-11.

Cunnessione à un header PDI 6-pin 100-mil

Aduprate u 6-pin 100-mil tap nantu à u cable flat (cumpresu in certi kits) per cunnette à un standard 100-mil PDI header.

Cunnessione à un header PDI 6-pin 50-mil

Aduprate a scheda di l'adattatore (inclusa in certi kits) per cunnette à un header PDI standard 50-mil.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Quattru cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

![]() Impurtante:

Impurtante:

U pinout necessariu hè diversu da u JTAGICE mkII JTAG sonda, induve PDI_DATA hè cunnessu à u pin 9. L'Atmel-ICE hè cumpatibile cù u pinout utilizatu da l'Atmel-ICE, JTAGICE3, AVR ONE!, è AVR Dragon™ prudutti.

Table 4-12. Atmel-ICE PDI Pin Mapping

|

Pin di portu Atmel-ICE AVR |

Pin di destinazione | Mini-squid pin |

Pinout Atmel STK600 PDI |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | PDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.7. Interfaccia fisica UPDI

U Programma Unificatu è Interfaccia di Debug (UPDI) hè una interfaccia proprietaria Atmel per a prugrammazione esterna è u debugging in chip di un dispositivu. Hè un successore di l'interfaccia fisica PDI 2-wire, chì si trova in tutti i dispositi AVR XMEGA. UPDI hè una interfaccia unicu filu chì furnisce una cumunicazione asincrona semi-duplex bidirezionale cù u dispusitivu di destinazione per scopi di prugrammazione è debugging.

Quandu cuncepisce un PCB di l'applicazione, chì include un Atmel AVR cù l'interfaccia UPDI, u pinout mostratu quì sottu deve esse usatu. Unu di l'adattatori 6-pin furniti cù u kit Atmel-ICE pò esse usatu per cunnette a sonda Atmel-ICE à u PCB di l'applicazione.

Figura 4-12. Pinout di l'intestazione UPDI 4.4.7.1 UPDI è / RESET

4.4.7.1 UPDI è / RESET

L'interfaccia di un filu UPDI pò esse un pin dedicatu o un pin spartutu, secondu u dispusitivu AVR di destinazione. Cunsultate a datasheet di u dispusitivu per più infurmazione.

Quandu l'interfaccia UPDI hè nantu à un pin spartutu, u pin pò esse cunfiguratu per esse UPDI, /RESET, o GPIO mettendu i fusibili RSTPINCFG [1: 0].

I fusi RTSPINCFG[1:0] anu e seguenti cunfigurazioni, cum'è descrittu in a datasheet. L'implicazioni pratiche di ogni scelta sò datu quì.

Table 4-13. RSTPINCFG[1:0] Configurazione di Fuse

| RSTPINCFG[1:0] | Cunfigurazione |

Usu |

| 00 | GPIO | Pin d'I/O di scopu generale. Per accede à UPDI, un impulsu 12V deve esse appiicatu à stu pin. Nisuna fonte di reset esterni hè dispunibule. |

| 01 | UPDI | Pin di prugrammazione è debugging dedicatu. Nisuna fonte di reset esterni hè dispunibule. |

| 10 | Resettate | Resetta l'ingressu di u signale. Per accede à UPDI, un impulsu 12V deve esse appiicatu à stu pin. |

| 11 | Riservatu | NA |

Nota: I vechji apparecchi AVR anu una interfaccia di prugrammazione, cunnisciuta cum'è "High-Voltage Programmazione "(esistenu varianti seriali è paralleli.) In generale, sta interfaccia richiede 12V per esse appiicata à u pin / RESET per a durata di a sessione di prugrammazione. L'interfaccia UPDI hè una interfaccia completamente diversa. U pin UPDI hè principalmente un pin di prugrammazione è debugging, chì pò esse fusionatu per avè una funzione alternativa (/RESET o GPIO). Se a funzione alternativa hè selezziunata allora un impulsu 12V hè necessariu nantu à quellu pin per riattivà a funziunalità UPDI.

Nota: Se un disignu richiede a spartera di u signale UPDI per via di limitazioni di pin, i passi deve esse pigliatu per assicurà chì u dispusitivu pò esse programatu. Per assicurà chì u signale UPDI pò funziunà currettamente, è ancu per evità danni à i cumpunenti esterni da l'impulsu 12V, hè cunsigliatu di disconnect qualsiasi cumpunenti nantu à questu pin quandu pruvate à debug o programà u dispusitivu. Questu pò esse fattu cù un resistore 0Ω, chì hè muntatu per difettu è sguassatu o rimpiazzatu da un pin header mentre debugging. Sta cunfigurazione significa effittivamenti chì a prugrammazione deve esse fatta prima di muntà u dispusitivu.

![]() Impurtante: L'Atmel-ICE ùn sustene micca 12V in a linea UPDI. In altre parolle, se u pin UPDI hè stata cunfigurata cum'è GPIO o RESET, l'Atmel-ICE ùn serà micca capaci di attivà l'interfaccia UPDI.

Impurtante: L'Atmel-ICE ùn sustene micca 12V in a linea UPDI. In altre parolle, se u pin UPDI hè stata cunfigurata cum'è GPIO o RESET, l'Atmel-ICE ùn serà micca capaci di attivà l'interfaccia UPDI.

4.4.8.Connecting à un Target UPDI

U pinout cunsigliatu per u cunnessu UPDI 6-pin hè mostratu in Figura 4-12.

Cunnessione à un header UPDI 6-pin 100-mil

Aduprate u 6-pin 100-mil tap in u cable flat (cumpresu in certi kits) per cunnette à un standard 100-mil UPDI header.

Cunnessione à un header UPDI 6-pin 50-mil

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un header UPDI standard 50-mil.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Trè cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

Table 4-14. Atmel-ICE UPDI Pin Mapping

| Pin di portu Atmel-ICE AVR | Pin di destinazione | Mini-squid pin |

Pinout Atmel STK600 UPDI |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | [/RESET sensu] | 6 | 5 |

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.9 Interfaccia fisica TPI

TPI hè una interfaccia di prugrammazione solu per certi dispositi AVR ATtiny. Ùn hè micca una interfaccia di debugging, è questi dispositi ùn anu micca capacità OCD. Quandu cuncepisce un PCB di l'applicazione chì include un AVR cù l'interfaccia TPI, u pinout mostratu in a figura sottu deve esse utilizatu.

Figura 4-13. Pinout di l'intestazione TPI 4.4.10.Connecting à un Target TPI

4.4.10.Connecting à un Target TPI

U pinout cunsigliatu per u cunnessu TPI à 6 pin hè mostratu in Figura 4-13.

Cunnessione à un header 6-pin 100-mil TPI

Aduprate u 6-pin 100-mil tap in u cable flat (cumpresu in certi kits) per cunnette à un standard 100-mil TPI header.

Cunnessione à un header 6-pin 50-mil TPI

Aduprate a scheda di l'adattatore (inclusa in certi kit) per cunnette à un capu standard 50-mil TPI.

Cunnessione à un header persunalizatu 100-mil

U cable mini-squid 10-pin deve esse usatu per cunnette trà u portu di u connettore Atmel-ICE AVR è a tavula di destinazione. Sei cunnessione sò necessarii, cum'è descrittu in a tabella sottu.

Table 4-15. Atmel-ICE TPI Pin Mapping

| Pin di portu Atmel-ICE AVR | Pin di destinazione | Mini-squid pin |

Pinout TPI |

| Pin 1 (TCK) | CLOCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | / RESET | 6 | 5 |

| Pin 7 (micca cunnessu) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.11. Debugging avanzatu (AVR JTAG /dispositivi debugWIRE)

I/O periferiche

A maiò parte di i periferichi I/O cuntinueghjanu à eseguisce ancu s'è l'esekzione di u prugramma hè fermata da un breakpoint. Esample: Se un breakpoint hè ghjuntu durante una trasmissione UART, a trasmissione serà cumpletata è i bits currispundenti stabiliti. A bandiera TXC (trasmissione cumpleta) serà stabilita è serà dispunibule nantu à u prossimu passu unicu di u codice, ancu s'ellu avaristi nurmale più tardi in un dispositivu attuale.

Tutti i moduli I/O continuanu à eseguisce in modu fermatu cù e duie eccezzioni seguenti:

- Timer/Counters (configurabile cù u software front-end)

- Watchdog Timer (sempre fermatu per impedisce reset durante a debugging)

Accessu I/O à un passu unicu

Siccomu l'I / O cuntinueghja à eseguisce in modu fermatu, deve esse cura per evità certi prublemi di timing. Per esample, u codice:

Quandu eseguisce stu codice in modu nurmale, u registru TEMP ùn leghje micca 0xAA perchè e dati ùn anu micca ancu esse stati fisichi à u pin à u mumentu chì hè s.ampguidatu da l'operazione IN. Una struzzione NOP deve esse piazzata trà l'istruzzioni OUT è IN per assicurà chì u valore currettu hè presente in u registru PIN.

In ogni casu, quandu si passa una sola funzione à traversu l'OCD, stu codice darà sempre 0xAA in u registru PIN postu chì l'I / O funziona à a velocità massima ancu quandu u core hè firmatu durante u passu unicu.

Singulu passu è timing

Certi registri anu da esse leghjite o scritte in un certu numaru di ciculi dopu avè attivatu un signalu di cuntrollu. Siccomu u clock I/O è i periferichi cuntinueghjanu à eseguisce à piena velocità in modu fermatu, un passu unicu attraversu un tali codice ùn risponde micca à i requisiti di timing. Trà dui passi unichi, u clock d'I / O pò avè eseguitu milioni di cicli. Per leghje o scrive cù successu i registri cù tali esigenze di timing, tutta a sequenza di lettura o scrittura deve esse realizata cum'è una operazione atomica chì eseguisce u dispusitivu à piena velocità. Questu pò esse fattu usendu una macro o una funzione chjamata per eseguisce u codice, o utilizate a funzione run-to-cursor in l'ambiente di debugging.