Programadors ICE Debugger

Programadors ICE Debugger

Guia d'usuari Programadors i depuradors

Programadors i depuradors

Atmel-ICE

GUIA D'USUARI

El depurador Atmel-ICE

Atmel-ICE és una potent eina de desenvolupament per depurar i programar microcontroladors Atmel ®SAM i Atmel AVR basats en ARM® Cortex®-M amb capacitat de depuració en xip ®.

Admet:

- Programació i depuració en xip de tots els microcontroladors Atmel AVR de 32 bits a tots dos JTAG i interfícies aWire

- Programació i depuració en xip de tots els dispositius de la família Atmel AVR XMEGA® tant a JTAG i interfícies PDI de 2 fils

- Programació (JTAG, SPI, UPDI) i depuració de tots els microcontroladors Atmel AVR de 8 bits amb suport OCD en qualsevol JTAG, debugWIRE o interfícies UPDI

- Programació i depuració de tots els microcontroladors basats en Atmel SAM ARM Cortex-M tant en SWD com en JTAG interfícies

- Programació (TPI) de tots els microcontroladors Atmel tinyAVR® de 8 bits amb suport per a aquesta interfície

Consulteu la llista de dispositius compatibles a la Guia d'usuari d'Atmel Studio per obtenir una llista completa de dispositius i interfícies compatibles amb aquesta versió del microprogramari.

Introducció

1.1. Introducció a l'Atmel-ICE

Atmel-ICE és una potent eina de desenvolupament per depurar i programar microcontroladors Atmel SAM i Atmel AVR basats en ARM Cortex-M amb capacitat de depuració en xip.

Admet:

- Programació i depuració en xip de tots els microcontroladors Atmel AVR UC3 tant a JTAG i interfícies aWire

- Programació i depuració en xip de tots els dispositius de la família AVR XMEGA tant a JTAG i interfícies PDI de 2 fils

- Programació (JTAG i SPI) i depuració de tots els microcontroladors AVR de 8 bits amb suport OCD tant a JTAG o interfícies debugWIRE

- Programació i depuració de tots els microcontroladors basats en Atmel SAM ARM Cortex-M tant en SWD com en JTAG interfícies

- Programació (TPI) de tots els microcontroladors Atmel tinyAVR de 8 bits amb suport per a aquesta interfície

1.2. Característiques d'Atmel-ICE

- Totalment compatible amb Atmel Studio

- Admet la programació i la depuració de tots els microcontroladors Atmel AVR UC3 de 32 bits

- Admet programació i depuració de tots els dispositius AVR XMEGA de 8 bits

- Admet la programació i la depuració de tots els dispositius Atmel megaAVR® i tinyAVR de 8 bits amb TOC

- Admet la programació i la depuració de tots els microcontroladors basats en SAM ARM Cortex-M

- Volum operatiu objectiutagrang d'1.62 V a 5.5 V

- Consumeix menys de 3 mA del VTref objectiu quan s'utilitza la interfície debugWIRE i menys d'1 mA per a totes les altres interfícies

- Suporta JTAG freqüències de rellotge de 32 kHz a 7.5 MHz

- Admet freqüències de rellotge PDI de 32 kHz a 7.5 MHz

- Admet velocitats de baudios debugWIRE des de 4 kbit/s fins a 0.5 Mbit/s

- Admet velocitats de transmissió aWire de 7.5 kbit/s a 7 Mbit/s

- Admet freqüències de rellotge SPI de 8 kHz a 5 MHz

- Admet velocitats de transmissió UPDI de fins a 750 kbit/s

- Admet freqüències de rellotge SWD de 32 kHz a 10 MHz

- Interfície host d'alta velocitat USB 2.0

- Captura de rastres en sèrie ITM fins a 3 MB/s

- Admet interfícies DGI SPI i USART quan no es depura ni es programa

- Admet 10 pins 50 mil JTAG connector amb pinouts AVR i Cortex. El cable de sonda estàndard admet capçaleres AVR de 6 pins ISP/PDI/TPI de 100 mil, així com de 10 pins de 50 mil. Hi ha un adaptador disponible per suportar capçaleres de 6 pins de 50 mil, 10 pins de 100 mil i 20 pins de 100 mil. Hi ha disponibles diverses opcions de kit amb diferents cablejats i adaptadors.

1.3. Requisits del sistema

La unitat Atmel-ICE requereix que s'instal·li a l'ordinador un entorn de depuració frontal Atmel Studio versió 6.2 o posterior.

L'Atmel-ICE s'ha de connectar a l'ordinador amfitrió mitjançant el cable USB subministrat o un cable Micro-USB certificat.

Introducció a l'Atmel-ICE

2.1. Contingut complet del kit

El kit complet Atmel-ICE conté aquests articles:

- Unitat Atmel-ICE

- Cable USB (1.8 m, alta velocitat, Micro-B)

- Placa adaptadora que conté adaptadors AVR de 50 mil, AVR/SAM de 100 mil i adaptadors SAM de 100 pins de 20 mil.

- Cable pla IDC amb connector de 10 pins 50 mil i connector de 6 pins 100 mil

- Mini cable de calamar de 50 mil de 10 pins amb endolls de 10 x 100 mil

Figura 2-1. Contingut del kit complet Atmel-ICE 2.2. Contingut del kit bàsic

2.2. Contingut del kit bàsic

El kit bàsic Atmel-ICE conté aquests elements:

- Unitat Atmel-ICE

- Cable USB (1.8 m, alta velocitat, Micro-B)

- Cable pla IDC amb connector de 10 pins 50 mil i connector de 6 pins 100 mil

Figura 2-2. Contingut del kit bàsic Atmel-ICE 2.3. Contingut del kit PCBA

2.3. Contingut del kit PCBA

El kit de PCBA Atmel-ICE conté aquests elements:

- Unitat Atmel-ICE sense encapsulació plàstica

Figura 2-3. Contingut del kit Atmel-ICE PCBA 2.4. Kits de recanvis

2.4. Kits de recanvis

Els següents kits de recanvis estan disponibles:

- Kit adaptador

- Kit de cables

Figura 2-4. Contingut del kit adaptador Atmel-ICE 2.5. S'ha acabat el kitview

2.5. S'ha acabat el kitview

Les opcions del kit Atmel-ICE es mostren esquemàticament aquí:

Figura 2-6. S'ha acabat el kit Atmel-ICEview 2.6. Muntatge de l'Atmel-ICE

2.6. Muntatge de l'Atmel-ICE

La unitat Atmel-ICE s'envia sense cables connectats. El kit complet ofereix dues opcions de cable:

- Cable pla IDC de 50 mil·límetres de 10 pins amb ISP de 6 pins i connectors de 10 pins

- Cable mini-calamar de 50 mils de 10 pins amb endolls de 10 x 100 mil.

Figura 2-7. Cables Atmel-ICE Per a la majoria de propòsits, es pot utilitzar el cable pla IDC de 50 pins de 10 mil, connectant-se de forma nativa als seus connectors de 10 o 6 pins, o connectant-se mitjançant la placa adaptadora. Es proporcionen tres adaptadors en un petit PCBA. S'inclouen els següents adaptadors:

Per a la majoria de propòsits, es pot utilitzar el cable pla IDC de 50 pins de 10 mil, connectant-se de forma nativa als seus connectors de 10 o 6 pins, o connectant-se mitjançant la placa adaptadora. Es proporcionen tres adaptadors en un petit PCBA. S'inclouen els següents adaptadors:

- 100 mil 10 pins JTAG/Adaptador SWD

- SAM J. de 100 mil i 20 pinsTAG/Adaptador SWD

- Adaptador SPI/debugWIRE/PDI/aWire de 50 mil

Figura 2-8. Adaptadors Atmel-ICE Nota:

Nota:

A 50 mil JTAG No s'ha proporcionat l'adaptador; això es deu al fet que el cable IDC de 50 pins de 10 mil es pot utilitzar per connectar-se directament a un J de 50 mil.TAG capçalera. Per al número de peça del component utilitzat per al connector de 50 pins de 10 mil, consulteu els números de peça dels connectors de destinació Atmel-ICE.

La capçalera ISP/PDI de 6 pins s'inclou com a part del cable IDC de 10 pins. Aquesta terminació es pot tallar si no és necessària.

Per muntar el vostre Atmel-ICE amb la seva configuració predeterminada, connecteu el cable IDC de 10 pins de 50 mil a la unitat tal com es mostra a continuació. Assegureu-vos d'orientar el cable de manera que el cable vermell (pin 1) del cable s'alinei amb l'indicador triangular del cinturó blau de la carcassa. El cable s'ha de connectar cap amunt des de la unitat. Assegureu-vos de connectar-vos al port corresponent al pinout del vostre objectiu: AVR o SAM.

Figura 2-9. Connexió de cable Atmel-ICE Figura 2-10. Connexió de la sonda Atmel-ICE AVR

Figura 2-10. Connexió de la sonda Atmel-ICE AVR

Figura 2-11. Connexió de la sonda Atmel-ICE SAM

Figura 2-11. Connexió de la sonda Atmel-ICE SAM 2.7. Obertura de l'Atmel-ICE

2.7. Obertura de l'Atmel-ICE

Nota:

Per al funcionament normal, la unitat Atmel-ICE no s'ha d'obrir. L'obertura de la unitat es fa sota el vostre propi risc.

S'han de prendre precaucions antiestàtiques.

El recinte Atmel-ICE consta de tres components de plàstic separats: coberta superior, coberta inferior i cinturó blau, que s'uneixen durant el muntatge. Per obrir la unitat, simplement introduïu un tornavís pla gran a les obertures del cinturó blau, apliqueu una mica de pressió cap a dins i gireu suaument. Repetiu el procés als altres forats del pargo i la coberta superior sortirà.

Figura 2-12. Obertura de l'Atmel-ICE (1)

Figura 2-13. Obertura de l'Atmel-ICE (2)

Figura 2-13. Obertura de l'Atmel-ICE (2)

Figura 2-14. Obertura de l'Atmel-ICE(3)

Figura 2-14. Obertura de l'Atmel-ICE(3) Per tornar a tancar la unitat, només cal que alineeu correctament les cobertes superior i inferior i premeu fermament.

Per tornar a tancar la unitat, només cal que alineeu correctament les cobertes superior i inferior i premeu fermament.

2.8. Alimentació de l'Atmel-ICE

L'Atmel-ICE funciona amb el bus USB voltage. Requereix menys de 100 mA per funcionar i, per tant, es pot alimentar mitjançant un concentrador USB. El LED d'alimentació s'il·luminarà quan la unitat estigui connectada. Quan no estigui connectada en una sessió de programació o depuració activa, la unitat entrarà en el mode de baix consum d'energia per preservar la bateria de l'ordinador. L'Atmel-ICE no es pot apagar; s'ha de desconnectar quan no estigui en ús.

2.9. Connexió a l'ordinador amfitrió

L'Atmel-ICE es comunica principalment mitjançant una interfície HID estàndard i no requereix un controlador especial a l'ordinador amfitrió. Per utilitzar la funcionalitat avançada de passarel·la de dades de l'Atmel-ICE, assegureu-vos d'instal·lar el controlador USB a l'ordinador amfitrió. Això es fa automàticament quan s'instal·la el programari de front-end proporcionat gratuïtament per Atmel. Mireu www.atmel.com per obtenir més informació o per descarregar el programari de front-end més recent.

L'Atmel-ICE s'ha de connectar a un port USB disponible a l'ordinador amfitrió mitjançant el cable USB proporcionat o un cable micro USB certificat adequat. L'Atmel-ICE conté un controlador compatible amb USB 2.0 i pot funcionar tant en modes de velocitat completa com d'alta velocitat. Per obtenir els millors resultats, connecteu l'Atmel-ICE directament a un concentrador d'alta velocitat compatible amb USB 2.0 a l'ordinador amfitrió mitjançant el cable proporcionat.

2.10. Instal·lació del controlador USB

2.10.1. Finestres

Quan instal·leu l'Atmel-ICE en un ordinador amb Microsoft® Windows®, el controlador USB es carrega quan l'Atmel-ICE es connecta per primera vegada.

Nota:

Assegureu-vos d'instal·lar els paquets de programari frontal abans de connectar la unitat per primera vegada.

Un cop instal·lat correctament, l'Atmel-ICE apareixerà al gestor de dispositius com a "Dispositiu d'interfície humana".

Connexió de l'Atmel-ICE

3.1. Connexió a dispositius de destinació AVR i SAM

L'Atmel-ICE està equipat amb dos J de 50 pins de 10 milTAG connectors. Tots dos connectors estan connectats directament elèctricament, però s'ajusten a dos pinouts diferents; l'AVR JTAG la capçalera i la capçalera ARM Cortex Debug. El connector s'ha de seleccionar en funció del pinout de la placa de destinació i no del tipus de MCU de destinació, per exempleampun dispositiu SAM muntat en una pila AVR STK® 600 hauria d'utilitzar la capçalera AVR.

Hi ha diversos cablejats i adaptadors disponibles als diferents kits Atmel-ICE. Un acabatview es mostra les opcions de connexió.

Figura 3-1. Opcions de connexió Atmel-ICE El cable vermell marca el pin 1 del connector de 10 pins de 50 mil. El pin 1 del connector de 6 pins de 100 mil es col·loca a la dreta de la clau quan es veu el connector des del cable. El pin 1 de cada connector de l'adaptador està marcat amb un punt blanc. La figura següent mostra el pinout del cable de depuració. El connector marcat amb A es connecta al depurador mentre que el costat B es connecta a la placa de destinació.

El cable vermell marca el pin 1 del connector de 10 pins de 50 mil. El pin 1 del connector de 6 pins de 100 mil es col·loca a la dreta de la clau quan es veu el connector des del cable. El pin 1 de cada connector de l'adaptador està marcat amb un punt blanc. La figura següent mostra el pinout del cable de depuració. El connector marcat amb A es connecta al depurador mentre que el costat B es connecta a la placa de destinació.

Figura 3-2. Pinout del cable de depuració

3.2. Connexió a un JTAG Objectiu

3.2. Connexió a un JTAG Objectiu

L'Atmel-ICE està equipat amb dos J de 50 pins de 10 milTAG connectors. Tots dos connectors estan connectats directament elèctricament, però s'ajusten a dos pinouts diferents; l'AVR JTAG la capçalera i la capçalera ARM Cortex Debug. El connector s'ha de seleccionar en funció del pinout de la placa de destinació i no del tipus de MCU de destinació, per exempleampun dispositiu SAM muntat en una pila AVR STK600 hauria d'utilitzar la capçalera AVR.

El pinout recomanat per a l'AVR J de 10 pinsTAG connector es mostra a la figura 4-6. A la figura 10-4 es mostra el pinout recomanat per al connector ARM Cortex Debug de 2 pins.

Connexió directa a una capçalera estàndard de 10 pins de 50 mil

Utilitzeu el cable pla de 50 pins de 10 mil (inclòs en alguns kits) per connectar-vos directament a una placa que admeti aquest tipus de capçalera. Utilitzeu el port del connector AVR de l'Atmel-ICE per a les capçaleres amb el pinout AVR i el port del connector SAM per a les capçaleres que compleixin amb el pinout de la capçalera ARM Cortex Debug.

A continuació es mostren els pinouts dels dos ports del connector de 10 pins.

Connexió a una capçalera estàndard de 10 pins de 100 mil

Utilitzeu un adaptador estàndard de 50 mil a 100 mil per connectar-se a capçaleres de 100 mil. Es pot utilitzar una placa adaptadora (inclosa en alguns kits) per a aquest propòsit o, alternativament, la placa JTAGL'adaptador ICE3 es pot utilitzar per a objectius AVR.

![]() Important:

Important:

El JTAGL'adaptador ICE3 de 100 mil no es pot utilitzar amb el port del connector SAM, ja que els pins 2 i 10 (AVR GND) de l'adaptador estan connectats.

Connexió a una capçalera personalitzada de 100 mil

Si el vostre tauler de destinació no té un dispositiu J de 10 pins compatibleTAG capçalera de 50 o 100 mil, podeu assignar un pinout personalitzat mitjançant el cable "mini-calamar" de 10 pins (inclòs en alguns kits), que dóna accés a deu endolls individuals de 100 mil.

Connexió a un capçal de 20 pins de 100 milr

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a objectius amb una capçalera de 20 pins de 100 mil.

Taula 3-1. Atmel-ICE JTAG Descripció del pin

| Nom | AVR pin del port | SAM pin del port | Descripció |

| TCK | 1 | 4 | Rellotge de prova (senyal de rellotge de l'Atmel-ICE al dispositiu objectiu). |

| TMS | 5 | 2 | Selecció del mode de prova (senyal de control de l'Atmel-ICE al dispositiu objectiu). |

| TDI | 9 | 8 | Test Data In (dades transmeses des de l'Atmel-ICE al dispositiu objectiu). |

| TDO | 3 | 6 | Sortida de dades de prova (dades transmeses des del dispositiu objectiu a l'Atmel-ICE). |

| nTRST | 8 | – | Prova de restabliment (opcional, només en alguns dispositius AVR). S'utilitza per restablir el JTAG Controlador TAP. |

| nSRST | 6 | 10 | Restablir (opcional). S'utilitza per restablir el dispositiu de destinació. Es recomana connectar aquest pin, ja que permet que l'Atmel-ICE mantingui el dispositiu objectiu en un estat de restabliment, que pot ser essencial per a la depuració en determinats escenaris. |

| VTG | 4 | 1 | Vol. objectiutage referència. Els Atmel-ICE samples the target voltage en aquest pin per alimentar correctament els convertidors de nivell. L'Atmel-ICE extreu menys de 3 mA d'aquest pin en mode debugWIRE i menys d'1 mA en altres modes. |

| GND | 2, 10 | 3, 5, 9 | Terra. Tots han d'estar connectats per garantir que l'Atmel-ICE i el dispositiu objectiu comparteixen la mateixa referència de terra. |

3.3. Connexió a un objectiu aWire

La interfície aWire només requereix una línia de dades a més de VCC i GND. A l'objectiu, aquesta línia és la línia nRESET, tot i que el depurador utilitza el JTAG Línia TDO com a línia de dades.

A la figura 6-4 es mostra el pinout recomanat per al connector aWire de 8 pins.

Connexió a una capçalera aWire de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera estàndard de 100 mil aWire.

Connexió a una capçalera aWire de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera aWire estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Es requereixen tres connexions, tal com es descriu a la taula següent.

Taula 3-2. Atmel-ICE aWire Pin Mapping

|

Pins del port Atmel-ICE AVR |

Pins objectiu | Mini-pin de calamar |

a Pintació del cable |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DADES | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (no connectat) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.4. Connexió a un PDI Target

El pinout recomanat per al connector PDI de 6 pins es mostra a la figura 4-11.

Connexió a una capçalera PDI de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera PDI estàndard de 100 mil.

Connexió a una capçalera PDI de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera PDI estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Es requereixen quatre connexions, tal com es descriu a la taula següent.

![]() Important:

Important:

El pinout requerit és diferent del de JTAGICE mkII JTAG sonda, on PDI_DATA està connectat al pin 9. L'Atmel-ICE és compatible amb el pinout utilitzat per l'Atmel-ICE, JTAGProductes ICE3, AVR ONE! i AVR Dragon™.

Taula 3-3. Atmel-ICE PDI Pin Mapping

| Pins del port Atmel-ICE AVR | Pins objectiu | Mini-pin de calamar |

a Pintació del cable |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DADES | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (no connectat) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.4 Connexió a un PDI Target

El pinout recomanat per al connector PDI de 6 pins es mostra a la figura 4-11.

Connexió a una capçalera PDI de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera PDI estàndard de 100 mil.

Connexió a una capçalera PDI de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera PDI estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Es requereixen quatre connexions, tal com es descriu a la taula següent.

![]() Important:

Important:

El pinout requerit és diferent del de JTAGICE mkII JTAG sonda, on PDI_DATA està connectat al pin 9. L'Atmel-ICE és compatible amb el pinout utilitzat per l'Atmel-ICE, JTAGICE3, AVR ONE! i AVR Dragon™ productes.

Taula 3-3. Atmel-ICE PDI Pin Mapping

| Pin del port Atmel-ICE AVR | Pins objectiu | Mini-pin de calamar | Pinout Atmel STK600 PDI |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | PDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (no connectat) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.5 Connexió a un objectiu UPDI

El pinout recomanat per al connector UPDI de 6 pins es mostra a la figura 4-12.

Connexió a una capçalera UPDI de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera UPDI estàndard de 100 mil.

Connexió a una capçalera UPDI de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera UPDI estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Es requereixen tres connexions, tal com es descriu a la taula següent.

Taula 3-4. Atmel-ICE UPDI Pin Mapping

| Pin del port Atmel-ICE AVR | Pins objectiu | Mini-pin de calamar |

Pinout Atmel STK600 UPDI |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | [/RESET el sentit] | 6 | 5 |

| Pin 7 (no connectat) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.6 Connexió a un objectiu debugWIRE

El pinout recomanat per al connector debugWIRE (SPI) de 6 pins es mostra a la Taula 3-6.

Connexió a una capçalera SPI de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera SPI estàndard de 100 mil.

Connexió a una capçalera SPI de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera SPI estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Calen tres connexions, tal com es descriu a la Taula 3-5.

Tot i que la interfície debugWIRE només requereix una línia de senyal (RESET), VCC i GND per funcionar correctament, es recomana tenir accés al connector SPI complet perquè la interfície debugWIRE es pugui activar i desactivar mitjançant la programació SPI.

Quan el fusible DWEN està habilitat, la interfície SPI s'anul·la internament per tal que el mòdul OCD tingui control sobre el pin RESET. El debugWIRE OCD és capaç de desactivar-se temporalment (utilitzant el botó de la pestanya de depuració del diàleg de propietats d'Atmel Studio), alliberant així el control de la línia RESET. La interfície SPI torna a estar disponible (només si el fusible SPIEN està programat), permetent que el fusible DWEN es desprograma mitjançant la interfície SPI. Si es canvia l'alimentació abans que el fusible DWEN no estigui programat, el mòdul debugWIRE tornarà a prendre el control del pin RESET.

Nota:

És molt recomanable deixar que Atmel Studio s'ocupi de la configuració i la neteja del fusible DWEN.

No és possible utilitzar la interfície debugWIRE si els bits de bloqueig del dispositiu AVR objectiu estan programats. Assegureu-vos sempre que els bits de bloqueig estiguin esborrats abans de programar el fusible DWEN i mai posis els bits de bloqueig mentre el fusible DWEN estigui programat. Si s'estableixen tant el fusible d'habilitació debugWIRE (DWEN) com els bits de bloqueig, es pot utilitzar High Vol.tage Programació per fer un esborrat de xip i, per tant, esborrar els lockbits.

Quan s'esborren els bits de bloqueig, la interfície debugWIRE es tornarà a habilitar. La interfície SPI només és capaç de llegir fusibles, llegir la signatura i realitzar un esborrat de xip quan el fusible DWEN no està programat.

Taula 3-5. Mapeig de pins Atmel-ICE debugWIRE

| Pin del port Atmel-ICE AVR | Pins objectiu |

Mini-pin de calamar |

| Pin 1 (TCK) | 1 | |

| Pin 2 (GND) | GND | 2 |

| Pin 3 (TDO) | 3 | |

| Pin 4 (VTG) | VTG | 4 |

| Pin 5 (TMS) | 5 | |

| Pin 6 (nSRST) | RESET | 6 |

| Pin 7 (no connectat) | 7 | |

| Pin 8 (nTRST) | 8 | |

| Pin 9 (TDI) | 9 | |

| Pin 10 (GND) | 0 |

3.7 Connexió a un objectiu SPI

El pinout recomanat per al connector SPI de 6 pins es mostra a la figura 4-10.

Connexió a una capçalera SPI de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera SPI estàndard de 100 mil.

Connexió a una capçalera SPI de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera SPI estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Es requereixen sis connexions, tal com es descriu a la taula següent.

![]() Important:

Important:

La interfície SPI es desactiva efectivament quan es programa el fusible d'habilitació debugWIRE (DWEN), fins i tot si també es programa el fusible SPIEN. Per tornar a habilitar la interfície SPI, s'ha d'emetre l'ordre "desactivar debugWIRE" mentre es troba en una sessió de depuració debugWIRE. Desactivar debugWIRE d'aquesta manera requereix que el fusible SPIEN ja estigui programat. Si Atmel Studio no desactiva debugWIRE, és probable perquè el fusible SPIEN NO està programat. Si aquest és el cas, cal utilitzar un alt voltage interfície de programació per programar el fusible SPIEN.

![]() Informació:

Informació:

La interfície SPI sovint es coneix com "ISP", ja que va ser la primera interfície de programació del sistema dels productes Atmel AVR. Altres interfícies ja estan disponibles per a la programació del sistema.

Taula 3-6. Atmel-ICE SPI Pin Mapping

| Pins del port Atmel-ICE AVR | Pins objectiu | Mini-pin de calamar |

Pinout SPI |

| Pin 1 (TCK) | SCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | MISO | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | / RESET | 6 | 5 |

| Pin 7 (no connectat) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | Extensió MOSI | 9 | 4 |

| Pin 10 (GND) | 0 |

3.8 Connexió a un TPI Target

El pinout recomanat per al connector TPI de 6 pins es mostra a la figura 4-13.

Connexió a una capçalera TPI de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera TPI estàndard de 100 mil.

Connexió a una capçalera TPI de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera TPI estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Es requereixen sis connexions, tal com es descriu a la taula següent.

Taula 3-7. Atmel-ICE TPI Pin Mapping

| Pins del port Atmel-ICE AVR | Pins objectiu | Mini-pin de calamar |

Pinout TPI |

| Pin 1 (TCK) | RELOJ | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DADES | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 |

| Pin 6 (nSRST) | / RESET | 6 | 5 |

| Pin 7 (no connectat) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

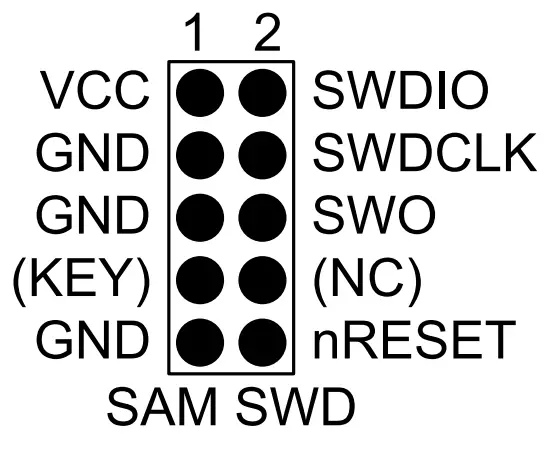

3.9 Connexió a un objectiu SWD

La interfície ARM SWD és un subconjunt de JTAG interfície, fent ús dels pins TCK i TMS, el que significa que quan es connecta a un dispositiu SWD, el J de 10 pinsTAG El connector es pot utilitzar tècnicament. L'ARM JTAG i AVR JTAG Els connectors, però, no són compatibles amb pins, de manera que això depèn de la disposició de la placa de destinació en ús. Quan utilitzeu un STK600 o una placa que utilitzeu l'AVR JTAG pinout, s'ha d'utilitzar el port del connector AVR de l'Atmel-ICE. Quan es connecta a una placa, que fa ús de l'ARM JTAG pinout, s'ha d'utilitzar el port del connector SAM de l'Atmel-ICE.

El pinout recomanat per al connector Cortex Debug de 10 pins es mostra a la figura 4-4.

Connexió a una capçalera Cortex de 10 pins de 50 mil

Utilitzeu el cable pla (inclòs en alguns kits) per connectar-vos a una capçalera Cortex estàndard de 50 mil.

Connexió a una capçalera de disseny Cortex de 10 pins i 100 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera Cortex-pinout de 100 mil.

Connexió a una capçalera SAM de 20 pins de 100 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera SAM de 20 pins de 100 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR o SAM i la placa de destinació. Es requereixen sis connexions, tal com es descriu a la taula següent.

Taula 3-8. Atmel-ICE SWD Pin Mapping

| Nom | AVR pin del port | SAM pin del port | Descripció |

| SWDC LK | 1 | 4 | Rellotge de depuració de cable sèrie. |

| SWDIO | 5 | 2 | Entrada/sortida de dades de depuració de cable sèrie. |

| SWO | 3 | 6 | Sortida de cable sèrie (opcional, no implementada en tots els dispositius). |

| nSRST | 6 | 10 | Restableix. |

| VTG | 4 | 1 | Vol. objectiutage referència. |

| GND | 2, 10 | 3, 5, 9 | Terra. |

3.10 Connexió a la interfície de passarel·la de dades

L'Atmel-ICE admet una interfície de passarel·la de dades (DGI) limitada quan no s'utilitza la depuració i la programació. La funcionalitat és idèntica a la que es troba als kits Atmel Xplained Pro alimentats pel dispositiu Atmel EDBG.

La interfície de passarel·la de dades és una interfície per transmetre dades des del dispositiu de destinació a un ordinador. Això vol ser una ajuda en la depuració d'aplicacions, així com per a la demostració de les funcions de l'aplicació que s'executa al dispositiu de destinació.

DGI consta de diversos canals per a la transmissió de dades. L'Atmel-ICE admet els modes següents:

- USART

- SPI

Taula 3-9. Atmel-ICE DGI USART Pinout

|

Port AVR |

Port SAM | Pin DGI USART |

Descripció |

| 3 | 6 | TX | Transmet el pin des d'Atmel-ICE al dispositiu objectiu |

| 4 | 1 | VTG | Vol. objectiutage (referència voltage) |

| 8 | 7 | RX | Rebeu el pin del dispositiu objectiu a Atmel-ICE |

| 9 | 8 | CLK | Rellotge USART |

| 2, 10 | 3, 5, 9 | GND | Terra |

Taula 3-10. Atmel-ICE DGI SPI Pinout

|

Port AVR |

Port SAM | Pin DGI SPI |

Descripció |

| 1 | 4 | SCK | Rellotge SPI |

| 3 | 6 | MISO | Master In Slave Out |

| 4 | 1 | VTG | Vol. objectiutage (referència voltage) |

| 5 | 2 | nCS | Selecció de xip actiu baix |

| 9 | 8 | Extensió MOSI | Master Out Slave In |

| 2, 10 | 3, 5, 9 | GND | Terra |

![]() Important: Les interfícies SPI i USART no es poden utilitzar simultàniament.

Important: Les interfícies SPI i USART no es poden utilitzar simultàniament.

![]() Important: DGI i la programació o la depuració no es poden utilitzar simultàniament.

Important: DGI i la programació o la depuració no es poden utilitzar simultàniament.

Depuració al xip

4.1 Introducció

Depuració al xip

Un mòdul de depuració en xip és un sistema que permet a un desenvolupador supervisar i controlar l'execució en un dispositiu des d'una plataforma de desenvolupament externa, normalment mitjançant un dispositiu conegut com a depurador o adaptador de depuració.

Amb un sistema OCD, l'aplicació es pot executar mantenint les característiques elèctriques i de temporització exactes al sistema objectiu, alhora que es pot aturar l'execució de manera condicional o manual i inspeccionar el flux i la memòria del programa.

Mode d'execució

En mode d'execució, l'execució del codi és completament independent de l'Atmel-ICE. L'Atmel-ICE supervisarà contínuament el dispositiu objectiu per veure si s'ha produït una condició de trencament. Quan això succeeix, el sistema OCD interrogarà el dispositiu mitjançant la seva interfície de depuració, permetent a l'usuari fer-ho view l'estat intern del dispositiu.

Mode aturat

Quan s'arriba a un punt d'interrupció, l'execució del programa s'atura, però algunes E/S poden continuar funcionant com si no s'hagués produït cap punt d'interrupció. Per example, suposa que s'acaba d'iniciar una transmissió USART quan s'arriba a un punt d'interrupció. En aquest cas, l'USART continua funcionant a tota velocitat completant la transmissió, tot i que el nucli està en mode aturat.

Punts d'interrupció del maquinari

El mòdul OCD objectiu conté una sèrie de comparadors de comptadors de programes implementats al maquinari. Quan el comptador del programa coincideix amb el valor emmagatzemat en un dels registres comparadors, l'OCD entra en mode aturat. Com que els punts d'interrupció de maquinari requereixen maquinari dedicat al mòdul OCD, el nombre de punts d'interrupció disponibles depèn de la mida del mòdul OCD implementat a l'objectiu. Normalment, un d'aquests comparadors de maquinari és "reservat" pel depurador per a ús intern.

Punts d'interrupció del programari

Un punt d'interrupció del programari és una instrucció BREAK col·locada a la memòria del programa del dispositiu de destinació. Quan es carregui aquesta instrucció, l'execució del programa es trencarà i l'OCD entrarà en mode aturat. Per continuar amb l'execució, s'ha de donar una ordre d'inici des de l'OCD. No tots els dispositius Atmel tenen mòduls OCD compatibles amb la instrucció BREAK.

4.2 Dispositius SAM amb JTAG/SWD

Tots els dispositius SAM disposen de la interfície SWD per a la programació i la depuració. A més, alguns dispositius SAM inclouen un JTAG interfície amb idèntica funcionalitat. Comproveu el full de dades del dispositiu per veure les interfícies compatibles amb aquest dispositiu.

4.2.1.Components ARM CoreSight

Els microcontroladors basats en Atmel ARM Cortex-M implementen components OCD compatibles amb CoreSight. Les característiques d'aquests components poden variar d'un dispositiu a un altre. Per obtenir més informació, consulteu la fitxa tècnica del dispositiu, així com la documentació de CoreSight proporcionada per ARM.

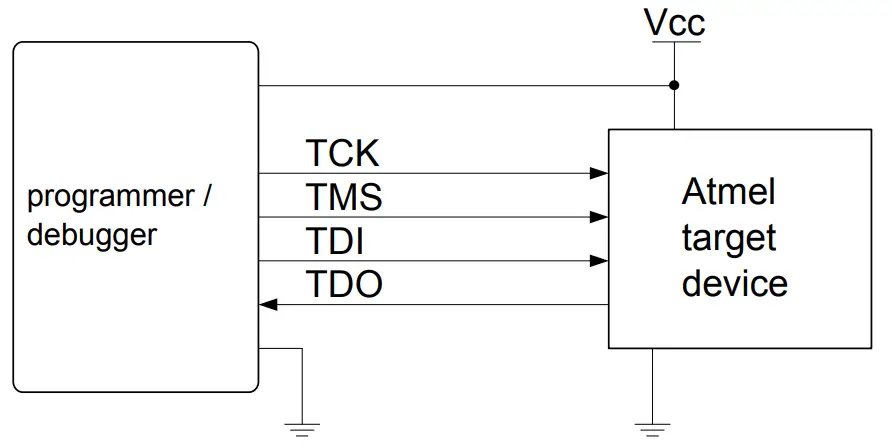

4.2.1. JTAG Interfície física

El JTAG La interfície consta d'un controlador de port d'accés de prova (TAP) de 4 cables que compleix amb l'IEEE® estàndard 1149.1. L'estàndard IEEE es va desenvolupar per proporcionar una manera estàndard de la indústria de provar de manera eficient la connectivitat de la placa de circuits (Boundary Scan). Els dispositius Atmel AVR i SAM han ampliat aquesta funcionalitat per incloure suport complet de programació i depuració en xip.

Figura 4-1. JTAG Conceptes bàsics de la interfície

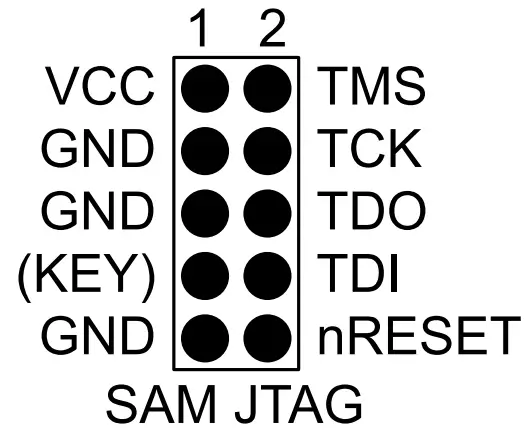

4.2.2.1 SAM JTAG Pinout (connector de depuració Cortex-M)

Quan es dissenya una PCB d'aplicació que inclogui un SAM Atmel amb el JTAG interfície, es recomana utilitzar el pinout tal com es mostra a la figura següent. S'admeten les variants de 100 mil i 50 mil d'aquest pinout, depenent del cablejat i dels adaptadors inclosos amb el kit en particular.

Figura 4-2. SAM JTAG Pinout de la capçalera

Taula 4-1. SAM JTAG Descripció del pin

| Nom | Pin |

Descripció |

| TCK | 4 | Rellotge de prova (senyal de rellotge de l'Atmel-ICE al dispositiu objectiu). |

| TMS | 2 | Selecció del mode de prova (senyal de control de l'Atmel-ICE al dispositiu objectiu). |

| TDI | 8 | Test Data In (dades transmeses des de l'Atmel-ICE al dispositiu objectiu). |

| TDO | 6 | Sortida de dades de prova (dades transmeses des del dispositiu objectiu a l'Atmel-ICE). |

| nRESET | 10 | Restablir (opcional). S'utilitza per restablir el dispositiu de destinació. Es recomana connectar aquest pin, ja que permet que l'Atmel-ICE mantingui el dispositiu objectiu en un estat de restabliment, que pot ser essencial per a la depuració en determinats escenaris. |

| VTG | 1 | Vol. objectiutage referència. Els Atmel-ICE samples the target voltage en aquest pin per alimentar correctament els convertidors de nivell. L'Atmel-ICE extreu menys d'1 mA d'aquest pin en aquest mode. |

| GND | 3, 5, 9 | Terra. Tots han d'estar connectats per garantir que l'Atmel-ICE i el dispositiu objectiu comparteixen la mateixa referència de terra. |

| CLAU | 7 | Connectat internament al pin TRST del connector AVR. Recomanat perquè no està connectat. |

![]() Consell: Recordeu incloure un condensador de desacoblament entre el pin 1 i GND.

Consell: Recordeu incloure un condensador de desacoblament entre el pin 1 i GND.

4.2.2.2 JTAG Margarida Encadenat

El JTAG La interfície permet connectar diversos dispositius a una única interfície en una configuració en cadena. Els dispositius objectiu han d'estar alimentats amb la mateixa font d'alimentaciótage, comparteixen un node de terra comú i s'han de connectar tal com es mostra a la figura següent.

Figura 4-3. JTAG Daisy Chain

Quan es connecten dispositius en cadena, s'han de tenir en compte els punts següents:

- Tots els dispositius han de compartir una terra comú, connectat a GND a la sonda Atmel-ICE

- Tots els dispositius han d'estar operant en el mateix vol objectiutage. El VTG de l'Atmel-ICE ha d'estar connectat a aquest voltage.

- TMS i TCK estan connectats en paral·lel; TDI i TDO estan connectats en sèrie

- nSRST a la sonda Atmel-ICE s'ha de connectar a RESET als dispositius si algun dels dispositius de la cadena desactiva el seu JTAG port

- "Dispositius abans" es refereix al nombre de JTAG dispositius pels quals el senyal TDI ha de passar a la cadena de margarides abans d'arribar al dispositiu objectiu. De la mateixa manera, "dispositius després" és el nombre de dispositius pels quals ha de passar el senyal després del dispositiu objectiu abans d'arribar a l'Atmel-ICE TDO

- "Els bits d'instrucció "abans" i "després" es refereixen a la suma total de tots els JTAG longituds del registre d'instruccions dels dispositius, que es connecten abans i després del dispositiu de destinació a la cadena

- La longitud total d'IR (bits d'instrucció abans + longitud d'IR del dispositiu objectiu Atmel + bits d'instrucció després) està limitada a un màxim de 256 bits. El nombre de dispositius de la cadena està limitat a 15 abans i 15 després.

![]() Consell:

Consell:

Encadenant example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Per connectar-se a l'Atmel AVR XMEGA® dispositiu, la configuració de la cadena de margarida és:

- Dispositius anteriors: 1

- Dispositius després de: 1

- Bits d'instrucció anteriors: 4 (els dispositius AVR de 8 bits tenen 4 bits IR)

- Bits d'instrucció després: 5 (els dispositius AVR de 32 bits tenen 5 bits IR)

Taula 4-2. Longituds IR dels MCU Atmel

| Tipus de dispositiu | Longitud IR |

| AVR de 8 bits | 4 bits |

| AVR de 32 bits | 5 bits |

| SAM | 4 bits |

4.2.3. Connexió a un JTAG Objectiu

L'Atmel-ICE està equipat amb dos J de 50 pins de 10 milTAG connectors. Tots dos connectors estan connectats directament elèctricament, però s'ajusten a dos pinouts diferents; l'AVR JTAG la capçalera i la capçalera ARM Cortex Debug. El connector s'ha de seleccionar en funció del pinout de la placa de destinació i no del tipus de MCU de destinació, per exempleampun dispositiu SAM muntat en una pila AVR STK600 hauria d'utilitzar la capçalera AVR.

El pinout recomanat per a l'AVR J de 10 pinsTAG connector es mostra a la figura 4-6.

A la figura 10-4 es mostra el pinout recomanat per al connector ARM Cortex Debug de 2 pins.

Connexió directa a una capçalera estàndard de 10 pins de 50 mil

Utilitzeu el cable pla de 50 pins de 10 mil (inclòs en alguns kits) per connectar-vos directament a una placa que admeti aquest tipus de capçalera. Utilitzeu el port del connector AVR de l'Atmel-ICE per a les capçaleres amb el pinout AVR i el port del connector SAM per a les capçaleres que compleixin amb el pinout de la capçalera ARM Cortex Debug.

A continuació es mostren els pinouts dels dos ports del connector de 10 pins.

Connexió a una capçalera estàndard de 10 pins de 100 mil

Utilitzeu un adaptador estàndard de 50 mil a 100 mil per connectar-se a capçaleres de 100 mil. Es pot utilitzar una placa adaptadora (inclosa en alguns kits) per a aquest propòsit o, alternativament, la placa JTAGL'adaptador ICE3 es pot utilitzar per a objectius AVR.

![]() Important:

Important:

El JTAGL'adaptador ICE3 de 100 mil no es pot utilitzar amb el port del connector SAM, ja que els pins 2 i 10 (AVR GND) de l'adaptador estan connectats.

Connexió a una capçalera personalitzada de 100 mil

Si el vostre tauler de destinació no té un dispositiu J de 10 pins compatibleTAG capçalera de 50 o 100 mil, podeu assignar un pinout personalitzat mitjançant el cable "mini-calamar" de 10 pins (inclòs en alguns kits), que dóna accés a deu endolls individuals de 100 mil.

Connexió a una capçalera de 20 pins de 100 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a objectius amb una capçalera de 20 pins de 100 mil.

Taula 4-3. Atmel-ICE JTAG Descripció del pin

| Nom | AVR pin del port | SAM pin del port | Descripció |

| TCK | 1 | 4 | Rellotge de prova (senyal de rellotge de l'Atmel-ICE al dispositiu objectiu). |

| TMS | 5 | 2 | Selecció del mode de prova (senyal de control de l'Atmel-ICE al dispositiu objectiu). |

| TDI | 9 | 8 | Test Data In (dades transmeses des de l'Atmel-ICE al dispositiu objectiu). |

| TDO | 3 | 6 | Sortida de dades de prova (dades transmeses des del dispositiu objectiu a l'Atmel-ICE). |

| nTRST | 8 | – | Prova de restabliment (opcional, només en alguns dispositius AVR). S'utilitza per restablir el JTAG Controlador TAP. |

| nSRST | 6 | 10 | Restablir (opcional). S'utilitza per restablir el dispositiu de destinació. Es recomana connectar aquest pin, ja que permet que l'Atmel-ICE mantingui el dispositiu objectiu en un estat de restabliment, que pot ser essencial per a la depuració en determinats escenaris. |

| VTG | 4 | 1 | Vol. objectiutage referència. Els Atmel-ICE samples the target voltage en aquest pin per alimentar correctament els convertidors de nivell. L'Atmel-ICE extreu menys de 3 mA d'aquest pin en mode debugWIRE i menys d'1 mA en altres modes. |

| GND | 2, 10 | 3, 5, 9 | Terra. Tots han d'estar connectats per garantir que l'Atmel-ICE i el dispositiu objectiu comparteixen la mateixa referència de terra. |

4.2.4. Interfície física SWD

La interfície ARM SWD és un subconjunt de JTAG interfície, fent ús de pins TCK i TMS. L'ARM JTAG i AVR JTAG Els connectors, però, no són compatibles amb pins, de manera que quan es dissenya una PCB d'aplicació, que utilitza un dispositiu SAM amb SWD o JTAG interfície, es recomana utilitzar el pinout ARM que es mostra a la figura següent. El port del connector SAM de l'Atmel-ICE es pot connectar directament a aquest pinout.

Figura 4-4. ARM SWD/J recomanatTAG Pinout de la capçalera

L'Atmel-ICE és capaç de transmetre la traça ITM en format UART a l'ordinador amfitrió. El rastre es captura al pin TRACE/SWO de la capçalera de 10 pins (JTAG pin TDO). Les dades s'emmagatzemen internament a l'Atmel-ICE i s'envien per la interfície HID a l'ordinador amfitrió. La velocitat màxima de dades fiables és d'uns 3 MB/s.

4.2.5. Connexió a un objectiu SWD

La interfície ARM SWD és un subconjunt de JTAG interfície, fent ús dels pins TCK i TMS, el que significa que quan es connecta a un dispositiu SWD, el J de 10 pinsTAG El connector es pot utilitzar tècnicament. L'ARM JTAG i AVR JTAG Els connectors, però, no són compatibles amb pins, de manera que això depèn de la disposició de la placa de destinació en ús. Quan utilitzeu un STK600 o una placa que utilitzeu l'AVR JTAG pinout, s'ha d'utilitzar el port del connector AVR de l'Atmel-ICE. Quan es connecta a una placa, que fa ús de l'ARM JTAG pinout, s'ha d'utilitzar el port del connector SAM de l'Atmel-ICE.

El pinout recomanat per al connector Cortex Debug de 10 pins es mostra a la figura 4-4.

Connexió a una capçalera Cortex de 10 pins de 50 mil

Utilitzeu el cable pla (inclòs en alguns kits) per connectar-vos a una capçalera Cortex estàndard de 50 mil.

Connexió a una capçalera de disseny Cortex de 10 pins i 100 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera Cortex-pinout de 100 mil.

Connexió a una capçalera SAM de 20 pins de 100 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera SAM de 20 pins de 100 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR o SAM i la placa de destinació. Es requereixen sis connexions, tal com es descriu a la taula següent.

Taula 4-4. Atmel-ICE SWD Pin Mapping

| Nom | AVR pin del port | SAM pin del port | Descripció |

| SWDC LK | 1 | 4 | Rellotge de depuració de cable sèrie. |

| SWDIO | 5 | 2 | Entrada/sortida de dades de depuració de cable sèrie. |

| SWO | 3 | 6 | Sortida de cable sèrie (opcional, no implementada en tots els dispositius). |

| nSRST | 6 | 10 | Restableix. |

| VTG | 4 | 1 | Vol. objectiutage referència. |

| GND | 2, 10 | 3, 5, 9 | Terra. |

4.2.6 Consideracions especials

ESBORRA pin

Alguns dispositius SAM inclouen un pin ERASE que s'afirma per dur a terme un esborrat complet del xip i desbloquejar els dispositius en què està configurat el bit de seguretat. Aquesta característica està acoblada al dispositiu en si, així com al controlador de flaix i no forma part del nucli ARM.

El pin ERASE NO forma part de cap capçalera de depuració i, per tant, l'Atmel-ICE no pot afirmar aquest senyal per desbloquejar un dispositiu. En aquests casos, l'usuari hauria d'esborrar manualment abans d'iniciar una sessió de depuració.

Interfícies físiques JTAG interfície

La línia RESET s'ha de connectar sempre perquè l'Atmel-ICE pugui habilitar el JTAG interfície.

Interfície SWD

La línia RESET ha d'estar connectada sempre perquè l'Atmel-ICE pugui habilitar la interfície SWD.

4.3 Dispositius AVR UC3 amb JTAG/aWire

Tots els dispositius AVR UC3 disposen de JTAG interfície de programació i depuració. A més, alguns dispositius AVR UC3 inclouen la interfície aWire amb una funcionalitat idèntica utilitzant un sol cable. Comproveu el full de dades del dispositiu per veure les interfícies compatibles amb aquest dispositiu

4.3.1 Sistema de depuració en xip Atmel AVR UC3

El sistema Atmel AVR UC3 OCD està dissenyat d'acord amb l'estàndard Nexus 2.0 (IEEE-ISTO 5001™-2003), que és un estàndard de depuració en xip obert altament flexible i potent per a microcontroladors de 32 bits. Admet les funcions següents:

- Solució de depuració compatible amb Nexus

- OCD admet qualsevol velocitat de CPU

- Sis punts d'interrupció de maquinari del comptador de programes

- Dos punts de ruptura de dades

- Els punts d'interrupció es poden configurar com a punts de vigilància

- Els punts d'interrupció del maquinari es poden combinar per donar interrupció als intervals

- Nombre il·limitat de punts d'interrupció del programa d'usuari (utilitzant BREAK)

- Traça de branques del comptador de programes en temps real, traça de dades, traça de procés (només compatible amb depuradors amb port de captura de traça paral·lel)

Per obtenir més informació sobre el sistema AVR UC3 OCD, consulteu els Manuals de referència tècnic de l'AVR32UC, situats a www.atmel.com/uc3.

4.3.2. JTAG Interfície física

El JTAG La interfície consta d'un controlador de port d'accés de prova (TAP) de 4 cables que compleix amb l'IEEE® estàndard 1149.1. L'estàndard IEEE es va desenvolupar per proporcionar una manera estàndard de la indústria de provar de manera eficient la connectivitat de la placa de circuits (Boundary Scan). Els dispositius Atmel AVR i SAM han ampliat aquesta funcionalitat per incloure suport complet de programació i depuració en xip.

Figura 4-5. JTAG Conceptes bàsics de la interfície

4.3.2.1 AVR JTAG Pinout

Quan es dissenya una PCB d'aplicació, que inclou un AVR Atmel amb el JTAG interfície, es recomana utilitzar el pinout tal com es mostra a la figura següent. S'admeten les variants de 100 mil i 50 mil d'aquest pinout, depenent del cablejat i dels adaptadors inclosos amb el kit en particular.

Figura 4-6. AVR JTAG Pinout de la capçalera

Taula 4-5. AVR JTAG Descripció del pin

| Nom | Pin |

Descripció |

| TCK | 1 | Rellotge de prova (senyal de rellotge de l'Atmel-ICE al dispositiu objectiu). |

| TMS | 5 | Selecció del mode de prova (senyal de control de l'Atmel-ICE al dispositiu objectiu). |

| TDI | 9 | Test Data In (dades transmeses des de l'Atmel-ICE al dispositiu objectiu). |

| TDO | 3 | Sortida de dades de prova (dades transmeses des del dispositiu objectiu a l'Atmel-ICE). |

| nTRST | 8 | Prova de restabliment (opcional, només en alguns dispositius AVR). S'utilitza per restablir el JTAG Controlador TAP. |

| nSRST | 6 | Restablir (opcional). S'utilitza per restablir el dispositiu de destinació. Es recomana connectar aquest pin, ja que permet que l'Atmel-ICE mantingui el dispositiu objectiu en un estat de restabliment, que pot ser essencial per a la depuració en determinats escenaris. |

| VTG | 4 | Vol. objectiutage referència. Els Atmel-ICE samples the target voltage en aquest pin per alimentar correctament els convertidors de nivell. L'Atmel-ICE extreu menys de 3 mA d'aquest pin en mode debugWIRE i menys d'1 mA en altres modes. |

| GND | 2, 10 | Terra. Tots dos s'han de connectar per garantir que l'Atmel-ICE i el dispositiu objectiu comparteixen la mateixa referència de terra. |

![]() Consell: Recordeu incloure un condensador de desacoblament entre el pin 4 i GND.

Consell: Recordeu incloure un condensador de desacoblament entre el pin 4 i GND.

4.3.2.2 JTAG Margarida Encadenat

El JTAG La interfície permet connectar diversos dispositius a una única interfície en una configuració en cadena. Els dispositius objectiu han d'estar alimentats amb la mateixa font d'alimentaciótage, comparteixen un node de terra comú i s'han de connectar tal com es mostra a la figura següent.

Figura 4-7. JTAG Daisy Chain

Quan es connecten dispositius en cadena, s'han de tenir en compte els punts següents:

- Tots els dispositius han de compartir una terra comú, connectat a GND a la sonda Atmel-ICE

- Tots els dispositius han d'estar operant en el mateix vol objectiutage. El VTG de l'Atmel-ICE ha d'estar connectat a aquest voltage.

- TMS i TCK estan connectats en paral·lel; TDI i TDO estan connectats en una cadena en sèrie.

- nSRST a la sonda Atmel-ICE s'ha de connectar a RESET als dispositius si algun dels dispositius de la cadena desactiva el seu JTAG port

- "Dispositius abans" es refereix al nombre de JTAG dispositius pels quals el senyal TDI ha de passar a la cadena de margarides abans d'arribar al dispositiu objectiu. De la mateixa manera, "dispositius després" és el nombre de dispositius pels quals ha de passar el senyal després del dispositiu objectiu abans d'arribar a l'Atmel-ICE TDO

- "Els bits d'instrucció "abans" i "després" es refereixen a la suma total de tots els JTAG longituds del registre d'instruccions dels dispositius, que es connecten abans i després del dispositiu de destinació a la cadena

- La longitud total d'IR (bits d'instrucció abans + longitud d'IR del dispositiu objectiu Atmel + bits d'instrucció després) està limitada a un màxim de 256 bits. El nombre de dispositius de la cadena està limitat a 15 abans i 15 després.

Consell:

Encadenant example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Per connectar-se a l'Atmel AVR XMEGA® dispositiu, la configuració de la cadena de margarida és:

- Dispositius anteriors: 1

- Dispositius després de: 1

- Bits d'instrucció anteriors: 4 (els dispositius AVR de 8 bits tenen 4 bits IR)

- Bits d'instrucció després: 5 (els dispositius AVR de 32 bits tenen 5 bits IR)

Taula 4-6. Longituds IR d'Atmel MCUS

| Tipus de dispositiu | Longitud IR |

| AVR de 8 bits | 4 bits |

| AVR de 32 bits | 5 bits |

| SAM | 4 bits |

4.3.3.Connexió a un JTAG Objectiu

L'Atmel-ICE està equipat amb dos J de 50 pins de 10 milTAG connectors. Tots dos connectors estan connectats directament elèctricament, però s'ajusten a dos pinouts diferents; l'AVR JTAG la capçalera i la capçalera ARM Cortex Debug. El connector s'ha de seleccionar en funció del pinout de la placa de destinació i no del tipus de MCU de destinació, per exempleampun dispositiu SAM muntat en una pila AVR STK600 hauria d'utilitzar la capçalera AVR.

El pinout recomanat per a l'AVR J de 10 pinsTAG connector es mostra a la figura 4-6.

A la figura 10-4 es mostra el pinout recomanat per al connector ARM Cortex Debug de 2 pins.

Connexió directa a una capçalera estàndard de 10 pins de 50 mil

Utilitzeu el cable pla de 50 pins de 10 mil (inclòs en alguns kits) per connectar-vos directament a una placa que admeti aquest tipus de capçalera. Utilitzeu el port del connector AVR de l'Atmel-ICE per a les capçaleres amb el pinout AVR i el port del connector SAM per a les capçaleres que compleixin amb el pinout de la capçalera ARM Cortex Debug.

A continuació es mostren els pinouts dels dos ports del connector de 10 pins.

Connexió a una capçalera estàndard de 10 pins de 100 mil

Utilitzeu un adaptador estàndard de 50 mil a 100 mil per connectar-se a capçaleres de 100 mil. Es pot utilitzar una placa adaptadora (inclosa en alguns kits) per a aquest propòsit o, alternativament, la placa JTAGL'adaptador ICE3 es pot utilitzar per a objectius AVR.

![]() Important:

Important:

El JTAGL'adaptador ICE3 de 100 mil no es pot utilitzar amb el port del connector SAM, ja que els pins 2 i 10 (AVR GND) de l'adaptador estan connectats.

Connexió a una capçalera personalitzada de 100 mil

Si el vostre tauler de destinació no té un dispositiu J de 10 pins compatibleTAG capçalera de 50 o 100 mil, podeu assignar un pinout personalitzat mitjançant el cable "mini-calamar" de 10 pins (inclòs en alguns kits), que dóna accés a deu endolls individuals de 100 mil.

Connexió a una capçalera de 20 pins de 100 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a objectius amb una capçalera de 20 pins de 100 mil.

Taula 4-7. Atmel-ICE JTAG Descripció del pin

|

Nom |

Pin del port AVR | Pin del port SAM |

Descripció |

| TCK | 1 | 4 | Rellotge de prova (senyal de rellotge de l'Atmel-ICE al dispositiu objectiu). |

| TMS | 5 | 2 | Selecció del mode de prova (senyal de control de l'Atmel-ICE al dispositiu objectiu). |

| TDI | 9 | 8 | Test Data In (dades transmeses des de l'Atmel-ICE al dispositiu objectiu). |

| TDO | 3 | 6 | Sortida de dades de prova (dades transmeses des del dispositiu objectiu a l'Atmel-ICE). |

| nTRST | 8 | – | Prova de restabliment (opcional, només en alguns dispositius AVR). S'utilitza per restablir el JTAG Controlador TAP. |

| nSRST | 6 | 10 | Restablir (opcional). S'utilitza per restablir el dispositiu de destinació. Es recomana connectar aquest pin, ja que permet que l'Atmel-ICE mantingui el dispositiu objectiu en un estat de restabliment, que pot ser essencial per a la depuració en determinats escenaris. |

| VTG | 4 | 1 | Vol. objectiutage referència. Els Atmel-ICE samples the target voltage en aquest pin per alimentar correctament els convertidors de nivell. L'Atmel-ICE extreu menys de 3 mA d'aquest pin en mode debugWIRE i menys d'1 mA en altres modes. |

| GND | 2, 10 | 3, 5, 9 | Terra. Tots han d'estar connectats per garantir que l'Atmel-ICE i el dispositiu objectiu comparteixen la mateixa referència de terra. |

4.3.4 a Interfície física de cable

La interfície aWire utilitza el cable RESET del dispositiu AVR per permetre les funcions de programació i depuració. L'Atmel-ICE transmet una seqüència d'habilitació especial, que desactiva la funcionalitat de RESET per defecte del pin. Quan es dissenya una PCB d'aplicació, que inclou un AVR Atmel amb la interfície aWire, es recomana utilitzar el pinout tal com es mostra a la figura 4. -8. S'admeten les variants de 100 mil i 50 mil d'aquest pinout, depenent del cablejat i dels adaptadors inclosos amb el kit en particular.

Figura 4-8. Pinout de la capçalera aWire

![]() Consell:

Consell:

Com que aWire és una interfície semidúplex, es recomana una resistència pull-up a la línia RESET de l'ordre de 47 kΩ per evitar la detecció de bits d'inici fals en canviar de direcció.

La interfície aWire es pot utilitzar tant com a interfície de programació com de depuració. Totes les característiques del sistema OCD disponibles a través del dispositiu JTAG També es pot accedir a la interfície mitjançant aWire.

4.3.5 Connexió a un objectiu aWire

La interfície aWire només requereix una línia de dades a més de VCC i GND. A l'objectiu, aquesta línia és la línia nRESET, tot i que el depurador utilitza el JTAG Línia TDO com a línia de dades.

A la figura 6-4 es mostra el pinout recomanat per al connector aWire de 8 pins.

Connexió a una capçalera aWire de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera estàndard de 100 mil aWire.

Connexió a una capçalera aWire de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera aWire estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Es requereixen tres connexions, tal com es descriu a la taula següent.

Taula 4-8. Atmel-ICE aWire Pin Mapping

| Pins del port Atmel-ICE AVR | Pins objectiu | Mini-pin de calamar |

a Pintació del cable |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DADES | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (no connectat) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.3.6. Consideracions especials

JTAG interfície

En alguns dispositius Atmel AVR UC3, el JTAG port no està habilitat per defecte. Quan s'utilitzen aquests dispositius és essencial connectar la línia RESET perquè l'Atmel-ICE pugui habilitar el JTAG interfície.

a Interfície de cable

La velocitat en baudis de les comunicacions aWire depèn de la freqüència del rellotge del sistema, ja que les dades s'han de sincronitzar entre aquests dos dominis. L'Atmel-ICE detectarà automàticament que el rellotge del sistema s'ha reduït i tornarà a calibrar la seva velocitat de transmissió en conseqüència. El calibratge automàtic només funciona fins a una freqüència de rellotge del sistema de 8 kHz. Canviar a un rellotge del sistema més baix durant una sessió de depuració pot provocar que es perdi el contacte amb l'objectiu.

Si cal, es pot restringir la velocitat en baudis aWire configurant el paràmetre de rellotge aWire. La detecció automàtica encara funcionarà, però s'imposarà un valor màxim als resultats.

Qualsevol condensador estabilitzador connectat al pin RESET s'ha de desconnectar quan utilitzeu aWire, ja que interferirà amb el correcte funcionament de la interfície. Es recomana un pullup extern feble (10 kΩ o més) en aquesta línia.

Apagueu el mode de repòs

Alguns dispositius AVR UC3 tenen un regulador intern que es pot utilitzar en mode d'alimentació de 3.3 V amb línies d'E/S regulades d'1.8 V. Això vol dir que el regulador intern alimenta tant el nucli com la majoria de les E/S. Només Atmel AVR ONE! el depurador admet la depuració mentre s'utilitza els modes de repòs on aquest regulador està desactivat.

4.3.7. Ús EVTI / EVTO

Els pins EVTI i EVTO no són accessibles a l'Atmel-ICE. Tanmateix, encara es poden utilitzar juntament amb altres equips externs.

EVTI es pot utilitzar per als propòsits següents:

- L'objectiu es pot forçar a aturar l'execució en resposta a un esdeveniment extern. Si els bits de control d'entrada d'esdeveniments (EIC) del registre DC s'escriuen a 0b01, la transició d'alt a baix al pin EVTI generarà una condició de punt d'interrupció. L'EVTI ha de romandre baix durant un cicle de rellotge de la CPU per garantir que un punt d'interrupció sigui. El bit de punt d'interrupció extern (EXB) a DS s'estableix quan això succeeix.

- Generació de missatges de sincronització de traça. No utilitzat per l'Atmel-ICE.

EVTO es pot utilitzar per als propòsits següents:

- Indicant que la CPU ha entrat a la depuració Si estableixen els bits EOS a DC a 0b01, el pin EVTO es baixa durant un cicle de rellotge de la CPU quan el dispositiu de destinació entra en mode de depuració. Aquest senyal es pot utilitzar com a font de disparador per a un oscil·loscopi extern.

- Indica que la CPU ha assolit un punt d'interrupció o un punt de vigilància. En establir el bit EOC en un registre de control de punt d'interrupció/punt de vigilància corresponent, el punt d'interrupció o l'estat del punt de vigilància s'indica al pin EVTO. Els bits EOS a DC s'han d'establir a 0xb10 per habilitar aquesta funció. El pin EVTO es pot connectar a un oscil·loscopi extern per examinar el punt de vigilància

- Generació de senyals de temporització de traça. No utilitzat per l'Atmel-ICE.

4.4 Dispositius tinyAVR, megaAVR i XMEGA

Els dispositius AVR inclouen diverses interfícies de programació i depuració. Comproveu el full de dades del dispositiu per veure les interfícies compatibles amb aquest dispositiu.

- Alguns petits AVR® els dispositius tenen un TPI El TPI només es pot utilitzar per programar el dispositiu, i aquests dispositius no tenen cap capacitat de depuració en xip.

- Alguns dispositius tinyAVR i alguns dispositius megaAVR tenen la interfície debugWIRE, que es connecta a un sistema de depuració en xip conegut com tinyOCD. Tots els dispositius amb debugWIRE també tenen la interfície SPI per al sistema

- Alguns dispositius megaAVR tenen un JTAG interfície per programar i depurar, amb un sistema de depuració en xip també conegut com a Tots els dispositius amb JTAG També inclou la interfície SPI com a interfície alternativa per a la programació del sistema.

- Tots els dispositius AVR XMEGA tenen la interfície PDI per a la programació i alguns dispositius AVR XMEGA també tenen una JTAG interfície amb idèntica funcionalitat.

- Els nous dispositius tinyAVR tenen una interfície UPDI, que s'utilitza per programar i depurar

Taula 4-9. Resum de programació i depuració d'interfícies

|

|

UPDI | TPI | SPI | debugWIR E | JTAG | PDI | aWire |

SWD |

| petitAVR | Nous dispositius | Alguns dispositius | Alguns dispositius | Alguns dispositius | ||||

| megaAV R | Tots els dispositius | Alguns dispositius | Alguns dispositius | |||||

| AVR XMEGA | Alguns dispositius | Tots els dispositius | ||||||

| AVR UC | Tots els dispositius | Alguns dispositius | ||||||

| SAM | Alguns dispositius | Tots els dispositius |

4.4.1. JTAG Interfície física

El JTAG La interfície consta d'un controlador de port d'accés de prova (TAP) de 4 cables que compleix amb l'IEEE® estàndard 1149.1. L'estàndard IEEE es va desenvolupar per proporcionar una manera estàndard de la indústria de provar de manera eficient la connectivitat de la placa de circuits (Boundary Scan). Els dispositius Atmel AVR i SAM han ampliat aquesta funcionalitat per incloure suport complet de programació i depuració en xip.

Figura 4-9. JTAG Conceptes bàsics de la interfície 4.4.2. Connexió a un JTAG Objectiu

4.4.2. Connexió a un JTAG Objectiu

L'Atmel-ICE està equipat amb dos J de 50 pins de 10 milTAG connectors. Tots dos connectors estan connectats directament elèctricament, però s'ajusten a dos pinouts diferents; l'AVR JTAG la capçalera i la capçalera ARM Cortex Debug. El connector s'ha de seleccionar en funció del pinout de la placa de destinació i no del tipus de MCU de destinació, per exempleampun dispositiu SAM muntat en una pila AVR STK600 hauria d'utilitzar la capçalera AVR.

El pinout recomanat per a l'AVR J de 10 pinsTAG connector es mostra a la figura 4-6.

A la figura 10-4 es mostra el pinout recomanat per al connector ARM Cortex Debug de 2 pins.

Connexió directa a una capçalera estàndard de 10 pins de 50 mil

Utilitzeu el cable pla de 50 pins de 10 mil (inclòs en alguns kits) per connectar-vos directament a una placa que admeti aquest tipus de capçalera. Utilitzeu el port del connector AVR de l'Atmel-ICE per a les capçaleres amb el pinout AVR i el port del connector SAM per a les capçaleres que compleixin amb el pinout de la capçalera ARM Cortex Debug.

A continuació es mostren els pinouts dels dos ports del connector de 10 pins.

Connexió a una capçalera estàndard de 10 pins de 100 mil

Utilitzeu un adaptador estàndard de 50 mil a 100 mil per connectar-se a capçaleres de 100 mil. Es pot utilitzar una placa adaptadora (inclosa en alguns kits) per a aquest propòsit o, alternativament, la placa JTAGL'adaptador ICE3 es pot utilitzar per a objectius AVR.

![]() Important:

Important:

El JTAGL'adaptador ICE3 de 100 mil no es pot utilitzar amb el port del connector SAM, ja que els pins 2 i 10 (AVR GND) de l'adaptador estan connectats.

Connexió a una capçalera personalitzada de 100 mil

Si el vostre tauler de destinació no té un dispositiu J de 10 pins compatibleTAG capçalera de 50 o 100 mil, podeu assignar un pinout personalitzat mitjançant el cable "mini-calamar" de 10 pins (inclòs en alguns kits), que dóna accés a deu endolls individuals de 100 mil.

Connexió a una capçalera de 20 pins de 100 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a objectius amb una capçalera de 20 pins de 100 mil.

Taula 4-10. Atmel-ICE JTAG Descripció del pin

| Nom | AVR pin del port | SAM pin del port | Descripció |

| TCK | 1 | 4 | Rellotge de prova (senyal de rellotge de l'Atmel-ICE al dispositiu objectiu). |

| TMS | 5 | 2 | Selecció del mode de prova (senyal de control de l'Atmel-ICE al dispositiu objectiu). |

| TDI | 9 | 8 | Test Data In (dades transmeses des de l'Atmel-ICE al dispositiu objectiu). |

| TDO | 3 | 6 | Sortida de dades de prova (dades transmeses des del dispositiu objectiu a l'Atmel-ICE). |

| nTRST | 8 | – | Prova de restabliment (opcional, només en alguns dispositius AVR). S'utilitza per restablir el JTAG Controlador TAP. |

| nSRST | 6 | 10 | Restablir (opcional). S'utilitza per restablir el dispositiu de destinació. Es recomana connectar aquest pin, ja que permet que l'Atmel-ICE mantingui el dispositiu objectiu en un estat de restabliment, que pot ser essencial per a la depuració en determinats escenaris. |

| VTG | 4 | 1 | Vol. objectiutage referència. Els Atmel-ICE samples the target voltage en aquest pin per alimentar correctament els convertidors de nivell. L'Atmel-ICE extreu menys de 3 mA d'aquest pin en mode debugWIRE i menys d'1 mA en altres modes. |

| GND | 2, 10 | 3, 5, 9 | Terra. Tots han d'estar connectats per garantir que l'Atmel-ICE i el dispositiu objectiu comparteixen la mateixa referència de terra. |

4.4.3.Interfície física SPI

La programació en el sistema utilitza l'SPI (Interfície perifèrica sèrie) interna de l'Atmel AVR objectiu per descarregar codi a les memòries flash i EEPROM. No és una interfície de depuració. Quan es dissenya una PCB d'aplicació, que inclou un AVR amb la interfície SPI, s'ha d'utilitzar el pinout tal com es mostra a la figura següent.

Figura 4-10. Pinout de la capçalera SPI 4.4.4. Connexió a un SPI Target

4.4.4. Connexió a un SPI Target

El pinout recomanat per al connector SPI de 6 pins es mostra a la figura 4-10.

Connexió a una capçalera SPI de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera SPI estàndard de 100 mil.

Connexió a una capçalera SPI de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera SPI estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Es requereixen sis connexions, tal com es descriu a la taula següent.

![]() Important:

Important:

La interfície SPI es desactiva efectivament quan es programa el fusible d'habilitació debugWIRE (DWEN), fins i tot si també es programa el fusible SPIEN. Per tornar a habilitar la interfície SPI, s'ha d'emetre l'ordre "desactivar debugWIRE" mentre es troba en una sessió de depuració debugWIRE. Desactivar debugWIRE d'aquesta manera requereix que el fusible SPIEN ja estigui programat. Si Atmel Studio no desactiva debugWIRE, és probable perquè el fusible SPIEN NO està programat. Si aquest és el cas, cal utilitzar un alt voltage interfície de programació per programar el fusible SPIEN.

![]() Informació:

Informació:

La interfície SPI sovint es coneix com "ISP", ja que va ser la primera interfície de programació del sistema dels productes Atmel AVR. Altres interfícies ja estan disponibles per a la programació del sistema.

Taula 4-11. Atmel-ICE SPI Pin Mapping

| Pins del port Atmel-ICE AVR | Pins objectiu | Mini-pin de calamar |

Pinout SPI |

| Pin 1 (TCK) | SCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | MISO | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | / RESET | 6 | 5 |

| Pin 7 (no connectat) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | Extensió MOSI | 9 | 4 |

| Pin 10 (GND) | 0 |

4.4.5. PDI

La interfície de programa i depuració (PDI) és una interfície propietat d'Atmel per a la programació externa i la depuració en xip d'un dispositiu. PDI Physical és una interfície de 2 pins que proporciona una comunicació síncrona semidúplex bidireccional amb el dispositiu objectiu.

Quan es dissenya una PCB d'aplicació, que inclou un AVR Atmel amb la interfície PDI, s'ha d'utilitzar el pinout que es mostra a la figura següent. Un dels adaptadors de 6 pins proporcionats amb el kit Atmel-ICE es pot utilitzar per connectar la sonda Atmel-ICE a la PCB de l'aplicació.

Figura 4-11. Pinout de la capçalera PDI 4.4.6.Connexió a un objectiu PDI

4.4.6.Connexió a un objectiu PDI

El pinout recomanat per al connector PDI de 6 pins es mostra a la figura 4-11.

Connexió a una capçalera PDI de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera PDI estàndard de 100 mil.

Connexió a una capçalera PDI de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera PDI estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Es requereixen quatre connexions, tal com es descriu a la taula següent.

![]() Important:

Important:

El pinout requerit és diferent del de JTAGICE mkII JTAG sonda, on PDI_DATA està connectat al pin 9. L'Atmel-ICE és compatible amb el pinout utilitzat per l'Atmel-ICE, JTAGICE3, AVR ONE! i AVR Dragon™ productes.

Taula 4-12. Atmel-ICE PDI Pin Mapping

|

Pin del port Atmel-ICE AVR |

Pins objectiu | Mini-pin de calamar |

Pinout Atmel STK600 PDI |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | PDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (no connectat) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.7. Interfície física UPDI

La interfície de depuració i programa unificada (UPDI) és una interfície propietat d'Atmel per a la programació externa i la depuració en xip d'un dispositiu. És un successor de la interfície física de 2 fils PDI, que es troba a tots els dispositius AVR XMEGA. UPDI és una interfície d'un sol cable que proporciona una comunicació asíncrona semidúplex bidireccional amb el dispositiu de destinació amb finalitats de programació i depuració.

Quan es dissenya una PCB d'aplicació, que inclou un AVR Atmel amb la interfície UPDI, s'ha d'utilitzar el pinout que es mostra a continuació. Un dels adaptadors de 6 pins proporcionats amb el kit Atmel-ICE es pot utilitzar per connectar la sonda Atmel-ICE a la PCB de l'aplicació.

Figura 4-12. Pinout de la capçalera UPDI 4.4.7.1 UPDI i /RESET

4.4.7.1 UPDI i /RESET

La interfície d'un cable UPDI pot ser un pin dedicat o un pin compartit, depenent del dispositiu AVR objectiu. Consulteu el full de dades del dispositiu per obtenir més informació.

Quan la interfície UPDI està en un pin compartit, el pin es pot configurar per ser UPDI, /RESET o GPIO configurant els fusibles RSTPINCFG[1:0].

Els fusibles RSTPINCFG[1:0] tenen les configuracions següents, tal com es descriu al full de dades. Aquí s'exposen les implicacions pràctiques de cada elecció.

Taula 4-13. RSTPINCFG[1:0] Configuració del fusible

| RSTPINCFG[1:0] | Configuració |

Ús |

| 00 | GPIO | Pin d'E/S d'ús general. Per accedir a UPDI, cal aplicar un pols de 12 V a aquest pin. No hi ha cap font de restabliment externa disponible. |

| 01 | UPDI | Pin de programació i depuració dedicada. No hi ha cap font de restabliment externa disponible. |

| 10 | Restableix | Restableix l'entrada del senyal. Per accedir a UPDI, cal aplicar un pols de 12 V a aquest pin. |

| 11 | Reservat | NA |

Nota: Els dispositius AVR més antics tenen una interfície de programació, coneguda com "High-Voltage Programming” (existeixen variants en sèrie i en paral·lel.) En general, aquesta interfície requereix que s'apliquin 12V al pin /RESET durant la sessió de programació. La interfície UPDI és una interfície completament diferent. El pin UPDI és principalment un pin de programació i depuració, que es pot fusionar per tenir una funció alternativa (/RESET o GPIO). Si es selecciona la funció alternativa, cal un pols de 12 V en aquest pin per reactivar la funcionalitat UPDI.

Nota: Si un disseny requereix compartir el senyal UPDI a causa de restriccions de pin, s'han de prendre mesures per garantir que el dispositiu es pugui programar. Per garantir que el senyal UPDI pugui funcionar correctament, així com per evitar danys als components externs del pols de 12 V, es recomana desconnectar qualsevol component d'aquest pin quan intenteu depurar o programar el dispositiu. Això es pot fer mitjançant una resistència de 0Ω, que es munta per defecte i s'elimina o substitueix per una capçalera de pin durant la depuració. Aquesta configuració significa efectivament que la programació s'ha de fer abans de muntar el dispositiu.

![]() Important: L'Atmel-ICE no admet 12V a la línia UPDI. En altres paraules, si el pin UPDI s'ha configurat com a GPIO o RESET, l'Atmel-ICE no podrà habilitar la interfície UPDI.

Important: L'Atmel-ICE no admet 12V a la línia UPDI. En altres paraules, si el pin UPDI s'ha configurat com a GPIO o RESET, l'Atmel-ICE no podrà habilitar la interfície UPDI.

4.4.8.Connexió a una destinació UPDI

El pinout recomanat per al connector UPDI de 6 pins es mostra a la figura 4-12.

Connexió a una capçalera UPDI de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera UPDI estàndard de 100 mil.

Connexió a una capçalera UPDI de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera UPDI estàndard de 50 mil.

Connexió a una capçalera personalitzada de 100 mil

El cable mini-calamar de 10 pins s'ha d'utilitzar per connectar-se entre el port del connector Atmel-ICE AVR i la placa de destinació. Es requereixen tres connexions, tal com es descriu a la taula següent.

Taula 4-14. Atmel-ICE UPDI Pin Mapping

| Pin del port Atmel-ICE AVR | Pins objectiu | Mini-pin de calamar |

Pinout Atmel STK600 UPDI |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | [/RESET el sentit] | 6 | 5 |

| Pin 7 (no connectat) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.9 Interfície física TPI

TPI és una interfície només de programació per a alguns dispositius AVR ATtiny. No és una interfície de depuració i aquests dispositius no tenen capacitat d'OCD. Quan es dissenya una PCB d'aplicació que inclogui un AVR amb la interfície TPI, s'ha d'utilitzar el pinout que es mostra a la figura següent.

Figura 4-13. Pinout de la capçalera TPI 4.4.10.Connexió a un TPI Target

4.4.10.Connexió a un TPI Target

El pinout recomanat per al connector TPI de 6 pins es mostra a la figura 4-13.

Connexió a una capçalera TPI de 6 pins de 100 mil

Utilitzeu l'aixeta de 6 pins de 100 mil al cable pla (inclòs en alguns kits) per connectar-vos a una capçalera TPI estàndard de 100 mil.

Connexió a una capçalera TPI de 6 pins de 50 mil

Utilitzeu la placa adaptadora (inclosa en alguns kits) per connectar-vos a una capçalera TPI estàndard de 50 mil.