Programmatori di debug ICE

Programmatori di debug ICE

Guida per l'utente Programmatori e debugger

Programmatori e debugger

Atmel-ICE

GUIDA PER L'UTENTE

Il debugger Atmel-ICE

Atmel-ICE è un potente strumento di sviluppo per il debug e la programmazione di microcontrollori Atmel®SAM e Atmel AVR basati su ARM® Cortex®-M con funzionalità di debug su chip®.

Supporta:

- Programmazione e debug on-chip di tutti i microcontrollori Atmel AVR a 32 bit sia su JTAG e interfacce aWire

- Programmazione e debug on-chip di tutti i dispositivi della famiglia Atmel AVR XMEGA® sia su JTAG e interfacce PDI a 2 fili

- Programmazione (GTAG, SPI, UPDI) e il debug di tutti i microcontrollori Atmel AVR a 8 bit con supporto OCD su JTAG, interfacce debugWIRE o UPDI

- Programmazione e debug di tutti i microcontrollori basati su Atmel SAM ARM Cortex-M sia su SWD che su JTAG interfacce

- Programmazione (TPI) di tutti i microcontrollori Atmel tinyAVR® a 8 bit con supporto per questa interfaccia

Consulta l'elenco dei dispositivi supportati nella Guida dell'utente di Atmel Studio per un elenco completo dei dispositivi e delle interfacce supportati da questa versione del firmware.

Introduzione

1.1. Introduzione all'Atmel-ICE

Atmel-ICE è un potente strumento di sviluppo per il debug e la programmazione di microcontrollori Atmel SAM e Atmel AVR basati su ARM Cortex-M con funzionalità di debug su chip.

Supporta:

- Programmazione e debug on-chip di tutti i microcontrollori Atmel AVR UC3 sia su JTAG e interfacce aWire

- Programmazione e debug on-chip di tutti i dispositivi della famiglia AVR XMEGA sia su JTAG e interfacce PDI 2wire

- Programmazione (GTAG e SPI) e il debug di tutti i microcontrollori AVR a 8 bit con supporto OCD sia su JTAG o interfacce debugWIRE

- Programmazione e debug di tutti i microcontrollori basati su Atmel SAM ARM Cortex-M sia su SWD che su JTAG interfacce

- Programmazione (TPI) di tutti i microcontrollori Atmel tinyAVR a 8 bit con supporto per questa interfaccia

1.2. Caratteristiche Atmel-ICE

- Completamente compatibile con Atmel Studio

- Supporta la programmazione e il debug di tutti i microcontrollori Atmel AVR UC3 a 32 bit

- Supporta la programmazione e il debug di tutti i dispositivi AVR XMEGA a 8 bit

- Supporta la programmazione e il debug di tutti i dispositivi Atmel megaAVR® e tinyAVR a 8 bit con OCD

- Supporta la programmazione e il debug di tutti i microcontrollori basati su SAM ARM Cortex-M

- Target operativo voltage range da 1.62V a 5.5V

- Assorbe meno di 3 mA dal target VTref quando si utilizza l'interfaccia debugWIRE e meno di 1 mA per tutte le altre interfacce

- Supporta JTAG frequenze di clock da 32kHz a 7.5MHz

- Supporta frequenze di clock PDI da 32 kHz a 7.5 MHz

- Supporta velocità di trasmissione debugWIRE da 4 kbit/s a 0.5 Mbit/s

- Supporta velocità di trasmissione aWire da 7.5 kbit/s a 7 Mbit/s

- Supporta frequenze di clock SPI da 8kHz a 5MHz

- Supporta velocità di trasmissione UPDI fino a 750 kbit/s

- Supporta frequenze di clock SWD da 32kHz a 10MHz

- Interfaccia host USB 2.0 ad alta velocità

- Acquisizione di tracce seriali ITM fino a 3 MB/s

- Supporta le interfacce DGI SPI e USART quando non si esegue il debug o la programmazione

- Supporta J a 10 pin da 50 milTAG connettore con pinout AVR e Cortex. Il cavo della sonda standard supporta le intestazioni AVR a 6 pin ISP/PDI/TPI da 100 mil e 10 pin da 50 mil. È disponibile un adattatore per supportare intestazioni da 6 mil a 50 pin, 10 mil a 100 pin e 20 mil a 100 pin. Sono disponibili diverse opzioni di kit con diversi cavi e adattatori.

1.3. Requisiti di sistema

L'unità Atmel-ICE richiede che sul computer sia installato un ambiente di debug front-end Atmel Studio versione 6.2 o successiva.

L'Atmel-ICE deve essere collegato al computer host utilizzando il cavo USB fornito o un cavo Micro-USB certificato.

Iniziare con l'Atmel-ICE

2.1. Contenuto completo del kit

Il kit completo Atmel-ICE contiene questi elementi:

- Unità Atmel-ICE

- Cavo USB (1.8 m, ad alta velocità, Micro-B)

- Scheda adattatore contenente adattatori AVR da 50 mil, AVR/SAM da 100 mil e SAM da 100 mil a 20 pin

- Cavo piatto IDC con connettore a 10 pin da 50 mil e connettore a 6 pin da 100 mil

- Cavo mini squid da 50 mil a 10 pin con 10 prese da 100 mil

Figura 2-1. Contenuto del kit completo Atmel-ICE 2.2. Contenuto del kit di base

2.2. Contenuto del kit di base

Il kit base Atmel-ICE contiene questi elementi:

- Unità Atmel-ICE

- Cavo USB (1.8 m, ad alta velocità, Micro-B)

- Cavo piatto IDC con connettore a 10 pin da 50 mil e connettore a 6 pin da 100 mil

Figura 2-2. Contenuto del kit di base Atmel-ICE 2.3. Contenuto del kit PCBA

2.3. Contenuto del kit PCBA

Il kit Atmel-ICE PCBA contiene questi elementi:

- Unità Atmel-ICE senza incapsulamento plastico

Figura 2-3. Contenuto del kit PCBA Atmel-ICE 2.4. Kit ricambi

2.4. Kit ricambi

Sono disponibili i seguenti kit di ricambi:

- Kit adattatore

- Kit cavi

Figura 2-4. Contenuto del kit adattatore Atmel-ICE 2.5. Kit finitoview

2.5. Kit finitoview

Le opzioni del kit Atmel-ICE sono mostrate schematicamente qui:

Figura 2-6. Kit finito Atmel-ICEview 2.6. Assemblare l'Atmel-ICE

2.6. Assemblare l'Atmel-ICE

L'unità Atmel-ICE viene spedita senza cavi collegati. Nel kit completo sono fornite due opzioni di cavo:

- Cavo piatto IDC a 50 pin da 10 mil con ISP a 6 pin e connettori a 10 pin

- Cavo mini-squid da 50 mil a 10 pin con 10 prese da 100 mil

Figura 2-7. Cavi Atmel-ICE Per la maggior parte degli scopi, è possibile utilizzare il cavo piatto IDC a 50 pin da 10 mil, collegandosi in modo nativo ai suoi connettori a 10 o 6 pin o collegandosi tramite la scheda dell'adattatore. Tre adattatori sono forniti su un piccolo PCBA. Sono inclusi i seguenti adattatori:

Per la maggior parte degli scopi, è possibile utilizzare il cavo piatto IDC a 50 pin da 10 mil, collegandosi in modo nativo ai suoi connettori a 10 o 6 pin o collegandosi tramite la scheda dell'adattatore. Tre adattatori sono forniti su un piccolo PCBA. Sono inclusi i seguenti adattatori:

- J da 100 mil a 10 pinTAGadattatore /SWD

- SAM J da 100 mil a 20 pinTAGadattatore /SWD

- Adattatore SPI/debugWIRE/PDI/aWire da 50 mil a 6 pin

Figura 2-8. Adattatori Atmel-ICE Nota:

Nota:

Una J da 50 milTAG l'adattatore non è stato fornito: questo perché il cavo IDC a 50 pin da 10 mil può essere utilizzato per connettersi direttamente a un J da 50 milTAG intestazione. Per il numero di parte del componente utilizzato per il connettore da 50 mil a 10 pin, vedere i numeri di parte dei connettori di destinazione Atmel-ICE.

L'intestazione ISP/PDI a 6 pin è inclusa come parte del cavo IDC a 10 pin. Questa terminazione può essere interrotta se non è richiesta.

Per assemblare Atmel-ICE nella sua configurazione predefinita, collegare il cavo IDC da 10 mil a 50 pin all'unità come mostrato di seguito. Accertarsi di orientare il cavo in modo che il filo rosso (pin 1) sul cavo sia allineato con l'indicatore triangolare sulla cintura blu dell'involucro. Il cavo dovrebbe collegarsi verso l'alto dall'unità. Assicurati di connetterti alla porta corrispondente al pinout del tuo target: AVR o SAM.

Figura 2-9. Connessione via cavo Atmel-ICE Figura 2-10. Connessione sonda Atmel-ICE AVR

Figura 2-10. Connessione sonda Atmel-ICE AVR Figura 2-11. Collegamento sonda Atmel-ICE SAM

Figura 2-11. Collegamento sonda Atmel-ICE SAM 2.7. Apertura dell'Atmel-ICE

2.7. Apertura dell'Atmel-ICE

Nota:

Per il normale funzionamento, l'unità Atmel-ICE non deve essere aperta. L'apertura dell'unità avviene a proprio rischio.

Devono essere prese precauzioni antistatiche.

L'involucro Atmel-ICE è costituito da tre componenti in plastica separati - coperchio superiore, coperchio inferiore e cintura blu - che vengono fissati insieme durante l'assemblaggio. Per aprire l'unità, basta inserire un grande cacciavite piatto nelle aperture della cintura blu, applicare una certa pressione verso l'interno e ruotare delicatamente. Ripeti il processo sugli altri fori degli snapper e il coperchio superiore si staccherà.

Figura 2-12. Apertura dell'Atmel-ICE (1) Figura 2-13. Apertura dell'Atmel-ICE (2)

Figura 2-13. Apertura dell'Atmel-ICE (2) Figura 2-14. Apertura dell'Atmel-ICE(3)

Figura 2-14. Apertura dell'Atmel-ICE(3) Per richiudere l'unità, è sufficiente allineare correttamente i coperchi superiore e inferiore e premere saldamente insieme.

Per richiudere l'unità, è sufficiente allineare correttamente i coperchi superiore e inferiore e premere saldamente insieme.

2.8. Alimentare l'Atmel-ICE

L'Atmel-ICE è alimentato dal bus USB voltage. Richiede meno di 100 mA per funzionare e può quindi essere alimentato tramite un hub USB. Il LED di alimentazione si illuminerà quando l'unità è collegata. Quando non è collegata a una sessione di programmazione o debug attiva, l'unità entrerà in modalità a basso consumo energetico per preservare la batteria del computer. L'Atmel-ICE non può essere spento: deve essere scollegato quando non viene utilizzato.

2.9. Connessione al computer host

Atmel-ICE comunica principalmente utilizzando un'interfaccia HID standard e non richiede un driver speciale sul computer host. Per utilizzare la funzionalità Data Gateway avanzata di Atmel-ICE, assicurarsi di installare il driver USB sul computer host. Questo viene fatto automaticamente durante l'installazione del software front-end fornito gratuitamente da Atmel. Vedere www.atmel.com per ulteriori informazioni o per scaricare l'ultimo software front-end.

L'Atmel-ICE deve essere collegato a una porta USB disponibile sul computer host utilizzando il cavo USB fornito o un microcavo certificato USB adatto. L'Atmel-ICE contiene un controller conforme a USB 2.0 e può funzionare sia in modalità a piena velocità che ad alta velocità. Per ottenere i migliori risultati, collegare l'Atmel-ICE direttamente a un hub ad alta velocità compatibile con USB 2.0 sul computer host utilizzando il cavo fornito.

2.10. Installazione del driver USB

2.10.1 Finestre

Quando si installa l'Atmel-ICE su un computer che esegue Microsoft® Windows®, il driver USB viene caricato quando l'Atmel-ICE viene collegato per la prima volta.

Nota:

Assicurarsi di installare i pacchetti software front-end prima di collegare l'unità per la prima volta.

Una volta installato con successo, l'Atmel-ICE apparirà nel gestore dispositivi come "Human Interface Device".

Collegamento dell'Atmel-ICE

3.1. Collegamento a dispositivi di destinazione AVR e SAM

L'Atmel-ICE è dotato di due connettori JTAG connettori. Entrambi i connettori sono collegati elettricamente direttamente, ma sono conformi a due diverse piedinature; l'AVR JTAG intestazione e l'intestazione ARM Cortex Debug. Il connettore deve essere selezionato in base al pinout della scheda di destinazione e non al tipo di MCU di destinazione, ad esampLe un dispositivo SAM montato in uno stack AVR STK® 600 deve utilizzare l'intestazione AVR.

Vari cavi e adattatori sono disponibili nei diversi kit Atmel-ICE. Un finitoview delle opzioni di connessione.

Figura 3-1. Opzioni di connessione Atmel-ICE Il filo rosso contrassegna il pin 1 del connettore a 10 pin da 50 mil. Il pin 1 del connettore a 6 pin da 100 mil è posizionato a destra della codifica quando il connettore è visto dal cavo. Il pin 1 di ciascun connettore sull'adattatore è contrassegnato da un punto bianco. La figura seguente mostra la piedinatura del cavo di debug. Il connettore contrassegnato con A si inserisce nel debugger mentre il lato B si inserisce nella scheda di destinazione.

Il filo rosso contrassegna il pin 1 del connettore a 10 pin da 50 mil. Il pin 1 del connettore a 6 pin da 100 mil è posizionato a destra della codifica quando il connettore è visto dal cavo. Il pin 1 di ciascun connettore sull'adattatore è contrassegnato da un punto bianco. La figura seguente mostra la piedinatura del cavo di debug. Il connettore contrassegnato con A si inserisce nel debugger mentre il lato B si inserisce nella scheda di destinazione.

Figura 3-2. Eseguire il debug del pinout del cavo 3.2. Collegamento a un JTAG Bersaglio

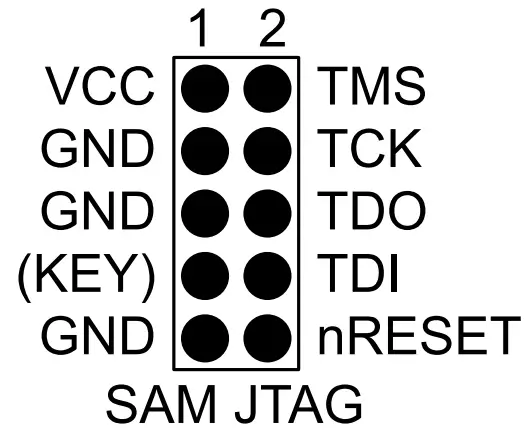

3.2. Collegamento a un JTAG Bersaglio

L'Atmel-ICE è dotato di due connettori JTAG connettori. Entrambi i connettori sono collegati elettricamente direttamente, ma sono conformi a due diverse piedinature; l'AVR JTAG intestazione e l'intestazione ARM Cortex Debug. Il connettore deve essere selezionato in base al pinout della scheda di destinazione e non al tipo di MCU di destinazione, ad esampLe un dispositivo SAM montato in uno stack AVR STK600 deve utilizzare l'intestazione AVR.

Il pinout consigliato per l'AVR JTAG connettore è mostrato nella Figura 4-6. La piedinatura consigliata per il connettore ARM Cortex Debug a 10 pin è mostrata nella Figura 4-2.

Collegamento diretto a un'intestazione standard a 10 pin da 50 mil

Utilizzare il cavo piatto da 50 mil a 10 pin (incluso in alcuni kit) per collegarsi direttamente a una scheda che supporta questo tipo di intestazione. Utilizzare la porta del connettore AVR su Atmel-ICE per le intestazioni con il pinout AVR e la porta del connettore SAM per le intestazioni conformi al pinout dell'intestazione ARM Cortex Debug.

I pinout per entrambe le porte del connettore a 10 pin sono mostrati di seguito.

Connessione a un'intestazione standard a 10 pin da 100 mil

Utilizzare un adattatore standard da 50 mil a 100 mil per connettersi alle intestazioni da 100 mil. A tale scopo può essere utilizzata una scheda adattatore (inclusa in alcuni kit) o in alternativa la scheda JTAGL'adattatore ICE3 può essere utilizzato per obiettivi AVR.![]() Importante:

Importante:

Il JTAGL'adattatore ICE3 da 100 mil non può essere utilizzato con la porta del connettore SAM, poiché i pin 2 e 10 (AVR GND) sull'adattatore sono collegati.

Connessione a un'intestazione personalizzata da 100 mil

Se la scheda di destinazione non dispone di un connettore J a 10 pin conformeTAG intestazione in 50 o 100 mil, è possibile mappare su una piedinatura personalizzata utilizzando il cavo "mini-squid" a 10 pin (incluso in alcuni kit), che consente l'accesso a dieci prese individuali da 100 mil.

Connessione a una testina da 20 mil a 100 pinr

Utilizzare la scheda adattatore (inclusa in alcuni kit) per connettersi a target con un'intestazione da 20 mil a 100 pin.

Tabella 3-1. Atmel-ICE JTAG Descrizione del pin

| Nome | AVR perno porta | SAM perno porta | Descrizione |

| TCK | 1 | 4 | Test Clock (segnale di clock dall'Atmel-ICE al dispositivo di destinazione). |

| Stimolazione magnetica | 5 | 2 | Test Mode Select (segnale di controllo dall'Atmel-ICE al dispositivo target). |

| TDI | 9 | 8 | Test Data In (dati trasmessi dall'Atmel-ICE al dispositivo di destinazione). |

| TDO | 3 | 6 | Test Data Out (dati trasmessi dal dispositivo target all'Atmel-ICE). |

| nTRST | 8 | – | Ripristino test (opzionale, solo su alcuni dispositivi AVR). Usato per resettare il JTAG Controllore TAP. |

| nSRST | 6 | 10 | Reimposta (facoltativo). Utilizzato per reimpostare il dispositivo di destinazione. Il collegamento di questo pin è consigliato poiché consente all'Atmel-ICE di mantenere il dispositivo di destinazione in uno stato di ripristino, che può essere essenziale per il debug in determinati scenari. |

| Vintage-vintage | 4 | 1 | Obiettivo voltage riferimento. L'Atmel-ICE samples il target voltage su questo pin per alimentare correttamente i convertitori di livello. L'Atmel-ICE assorbe meno di 3 mA da questo pin in modalità debugWIRE e meno di 1 mA in altre modalità. |

| Terra | 2, 10 | 3, 5, 9 | Terra. Tutti devono essere collegati per garantire che l'Atmel-ICE e il dispositivo target condividano lo stesso riferimento di terra. |

3.3. Connessione a un target aWire

L'interfaccia aWire richiede solo una linea dati oltre a VCC e GND. Sulla destinazione questa riga è la riga nRESET, sebbene il debugger utilizzi il JTAG Linea TDO come linea dati.

La piedinatura consigliata per il connettore aWire a 6 pin è illustrata nella Figura 4-8.

Collegamento a un'intestazione aWire da 6 mil a 100 pin

Utilizzare la presa a 6 pin da 100 mil sul cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione aWire standard da 100 mil.

Collegamento a un'intestazione aWire da 6 mil a 50 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per il collegamento a un'intestazione aWire standard da 50 mil.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR e la scheda di destinazione. Sono necessarie tre connessioni, come descritto nella tabella sottostante.

Tabella 3-2. Mappatura pin aWire Atmel-ICE

Perni porta Atmel-ICE AVR | Perni bersaglio | Pin di mini-calamari | aFilo pinout |

| Perno 1 (TCK) | 1 | ||

| Perno 2 (GND) | Terra | 2 | 6 |

| Perno 3 (TDO) | DATI | 3 | 1 |

| Perno 4 (VTG) | Vintage-vintage | 4 | 2 |

| Perno 5 (TMS) | 5 | ||

| Perno 6 (nSRST) | 6 | ||

| Pin 7 (non connesso) | 7 | ||

| Perno 8 (nTRST) | 8 | ||

| Perno 9 (TDI) | 9 | ||

| Perno 10 (GND) | 0 |

3.4. Connessione a un target PDI

La piedinatura consigliata per il connettore PDI a 6 pin è mostrata nella Figura 4-11.

Connessione a un'intestazione PDI da 6 mil a 100 pin

Utilizzare la presa da 6 mil a 100 pin sul cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione PDI standard da 100 mil.

Connessione a un'intestazione PDI da 6 mil a 50 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per il collegamento a un'intestazione PDI standard da 50 mil.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR e la scheda di destinazione. Sono necessarie quattro connessioni, come descritto nella tabella sottostante.![]() Importante:

Importante:

Il pinout richiesto è diverso dal JTAGICE mk II JTAG probe, dove PDI_DATA è connesso al pin 9. L'Atmel-ICE è compatibile con il pinout utilizzato dall'Atmel-ICE, JTAGICE3, AVR ONE! e AVR Dragon™.

Tabella 3-3. Mappatura pin PDI Atmel-ICE

| Perni porta Atmel-ICE AVR | Perni bersaglio | Pin di mini-calamari | aFilo pinout |

| Perno 1 (TCK) | 1 | ||

| Perno 2 (GND) | Terra | 2 | 6 |

| Perno 3 (TDO) | DATI | 3 | 1 |

| Perno 4 (VTG) | Vintage-vintage | 4 | 2 |

| Perno 5 (TMS) | 5 | ||

| Perno 6 (nSRST) | 6 | ||

| Pin 7 (non connesso) | 7 | ||

| Perno 8 (nTRST) | 8 | ||

| Perno 9 (TDI) | 9 | ||

| Perno 10 (GND) | 0 |

3.4 Connessione a un target PDI

La piedinatura consigliata per il connettore PDI a 6 pin è mostrata nella Figura 4-11.

Connessione a un'intestazione PDI da 6 mil a 100 pin

Utilizzare la presa da 6 mil a 100 pin sul cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione PDI standard da 100 mil.

Connessione a un'intestazione PDI da 6 mil a 50 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per il collegamento a un'intestazione PDI standard da 50 mil.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR e la scheda di destinazione. Sono necessarie quattro connessioni, come descritto nella tabella sottostante.![]() Importante:

Importante:

Il pinout richiesto è diverso dal JTAGICE mk II JTAG probe, dove PDI_DATA è connesso al pin 9. L'Atmel-ICE è compatibile con il pinout utilizzato dall'Atmel-ICE, JTAGICE3, AVR ONE! e AVR Dragon™ prodotti.

Tabella 3-3. Mappatura pin PDI Atmel-ICE

| Perno porta Atmel-ICE AVR | Perni bersaglio | Pin di mini-calamari | Piedinatura PDI Atmel STK600 |

| Perno 1 (TCK) | 1 | ||

| Perno 2 (GND) | Terra | 2 | 6 |

| Perno 3 (TDO) | PDI_DATI | 3 | 1 |

| Perno 4 (VTG) | Vintage-vintage | 4 | 2 |

| Perno 5 (TMS) | 5 | ||

| Perno 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (non connesso) | 7 | ||

| Perno 8 (nTRST) | 8 | ||

| Perno 9 (TDI) | 9 | ||

| Perno 10 (GND) | 0 |

3.5 Connessione a una destinazione UPDI

La piedinatura consigliata per il connettore UPDI a 6 pin è illustrata nella Figura 4-12.

Connessione a un'intestazione UPDI da 6 mil a 100 pin

Utilizzare la presa a 6 pin da 100 mil sul cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione UPDI standard da 100 mil.

Connessione a un'intestazione UPDI da 6 mil a 50 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per il collegamento a un'intestazione UPDI standard da 50 mil.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR e la scheda di destinazione. Sono necessarie tre connessioni, come descritto nella tabella sottostante.

Tabella 3-4. Mappatura pin UPDI Atmel-ICE

| Perno porta Atmel-ICE AVR | Perni bersaglio | Pin di mini-calamari | Piedinatura UPDI Atmel STK600 |

| Perno 1 (TCK) | 1 | ||

| Perno 2 (GND) | Terra | 2 | 6 |

| Perno 3 (TDO) | UPDI_DATI | 3 | 1 |

| Perno 4 (VTG) | Vintage-vintage | 4 | 2 |

| Perno 5 (TMS) | 5 | ||

| Perno 6 (nSRST) | [/RESET senso] | 6 | 5 |

| Pin 7 (non connesso) | 7 | ||

| Perno 8 (nTRST) | 8 | ||

| Perno 9 (TDI) | 9 | ||

| Perno 10 (GND) | 0 |

3.6 Connessione a un target debugWIRE

La piedinatura consigliata per il connettore SPI (debugWIRE) a 6 pin è mostrata nella Tabella 3-6.

Connessione a un'intestazione SPI da 6 mil a 100 pin

Utilizzare la presa da 6 mil a 100 pin sul cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione SPI standard da 100 mil.

Connessione a un'intestazione SPI da 6 mil a 50 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per connettersi a un'intestazione SPI standard da 50 mil.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR e la scheda di destinazione. Sono necessarie tre connessioni, come descritto nella Tabella 3-5.

Sebbene l'interfaccia debugWIRE richieda solo una linea di segnale (RESET), VCC e GND per funzionare correttamente, si consiglia di avere accesso al connettore SPI completo in modo che l'interfaccia debugWIRE possa essere abilitata e disabilitata utilizzando la programmazione SPI.

Quando il fusibile DWEN è abilitato, l'interfaccia SPI viene sovrascritta internamente in modo che il modulo OCD abbia il controllo sul pin RESET. L'OCD debugWIRE è in grado di disabilitarsi temporaneamente (utilizzando il pulsante nella scheda di debug nella finestra di dialogo delle proprietà in Atmel Studio), rilasciando così il controllo della riga RESET. L'interfaccia SPI è quindi nuovamente disponibile (solo se il fusibile SPIEN è programmato), consentendo di deprogrammare il fusibile DWEN utilizzando l'interfaccia SPI. Se l'alimentazione viene commutata prima che il fusibile DWEN non sia programmato, il modulo debugWIRE riprenderà il controllo del pin RESET.

Nota:

Si consiglia vivamente di lasciare semplicemente che Atmel Studio gestisca l'impostazione e la cancellazione del fusibile DWEN.

Non è possibile utilizzare l'interfaccia debugWIRE se i lockbit sul dispositivo AVR di destinazione sono programmati. Assicurarsi sempre che i lockbit siano azzerati prima di programmare il fusibile DWEN e non impostare mai i lockbit mentre il fusibile DWEN è programmato. Se sono impostati sia il fusibile di abilitazione debugWIRE (DWEN) che i bit di blocco, è possibile utilizzare High Voltage Programmazione per eseguire una cancellazione del chip e quindi cancellare i lockbit.

Quando i lockbit vengono cancellati, l'interfaccia debugWIRE verrà riattivata. L'interfaccia SPI è in grado di leggere i fusibili, leggere la firma ed eseguire una cancellazione del chip solo quando il fusibile DWEN non è programmato.

Tabella 3-5. Atmel-ICE debugWIRE Pin Mapping

| Perno porta Atmel-ICE AVR | Perni bersaglio | Pin di mini-calamari |

| Perno 1 (TCK) | 1 | |

| Perno 2 (GND) | Terra | 2 |

| Perno 3 (TDO) | 3 | |

| Perno 4 (VTG) | Vintage-vintage | 4 |

| Perno 5 (TMS) | 5 | |

| Perno 6 (nSRST) | RESET | 6 |

| Pin 7 (non connesso) | 7 | |

| Perno 8 (nTRST) | 8 | |

| Perno 9 (TDI) | 9 | |

| Perno 10 (GND) | 0 |

3.7 Connessione a un target SPI

La piedinatura consigliata per il connettore SPI a 6 pin è illustrata nella Figura 4-10.

Connessione a un'intestazione SPI da 6 mil a 100 pin

Utilizzare la presa da 6 mil a 100 pin sul cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione SPI standard da 100 mil.

Connessione a un'intestazione SPI da 6 mil a 50 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per connettersi a un'intestazione SPI standard da 50 mil.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR e la scheda di destinazione. Sono necessarie sei connessioni, come descritto nella tabella sottostante.![]() Importante:

Importante:

L'interfaccia SPI è effettivamente disabilitata quando è programmato il fusibile di abilitazione debugWIRE (DWEN), anche se è programmato anche il fusibile SPIEN. Per riattivare l'interfaccia SPI, è necessario eseguire il comando 'disable debugWIRE' durante una sessione di debugging debugWIRE. La disabilitazione di debugWIRE in questo modo richiede che il fusibile SPIEN sia già programmato. Se Atmel Studio non riesce a disabilitare debugWIRE, è probabile perché il fusibile SPIEN NON è programmato. Se questo è il caso, è necessario utilizzare un high-voltage interfaccia di programmazione per programmare il fusibile SPIEN.![]() Informazioni:

Informazioni:

L'interfaccia SPI viene spesso definita "ISP", poiché è stata la prima interfaccia di programmazione In System sui prodotti Atmel AVR. Altre interfacce sono ora disponibili per In System Programming.

Tabella 3-6. Mappatura dei pin SPI Atmel-ICE

| Perni porta Atmel-ICE AVR | Perni bersaglio | Pin di mini-calamari | Piedinatura SPI |

| Perno 1 (TCK) | SCK | 1 | 3 |

| Perno 2 (GND) | Terra | 2 | 6 |

| Perno 3 (TDO) | MISO | 3 | 1 |

| Perno 4 (VTG) | Vintage-vintage | 4 | 2 |

| Perno 5 (TMS) | 5 | ||

| Perno 6 (nSRST) | / RIPRISTINA | 6 | 5 |

| Pin 7 (non connesso) | 7 | ||

| Perno 8 (nTRST) | 8 | ||

| Perno 9 (TDI) | MOSI | 9 | 4 |

| Perno 10 (GND) | 0 |

3.8 Collegamento a un target TPI

La piedinatura consigliata per il connettore TPI a 6 pin è mostrata nella Figura 4-13.

Connessione a un'intestazione TPI da 6 mil a 100 pin

Utilizzare la presa a 6 pin da 100 mil sul cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione TPI standard da 100 mil.

Connessione a un'intestazione TPI da 6 mil a 50 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per il collegamento a un'intestazione TPI standard da 50 mil.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR e la scheda di destinazione. Sono necessarie sei connessioni, come descritto nella tabella sottostante.

Tabella 3-7. Mappatura dei pin TPI Atmel-ICE

| Perni porta Atmel-ICE AVR | Perni bersaglio | Pin di mini-calamari | Piedinatura TPI |

| Perno 1 (TCK) | OROLOGIO | 1 | 3 |

| Perno 2 (GND) | Terra | 2 | 6 |

| Perno 3 (TDO) | DATI | 3 | 1 |

| Perno 4 (VTG) | Vintage-vintage | 4 | 2 |

| Perno 5 (TMS) | 5 |

| Perno 6 (nSRST) | / RIPRISTINA | 6 | 5 |

| Pin 7 (non connesso) | 7 | ||

| Perno 8 (nTRST) | 8 | ||

| Perno 9 (TDI) | 9 | ||

| Perno 10 (GND) | 0 |

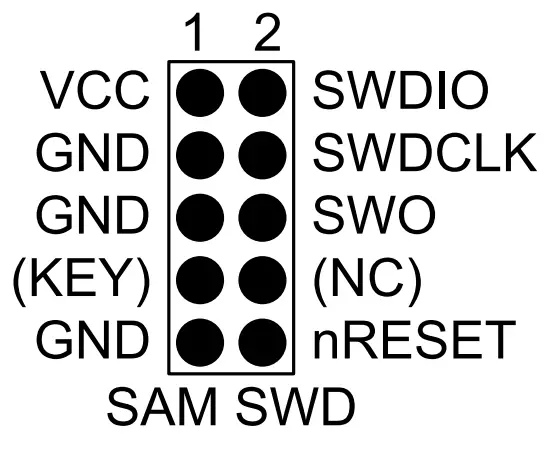

3.9 Connessione a una destinazione SWD

L'interfaccia ARM SWD è un sottoinsieme dell'interfaccia JTAG interfaccia, facendo uso dei pin TCK e TMS, il che significa che quando ci si collega a un dispositivo SWD, il J a 10 pinTAG connettore può essere tecnicamente utilizzato. L'ARM JTAG e AVR JTAG i connettori, tuttavia, non sono compatibili con i pin, quindi ciò dipende dal layout della scheda di destinazione in uso. Quando si utilizza un STK600 o una scheda che utilizza l'AVR JTAG pinout, deve essere utilizzata la porta del connettore AVR su Atmel-ICE. Quando ci si collega a una scheda che utilizza ARM JTAG piedinatura, deve essere utilizzata la porta del connettore SAM su Atmel-ICE.

Il pinout consigliato per il connettore Cortex Debug a 10 pin è mostrato nella Figura 4-4.

Connessione a un'intestazione Cortex a 10 pin da 50 mil

Utilizzare il cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione Cortex standard da 50 mil.

Connessione a un'intestazione con layout Cortex da 10 mil a 100 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per connettersi a un'intestazione con piedinatura Cortex da 100 mil.

Connessione a un'intestazione SAM da 20 mil a 100 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per il collegamento a un'intestazione SAM da 20 mil a 100 pin.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR o SAM e la scheda di destinazione. Sono necessarie sei connessioni, come descritto nella tabella sottostante.

Tabella 3-8. Mappatura dei pin SWD Atmel-ICE

| Nome | AVR perno porta | SAM perno porta | Descrizione |

| SWDC LK | 1 | 4 | Orologio di debug del cavo seriale. |

| SWDIO | 5 | 2 | Ingresso/uscita dati di debug del cavo seriale. |

| SWO | 3 | 6 | Serial Wire Output (opzionale, non implementato su tutti i dispositivi). |

| nSRST | 6 | 10 | Reset. |

| Vintage-vintage | 4 | 1 | Obiettivo voltage riferimento. |

| Terra | 2, 10 | 3, 5, 9 | Terra. |

3.10 Collegamento all'interfaccia del gateway dati

Atmel-ICE supporta un'interfaccia DGI (Data Gateway Interface) limitata quando il debug e la programmazione non sono in uso. La funzionalità è identica a quella dei kit Atmel Xplained Pro alimentati dal dispositivo Atmel EDBG.

L'interfaccia Data Gateway è un'interfaccia per lo streaming di dati dal dispositivo di destinazione a un computer. Questo è inteso come un aiuto nel debug dell'applicazione e per la dimostrazione delle funzionalità nell'applicazione in esecuzione sul dispositivo di destinazione.

DGI è costituito da più canali per lo streaming dei dati. Atmel-ICE supporta le seguenti modalità:

- USART

- SPI

Tabella 3-9. Piedinatura Atmel-ICE DGI USART

Porta dell'AVR | porta SAM | Perno DGI USART | Descrizione |

| 3 | 6 | TX | Trasmetti il pin da Atmel-ICE al dispositivo di destinazione |

| 4 | 1 | Vintage-vintage | Obiettivo voltage (riferimento voltage) |

| 8 | 7 | RX | Ricevi il pin dal dispositivo di destinazione ad Atmel-ICE |

| 9 | 8 | Orologio | Orologio USART |

| 2, 10 | 3, 5, 9 | Terra | Terra |

Tabella 3-10. Piedinatura Atmel-ICE DGI SPI

Porta dell'AVR | porta SAM | Spina DGI SPI | Descrizione |

| 1 | 4 | SCK | Orologio SPI |

| 3 | 6 | MISO | Master In Schiavo Fuori |

| 4 | 1 | Vintage-vintage | Obiettivo voltage (riferimento voltage) |

| 5 | 2 | NCS | Chip select attivo basso |

| 9 | 8 | MOSI | Master Out Schiavo In |

| 2, 10 | 3, 5, 9 | Terra | Terra |

![]() Importante: Le interfacce SPI e USART non possono essere utilizzate contemporaneamente.

Importante: Le interfacce SPI e USART non possono essere utilizzate contemporaneamente.![]() Importante: DGI e programmazione o debug non possono essere usati contemporaneamente.

Importante: DGI e programmazione o debug non possono essere usati contemporaneamente.

Debug su chip

4.1 Introduzione

Debug su chip

Un modulo di debug su chip è un sistema che consente a uno sviluppatore di monitorare e controllare l'esecuzione su un dispositivo da una piattaforma di sviluppo esterna, in genere tramite un dispositivo noto come debugger o adattatore di debug.

Con un sistema OCD l'applicazione può essere eseguita mantenendo le esatte caratteristiche elettriche e di temporizzazione nel sistema di destinazione, pur essendo in grado di interrompere l'esecuzione condizionalmente o manualmente e ispezionare il flusso e la memoria del programma.

Modalità di esecuzione

In modalità Run, l'esecuzione del codice è completamente indipendente da Atmel-ICE. L'Atmel-ICE monitorerà continuamente il dispositivo di destinazione per vedere se si è verificata una condizione di rottura. Quando ciò accade, il sistema OCD interrogherà il dispositivo attraverso la sua interfaccia di debug, consentendo all'utente di farlo view lo stato interno del dispositivo.

Modalità interrotta

Quando viene raggiunto un punto di interruzione, l'esecuzione del programma viene interrotta, ma alcuni I/O potrebbero continuare a essere eseguiti come se non si fosse verificato alcun punto di interruzione. Per esample, supponiamo che una trasmissione USART sia appena stata avviata quando viene raggiunto un punto di interruzione. In questo caso l'USART continua a funzionare a piena velocità completando la trasmissione, anche se il nucleo è in modalità di arresto.

Punti di interruzione hardware

Il modulo OCD di destinazione contiene una serie di comparatori di contatori di programma implementati nell'hardware. Quando il contatore di programma corrisponde al valore memorizzato in uno dei registri del comparatore, l'OCD entra in modalità di arresto. Poiché i punti di interruzione hardware richiedono hardware dedicato sul modulo OCD, il numero di punti di interruzione disponibili dipende dalla dimensione del modulo OCD implementato sulla destinazione. Di solito uno di questi comparatori hardware è "riservato" dal debugger per uso interno.

Punti di interruzione del software

Un punto di interruzione software è un'istruzione BREAK collocata nella memoria del programma sul dispositivo di destinazione. Quando questa istruzione viene caricata, l'esecuzione del programma si interrompe e l'OCD entra in modalità di arresto. Per continuare l'esecuzione è necessario dare un comando "start" dall'OCD. Non tutti i dispositivi Atmel dispongono di moduli OCD che supportano l'istruzione BREAK.

4.2 Dispositivi SAM con JTAG/SWD

Tutti i dispositivi SAM dispongono dell'interfaccia SWD per la programmazione e il debug. Inoltre, alcuni dispositivi SAM sono dotati di JTAG interfaccia con funzionalità identiche. Controlla la scheda tecnica del dispositivo per le interfacce supportate di quel dispositivo.

4.2.1.Componenti ARM CoreSight

I microcontrollori basati su Atmel ARM Cortex-M implementano componenti OCD conformi a CoreSight. Le caratteristiche di questi componenti possono variare da dispositivo a dispositivo. Per ulteriori informazioni consultare la scheda tecnica del dispositivo e la documentazione CoreSight fornita da ARM.

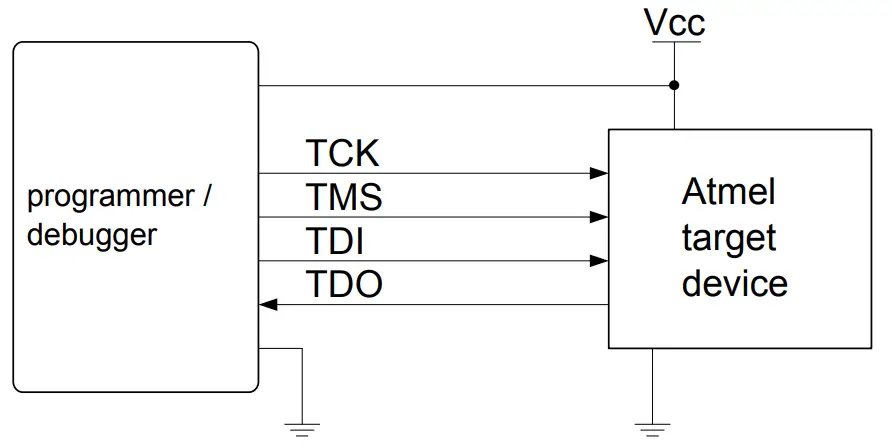

4.2.1. ETAG Interfaccia fisica

Il JTAG l'interfaccia è costituita da un controller TAP (Test Access Port) a 4 fili conforme a IEEE® 1149.1 standard. Lo standard IEEE è stato sviluppato per fornire un modo standard del settore per testare in modo efficiente la connettività del circuito stampato (Boundary Scan). I dispositivi Atmel AVR e SAM hanno esteso questa funzionalità per includere il supporto completo per la programmazione e il debug su chip.

Figura 4-1. JTAG Nozioni di base sull'interfaccia

4.2.2.1 SAM JTAG Piedinatura (connettore di debug Cortex-M)

Quando si progetta un'applicazione PCB che include un Atmel SAM con JTAG interfaccia, si consiglia di utilizzare il pinout come mostrato nella figura sottostante. Sono supportate entrambe le varianti da 100 e 50 mil di questa piedinatura, a seconda del cablaggio e degli adattatori inclusi nel kit specifico.

Figura 4-2. SAM JTAG Piedinatura dell'intestazione

Tabella 4-1. SAM JTAG Descrizione del pin

| Nome | Spillo | Descrizione |

| TCK | 4 | Test Clock (segnale di clock dall'Atmel-ICE al dispositivo di destinazione). |

| Stimolazione magnetica | 2 | Test Mode Select (segnale di controllo dall'Atmel-ICE al dispositivo target). |

| TDI | 8 | Test Data In (dati trasmessi dall'Atmel-ICE al dispositivo di destinazione). |

| TDO | 6 | Test Data Out (dati trasmessi dal dispositivo target all'Atmel-ICE). |

| nREIMPOSTA | 10 | Reimposta (facoltativo). Utilizzato per reimpostare il dispositivo di destinazione. Il collegamento di questo pin è consigliato poiché consente all'Atmel-ICE di mantenere il dispositivo di destinazione in uno stato di ripristino, che può essere essenziale per il debug in determinati scenari. |

| Vintage-vintage | 1 | Obiettivo voltage riferimento. L'Atmel-ICE samples il target voltage su questo pin per alimentare correttamente i convertitori di livello. L'Atmel-ICE assorbe meno di 1 mA da questo pin in questa modalità. |

| Terra | 3, 5, 9 | Terra. Tutti devono essere collegati per garantire che l'Atmel-ICE e il dispositivo target condividano lo stesso riferimento di terra. |

| CHIAVE | 7 | Collegato internamente al pin TRST sul connettore AVR. Consigliato in quanto non connesso. |

![]() Mancia: Ricordarsi di includere un condensatore di disaccoppiamento tra il pin 1 e GND.

Mancia: Ricordarsi di includere un condensatore di disaccoppiamento tra il pin 1 e GND.

4.2.2.2 ETAG Margherita Concatenamento

Il JTAG L'interfaccia consente di collegare più dispositivi a un'unica interfaccia in una configurazione a margherita. I dispositivi target devono essere tutti alimentati dalla stessa alimentazione voltage, condividono un nodo di terra comune e devono essere collegati come mostrato nella figura sottostante.

Figura 4-3. JTAG Catena di margherite

Quando si collegano dispositivi in un collegamento a margherita, è necessario considerare i seguenti punti:

- Tutti i dispositivi devono condividere una terra comune, collegata a GND sulla sonda Atmel-ICE

- Tutti i dispositivi devono funzionare sullo stesso target voltage. VTG su Atmel-ICE deve essere collegato a questo voltage.

- TMS e TCK sono collegati in parallelo; TDI e TDO sono collegati in seriale

- nSRST sulla sonda Atmel-ICE deve essere collegato a RESET sui dispositivi se uno qualsiasi dei dispositivi della catena disabilita il suo JTAG porta

- "Dispositivi prima" si riferisce al numero di JTAG dispositivi che il segnale TDI deve attraversare nel collegamento a margherita prima di raggiungere il dispositivo di destinazione. Allo stesso modo "dispositivi dopo" è il numero di dispositivi che il segnale deve attraversare dopo il dispositivo di destinazione prima di raggiungere il TDO Atmel-ICE

- "I bit di istruzione "prima" e "dopo" si riferiscono alla somma totale di tutti i JTAG le lunghezze dei registri delle istruzioni dei dispositivi, che sono collegati prima e dopo il dispositivo di destinazione nella catena a margherita

- La lunghezza IR totale (bit di istruzione prima + lunghezza IR del dispositivo di destinazione Atmel + bit di istruzione dopo) è limitata a un massimo di 256 bit. Il numero di dispositivi nella catena è limitato a 15 prima e 15 dopo.

![]() Mancia:

Mancia:

Collegamento a margherita esample: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Per connettersi all'Atmel AVR XMEGA® dispositivo, le impostazioni del collegamento a margherita sono:

- Dispositivi prima di: 1

- Dispositivi dopo: 1

- Bit di istruzioni prima di: 4 (i dispositivi AVR a 8 bit hanno 4 bit IR)

- Bit di istruzioni dopo: 5 (i dispositivi AVR a 32 bit hanno 5 bit IR)

Tabella 4-2. Lunghezze IR degli MCU Atmel

| Tipo di dispositivo | Lunghezza IR |

| Avr a 8 bit | 4 bit |

| Avr a 32 bit | 5 bit |

| SAM | 4 bit |

4.2.3. Collegamento a un JTAG Bersaglio

L'Atmel-ICE è dotato di due connettori JTAG connettori. Entrambi i connettori sono collegati elettricamente direttamente, ma sono conformi a due diverse piedinature; l'AVR JTAG intestazione e l'intestazione ARM Cortex Debug. Il connettore deve essere selezionato in base al pinout della scheda di destinazione e non al tipo di MCU di destinazione, ad esampLe un dispositivo SAM montato in uno stack AVR STK600 deve utilizzare l'intestazione AVR.

Il pinout consigliato per l'AVR JTAG connettore è mostrato nella Figura 4-6.

La piedinatura consigliata per il connettore ARM Cortex Debug a 10 pin è mostrata nella Figura 4-2.

Collegamento diretto a un'intestazione standard a 10 pin da 50 mil

Utilizzare il cavo piatto da 50 mil a 10 pin (incluso in alcuni kit) per collegarsi direttamente a una scheda che supporta questo tipo di intestazione. Utilizzare la porta del connettore AVR su Atmel-ICE per le intestazioni con il pinout AVR e la porta del connettore SAM per le intestazioni conformi al pinout dell'intestazione ARM Cortex Debug.

I pinout per entrambe le porte del connettore a 10 pin sono mostrati di seguito.

Connessione a un'intestazione standard a 10 pin da 100 mil

Utilizzare un adattatore standard da 50 mil a 100 mil per connettersi alle intestazioni da 100 mil. A tale scopo può essere utilizzata una scheda adattatore (inclusa in alcuni kit) o in alternativa la scheda JTAGL'adattatore ICE3 può essere utilizzato per obiettivi AVR.![]() Importante:

Importante:

Il JTAGL'adattatore ICE3 da 100 mil non può essere utilizzato con la porta del connettore SAM, poiché i pin 2 e 10 (AVR GND) sull'adattatore sono collegati.

Connessione a un'intestazione personalizzata da 100 mil

Se la scheda di destinazione non dispone di un connettore J a 10 pin conformeTAG intestazione in 50 o 100 mil, è possibile mappare su una piedinatura personalizzata utilizzando il cavo "mini-squid" a 10 pin (incluso in alcuni kit), che consente l'accesso a dieci prese individuali da 100 mil.

Connessione a un'intestazione da 20 mil a 100 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per connettersi a target con un'intestazione da 20 mil a 100 pin.

Tabella 4-3. Atmel-ICE JTAG Descrizione del pin

| Nome | AVR perno porta | SAM perno porta | Descrizione |

| TCK | 1 | 4 | Test Clock (segnale di clock dall'Atmel-ICE al dispositivo di destinazione). |

| Stimolazione magnetica | 5 | 2 | Test Mode Select (segnale di controllo dall'Atmel-ICE al dispositivo target). |

| TDI | 9 | 8 | Test Data In (dati trasmessi dall'Atmel-ICE al dispositivo di destinazione). |

| TDO | 3 | 6 | Test Data Out (dati trasmessi dal dispositivo target all'Atmel-ICE). |

| nTRST | 8 | – | Ripristino test (opzionale, solo su alcuni dispositivi AVR). Usato per resettare il JTAG Controllore TAP. |

| nSRST | 6 | 10 | Reimposta (facoltativo). Utilizzato per reimpostare il dispositivo di destinazione. Il collegamento di questo pin è consigliato poiché consente all'Atmel-ICE di mantenere il dispositivo di destinazione in uno stato di ripristino, che può essere essenziale per il debug in determinati scenari. |

| Vintage-vintage | 4 | 1 | Obiettivo voltage riferimento. L'Atmel-ICE samples il target voltage su questo pin per alimentare correttamente i convertitori di livello. L'Atmel-ICE assorbe meno di 3 mA da questo pin in modalità debugWIRE e meno di 1 mA in altre modalità. |

| Terra | 2, 10 | 3, 5, 9 | Terra. Tutti devono essere collegati per garantire che l'Atmel-ICE e il dispositivo target condividano lo stesso riferimento di terra. |

4.2.4. Interfaccia fisica SWD

L'interfaccia ARM SWD è un sottoinsieme dell'interfaccia JTAG interfaccia, facendo uso di pin TCK e TMS. L'ARM JTAG e AVR JTAG i connettori, tuttavia, non sono compatibili con i pin, quindi quando si progetta un'applicazione PCB, che utilizza un dispositivo SAM con SWD o JTAG interfaccia, si consiglia di utilizzare il pinout ARM mostrato nella figura seguente. La porta del connettore SAM sull'Atmel-ICE può connettersi direttamente a questa piedinatura.

Figura 4-4. Raccomandato ARM SWD/JTAG Piedinatura dell'intestazione

Atmel-ICE è in grado di eseguire lo streaming della traccia ITM in formato UART al computer host. La traccia viene acquisita sul pin TRACE/SWO dell'intestazione a 10 pin (JTAG perno TDO). I dati vengono memorizzati internamente su Atmel-ICE e inviati tramite l'interfaccia HID al computer host. La velocità dati massima affidabile è di circa 3 MB/s.

4.2.5. Connessione a una destinazione SWD

L'interfaccia ARM SWD è un sottoinsieme dell'interfaccia JTAG interfaccia, facendo uso dei pin TCK e TMS, il che significa che quando ci si collega a un dispositivo SWD, il J a 10 pinTAG connettore può essere tecnicamente utilizzato. L'ARM JTAG e AVR JTAG i connettori, tuttavia, non sono compatibili con i pin, quindi ciò dipende dal layout della scheda di destinazione in uso. Quando si utilizza un STK600 o una scheda che utilizza l'AVR JTAG pinout, deve essere utilizzata la porta del connettore AVR su Atmel-ICE. Quando ci si collega a una scheda che utilizza ARM JTAG piedinatura, deve essere utilizzata la porta del connettore SAM su Atmel-ICE.

Il pinout consigliato per il connettore Cortex Debug a 10 pin è mostrato nella Figura 4-4.

Connessione a un'intestazione Cortex a 10 pin da 50 mil

Utilizzare il cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione Cortex standard da 50 mil.

Connessione a un'intestazione con layout Cortex da 10 mil a 100 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per connettersi a un'intestazione con piedinatura Cortex da 100 mil.

Connessione a un'intestazione SAM da 20 mil a 100 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per il collegamento a un'intestazione SAM da 20 mil a 100 pin.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR o SAM e la scheda di destinazione. Sono necessarie sei connessioni, come descritto nella tabella sottostante.

Tabella 4-4. Mappatura dei pin SWD Atmel-ICE

| Nome | AVR perno porta | SAM perno porta | Descrizione |

| SWDC LK | 1 | 4 | Orologio di debug del cavo seriale. |

| SWDIO | 5 | 2 | Ingresso/uscita dati di debug del cavo seriale. |

| SWO | 3 | 6 | Serial Wire Output (opzionale, non implementato su tutti i dispositivi). |

| nSRST | 6 | 10 | Reset. |

| Vintage-vintage | 4 | 1 | Obiettivo voltage riferimento. |

| Terra | 2, 10 | 3, 5, 9 | Terra. |

4.2.6 Considerazioni speciali

CANCELLA perno

Alcuni dispositivi SAM includono un pin ERASE che si afferma esegua una cancellazione completa del chip e sblocchi i dispositivi su cui è impostato il bit di sicurezza. Questa funzione è accoppiata al dispositivo stesso e al controller flash e non fa parte del core ARM.

Il pin ERASE NON fa parte di alcuna intestazione di debug e Atmel-ICE non è quindi in grado di affermare questo segnale per sbloccare un dispositivo. In tali casi l'utente dovrebbe eseguire la cancellazione manualmente prima di avviare una sessione di debug.

Interfacce fisiche JTAG interfaccia

La linea RESET deve essere sempre collegata in modo che l'Atmel-ICE possa abilitare il JTAG interfaccia.

Interfaccia SWD

La linea RESET deve essere sempre collegata in modo che l'Atmel-ICE possa abilitare l'interfaccia SWD.

4.3 Dispositivi AVR UC3 con JTAG/un cavo

Tutti i dispositivi AVR UC3 presentano JTAG interfaccia per la programmazione e il debug. Inoltre, alcuni dispositivi AVR UC3 presentano l'interfaccia aWire con funzionalità identiche utilizzando un singolo cavo. Controlla la scheda tecnica del dispositivo per le interfacce supportate di quel dispositivo

4.3.1 Sistema di debug su chip Atmel AVR UC3

Il sistema OCD Atmel AVR UC3 è progettato in conformità con lo standard Nexus 2.0 (IEEE-ISTO 5001™-2003), che è uno standard di debug su chip aperto altamente flessibile e potente per microcontrollori a 32 bit. Supporta le seguenti funzionalità:

- Soluzione di debug conforme a Nexus

- OCD supporta qualsiasi velocità della CPU

- Sei punti di interruzione hardware del contatore del programma

- Due punti di interruzione dei dati

- I breakpoint possono essere configurati come watchpoint

- I punti di interruzione hardware possono essere combinati per fornire intervalli di interruzione

- Numero illimitato di punti di interruzione del programma utente (utilizzando BREAK)

- Traccia ramo contatore programma in tempo reale, traccia dati, traccia processo (supportato solo da debugger con porta di acquisizione traccia parallela)

Per ulteriori informazioni sul sistema OCD AVR UC3, consultare i manuali di riferimento tecnico AVR32UC, disponibili su www.atmel.com/uc3.

4.3.2. ETAG Interfaccia fisica

Il JTAG l'interfaccia è costituita da un controller TAP (Test Access Port) a 4 fili conforme a IEEE® 1149.1 standard. Lo standard IEEE è stato sviluppato per fornire un modo standard del settore per testare in modo efficiente la connettività del circuito stampato (Boundary Scan). I dispositivi Atmel AVR e SAM hanno esteso questa funzionalità per includere il supporto completo per la programmazione e il debug su chip.

Figura 4-5. JTAG Nozioni di base sull'interfaccia

4.3.2.1 Controllo automatico della velocità JTAG Pinout

Durante la progettazione di un'applicazione PCB, che include un Atmel AVR con JTAG interfaccia, si consiglia di utilizzare il pinout come mostrato nella figura sottostante. Sono supportate entrambe le varianti da 100 e 50 mil di questa piedinatura, a seconda del cablaggio e degli adattatori inclusi nel kit specifico.

Figura 4-6. AVR JTAG Piedinatura dell'intestazione

Tavolo 4-5. AVR JTAG Descrizione del pin

| Nome | Spillo | Descrizione |

| TCK | 1 | Test Clock (segnale di clock dall'Atmel-ICE al dispositivo di destinazione). |

| Stimolazione magnetica | 5 | Test Mode Select (segnale di controllo dall'Atmel-ICE al dispositivo target). |

| TDI | 9 | Test Data In (dati trasmessi dall'Atmel-ICE al dispositivo di destinazione). |

| TDO | 3 | Test Data Out (dati trasmessi dal dispositivo target all'Atmel-ICE). |

| nTRST | 8 | Ripristino test (opzionale, solo su alcuni dispositivi AVR). Usato per resettare il JTAG Controllore TAP. |

| nSRST | 6 | Reimposta (facoltativo). Utilizzato per reimpostare il dispositivo di destinazione. Il collegamento di questo pin è consigliato poiché consente all'Atmel-ICE di mantenere il dispositivo di destinazione in uno stato di ripristino, che può essere essenziale per il debug in determinati scenari. |

| Vintage-vintage | 4 | Obiettivo voltage riferimento. L'Atmel-ICE samples il target voltage su questo pin per alimentare correttamente i convertitori di livello. L'Atmel-ICE assorbe meno di 3 mA da questo pin in modalità debugWIRE e meno di 1 mA in altre modalità. |

| Terra | 2, 10 | Terra. Entrambi devono essere collegati per garantire che l'Atmel-ICE e il dispositivo target condividano lo stesso riferimento di terra. |

![]() Mancia: Ricordarsi di includere un condensatore di disaccoppiamento tra il pin 4 e GND.

Mancia: Ricordarsi di includere un condensatore di disaccoppiamento tra il pin 4 e GND.

4.3.2.2 ETAG Margherita Concatenamento

Il JTAG L'interfaccia consente di collegare più dispositivi a un'unica interfaccia in una configurazione a margherita. I dispositivi target devono essere tutti alimentati dalla stessa alimentazione voltage, condividono un nodo di terra comune e devono essere collegati come mostrato nella figura sottostante.

Figura 4-7. JTAG Catena di margherite

Quando si collegano dispositivi in un collegamento a margherita, è necessario considerare i seguenti punti:

- Tutti i dispositivi devono condividere una terra comune, collegata a GND sulla sonda Atmel-ICE

- Tutti i dispositivi devono funzionare sullo stesso target voltage. VTG su Atmel-ICE deve essere collegato a questo voltage.

- TMS e TCK sono collegati in parallelo; TDI e TDO sono collegati in una catena seriale.

- nSRST sulla sonda Atmel-ICE deve essere collegato a RESET sui dispositivi se uno qualsiasi dei dispositivi della catena disabilita il suo JTAG porta

- "Dispositivi prima" si riferisce al numero di JTAG dispositivi che il segnale TDI deve attraversare nel collegamento a margherita prima di raggiungere il dispositivo di destinazione. Allo stesso modo "dispositivi dopo" è il numero di dispositivi che il segnale deve attraversare dopo il dispositivo di destinazione prima di raggiungere il TDO Atmel-ICE

- "I bit di istruzione "prima" e "dopo" si riferiscono alla somma totale di tutti i JTAG le lunghezze dei registri delle istruzioni dei dispositivi, che sono collegati prima e dopo il dispositivo di destinazione nella catena a margherita

- La lunghezza IR totale (bit di istruzione prima + lunghezza IR del dispositivo di destinazione Atmel + bit di istruzione dopo) è limitata a un massimo di 256 bit. Il numero di dispositivi nella catena è limitato a 15 prima e 15 dopo.

Mancia:

Collegamento a margherita esample: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Per connettersi all'Atmel AVR XMEGA® dispositivo, le impostazioni del collegamento a margherita sono:

- Dispositivi prima di: 1

- Dispositivi dopo: 1

- Bit di istruzioni prima di: 4 (i dispositivi AVR a 8 bit hanno 4 bit IR)

- Bit di istruzioni dopo: 5 (i dispositivi AVR a 32 bit hanno 5 bit IR)

Tabella 4-6. Lunghezze IR di Atmel MCUS

| Tipo di dispositivo | Lunghezza IR |

| Avr a 8 bit | 4 bit |

| Avr a 32 bit | 5 bit |

| SAM | 4 bit |

4.3.3.Collegamento a JTAG Bersaglio

L'Atmel-ICE è dotato di due connettori JTAG connettori. Entrambi i connettori sono collegati elettricamente direttamente, ma sono conformi a due diverse piedinature; l'AVR JTAG intestazione e l'intestazione ARM Cortex Debug. Il connettore deve essere selezionato in base al pinout della scheda di destinazione e non al tipo di MCU di destinazione, ad esampLe un dispositivo SAM montato in uno stack AVR STK600 deve utilizzare l'intestazione AVR.

Il pinout consigliato per l'AVR JTAG connettore è mostrato nella Figura 4-6.

La piedinatura consigliata per il connettore ARM Cortex Debug a 10 pin è mostrata nella Figura 4-2.

Collegamento diretto a un'intestazione standard a 10 pin da 50 mil

Utilizzare il cavo piatto da 50 mil a 10 pin (incluso in alcuni kit) per collegarsi direttamente a una scheda che supporta questo tipo di intestazione. Utilizzare la porta del connettore AVR su Atmel-ICE per le intestazioni con il pinout AVR e la porta del connettore SAM per le intestazioni conformi al pinout dell'intestazione ARM Cortex Debug.

I pinout per entrambe le porte del connettore a 10 pin sono mostrati di seguito.

Connessione a un'intestazione standard a 10 pin da 100 mil

Utilizzare un adattatore standard da 50 mil a 100 mil per connettersi alle intestazioni da 100 mil. A tale scopo può essere utilizzata una scheda adattatore (inclusa in alcuni kit) o in alternativa la scheda JTAGL'adattatore ICE3 può essere utilizzato per obiettivi AVR.![]() Importante:

Importante:

Il JTAGL'adattatore ICE3 da 100 mil non può essere utilizzato con la porta del connettore SAM, poiché i pin 2 e 10 (AVR GND) sull'adattatore sono collegati.

Connessione a un'intestazione personalizzata da 100 mil

Se la scheda di destinazione non dispone di un connettore J a 10 pin conformeTAG intestazione in 50 o 100 mil, è possibile mappare su una piedinatura personalizzata utilizzando il cavo "mini-squid" a 10 pin (incluso in alcuni kit), che consente l'accesso a dieci prese individuali da 100 mil.

Connessione a un'intestazione da 20 mil a 100 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per connettersi a target con un'intestazione da 20 mil a 100 pin.

Tabella 4-7. Atmel-ICE JTAG Descrizione del pin

Nome | Perno porta AVR | Pin della porta SAM | Descrizione |

| TCK | 1 | 4 | Test Clock (segnale di clock dall'Atmel-ICE al dispositivo di destinazione). |

| Stimolazione magnetica | 5 | 2 | Test Mode Select (segnale di controllo dall'Atmel-ICE al dispositivo target). |

| TDI | 9 | 8 | Test Data In (dati trasmessi dall'Atmel-ICE al dispositivo di destinazione). |

| TDO | 3 | 6 | Test Data Out (dati trasmessi dal dispositivo target all'Atmel-ICE). |

| nTRST | 8 | – | Ripristino test (opzionale, solo su alcuni dispositivi AVR). Usato per resettare il JTAG Controllore TAP. |

| nSRST | 6 | 10 | Reimposta (facoltativo). Utilizzato per reimpostare il dispositivo di destinazione. Il collegamento di questo pin è consigliato poiché consente all'Atmel-ICE di mantenere il dispositivo di destinazione in uno stato di ripristino, che può essere essenziale per il debug in determinati scenari. |

| Vintage-vintage | 4 | 1 | Obiettivo voltage riferimento. L'Atmel-ICE samples il target voltage su questo pin per alimentare correttamente i convertitori di livello. L'Atmel-ICE assorbe meno di 3 mA da questo pin in modalità debugWIRE e meno di 1 mA in altre modalità. |

| Terra | 2, 10 | 3, 5, 9 | Terra. Tutti devono essere collegati per garantire che l'Atmel-ICE e il dispositivo target condividano lo stesso riferimento di terra. |

4.3.4 Interfaccia fisica aWire

L'interfaccia aWire utilizza il cavo RESET del dispositivo AVR per consentire funzioni di programmazione e debug. Una speciale sequenza di abilitazione viene trasmessa da Atmel-ICE, che disabilita la funzionalità RESET predefinita del pin. Quando si progetta un'applicazione PCB, che include un Atmel AVR con l'interfaccia aWire, si consiglia di utilizzare il pinout come mostrato nella Figura 4 -8. Sono supportate entrambe le varianti da 100 e 50 mil di questa piedinatura, a seconda del cablaggio e degli adattatori inclusi nel kit specifico.

Figura 4-8. aPinout dell'intestazione del cavo

![]() Mancia:

Mancia:

Poiché aWire è un'interfaccia half-duplex, si consiglia un resistore di pull-up sulla linea RESET dell'ordine di 47kΩ per evitare il falso rilevamento del bit di avvio quando si cambia direzione.

L'interfaccia aWire può essere utilizzata sia come interfaccia di programmazione che di debug. Tutte le funzionalità del sistema OCD disponibili tramite il connettore JTAG è possibile accedere all'interfaccia anche tramite aWire.

4.3.5 Collegamento a un bersaglio aWire

L'interfaccia aWire richiede solo una linea dati oltre a VCC e GND. Sulla destinazione questa riga è la riga nRESET, sebbene il debugger utilizzi il JTAG Linea TDO come linea dati.

La piedinatura consigliata per il connettore aWire a 6 pin è illustrata nella Figura 4-8.

Collegamento a un'intestazione aWire da 6 mil a 100 pin

Utilizzare la presa a 6 pin da 100 mil sul cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione aWire standard da 100 mil.

Collegamento a un'intestazione aWire da 6 mil a 50 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per il collegamento a un'intestazione aWire standard da 50 mil.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR e la scheda di destinazione. Sono necessarie tre connessioni, come descritto nella tabella sottostante.

Tabella 4-8. Mappatura pin aWire Atmel-ICE

| Perni porta Atmel-ICE AVR | Perni bersaglio | Pin di mini-calamari | aFilo pinout |

| Perno 1 (TCK) | 1 | ||

| Perno 2 (GND) | Terra | 2 | 6 |

| Perno 3 (TDO) | DATI | 3 | 1 |

| Perno 4 (VTG) | Vintage-vintage | 4 | 2 |

| Perno 5 (TMS) | 5 | ||

| Perno 6 (nSRST) | 6 | ||

| Pin 7 (non connesso) | 7 | ||

| Perno 8 (nTRST) | 8 | ||

| Perno 9 (TDI) | 9 | ||

| Perno 10 (GND) | 0 |

4.3.6. Considerazioni speciali

JTAG interfaccia

Su alcuni dispositivi Atmel AVR UC3 il JTAG la porta non è abilitata per impostazione predefinita. Quando si utilizzano questi dispositivi è indispensabile collegare la linea RESET in modo che l'Atmel-ICE possa abilitare il JTAG interfaccia.

aWire interfaccia

Il baud rate delle comunicazioni aWire dipende dalla frequenza dell'orologio di sistema, poiché i dati devono essere sincronizzati tra questi due domini. L'Atmel-ICE rileverà automaticamente che l'orologio di sistema è stato abbassato e ricalibrerà la sua velocità di trasmissione di conseguenza. La calibrazione automatica funziona solo fino a una frequenza di clock di sistema di 8kHz. Il passaggio a un clock di sistema inferiore durante una sessione di debug può causare la perdita del contatto con il target.

Se necessario, la velocità di trasmissione aWire può essere limitata impostando il parametro clock aWire. Il rilevamento automatico continuerà a funzionare, ma ai risultati verrà imposto un valore massimo.

Qualsiasi condensatore di stabilizzazione collegato al pin RESET deve essere scollegato quando si utilizza aWire poiché interferirà con il corretto funzionamento dell'interfaccia. Si consiglia un pullup esterno debole (10kΩ o superiore) su questa linea.

Spegni la modalità di sospensione

Alcuni dispositivi AVR UC3 dispongono di un regolatore interno che può essere utilizzato in modalità di alimentazione a 3.3 V con linee I/O regolate a 1.8 V. Ciò significa che il regolatore interno alimenta sia il core che la maggior parte degli I/O. Solo Atmel AVR ONE! debugger supporta il debug durante l'utilizzo delle modalità di sospensione in cui questo regolatore è disattivato.

4.3.7. Utilizzo EVTI/EVTO

I pin EVTI ed EVTO non sono accessibili su Atmel-ICE. Tuttavia, possono ancora essere utilizzati insieme ad altre apparecchiature esterne.

EVTI può essere utilizzato per i seguenti scopi:

- La destinazione può essere forzata a interrompere l'esecuzione in risposta a un evento esterno. Se i bit Event In Control (EIC) nel registro DC vengono scritti su 0b01, la transizione da alto a basso sul pin EVTI genererà una condizione di punto di interruzione. EVTI deve rimanere basso per un ciclo di clock della CPU per garantire che un punto di interruzione sia Il bit EXB (External Breakpoint) in DS viene impostato quando ciò si verifica.

- Generazione di messaggi di sincronizzazione della traccia. Non utilizzato dall'Atmel-ICE.

EVTO può essere utilizzato per i seguenti scopi:

- Indica che la CPU è entrata nel debug L'impostazione dei bit EOS in DC su 0b01 fa sì che il pin EVTO venga abbassato per un ciclo di clock della CPU quando il dispositivo di destinazione entra in modalità di debug. Questo segnale può essere utilizzato come sorgente di trigger per un oscilloscopio esterno.

- Indica che la CPU ha raggiunto un breakpoint o watchpoint. Impostando il bit EOC in un registro di controllo Breakpoint/Watchpoint corrispondente, lo stato del punto di interruzione o del punto di controllo viene indicato sul pin EVTO. I bit EOS in DC devono essere impostati su 0xb10 per abilitare questa funzione. Il pin EVTO può quindi essere collegato a un oscilloscopio esterno per esaminare il punto di controllo

- Generazione di segnali di temporizzazione della traccia. Non utilizzato dall'Atmel-ICE.

4.4 Dispositivi tinyAVR, megaAVR e XMEGA

I dispositivi AVR sono dotati di varie interfacce di programmazione e debug. Controlla la scheda tecnica del dispositivo per le interfacce supportate di quel dispositivo.

- Alcuni minuscoli AVR® i dispositivi hanno un TPI TPI può essere utilizzato solo per programmare il dispositivo e questi dispositivi non hanno alcuna capacità di debug su chip.

- Alcuni dispositivi tinyAVR e alcuni dispositivi megaAVR hanno l'interfaccia debugWIRE, che si collega a un sistema di debug su chip noto come tinyOCD. Tutti i dispositivi con debugWIRE hanno anche l'interfaccia SPI per il sistema

- Alcuni dispositivi megaAVR hanno un JTAG interfaccia per la programmazione e il debug, con un sistema di debug su chip noto anche come Tutti i dispositivi con JTAG presentano anche l'interfaccia SPI come interfaccia alternativa per la programmazione nel sistema.

- Tutti i dispositivi AVR XMEGA hanno l'interfaccia PDI per la programmazione e alcuni dispositivi AVR XMEGA hanno anche un JTAG interfaccia con funzionalità identiche.

- I nuovi dispositivi tinyAVR hanno un'interfaccia UPDI, che viene utilizzata per la programmazione e il debug

Tabella 4-9. Riepilogo delle interfacce di programmazione e debug

| AGGIORNAMENTO | TPI | SPI | debugWIR E | JTAG | PDI | un cavo | SWD | |

| tinyAVR | Nuovi dispositivi | Alcuni dispositivi | Alcuni dispositivi | Alcuni dispositivi | ||||

| megaAV R | Tutti i dispositivi | Alcuni dispositivi | Alcuni dispositivi | |||||

| AVRXMEGA | Alcuni dispositivi | Tutti i dispositivi | ||||||

| AVRUC | Tutti i dispositivi | Alcuni dispositivi | ||||||

| SAM | Alcuni dispositivi | Tutti i dispositivi |

4.4.1. ETAG Interfaccia fisica

Il JTAG l'interfaccia è costituita da un controller TAP (Test Access Port) a 4 fili conforme a IEEE® 1149.1 standard. Lo standard IEEE è stato sviluppato per fornire un modo standard del settore per testare in modo efficiente la connettività del circuito stampato (Boundary Scan). I dispositivi Atmel AVR e SAM hanno esteso questa funzionalità per includere il supporto completo per la programmazione e il debug su chip.

Figura 4-9. JTAG Nozioni di base sull'interfaccia 4.4.2. Collegamento a un JTAG Bersaglio

4.4.2. Collegamento a un JTAG Bersaglio

L'Atmel-ICE è dotato di due connettori JTAG connettori. Entrambi i connettori sono collegati elettricamente direttamente, ma sono conformi a due diverse piedinature; l'AVR JTAG intestazione e l'intestazione ARM Cortex Debug. Il connettore deve essere selezionato in base al pinout della scheda di destinazione e non al tipo di MCU di destinazione, ad esampLe un dispositivo SAM montato in uno stack AVR STK600 deve utilizzare l'intestazione AVR.

Il pinout consigliato per l'AVR JTAG connettore è mostrato nella Figura 4-6.

La piedinatura consigliata per il connettore ARM Cortex Debug a 10 pin è mostrata nella Figura 4-2.

Collegamento diretto a un'intestazione standard a 10 pin da 50 mil

Utilizzare il cavo piatto da 50 mil a 10 pin (incluso in alcuni kit) per collegarsi direttamente a una scheda che supporta questo tipo di intestazione. Utilizzare la porta del connettore AVR su Atmel-ICE per le intestazioni con il pinout AVR e la porta del connettore SAM per le intestazioni conformi al pinout dell'intestazione ARM Cortex Debug.

I pinout per entrambe le porte del connettore a 10 pin sono mostrati di seguito.

Connessione a un'intestazione standard a 10 pin da 100 mil

Utilizzare un adattatore standard da 50 mil a 100 mil per connettersi alle intestazioni da 100 mil. A tale scopo può essere utilizzata una scheda adattatore (inclusa in alcuni kit) o in alternativa la scheda JTAGL'adattatore ICE3 può essere utilizzato per obiettivi AVR.![]() Importante:

Importante:

Il JTAGL'adattatore ICE3 da 100 mil non può essere utilizzato con la porta del connettore SAM, poiché i pin 2 e 10 (AVR GND) sull'adattatore sono collegati.

Connessione a un'intestazione personalizzata da 100 mil

Se la scheda di destinazione non dispone di un connettore J a 10 pin conformeTAG intestazione in 50 o 100 mil, è possibile mappare su una piedinatura personalizzata utilizzando il cavo "mini-squid" a 10 pin (incluso in alcuni kit), che consente l'accesso a dieci prese individuali da 100 mil.

Connessione a un'intestazione da 20 mil a 100 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per connettersi a target con un'intestazione da 20 mil a 100 pin.

Tabella 4-10. Atmel-ICE JTAG Descrizione del pin

| Nome | AVR perno porta | SAM perno porta | Descrizione |

| TCK | 1 | 4 | Test Clock (segnale di clock dall'Atmel-ICE al dispositivo di destinazione). |

| Stimolazione magnetica | 5 | 2 | Test Mode Select (segnale di controllo dall'Atmel-ICE al dispositivo target). |

| TDI | 9 | 8 | Test Data In (dati trasmessi dall'Atmel-ICE al dispositivo di destinazione). |

| TDO | 3 | 6 | Test Data Out (dati trasmessi dal dispositivo target all'Atmel-ICE). |

| nTRST | 8 | – | Ripristino test (opzionale, solo su alcuni dispositivi AVR). Usato per resettare il JTAG Controllore TAP. |

| nSRST | 6 | 10 | Reimposta (facoltativo). Utilizzato per reimpostare il dispositivo di destinazione. Il collegamento di questo pin è consigliato poiché consente all'Atmel-ICE di mantenere il dispositivo di destinazione in uno stato di ripristino, che può essere essenziale per il debug in determinati scenari. |

| Vintage-vintage | 4 | 1 | Obiettivo voltage riferimento. L'Atmel-ICE samples il target voltage su questo pin per alimentare correttamente i convertitori di livello. L'Atmel-ICE assorbe meno di 3 mA da questo pin in modalità debugWIRE e meno di 1 mA in altre modalità. |

| Terra | 2, 10 | 3, 5, 9 | Terra. Tutti devono essere collegati per garantire che l'Atmel-ICE e il dispositivo target condividano lo stesso riferimento di terra. |

4.4.3.Interfaccia fisica SPI

La programmazione In-System utilizza la SPI (Serial Peripheral Interface) interna dell'AVR Atmel di destinazione per scaricare il codice nelle memorie flash ed EEPROM. Non è un'interfaccia di debug. Quando si progetta un PCB dell'applicazione, che include un AVR con l'interfaccia SPI, è necessario utilizzare il pinout come mostrato nella figura seguente.

Figura 4-10. Piedinatura dell'intestazione SPI 4.4.4. Connessione a un target SPI

4.4.4. Connessione a un target SPI

La piedinatura consigliata per il connettore SPI a 6 pin è illustrata nella Figura 4-10.

Connessione a un'intestazione SPI da 6 mil a 100 pin

Utilizzare la presa da 6 mil a 100 pin sul cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione SPI standard da 100 mil.

Connessione a un'intestazione SPI da 6 mil a 50 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per connettersi a un'intestazione SPI standard da 50 mil.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR e la scheda di destinazione. Sono necessarie sei connessioni, come descritto nella tabella sottostante.![]() Importante:

Importante:

L'interfaccia SPI è effettivamente disabilitata quando è programmato il fusibile di abilitazione debugWIRE (DWEN), anche se è programmato anche il fusibile SPIEN. Per riattivare l'interfaccia SPI, è necessario eseguire il comando 'disable debugWIRE' durante una sessione di debugging debugWIRE. La disabilitazione di debugWIRE in questo modo richiede che il fusibile SPIEN sia già programmato. Se Atmel Studio non riesce a disabilitare debugWIRE, è probabile perché il fusibile SPIEN NON è programmato. Se questo è il caso, è necessario utilizzare un high-voltage interfaccia di programmazione per programmare il fusibile SPIEN.![]() Informazioni:

Informazioni:

L'interfaccia SPI viene spesso definita "ISP", poiché è stata la prima interfaccia di programmazione In System sui prodotti Atmel AVR. Altre interfacce sono ora disponibili per In System Programming.

Tabella 4-11. Mappatura dei pin SPI Atmel-ICE

| Perni porta Atmel-ICE AVR | Perni bersaglio | Pin di mini-calamari | Piedinatura SPI |

| Perno 1 (TCK) | SCK | 1 | 3 |

| Perno 2 (GND) | Terra | 2 | 6 |

| Perno 3 (TDO) | MISO | 3 | 1 |

| Perno 4 (VTG) | Vintage-vintage | 4 | 2 |

| Perno 5 (TMS) | 5 | ||

| Perno 6 (nSRST) | / RIPRISTINA | 6 | 5 |

| Pin 7 (non connesso) | 7 | ||

| Perno 8 (nTRST) | 8 | ||

| Perno 9 (TDI) | MOSI | 9 | 4 |

| Perno 10 (GND) | 0 |

4.4.5. PDI

L'interfaccia di programma e debug (PDI) è un'interfaccia proprietaria Atmel per la programmazione esterna e il debug su chip di un dispositivo. PDI Physical è un'interfaccia a 2 pin che fornisce una comunicazione sincrona half-duplex bidirezionale con il dispositivo di destinazione.

Quando si progetta un PCB dell'applicazione, che include un Atmel AVR con l'interfaccia PDI, è necessario utilizzare il pinout mostrato nella figura seguente. È quindi possibile utilizzare uno degli adattatori a 6 pin forniti con il kit Atmel-ICE per collegare la sonda Atmel-ICE al PCB dell'applicazione.

Figura 4-11. Piedinatura dell'intestazione PDI 4.4.6.Connessione a un PDI Target

4.4.6.Connessione a un PDI Target

La piedinatura consigliata per il connettore PDI a 6 pin è mostrata nella Figura 4-11.

Connessione a un'intestazione PDI da 6 mil a 100 pin

Utilizzare la presa da 6 mil a 100 pin sul cavo piatto (incluso in alcuni kit) per il collegamento a un'intestazione PDI standard da 100 mil.

Connessione a un'intestazione PDI da 6 mil a 50 pin

Utilizzare la scheda adattatore (inclusa in alcuni kit) per il collegamento a un'intestazione PDI standard da 50 mil.

Connessione a un'intestazione personalizzata da 100 mil

Il cavo mini-squid a 10 pin deve essere utilizzato per il collegamento tra la porta del connettore Atmel-ICE AVR e la scheda di destinazione. Sono necessarie quattro connessioni, come descritto nella tabella sottostante.![]() Importante:

Importante:

Il pinout richiesto è diverso dal JTAGICE mk II JTAG probe, dove PDI_DATA è connesso al pin 9. L'Atmel-ICE è compatibile con il pinout utilizzato dall'Atmel-ICE, JTAGICE3, AVR ONE! e AVR Dragon™ prodotti.

Tabella 4-12. Mappatura pin PDI Atmel-ICE

Perno porta Atmel-ICE AVR | Perni bersaglio | Pin di mini-calamari | Piedinatura PDI Atmel STK600 |

| Perno 1 (TCK) | 1 | ||

| Perno 2 (GND) | Terra | 2 | 6 |

| Perno 3 (TDO) | PDI_DATI | 3 | 1 |

| Perno 4 (VTG) | Vintage-vintage | 4 | 2 |

| Perno 5 (TMS) | 5 | ||

| Perno 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (non connesso) | 7 | ||

| Perno 8 (nTRST) | 8 | ||

| Perno 9 (TDI) | 9 | ||

| Perno 10 (GND) | 0 |

4.4.7. Interfaccia fisica UPDI

L'Unified Program and Debug Interface (UPDI) è un'interfaccia proprietaria Atmel per la programmazione esterna e il debug su chip di un dispositivo. È un successore dell'interfaccia fisica a 2 fili PDI, che si trova su tutti i dispositivi AVR XMEGA. UPDI è un'interfaccia a filo singolo che fornisce una comunicazione asincrona half-duplex bidirezionale con il dispositivo di destinazione per scopi di programmazione e debug.

Quando si progetta un'applicazione PCB, che include un Atmel AVR con l'interfaccia UPDI, è necessario utilizzare il pinout mostrato di seguito. È quindi possibile utilizzare uno degli adattatori a 6 pin forniti con il kit Atmel-ICE per collegare la sonda Atmel-ICE al PCB dell'applicazione.

Figura 4-12. Piedinatura dell'intestazione UPDI 4.4.7.1 UPDI e /RESET

4.4.7.1 UPDI e /RESET

L'interfaccia UPDI a un filo può essere un pin dedicato o un pin condiviso, a seconda del dispositivo AVR di destinazione. Consultare la scheda tecnica del dispositivo per ulteriori informazioni.

Quando l'interfaccia UPDI si trova su un pin condiviso, il pin può essere configurato per essere UPDI, /RESET o GPIO impostando i fusibili RSTPINCFG[1:0].

I fusibili RSTPINCFG[1:0] hanno le seguenti configurazioni, come descritto nel datasheet. Le implicazioni pratiche di ogni scelta sono qui fornite.

Tabella 4-13. RSTPINCFG[1:0] Configurazione fusibili

| RSTPINCFG[1:0] | Configurazione | Utilizzo |

| 00 | GPIO | Pin I/O per uso generico. Per accedere a UPDI, è necessario applicare un impulso a 12V a questo pin. Non è disponibile alcuna sorgente di ripristino esterna. |

| 01 | AGGIORNAMENTO | Pin di programmazione e debug dedicato. Non è disponibile alcuna sorgente di ripristino esterna. |

| 10 | Reset | Reimpostare l'ingresso del segnale. Per accedere a UPDI, è necessario applicare un impulso a 12V a questo pin. |

| 11 | Prenotato | NA |

Nota: I vecchi dispositivi AVR hanno un'interfaccia di programmazione, nota come "High-Voltage Programming” (esistono sia varianti seriali che parallele). In generale questa interfaccia richiede l'applicazione di 12V al pin /RESET per la durata della sessione di programmazione. L'interfaccia UPDI è un'interfaccia completamente diversa. Il pin UPDI è principalmente un pin di programmazione e debug, che può essere fuso per avere una funzione alternativa (/RESET o GPIO). Se viene selezionata la funzione alternativa, è necessario un impulso a 12V su quel pin per riattivare la funzionalità UPDI.

Nota: Se un progetto richiede la condivisione del segnale UPDI a causa di vincoli di pin, è necessario adottare misure per garantire che il dispositivo possa essere programmato. Per garantire che il segnale UPDI possa funzionare correttamente, nonché per evitare danni ai componenti esterni dall'impulso 12V, si consiglia di scollegare qualsiasi componente su questo pin quando si tenta di eseguire il debug o programmare il dispositivo. Questo può essere fatto utilizzando un resistore da 0Ω, che è montato per impostazione predefinita e rimosso o sostituito da un'intestazione pin durante il debug. Questa configurazione significa effettivamente che la programmazione deve essere eseguita prima di montare il dispositivo.![]() Importante: L'Atmel-ICE non supporta 12V sulla linea UPDI. In altre parole, se il pin UPDI è stato configurato come GPIO o RESET, l'Atmel-ICE non sarà in grado di abilitare l'interfaccia UPDI.

Importante: L'Atmel-ICE non supporta 12V sulla linea UPDI. In altre parole, se il pin UPDI è stato configurato come GPIO o RESET, l'Atmel-ICE non sarà in grado di abilitare l'interfaccia UPDI.

4.4.8.Connessione a una destinazione UPDI