Mga Programmer ng ICE Debugger

Mga Programmer ng ICE Debugger

Gabay sa Gumagamit Mga Programmer at Debugger

Mga Programmer at Debugger

Atmel-ICE

GABAY NG USER

Ang Atmel-ICE Debugger

Ang Atmel-ICE ay isang mahusay na tool sa pag-develop para sa pag-debug at pagprograma ng ARM® Cortex®-M na nakabatay sa Atmel ®SAM at Atmel AVR microcontroller na may kakayahan sa ® On-Chip Debug.

Sinusuportahan nito ang:

- Programming at on-chip debugging ng lahat ng Atmel AVR 32-bit microcontrollers sa parehong JTAG at mga interface ng aWire

- Programming at on-chip debugging ng lahat ng Atmel AVR XMEGA® family device sa parehong JTAG at PDI 2-wire na mga interface

- Programming (JTAG, SPI, UPDI) at pag-debug ng lahat ng Atmel AVR 8-bit microcontroller na may suporta sa OCD sa alinmang JTAG, mga interface ng debugWIRE o UPDI

- Pagprograma at pag-debug ng lahat ng Atmel SAM ARM Cortex-M na nakabatay sa microcontroller sa parehong SWD at JTAG mga interface

- Programming (TPI) ng lahat ng Atmel tinyAVR® 8-bit microcontrollers na may suporta para sa interface na ito

Kumonsulta sa listahan ng mga sinusuportahang device sa Gabay sa Gumagamit ng Atmel Studio para sa buong listahan ng mga device at interface na sinusuportahan ng paglabas ng firmware na ito.

Panimula

1.1. Panimula sa Atmel-ICE

Ang Atmel-ICE ay isang mahusay na tool sa pag-develop para sa pag-debug at pagprograma ng ARM Cortex-M na nakabatay sa Atmel SAM at Atmel AVR microcontroller na may kakayahan sa On-Chip Debug.

Sinusuportahan nito ang:

- Programming at on-chip debugging ng lahat ng Atmel AVR UC3 microcontroller sa parehong JTAG at mga interface ng aWire

- Programming at on-chip debugging ng lahat ng AVR XMEGA family device sa parehong JTAG at mga interface ng PDI 2wire

- Programming (JTAG at SPI) at pag-debug ng lahat ng AVR 8-bit microcontroller na may suporta sa OCD sa parehong JTAG o mga interface ng debugWIRE

- Pagprograma at pag-debug ng lahat ng Atmel SAM ARM Cortex-M na nakabatay sa microcontroller sa parehong SWD at JTAG mga interface

- Programming (TPI) ng lahat ng Atmel tinyAVR 8-bit microcontrollers na may suporta para sa interface na ito

1.2. Mga Tampok ng Atmel-ICE

- Ganap na katugma sa Atmel Studio

- Sinusuportahan ang programming at pag-debug ng lahat ng Atmel AVR UC3 32-bit microcontrollers

- Sinusuportahan ang programming at pag-debug ng lahat ng 8-bit na AVR XMEGA device

- Sinusuportahan ang programming at pag-debug ng lahat ng 8-bit na Atmel megaAVR® at tinyAVR device na may OCD

- Sinusuportahan ang programming at pag-debug ng lahat ng SAM ARM Cortex-M na nakabatay sa microcontroller

- Target na operating voltage saklaw ng 1.62V hanggang 5.5V

- Gumuhit ng mas mababa sa 3mA mula sa target na VTref kapag gumagamit ng debugWIRE interface at mas mababa sa 1mA para sa lahat ng iba pang interface

- Sinusuportahan si JTAG mga frequency ng orasan mula 32kHz hanggang 7.5MHz

- Sinusuportahan ang PDI clock frequency mula 32kHz hanggang 7.5MHz

- Sinusuportahan ang debugWIRE baud rate mula 4kbit/s hanggang 0.5Mbit/s

- Sinusuportahan ang aWire baud rate mula 7.5kbit/s hanggang 7Mbit/s

- Sinusuportahan ang mga frequency ng orasan ng SPI mula 8kHz hanggang 5MHz

- Sinusuportahan ang UPDI baud rate mula hanggang 750kbit/s

- Sinusuportahan ang mga frequency ng orasan ng SWD mula 32kHz hanggang 10MHz

- USB 2.0 high-speed host interface

- ITM serial trace capture sa hanggang 3MB/s

- Sinusuportahan ang mga interface ng DGI SPI at USART kapag hindi nagde-debug o nagprograma

- Sinusuportahan ang 10-pin 50-mil JTAG connector na may parehong AVR at Cortex pinout. Sinusuportahan ng karaniwang probe cable ang AVR 6-pin ISP/PDI/TPI 100-mil header pati na rin ang 10-pin 50-mil. Available ang adapter para suportahan ang 6-pin 50-mil, 10-pin 100-mil, at 20-pin 100-mil na mga header. Maraming opsyon sa kit ang available na may iba't ibang paglalagay ng kable at mga adaptor.

1.3. Mga Kinakailangan sa System

Kinakailangan ng unit ng Atmel-ICE na naka-install sa iyong computer ang isang front-end na debugging environment na Atmel Studio na bersyon 6.2 o mas bago.

Ang Atmel-ICE ay dapat na konektado sa host computer gamit ang ibinigay na USB cable, o isang certified Micro-USB cable.

Pagsisimula sa Atmel-ICE

2.1. Mga Nilalaman ng Buong Kit

Ang buong kit ng Atmel-ICE ay naglalaman ng mga item na ito:

- Atmel-ICE unit

- USB cable (1.8m, high-speed, Micro-B)

- Adapter board na naglalaman ng 50-mil AVR, 100-mil AVR/SAM, at 100-mil 20-pin SAM adapters

- IDC flat cable na may 10-pin 50-mil connector at 6-pin 100-mil connector

- 50-mil 10-pin mini squid cable na may 10 x 100-mil socket

Larawan 2-1. Mga Nilalaman ng Buong Kit ng Atmel-ICE 2.2. Pangunahing Nilalaman ng Kit

2.2. Pangunahing Nilalaman ng Kit

Ang pangunahing kit ng Atmel-ICE ay naglalaman ng mga item na ito:

- Atmel-ICE unit

- USB cable (1.8m, high-speed, Micro-B)

- IDC flat cable na may 10-pin 50-mil connector at 6-pin 100-mil connector

Larawan 2-2. Mga Nilalaman ng Atmel-ICE Basic Kit 2.3. Mga Nilalaman ng PCBA Kit

2.3. Mga Nilalaman ng PCBA Kit

Ang Atmel-ICE PCBA kit ay naglalaman ng mga item na ito:

- Atmel-ICE unit na walang plastic encapsulation

Larawan 2-3. Mga Nilalaman ng Atmel-ICE PCBA Kit 2.4. Mga Spare Parts Kit

2.4. Mga Spare Parts Kit

Available ang mga sumusunod na spare parts kit:

- Adapter kit

- Cable kit

Larawan 2-4. Mga Nilalaman ng Atmel-ICE Adapter Kit 2.5. Tapos na ang Kitview

2.5. Tapos na ang Kitview

Ang mga opsyon sa Atmel-ICE kit ay ipinapakita sa diagrammatically dito:

Larawan 2-6. Atmel-ICE Kit Overview 2.6. Pagtitipon ng Atmel-ICE

2.6. Pagtitipon ng Atmel-ICE

Ang unit ng Atmel-ICE ay ipinadala nang walang mga kable na nakakabit. Dalawang opsyon sa cable ang ibinibigay sa buong kit:

- 50-mil 10-pin IDC flat cable na may 6-pin ISP at 10-pin connector

- 50-mil 10-pin mini-squid cable na may 10 x 100-mil socket

Larawan 2-7. Mga Kable ng Atmel-ICE Para sa karamihan ng mga layunin, maaaring gamitin ang 50-mil 10-pin IDC flat cable, kumokonekta sa alinman sa natively sa 10-pin o 6-pin connector nito, o kumokonekta sa pamamagitan ng adapter board. Tatlong adapter ang ibinibigay sa isang maliit na PCBA. Ang mga sumusunod na adapter ay kasama:

Para sa karamihan ng mga layunin, maaaring gamitin ang 50-mil 10-pin IDC flat cable, kumokonekta sa alinman sa natively sa 10-pin o 6-pin connector nito, o kumokonekta sa pamamagitan ng adapter board. Tatlong adapter ang ibinibigay sa isang maliit na PCBA. Ang mga sumusunod na adapter ay kasama:

- 100-mil 10-pin JTAG/SWD adapter

- 100-mil 20-pin SAM JTAG/SWD adapter

- 50-mil 6-pin SPI/debugWIRE/PDI/aWire adapter

Larawan 2-8. Mga Adapter ng Atmel-ICE Tandaan:

Tandaan:

Isang 50-mil JTAG hindi ibinigay ang adapter – ito ay dahil ang 50-mil 10-pin IDC cable ay maaaring gamitin upang direktang kumonekta sa isang 50-mil JTAG header. Para sa part number ng component na ginamit para sa 50-mil 10-pin connector, tingnan ang Atmel-ICE Target Connectors Part Numbers.

Ang 6-pin na ISP/PDI header ay kasama bilang bahagi ng 10-pin IDC cable. Ang pagwawakas na ito ay maaaring putulin kung hindi ito kinakailangan.

Upang i-assemble ang iyong Atmel-ICE sa default na configuration nito, ikonekta ang 10-pin 50-mil IDC cable sa unit tulad ng ipinapakita sa ibaba. Siguraduhing i-orient ang cable upang ang pulang wire (pin 1) sa cable ay nakahanay sa triangular indicator sa asul na sinturon ng enclosure. Ang cable ay dapat kumonekta paitaas mula sa yunit. Tiyaking kumonekta sa port na tumutugma sa pinout ng iyong target - AVR o SAM.

Larawan 2-9. Koneksyon ng Atmel-ICE Cable Larawan 2-10. Koneksyon ng Atmel-ICE AVR Probe

Larawan 2-10. Koneksyon ng Atmel-ICE AVR Probe

Larawan 2-11. Koneksyon ng Atmel-ICE SAM Probe

Larawan 2-11. Koneksyon ng Atmel-ICE SAM Probe 2.7. Binuksan ang Atmel-ICE

2.7. Binuksan ang Atmel-ICE

Tandaan:

Para sa normal na operasyon, hindi dapat buksan ang unit ng Atmel-ICE. Ang pagbubukas ng yunit ay ginagawa sa iyong sariling peligro.

Dapat gawin ang mga anti-static na pag-iingat.

Binubuo ang Atmel-ICE enclosure ng tatlong magkahiwalay na bahagi ng plastic – takip sa itaas, takip sa ibaba, at asul na sinturon – na pinagsasama-sama sa panahon ng pagpupulong. Para buksan ang unit, ipasok lang ang isang malaking flat screwdriver sa mga butas sa asul na sinturon, ilapat ang ilang papasok na presyon at i-twist nang malumanay. Ulitin ang proseso sa iba pang mga butas ng snapper, at lalabas ang tuktok na takip.

Larawan 2-12. Pagbubukas ng Atmel-ICE (1)

Larawan 2-13. Pagbubukas ng Atmel-ICE (2)

Larawan 2-13. Pagbubukas ng Atmel-ICE (2)

Larawan 2-14. Pagbubukas ng Atmel-ICE(3)

Larawan 2-14. Pagbubukas ng Atmel-ICE(3) Upang isara muli ang unit, ihanay lang nang tama ang tuktok at ibabang mga takip, at pindutin nang mahigpit nang magkasabay.

Upang isara muli ang unit, ihanay lang nang tama ang tuktok at ibabang mga takip, at pindutin nang mahigpit nang magkasabay.

2.8. Pinapagana ang Atmel-ICE

Ang Atmel-ICE ay pinapagana ng USB bus voltage. Nangangailangan ito ng mas mababa sa 100mA upang gumana, at samakatuwid ay maaaring paganahin sa pamamagitan ng USB hub. Mag-iilaw ang power LED kapag nakasaksak ang unit. Kapag hindi nakakonekta sa isang aktibong programming o debugging session, papasok ang unit sa low-power consumption mode upang mapanatili ang baterya ng iyong computer. Ang Atmel-ICE ay hindi maaaring patayin - dapat itong i-unplug kapag hindi ginagamit.

2.9. Pagkonekta sa Host Computer

Ang Atmel-ICE ay pangunahing nakikipag-usap gamit ang isang karaniwang HID interface, at hindi nangangailangan ng isang espesyal na driver sa host computer. Para magamit ang advanced na Data Gateway functionality ng Atmel-ICE, tiyaking i-install ang USB driver sa host computer. Awtomatiko itong ginagawa kapag ini-install ang front-end na software na ibinigay ng Atmel nang libre. Tingnan mo www.atmel.com para sa karagdagang impormasyon o upang i-download ang pinakabagong front-end na software.

Ang Atmel-ICE ay dapat na konektado sa isang available na USB port sa host computer gamit ang ibinigay na USB cable, o angkop na USB certified micro cable. Ang Atmel-ICE ay naglalaman ng USB 2.0 compliant controller, at maaaring gumana sa parehong full-speed at high-speed mode. Para sa pinakamahusay na mga resulta, direktang ikonekta ang Atmel-ICE sa isang USB 2.0 compliant high-speed hub sa host computer gamit ang ibinigay na cable.

2.10. Pag-install ng USB Driver

2.10.1. Windows

Kapag ini-install ang Atmel-ICE sa isang computer na nagpapatakbo ng Microsoft® Windows® , ang USB driver ay na-load kapag ang Atmel-ICE ay unang nakasaksak.

Tandaan:

Tiyaking i-install ang mga front-end na software package bago isaksak ang unit sa unang pagkakataon.

Kapag matagumpay na na-install, lalabas ang Atmel-ICE sa device manager bilang isang "Human Interface Device".

Pagkonekta sa Atmel-ICE

3.1. Kumokonekta sa AVR at SAM Target na Mga Device

Ang Atmel-ICE ay nilagyan ng dalawang 50-mil 10-pin na JTAG mga konektor. Ang parehong mga konektor ay direktang konektado sa kuryente, ngunit umaayon sa dalawang magkaibang mga pinout; ang AVR JTAG header at ang ARM Cortex Debug header. Dapat piliin ang connector batay sa pinout ng target na board, at hindi sa target na uri ng MCU – para sa halampAng isang SAM device na naka-mount sa isang AVR STK® 600 stack ay dapat gumamit ng AVR header.

Available ang iba't ibang mga paglalagay ng kable at adapter sa iba't ibang mga Atmel-ICE kit. Isang taposview ng mga opsyon sa koneksyon ay ipinapakita.

Larawan 3-1. Mga Opsyon sa Koneksyon ng Atmel-ICE Ang pulang wire ay nagmamarka ng pin 1 ng 10-pin 50-mil connector. Ang pin 1 ng 6-pin 100-mil connector ay inilalagay sa kanan ng keying kapag ang connector ay nakikita mula sa cable. Ang pin 1 ng bawat connector sa adapter ay minarkahan ng puting tuldok. Ipinapakita ng figure sa ibaba ang pinout ng debug cable. Ang connector na may markang A ay nakasaksak sa debugger habang ang B na bahagi ay nakasaksak sa target na board.

Ang pulang wire ay nagmamarka ng pin 1 ng 10-pin 50-mil connector. Ang pin 1 ng 6-pin 100-mil connector ay inilalagay sa kanan ng keying kapag ang connector ay nakikita mula sa cable. Ang pin 1 ng bawat connector sa adapter ay minarkahan ng puting tuldok. Ipinapakita ng figure sa ibaba ang pinout ng debug cable. Ang connector na may markang A ay nakasaksak sa debugger habang ang B na bahagi ay nakasaksak sa target na board.

Larawan 3-2. Debug Cable Pinout

3.2. Kumokonekta sa isang JTAG Target

3.2. Kumokonekta sa isang JTAG Target

Ang Atmel-ICE ay nilagyan ng dalawang 50-mil 10-pin na JTAG mga konektor. Ang parehong mga konektor ay direktang konektado sa kuryente, ngunit umaayon sa dalawang magkaibang mga pinout; ang AVR JTAG header at ang ARM Cortex Debug header. Dapat piliin ang connector batay sa pinout ng target na board, at hindi sa target na uri ng MCU – para sa halampAng isang SAM device na naka-mount sa isang AVR STK600 stack ay dapat gumamit ng AVR header.

Ang inirerekomendang pinout para sa 10-pin na AVR JTAG connector ay ipinapakita sa Figure 4-6. Ang inirerekomendang pinout para sa 10-pin ARM Cortex Debug connector ay ipinapakita sa Figure 4-2.

Direktang koneksyon sa isang karaniwang 10-pin 50-mil na header

Gamitin ang 50-mil 10-pin flat cable (kasama sa ilang kit) para direktang kumonekta sa isang board na sumusuporta sa ganitong uri ng header. Gamitin ang AVR connector port sa Atmel-ICE para sa mga header na may AVR pinout, at ang SAM connector port para sa mga header na sumusunod sa ARM Cortex Debug header pinout.

Ang mga pinout para sa parehong 10-pin connector port ay ipinapakita sa ibaba.

Koneksyon sa isang karaniwang 10-pin 100-mil na header

Gumamit ng karaniwang 50-mil hanggang 100-mil na adaptor para kumonekta sa 100-mil na mga header. Maaaring gamitin ang adapter board (kasama sa ilang kit) para sa layuning ito, o bilang kahalili ang JTAGMaaaring gamitin ang ICE3 adapter para sa mga target ng AVR.

![]() Mahalaga:

Mahalaga:

Ang JTAGAng ICE3 100-mil adapter ay hindi magagamit sa SAM connector port, dahil ang mga pin 2 at 10 (AVR GND) sa adapter ay konektado.

Koneksyon sa isang custom na 100-mil na header

Kung ang iyong target na board ay walang sumusunod na 10-pin na JTAG header sa 50- o 100-mil, maaari kang mag-map sa isang custom na pinout gamit ang 10-pin na "mini-squid" cable (kasama sa ilang kit), na nagbibigay ng access sa sampung indibidwal na 100-mil socket.

Koneksyon sa isang 20-pin 100-mil header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa mga target na may 20-pin 100-mil na header.

Talahanayan 3-1. Atmel-ICE JTAG Paglalarawan ng Pin

| Pangalan | AVR port pin | SAM port pin | Paglalarawan |

| TCK | 1 | 4 | Pagsubok na Orasan (signal ng orasan mula sa Atmel-ICE papunta sa target na device). |

| TMS | 5 | 2 | Test Mode Select (control signal mula sa Atmel-ICE papunta sa target na device). |

| TDI | 9 | 8 | Test Data In (data na ipinadala mula sa Atmel-ICE papunta sa target na device). |

| TDO | 3 | 6 | Test Data Out (data na ipinadala mula sa target na device papunta sa Atmel-ICE). |

| nTRST | 8 | – | Test Reset (opsyonal, sa ilang AVR device lang). Ginamit upang i-reset ang JTAG TAP controller. |

| nSRST | 6 | 10 | I-reset (opsyonal). Ginagamit para i-reset ang target na device. Inirerekomenda ang pagkonekta sa pin na ito dahil pinapayagan nito ang Atmel-ICE na hawakan ang target na device sa isang estado ng pag-reset, na maaaring maging mahalaga sa pag-debug sa ilang partikular na sitwasyon. |

| VTG | 4 | 1 | Target voltage sanggunian. Ang Atmel-ICE samples ang target voltage sa pin na ito upang paganahin nang tama ang mga level converter. Ang Atmel-ICE ay kumukuha ng mas mababa sa 3mA mula sa pin na ito sa debugWIRE mode at mas mababa sa 1mA sa iba pang mga mode. |

| GND | 2, 10 | 3, 5, 9 | Lupa. Dapat na konektado ang lahat upang matiyak na ang Atmel-ICE at ang target na device ay nagbabahagi ng parehong ground reference. |

3.3. Pagkonekta sa isang aWire Target

Ang interface ng aWire ay nangangailangan lamang ng isang linya ng data bilang karagdagan sa VCC at GND. Sa target na linyang ito ay ang nRESET na linya, bagaman ginagamit ng debugger ang JTAG TDO line bilang linya ng data.

Ang inirerekomendang pinout para sa 6-pin aWire connector ay ipinapakita sa Figure 4-8.

Koneksyon sa isang 6-pin 100-mil aWire header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang standard na 100-mil aWire header.

Koneksyon sa isang 6-pin 50-mil aWire header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang karaniwang 50-mil aWire header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Tatlong koneksyon ang kinakailangan, tulad ng inilarawan sa talahanayan sa ibaba.

Talahanayan 3-2. Atmel-ICE aWire Pin Mapping

|

Atmel-ICE AVR port pin |

Mga target na pin | Mini-squid pin |

aWire pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (Hindi konektado) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.4. Pagkonekta sa isang PDI Target

Ang inirerekomendang pinout para sa 6-pin PDI connector ay ipinapakita sa Figure 4-11.

Koneksyon sa isang 6-pin 100-mil PDI header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang karaniwang 100-mil PDI header.

Koneksyon sa isang 6-pin 50-mil PDI header

Gamitin ang adapter board (kasama sa ilang kit) upang kumonekta sa isang karaniwang 50-mil na PDI header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Apat na koneksyon ang kailangan, gaya ng inilarawan sa talahanayan sa ibaba.

![]() Mahalaga:

Mahalaga:

Ang kinakailangang pinout ay iba sa JTAGICE mkII JTAG probe, kung saan nakakonekta ang PDI_DATA sa pin 9. Ang Atmel-ICE ay katugma sa pinout na ginamit ng Atmel-ICE, JTAGMga produkto ng ICE3, AVR ONE!, at AVR Dragon™.

Talahanayan 3-3. Atmel-ICE PDI Pin Mapping

| Atmel-ICE AVR port pin | Mga target na pin | Mini-squid pin |

aWire pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (Hindi konektado) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.4 Pagkonekta sa isang PDI Target

Ang inirerekomendang pinout para sa 6-pin PDI connector ay ipinapakita sa Figure 4-11.

Koneksyon sa isang 6-pin 100-mil PDI header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang karaniwang 100-mil PDI header.

Koneksyon sa isang 6-pin 50-mil PDI header

Gamitin ang adapter board (kasama sa ilang kit) upang kumonekta sa isang karaniwang 50-mil na PDI header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Apat na koneksyon ang kailangan, gaya ng inilarawan sa talahanayan sa ibaba.

![]() Mahalaga:

Mahalaga:

Ang kinakailangang pinout ay iba sa JTAGICE mkII JTAG probe, kung saan nakakonekta ang PDI_DATA sa pin 9. Ang Atmel-ICE ay katugma sa pinout na ginamit ng Atmel-ICE, JTAGICE3, AVR ONE!, at AVR Dragon™ mga produkto.

Talahanayan 3-3. Atmel-ICE PDI Pin Mapping

| Atmel-ICE AVR port pin | Mga target na pin | Mini-squid pin | Atmel STK600 PDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | PDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (hindi konektado) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.5 Pagkonekta sa isang Target ng UPDI

Ang inirerekomendang pinout para sa 6-pin na UPDI connector ay ipinapakita sa Figure 4-12.

Koneksyon sa isang 6-pin 100-mil UPDI header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang standard na 100-mil UPDI header.

Koneksyon sa isang 6-pin 50-mil UPDI header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang standard na 50-mil UPDI header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Tatlong koneksyon ang kinakailangan, tulad ng inilarawan sa talahanayan sa ibaba.

Talahanayan 3-4. Atmel-ICE UPDI Pin Mapping

| Atmel-ICE AVR port pin | Mga target na pin | Mini-squid pin |

Atmel STK600 UPDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | [/RESET sense] | 6 | 5 |

| Pin 7 (Hindi konektado) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.6 Pagkonekta sa isang debugWIRE Target

Ang inirerekomendang pinout para sa 6-pin debugWIRE (SPI) connector ay ipinapakita sa Talahanayan 3-6.

Koneksyon sa isang 6-pin 100-mil SPI header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang standard na 100-mil SPI header.

Koneksyon sa isang 6-pin 50-mil SPI header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang standard na 50-mil SPI header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Tatlong koneksyon ang kailangan, gaya ng inilarawan sa Talahanayan 3-5.

Bagama't ang interface ng debugWIRE ay nangangailangan lamang ng isang linya ng signal (RESET), ang VCC at GND upang gumana nang tama, pinapayuhan na magkaroon ng access sa buong SPI connector upang ang interface ng debugWIRE ay ma-enable at ma-disable gamit ang SPI programming.

Kapag ang DWEN fuse ay pinagana, ang interface ng SPI ay na-override sa loob upang ang OCD module ay magkaroon ng kontrol sa RESET pin. Ang debugWIRE OCD ay may kakayahang pansamantalang i-disable ang sarili nito (gamit ang button sa tab na pag-debug sa dialog ng mga katangian sa Atmel Studio), kaya inilalabas ang kontrol ng linya ng RESET. Ang interface ng SPI ay magagamit muli (lamang kung ang SPIEN fuse ay naka-program), na nagpapahintulot sa DWEN fuse na ma-unprogram gamit ang SPI interface. Kung i-toggle ang power bago ma-unprogram ang DWEN fuse, ang debugWIRE module ang muling kukuha ng kontrol sa RESET pin.

Tandaan:

Lubos na pinapayuhan na hayaan lang ang Atmel Studio na pangasiwaan ang setting at pag-clear ng DWEN fuse.

Hindi posibleng gamitin ang interface ng debugWIRE kung naka-program ang mga lockbit sa target na AVR device. Laging siguraduhin na ang mga lockbit ay na-clear bago i-program ang DWEN fuse at hindi kailanman itakda ang lockbits habang ang DWEN fuse ay naka-program. Kung parehong nakatakda ang debugWIRE enable fuse (DWEN) at lockbits, magagamit ng isa ang High Voltage Programming upang gawin ang isang chip bura, at sa gayon ay i-clear ang lockbits.

Kapag na-clear ang mga lockbit, muling papaganahin ang interface ng debugWIRE. Ang SPI Interface ay may kakayahan lamang na magbasa ng mga piyus, magbasa ng lagda at magsagawa ng pagbubura ng chip kapag ang DWEN fuse ay hindi nakaprograma.

Talahanayan 3-5. Atmel-ICE debugWIRE Pin Mapping

| Atmel-ICE AVR port pin | Mga target na pin |

Mini-squid pin |

| Pin 1 (TCK) | 1 | |

| Pin 2 (GND) | GND | 2 |

| Pin 3 (TDO) | 3 | |

| Pin 4 (VTG) | VTG | 4 |

| Pin 5 (TMS) | 5 | |

| Pin 6 (nSRST) | I-RESET | 6 |

| Pin 7 (Hindi konektado) | 7 | |

| Pin 8 (nTRST) | 8 | |

| Pin 9 (TDI) | 9 | |

| Pin 10 (GND) | 0 |

3.7 Pagkonekta sa isang Target ng SPI

Ang inirerekomendang pinout para sa 6-pin na SPI connector ay ipinapakita sa Figure 4-10.

Koneksyon sa isang 6-pin 100-mil SPI header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang standard na 100-mil SPI header.

Koneksyon sa isang 6-pin 50-mil SPI header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang standard na 50-mil SPI header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Anim na koneksyon ang kinakailangan, tulad ng inilarawan sa talahanayan sa ibaba.

![]() Mahalaga:

Mahalaga:

Ang interface ng SPI ay epektibong hindi pinagana kapag ang debugWIRE enable fuse (DWEN) ay na-program, kahit na ang SPIEN fuse ay naka-program din. Upang muling paganahin ang interface ng SPI, ang command na 'disable debugWIRE' ay dapat na ibigay habang nasa isang debugWIRE debugging session. Ang hindi pagpapagana ng debugWIRE sa ganitong paraan ay nangangailangan na ang SPIEN fuse ay naka-program na. Kung nabigo ang Atmel Studio na i-disable ang debugWIRE, malamang dahil HINDI naka-program ang SPIEN fuse. Kung ito ang kaso, kinakailangang gumamit ng high-voltage programming interface upang i-program ang SPIEN fuse.

![]() impormasyon:

impormasyon:

Ang interface ng SPI ay madalas na tinutukoy bilang "ISP", dahil ito ang unang In System Programming interface sa mga produkto ng Atmel AVR. Available na ngayon ang iba pang mga interface para sa In System Programming.

Talahanayan 3-6. Atmel-ICE SPI Pin Mapping

| Atmel-ICE AVR port pin | Mga target na pin | Mini-squid pin |

SPI pinout |

| Pin 1 (TCK) | SCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | MISO | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | / I-reset | 6 | 5 |

| Pin 7 (hindi konektado) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | DAWDLE | 9 | 4 |

| Pin 10 (GND) | 0 |

3.8 Pagkonekta sa isang Target ng TPI

Ang inirerekomendang pinout para sa 6-pin TPI connector ay ipinapakita sa Figure 4-13.

Koneksyon sa isang 6-pin 100-mil TPI header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang standard na 100-mil TPI header.

Koneksyon sa isang 6-pin 50-mil TPI header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang karaniwang 50-mil TPI header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Anim na koneksyon ang kinakailangan, tulad ng inilarawan sa talahanayan sa ibaba.

Talahanayan 3-7. Atmel-ICE TPI Pin Mapping

| Atmel-ICE AVR port pin | Mga target na pin | Mini-squid pin |

TPI pinout |

| Pin 1 (TCK) | Orasan | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 |

| Pin 6 (nSRST) | / I-reset | 6 | 5 |

| Pin 7 (hindi konektado) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

3.9 Pagkonekta sa isang Target ng SWD

Ang interface ng ARM SWD ay isang subset ng JTAG interface, gamit ang TCK at TMS pin, na nangangahulugang kapag kumokonekta sa isang SWD device, ang 10-pin JTAG maaaring teknikal na gamitin ang connector. Ang ARM JTAG at AVR JTAG Ang mga konektor ay, gayunpaman, ay hindi tugma sa pin, kaya depende ito sa layout ng target na board na ginagamit. Kapag gumagamit ng STK600 o board na gumagamit ng AVR JTAG pinout, dapat gamitin ang AVR connector port sa Atmel-ICE. Kapag kumokonekta sa isang board, na gumagamit ng ARM JTAG pinout, dapat gamitin ang SAM connector port sa Atmel-ICE.

Ang inirerekomendang pinout para sa 10-pin Cortex Debug connector ay ipinapakita sa Figure 4-4.

Koneksyon sa isang 10-pin 50-mil Cortex header

Gamitin ang flat cable (kasama sa ilang kit) para kumonekta sa isang karaniwang 50-mil Cortex header.

Koneksyon sa isang 10-pin 100-mil Cortex-layout header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang 100-mil Cortex-pinout header.

Koneksyon sa isang 20-pin 100-mil SAM header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang 20-pin 100-mil SAM header.

Koneksyon sa isang custom na 100-mil na header

Dapat gamitin ang 10-pin na mini-squid cable para kumonekta sa pagitan ng Atmel-ICE AVR o SAM connector port at ng target board. Anim na koneksyon ang kinakailangan, tulad ng inilarawan sa talahanayan sa ibaba.

Talahanayan 3-8. Atmel-ICE SWD Pin Mapping

| Pangalan | AVR port pin | SAM port pin | Paglalarawan |

| SWDC LK | 1 | 4 | Serial Wire Debug Clock. |

| SWIDIO | 5 | 2 | Serial Wire Debug Data Input/Output. |

| SWO | 3 | 6 | Serial Wire Output (opsyonal- hindi ipinatupad sa lahat ng device). |

| nSRST | 6 | 10 | I-reset. |

| VTG | 4 | 1 | Target voltage sanggunian. |

| GND | 2, 10 | 3, 5, 9 | Lupa. |

3.10 Pagkonekta sa Data Gateway Interface

Sinusuportahan ng Atmel-ICE ang limitadong Data Gateway Interface (DGI) kapag hindi ginagamit ang pag-debug at programming. Ang functionality ay kapareho ng makikita sa Atmel Xplained Pro kit na pinapagana ng Atmel EDBG device.

Ang Data Gateway Interface ay isang interface para sa pag-stream ng data mula sa target na device patungo sa isang computer. Ito ay sinadya bilang tulong sa pag-debug ng application pati na rin para sa pagpapakita ng mga feature sa application na tumatakbo sa target na device.

Ang DGI ay binubuo ng maraming channel para sa data streaming. Sinusuportahan ng Atmel-ICE ang mga sumusunod na mode:

- USART

- SPI

Talahanayan 3-9. Atmel-ICE DGI USART Pinout

|

AVR port |

SAM port | DGI USART pin |

Paglalarawan |

| 3 | 6 | TX | Ipadala ang pin mula sa Atmel-ICE patungo sa target na device |

| 4 | 1 | VTG | Target voltage (sanggunian voltage) |

| 8 | 7 | RX | Tumanggap ng pin mula sa target na device patungo sa Atmel-ICE |

| 9 | 8 | CLK | USART orasan |

| 2, 10 | 3, 5, 9 | GND | Lupa |

Talahanayan 3-10. Atmel-ICE DGI SPI Pinout

|

AVR port |

SAM port | DGI SPI pin |

Paglalarawan |

| 1 | 4 | SCK | SPI orasan |

| 3 | 6 | MISO | Master In Slave Out |

| 4 | 1 | VTG | Target voltage (sanggunian voltage) |

| 5 | 2 | nCS | Chip piliin ang aktibong mababa |

| 9 | 8 | DAWDLE | Master Out Alipin Sa |

| 2, 10 | 3, 5, 9 | GND | Lupa |

![]() Mahalaga: Ang mga interface ng SPI at USART ay hindi maaaring gamitin nang sabay.

Mahalaga: Ang mga interface ng SPI at USART ay hindi maaaring gamitin nang sabay.

![]() Mahalaga: Ang DGI at programming o pag-debug ay hindi maaaring gamitin nang sabay-sabay.

Mahalaga: Ang DGI at programming o pag-debug ay hindi maaaring gamitin nang sabay-sabay.

On-chip Debugging

4.1 Panimula

On-chip Debugging

Ang on-chip debug module ay isang system na nagpapahintulot sa isang developer na subaybayan at kontrolin ang execution sa isang device mula sa isang external na platform ng pag-develop, kadalasan sa pamamagitan ng isang device na kilala bilang isang debugger o debug adapter.

Sa isang OCD system ang application ay maaaring isagawa habang pinapanatili ang eksaktong mga katangian ng elektrikal at timing sa target na sistema, habang nagagawang ihinto ang pagpapatupad nang may kondisyon o manu-mano at sinisiyasat ang daloy ng programa at memorya.

Run Mode

Kapag nasa Run mode, ang execution ng code ay ganap na independiyente sa Atmel-ICE. Patuloy na susubaybayan ng Atmel-ICE ang target na device upang makita kung may nangyaring break condition. Kapag nangyari ito, itatanong ng OCD system ang device sa pamamagitan ng interface ng debug nito, na magbibigay-daan sa user view ang panloob na estado ng device.

Huminto ang Mode

Kapag naabot ang isang breakpoint, ihihinto ang pagpapatupad ng programa, ngunit maaaring patuloy na tumakbo ang ilang I/O na parang walang naganap na breakpoint. Para kay example, ipagpalagay na ang isang USART transmit ay sinimulan lamang kapag naabot ang isang breakpoint. Sa kasong ito ang USART ay patuloy na tumatakbo sa buong bilis na nakumpleto ang paghahatid, kahit na ang core ay nasa stop mode.

Mga Breakpoint ng Hardware

Ang target na OCD module ay naglalaman ng isang bilang ng mga program counter comparator na ipinatupad sa hardware. Kapag ang program counter ay tumugma sa halagang nakaimbak sa isa sa mga comparator register, ang OCD ay papasok sa stop mode. Dahil ang mga breakpoint ng hardware ay nangangailangan ng dedikadong hardware sa OCD module, ang bilang ng mga breakpoint na available ay depende sa laki ng OCD module na ipinatupad sa target. Karaniwan ang isang naturang hardware comparator ay 'nakareserba' ng debugger para sa panloob na paggamit.

Mga Breakpoint ng Software

Ang software breakpoint ay isang BREAK na pagtuturo na inilagay sa memory ng program sa target na device. Kapag na-load ang pagtuturo na ito, masisira ang pagpapatupad ng programa at ang OCD ay papasok sa stop mode. Upang ipagpatuloy ang pagpapatupad ng isang "simula" na utos ay kailangang ibigay mula sa OCD. Hindi lahat ng Atmel device ay may mga OCD module na sumusuporta sa BREAK na pagtuturo.

4.2 Mga SAM Device na may JTAG/SWD

Nagtatampok ang lahat ng SAM device ng interface ng SWD para sa programming at pag-debug. Bilang karagdagan, ang ilang SAM device ay nagtatampok ng JTAG interface na may magkaparehong pag-andar. Suriin ang datasheet ng device para sa mga sinusuportahang interface ng device na iyon.

4.2.1.Mga Bahagi ng ARM CoreSight

Ang mga microcontroller na nakabase sa Atmel ARM Cortex-M ay nagpapatupad ng mga bahagi ng OCD na sumusunod sa CoreSight. Maaaring mag-iba ang mga feature ng mga bahaging ito sa bawat device. Para sa karagdagang impormasyon kumonsulta sa datasheet ng device pati na rin ang dokumentasyon ng CoreSight na ibinigay ng ARM.

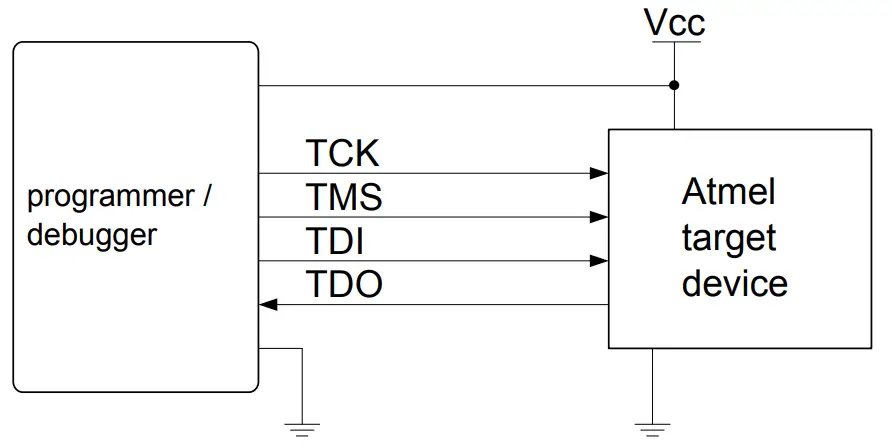

4.2.1. JTAG Pisikal na Interface

Ang JTAG ang interface ay binubuo ng isang 4-wire Test Access Port (TAP) controller na sumusunod sa IEEE® 1149.1 pamantayan. Ang pamantayang IEEE ay binuo upang magbigay ng isang pamantayang pang-industriya na paraan upang mahusay na masuri ang pagkakakonekta ng circuit board (Boundary Scan). Pinalawak ng mga Atmel AVR at SAM na device ang functionality na ito para isama ang buong Programming at On-chip Debugging na suporta.

Larawan 4-1. JTAG Mga Pangunahing Kaalaman sa Interface

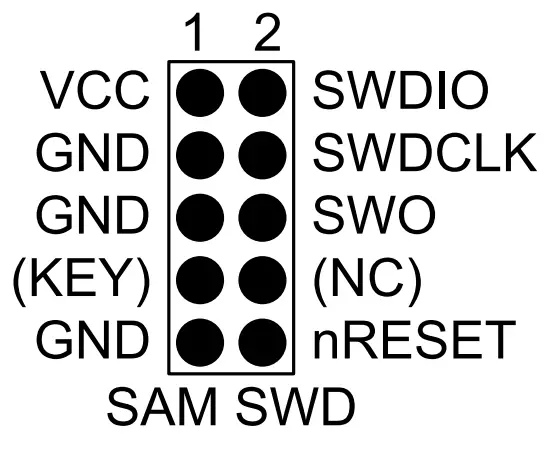

4.2.2.1 SAM JTAG Pinout (Cortex-M debug connector)

Kapag nagdidisenyo ng isang application PCB na may kasamang Atmel SAM na may JTAG interface, inirerekumenda na gamitin ang pinout tulad ng ipinapakita sa figure sa ibaba. Parehong sinusuportahan ang 100-mil at 50-mil na variant ng pinout na ito, depende sa paglalagay ng kable at mga adapter na kasama sa partikular na kit.

Larawan 4-2. SAM JTAG Pinout ng Header

Talahanayan 4-1. SAM JTAG Paglalarawan ng Pin

| Pangalan | Pin |

Paglalarawan |

| TCK | 4 | Pagsubok na Orasan (signal ng orasan mula sa Atmel-ICE papunta sa target na device). |

| TMS | 2 | Test Mode Select (control signal mula sa Atmel-ICE papunta sa target na device). |

| TDI | 8 | Test Data In (data na ipinadala mula sa Atmel-ICE papunta sa target na device). |

| TDO | 6 | Test Data Out (data na ipinadala mula sa target na device papunta sa Atmel-ICE). |

| nRESET | 10 | I-reset (opsyonal). Ginagamit para i-reset ang target na device. Inirerekomenda ang pagkonekta sa pin na ito dahil pinapayagan nito ang Atmel-ICE na hawakan ang target na device sa isang estado ng pag-reset, na maaaring maging mahalaga sa pag-debug sa ilang partikular na sitwasyon. |

| VTG | 1 | Target voltage sanggunian. Ang Atmel-ICE samples ang target voltage sa pin na ito upang paganahin nang tama ang mga level converter. Ang Atmel-ICE ay kumukuha ng mas mababa sa 1mA mula sa pin na ito sa mode na ito. |

| GND | 3, 5, 9 | Lupa. Dapat na konektado ang lahat upang matiyak na ang Atmel-ICE at ang target na device ay nagbabahagi ng parehong ground reference. |

| SUSI | 7 | Nakakonekta sa loob sa TRST pin sa AVR connector. Inirerekomenda bilang hindi konektado. |

![]() Tip: Tandaan na magsama ng decoupling capacitor sa pagitan ng pin 1 at GND.

Tip: Tandaan na magsama ng decoupling capacitor sa pagitan ng pin 1 at GND.

4.2.2.2 JTAG Daisy Pagkakadena

Ang JTAG interface ay nagbibigay-daan para sa ilang mga aparato na konektado sa isang solong interface sa isang daisy chain configuration. Ang mga target na device ay dapat lahat ay pinapagana ng parehong supply voltage, magbahagi ng common ground node, at dapat na konektado gaya ng ipinapakita sa figure sa ibaba.

Larawan 4-3. JTAG Daisy Chain

Kapag nagkokonekta ng mga device sa isang daisy chain, dapat isaalang-alang ang mga sumusunod na punto:

- Ang lahat ng mga device ay dapat magbahagi ng isang karaniwang lupa, na konektado sa GND sa Atmel-ICE probe

- Ang lahat ng mga aparato ay dapat na gumagana sa parehong target voltage. Ang VTG sa Atmel-ICE ay dapat na konektado sa vol na itotage.

- TMS at TCK ay konektado sa parallel; Ang TDI at TDO ay konektado sa isang serial

- Dapat na konektado ang nSRST sa Atmel-ICE probe sa RESET sa mga device kung ang alinman sa mga device sa chain ay hindi pinagana ang J nito.TAG daungan

- Ang "mga device dati" ay tumutukoy sa bilang ng JTAG mga device na kailangang dumaan ng signal ng TDI sa daisy chain bago maabot ang target na device. Katulad nito, ang “devices after” ay ang bilang ng mga device na kailangang dumaan ng signal pagkatapos ng target na device bago maabot ang Atmel-ICE TDO

- Ang "mga bit ng tagubilin "bago" at "pagkatapos" ay tumutukoy sa kabuuang kabuuan ng lahat ng JTAG mga haba ng rehistro ng pagtuturo ng mga device, na konektado bago at pagkatapos ng target na device sa daisy chain

- Ang kabuuang haba ng IR (mga bit ng tagubilin bago + haba ng IR ng target na device ng Atmel + mga bit ng pagtuturo pagkatapos) ay limitado sa maximum na 256 bit. Ang bilang ng mga device sa chain ay limitado sa 15 bago at 15 pagkatapos.

![]() Tip:

Tip:

Daisy chaining example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Upang kumonekta sa Atmel AVR XMEGA® device, ang mga setting ng daisy chain ay:

- Mga device bago: 1

- Mga device pagkatapos ng: 1

- Instruction bits bago: 4 (8-bit AVR device has 4 IR bits)

- Instruction bits pagkatapos ng: 5 (32-bit AVR device ay may 5 IR bits)

Talahanayan 4-2. IR Haba ng Atmel MCUs

| Uri ng device | haba ng IR |

| AVR 8-bit | 4 bits |

| AVR 32-bit | 5 bits |

| SAM | 4 bits |

4.2.3. Kumokonekta sa isang JTAG Target

Ang Atmel-ICE ay nilagyan ng dalawang 50-mil 10-pin na JTAG mga konektor. Ang parehong mga konektor ay direktang konektado sa kuryente, ngunit umaayon sa dalawang magkaibang mga pinout; ang AVR JTAG header at ang ARM Cortex Debug header. Dapat piliin ang connector batay sa pinout ng target na board, at hindi sa target na uri ng MCU – para sa halampAng isang SAM device na naka-mount sa isang AVR STK600 stack ay dapat gumamit ng AVR header.

Ang inirerekomendang pinout para sa 10-pin na AVR JTAG connector ay ipinapakita sa Figure 4-6.

Ang inirerekomendang pinout para sa 10-pin ARM Cortex Debug connector ay ipinapakita sa Figure 4-2.

Direktang koneksyon sa isang karaniwang 10-pin 50-mil na header

Gamitin ang 50-mil 10-pin flat cable (kasama sa ilang kit) para direktang kumonekta sa isang board na sumusuporta sa ganitong uri ng header. Gamitin ang AVR connector port sa Atmel-ICE para sa mga header na may AVR pinout, at ang SAM connector port para sa mga header na sumusunod sa ARM Cortex Debug header pinout.

Ang mga pinout para sa parehong 10-pin connector port ay ipinapakita sa ibaba.

Koneksyon sa isang karaniwang 10-pin 100-mil na header

Gumamit ng karaniwang 50-mil hanggang 100-mil na adaptor para kumonekta sa 100-mil na mga header. Maaaring gamitin ang adapter board (kasama sa ilang kit) para sa layuning ito, o bilang kahalili ang JTAGMaaaring gamitin ang ICE3 adapter para sa mga target ng AVR.

![]() Mahalaga:

Mahalaga:

Ang JTAGAng ICE3 100-mil adapter ay hindi magagamit sa SAM connector port, dahil ang mga pin 2 at 10 (AVR GND) sa adapter ay konektado.

Koneksyon sa isang custom na 100-mil na header

Kung ang iyong target na board ay walang sumusunod na 10-pin na JTAG header sa 50- o 100-mil, maaari kang mag-map sa isang custom na pinout gamit ang 10-pin na "mini-squid" cable (kasama sa ilang kit), na nagbibigay ng access sa sampung indibidwal na 100-mil socket.

Koneksyon sa isang 20-pin na 100-mil na header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa mga target na may 20-pin 100-mil na header.

Talahanayan 4-3. Atmel-ICE JTAG Paglalarawan ng Pin

| Pangalan | AVR port pin | SAM port pin | Paglalarawan |

| TCK | 1 | 4 | Pagsubok na Orasan (signal ng orasan mula sa Atmel-ICE papunta sa target na device). |

| TMS | 5 | 2 | Test Mode Select (control signal mula sa Atmel-ICE papunta sa target na device). |

| TDI | 9 | 8 | Test Data In (data na ipinadala mula sa Atmel-ICE papunta sa target na device). |

| TDO | 3 | 6 | Test Data Out (data na ipinadala mula sa target na device papunta sa Atmel-ICE). |

| nTRST | 8 | – | Test Reset (opsyonal, sa ilang AVR device lang). Ginamit upang i-reset ang JTAG TAP controller. |

| nSRST | 6 | 10 | I-reset (opsyonal). Ginagamit para i-reset ang target na device. Inirerekomenda ang pagkonekta sa pin na ito dahil pinapayagan nito ang Atmel-ICE na hawakan ang target na device sa isang estado ng pag-reset, na maaaring maging mahalaga sa pag-debug sa ilang partikular na sitwasyon. |

| VTG | 4 | 1 | Target voltage sanggunian. Ang Atmel-ICE samples ang target voltage sa pin na ito upang paganahin nang tama ang mga level converter. Ang Atmel-ICE ay kumukuha ng mas mababa sa 3mA mula sa pin na ito sa debugWIRE mode at mas mababa sa 1mA sa iba pang mga mode. |

| GND | 2, 10 | 3, 5, 9 | Lupa. Dapat na konektado ang lahat upang matiyak na ang Atmel-ICE at ang target na device ay nagbabahagi ng parehong ground reference. |

4.2.4. Pisikal na Interface ng SWD

Ang interface ng ARM SWD ay isang subset ng JTAG interface, gamit ang mga TCK at TMS pin. Ang ARM JTAG at AVR JTAG ang mga konektor, gayunpaman, ay hindi tugma sa pin, kaya kapag nagdidisenyo ng isang application PCB, na gumagamit ng SAM device na may SWD o JTAG interface, inirerekomendang gamitin ang ARM pinout na ipinapakita sa figure sa ibaba. Ang SAM connector port sa Atmel-ICE ay maaaring direktang kumonekta sa pinout na ito.

Larawan 4-4. Inirerekomenda ang ARM SWD/JTAG Pinout ng Header

Ang Atmel-ICE ay may kakayahang mag-stream ng UART-format na ITM trace sa host computer. Nakukuha ang bakas sa TRACE/SWO pin ng 10-pin na header (JTAG TDO pin). Ang data ay nasa loob ng buffer sa Atmel-ICE at ipinapadala sa HID interface sa host computer. Ang maximum na maaasahang rate ng data ay humigit-kumulang 3MB/s.

4.2.5. Pagkonekta sa isang SWD Target

Ang interface ng ARM SWD ay isang subset ng JTAG interface, gamit ang TCK at TMS pin, na nangangahulugang kapag kumokonekta sa isang SWD device, ang 10-pin JTAG maaaring teknikal na gamitin ang connector. Ang ARM JTAG at AVR JTAG Ang mga konektor ay, gayunpaman, ay hindi tugma sa pin, kaya depende ito sa layout ng target na board na ginagamit. Kapag gumagamit ng STK600 o board na gumagamit ng AVR JTAG pinout, dapat gamitin ang AVR connector port sa Atmel-ICE. Kapag kumokonekta sa isang board, na gumagamit ng ARM JTAG pinout, dapat gamitin ang SAM connector port sa Atmel-ICE.

Ang inirerekomendang pinout para sa 10-pin Cortex Debug connector ay ipinapakita sa Figure 4-4.

Koneksyon sa isang 10-pin 50-mil Cortex header

Gamitin ang flat cable (kasama sa ilang kit) para kumonekta sa isang karaniwang 50-mil Cortex header.

Koneksyon sa isang 10-pin 100-mil Cortex-layout header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang 100-mil Cortex-pinout header.

Koneksyon sa isang 20-pin 100-mil SAM header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang 20-pin 100-mil SAM header.

Koneksyon sa isang custom na 100-mil na header

Dapat gamitin ang 10-pin na mini-squid cable para kumonekta sa pagitan ng Atmel-ICE AVR o SAM connector port at ng target board. Anim na koneksyon ang kinakailangan, tulad ng inilarawan sa talahanayan sa ibaba.

Talahanayan 4-4. Atmel-ICE SWD Pin Mapping

| Pangalan | AVR port pin | SAM port pin | Paglalarawan |

| SWDC LK | 1 | 4 | Serial Wire Debug Clock. |

| SWIDIO | 5 | 2 | Serial Wire Debug Data Input/Output. |

| SWO | 3 | 6 | Serial Wire Output (opsyonal- hindi ipinatupad sa lahat ng device). |

| nSRST | 6 | 10 | I-reset. |

| VTG | 4 | 1 | Target voltage sanggunian. |

| GND | 2, 10 | 3, 5, 9 | Lupa. |

4.2.6 Mga Espesyal na Pagsasaalang-alang

Burahin ang pin

Ang ilang SAM device ay may kasamang ERASE pin na iginiit na magsagawa ng kumpletong pagbubura ng chip at pag-unlock ng mga device kung saan nakatakda ang security bit. Ang feature na ito ay isinama sa mismong device pati na rin sa flash controller at hindi bahagi ng ARM core.

Ang ERASE pin ay HINDI bahagi ng anumang debug header, at sa gayon ang Atmel-ICE ay hindi maigigiit ang signal na ito upang i-unlock ang isang device. Sa ganitong mga kaso, dapat manu-manong isagawa ng user ang pagbura bago magsimula ng session ng pag-debug.

Mga pisikal na interface JTAG interface

Ang linya ng RESET ay dapat palaging konektado upang mapagana ng Atmel-ICE ang JTAG interface.

Interface ng SWD

Ang linya ng RESET ay dapat palaging konektado upang ma-enable ng Atmel-ICE ang interface ng SWD.

4.3 AVR UC3 Device na may JTAG/isang wire

Nagtatampok ang lahat ng AVR UC3 device ng JTAG interface para sa programming at debugging. Bilang karagdagan, nagtatampok ang ilang AVR UC3 device ng interface ng aWire na may magkaparehong functionality gamit ang isang wire. Suriin ang datasheet ng device para sa mga sinusuportahang interface ng device na iyon

4.3.1 Atmel AVR UC3 On-chip Debug System

Ang Atmel AVR UC3 OCD system ay idinisenyo alinsunod sa Nexus 2.0 standard (IEEE-ISTO 5001™-2003), na isang napaka-flexible at mahusay na open on-chip debug standard para sa 32-bit microcontrollers. Sinusuportahan nito ang mga sumusunod na tampok:

- Solusyon sa pag-debug na sumusunod sa Nexus

- Sinusuportahan ng OCD ang anumang bilis ng CPU

- Anim na program counter hardware breakpoints

- Dalawang breakpoint ng data

- Maaaring i-configure ang mga breakpoint bilang mga watchpoint

- Maaaring pagsamahin ang mga breakpoint ng hardware upang magbigay ng break sa mga hanay

- Walang limitasyong bilang ng mga breakpoint ng user program (gamit ang BREAK)

- Real-time na program counter branch tracing, data trace, process trace (sinusuportahan lang ng mga debugger na may parallel trace capture port)

Para sa karagdagang impormasyon tungkol sa AVR UC3 OCD system, kumonsulta sa AVR32UC Technical Reference Manuals, na matatagpuan sa www.atmel.com/uc3.

4.3.2. JTAG Pisikal na Interface

Ang JTAG ang interface ay binubuo ng isang 4-wire Test Access Port (TAP) controller na sumusunod sa IEEE® 1149.1 pamantayan. Ang pamantayang IEEE ay binuo upang magbigay ng isang pamantayang pang-industriya na paraan upang mahusay na masuri ang pagkakakonekta ng circuit board (Boundary Scan). Pinalawak ng mga Atmel AVR at SAM na device ang functionality na ito para isama ang buong Programming at On-chip Debugging na suporta.

Larawan 4-5. JTAG Mga Pangunahing Kaalaman sa Interface

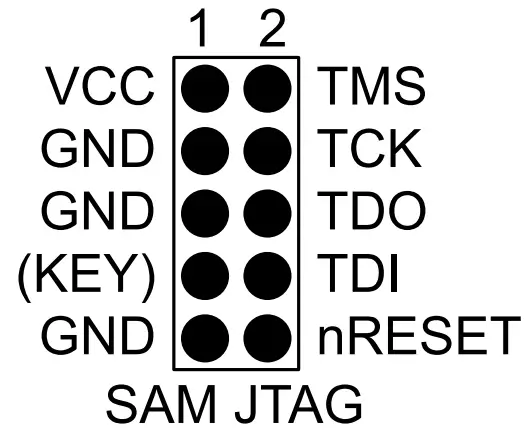

4.3.2.1 AVR JTAG Pinout

Kapag nagdidisenyo ng isang application PCB, na kinabibilangan ng Atmel AVR na may JTAG interface, inirerekumenda na gamitin ang pinout tulad ng ipinapakita sa figure sa ibaba. Parehong sinusuportahan ang 100-mil at 50-mil na variant ng pinout na ito, depende sa paglalagay ng kable at mga adapter na kasama sa partikular na kit.

Larawan 4-6. AVR JTAG Pinout ng Header

mesa 4-5. AVR JTAG Paglalarawan ng Pin

| Pangalan | Pin |

Paglalarawan |

| TCK | 1 | Pagsubok na Orasan (signal ng orasan mula sa Atmel-ICE papunta sa target na device). |

| TMS | 5 | Test Mode Select (control signal mula sa Atmel-ICE papunta sa target na device). |

| TDI | 9 | Test Data In (data na ipinadala mula sa Atmel-ICE papunta sa target na device). |

| TDO | 3 | Test Data Out (data na ipinadala mula sa target na device papunta sa Atmel-ICE). |

| nTRST | 8 | Test Reset (opsyonal, sa ilang AVR device lang). Ginamit upang i-reset ang JTAG TAP controller. |

| nSRST | 6 | I-reset (opsyonal). Ginagamit para i-reset ang target na device. Inirerekomenda ang pagkonekta sa pin na ito dahil pinapayagan nito ang Atmel-ICE na hawakan ang target na device sa isang estado ng pag-reset, na maaaring maging mahalaga sa pag-debug sa ilang partikular na sitwasyon. |

| VTG | 4 | Target voltage sanggunian. Ang Atmel-ICE samples ang target voltage sa pin na ito upang paganahin nang tama ang mga level converter. Ang Atmel-ICE ay kumukuha ng mas mababa sa 3mA mula sa pin na ito sa debugWIRE mode at mas mababa sa 1mA sa iba pang mga mode. |

| GND | 2, 10 | Lupa. Parehong dapat na konektado upang matiyak na ang Atmel-ICE at ang target na device ay nagbabahagi ng parehong ground reference. |

![]() Tip: Tandaan na magsama ng decoupling capacitor sa pagitan ng pin 4 at GND.

Tip: Tandaan na magsama ng decoupling capacitor sa pagitan ng pin 4 at GND.

4.3.2.2 JTAG Daisy Pagkakadena

Ang JTAG interface ay nagbibigay-daan para sa ilang mga aparato na konektado sa isang solong interface sa isang daisy chain configuration. Ang mga target na device ay dapat lahat ay pinapagana ng parehong supply voltage, magbahagi ng common ground node, at dapat na konektado gaya ng ipinapakita sa figure sa ibaba.

Larawan 4-7. JTAG Daisy Chain

Kapag nagkokonekta ng mga device sa isang daisy chain, dapat isaalang-alang ang mga sumusunod na punto:

- Ang lahat ng mga device ay dapat magbahagi ng isang karaniwang lupa, na konektado sa GND sa Atmel-ICE probe

- Ang lahat ng mga aparato ay dapat na gumagana sa parehong target voltage. Ang VTG sa Atmel-ICE ay dapat na konektado sa vol na itotage.

- TMS at TCK ay konektado sa parallel; Ang TDI at TDO ay konektado sa isang serial chain.

- Dapat na konektado ang nSRST sa Atmel-ICE probe sa RESET sa mga device kung ang alinman sa mga device sa chain ay hindi pinagana ang J nito.TAG daungan

- Ang "mga device dati" ay tumutukoy sa bilang ng JTAG mga device na kailangang dumaan ng signal ng TDI sa daisy chain bago maabot ang target na device. Katulad nito, ang “devices after” ay ang bilang ng mga device na kailangang dumaan ng signal pagkatapos ng target na device bago maabot ang Atmel-ICE TDO

- Ang "mga bit ng tagubilin "bago" at "pagkatapos" ay tumutukoy sa kabuuang kabuuan ng lahat ng JTAG mga haba ng rehistro ng pagtuturo ng mga device, na konektado bago at pagkatapos ng target na device sa daisy chain

- Ang kabuuang haba ng IR (mga bit ng tagubilin bago + haba ng IR ng target na device ng Atmel + mga bit ng pagtuturo pagkatapos) ay limitado sa maximum na 256 bit. Ang bilang ng mga device sa chain ay limitado sa 15 bago at 15 pagkatapos.

Tip:

Daisy chaining example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Upang kumonekta sa Atmel AVR XMEGA® device, ang mga setting ng daisy chain ay:

- Mga device bago: 1

- Mga device pagkatapos ng: 1

- Instruction bits bago: 4 (8-bit AVR device has 4 IR bits)

- Instruction bits pagkatapos ng: 5 (32-bit AVR device ay may 5 IR bits)

Talahanayan 4-6. IR Mga Haba ng Atmel MCUS

| Uri ng device | haba ng IR |

| AVR 8-bit | 4 bits |

| AVR 32-bit | 5 bits |

| SAM | 4 bits |

4.3.3. Kumokonekta sa isang JTAG Target

Ang Atmel-ICE ay nilagyan ng dalawang 50-mil 10-pin na JTAG mga konektor. Ang parehong mga konektor ay direktang konektado sa kuryente, ngunit umaayon sa dalawang magkaibang mga pinout; ang AVR JTAG header at ang ARM Cortex Debug header. Dapat piliin ang connector batay sa pinout ng target na board, at hindi sa target na uri ng MCU – para sa halampAng isang SAM device na naka-mount sa isang AVR STK600 stack ay dapat gumamit ng AVR header.

Ang inirerekomendang pinout para sa 10-pin na AVR JTAG connector ay ipinapakita sa Figure 4-6.

Ang inirerekomendang pinout para sa 10-pin ARM Cortex Debug connector ay ipinapakita sa Figure 4-2.

Direktang koneksyon sa isang karaniwang 10-pin 50-mil na header

Gamitin ang 50-mil 10-pin flat cable (kasama sa ilang kit) para direktang kumonekta sa isang board na sumusuporta sa ganitong uri ng header. Gamitin ang AVR connector port sa Atmel-ICE para sa mga header na may AVR pinout, at ang SAM connector port para sa mga header na sumusunod sa ARM Cortex Debug header pinout.

Ang mga pinout para sa parehong 10-pin connector port ay ipinapakita sa ibaba.

Koneksyon sa isang karaniwang 10-pin 100-mil na header

Gumamit ng karaniwang 50-mil hanggang 100-mil na adaptor para kumonekta sa 100-mil na mga header. Maaaring gamitin ang adapter board (kasama sa ilang kit) para sa layuning ito, o bilang kahalili ang JTAGMaaaring gamitin ang ICE3 adapter para sa mga target ng AVR.

![]() Mahalaga:

Mahalaga:

Ang JTAGAng ICE3 100-mil adapter ay hindi magagamit sa SAM connector port, dahil ang mga pin 2 at 10 (AVR GND) sa adapter ay konektado.

Koneksyon sa isang custom na 100-mil na header

Kung ang iyong target na board ay walang sumusunod na 10-pin na JTAG header sa 50- o 100-mil, maaari kang mag-map sa isang custom na pinout gamit ang 10-pin na "mini-squid" cable (kasama sa ilang kit), na nagbibigay ng access sa sampung indibidwal na 100-mil socket.

Koneksyon sa isang 20-pin na 100-mil na header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa mga target na may 20-pin 100-mil na header.

Talahanayan 4-7. Atmel-ICE JTAG Paglalarawan ng Pin

|

Pangalan |

AVR port pin | SAM port pin |

Paglalarawan |

| TCK | 1 | 4 | Pagsubok na Orasan (signal ng orasan mula sa Atmel-ICE papunta sa target na device). |

| TMS | 5 | 2 | Test Mode Select (control signal mula sa Atmel-ICE papunta sa target na device). |

| TDI | 9 | 8 | Test Data In (data na ipinadala mula sa Atmel-ICE papunta sa target na device). |

| TDO | 3 | 6 | Test Data Out (data na ipinadala mula sa target na device papunta sa Atmel-ICE). |

| nTRST | 8 | – | Test Reset (opsyonal, sa ilang AVR device lang). Ginamit upang i-reset ang JTAG TAP controller. |

| nSRST | 6 | 10 | I-reset (opsyonal). Ginagamit para i-reset ang target na device. Inirerekomenda ang pagkonekta sa pin na ito dahil pinapayagan nito ang Atmel-ICE na hawakan ang target na device sa isang estado ng pag-reset, na maaaring maging mahalaga sa pag-debug sa ilang partikular na sitwasyon. |

| VTG | 4 | 1 | Target voltage sanggunian. Ang Atmel-ICE samples ang target voltage sa pin na ito upang paganahin nang tama ang mga level converter. Ang Atmel-ICE ay kumukuha ng mas mababa sa 3mA mula sa pin na ito sa debugWIRE mode at mas mababa sa 1mA sa iba pang mga mode. |

| GND | 2, 10 | 3, 5, 9 | Lupa. Dapat na konektado ang lahat upang matiyak na ang Atmel-ICE at ang target na device ay nagbabahagi ng parehong ground reference. |

4.3.4 aWire Physical Interface

Ginagamit ng interface ng aWire ang RESET wire ng AVR device para payagan ang mga function ng programming at debugging. Ang isang espesyal na enable sequence ay ipinadala ng Atmel-ICE, na hindi pinapagana ang default na RESET functionality ng pin. Kapag nagdidisenyo ng application PCB, na kinabibilangan ng Atmel AVR na may aWire interface, inirerekomendang gamitin ang pinout tulad ng ipinapakita sa Figure 4 -8. Parehong sinusuportahan ang 100-mil at 50-mil na variant ng pinout na ito, depende sa paglalagay ng kable at mga adapter na kasama sa partikular na kit.

Larawan 4-8. aWire Header Pinout

![]() Tip:

Tip:

Dahil ang aWire ay isang half-duplex interface, ang isang pull-up resistor sa linya ng RESET sa pagkakasunud-sunod ng 47kΩ ay inirerekomenda upang maiwasan ang maling pag-detect ng start-bit kapag nagbabago ng direksyon.

Ang interface ng aWire ay maaaring gamitin bilang parehong programming at debugging interface. Ang lahat ng mga tampok ng sistema ng OCD ay magagamit sa pamamagitan ng 10-pin na JTAG ang interface ay maaari ding ma-access gamit ang aWire.

4.3.5 Pagkonekta sa isang aWire Target

Ang interface ng aWire ay nangangailangan lamang ng isang linya ng data bilang karagdagan sa VCC at GND. Sa target na linyang ito ay ang nRESET na linya, bagaman ginagamit ng debugger ang JTAG TDO line bilang linya ng data.

Ang inirerekomendang pinout para sa 6-pin aWire connector ay ipinapakita sa Figure 4-8.

Koneksyon sa isang 6-pin 100-mil aWire header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang standard na 100-mil aWire header.

Koneksyon sa isang 6-pin 50-mil aWire header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang karaniwang 50-mil aWire header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Tatlong koneksyon ang kinakailangan, tulad ng inilarawan sa talahanayan sa ibaba.

Talahanayan 4-8. Atmel-ICE aWire Pin Mapping

| Atmel-ICE AVR port pin | Mga target na pin | Mini-squid pin |

aWire pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | 6 | ||

| Pin 7 (Hindi konektado) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.3.6. Mga Espesyal na Pagsasaalang-alang

JTAG interface

Sa ilang mga Atmel AVR UC3 device ang JTAG port ay hindi pinagana bilang default. Kapag ginagamit ang mga device na ito, mahalagang ikonekta ang linya ng RESET upang mapagana ng Atmel-ICE ang JTAG interface.

aWire interface

Ang baud rate ng mga komunikasyon sa aWire ay nakasalalay sa dalas ng orasan ng system, dahil ang data ay dapat na naka-synchronize sa pagitan ng dalawang domain na ito. Awtomatikong matutukoy ng Atmel-ICE na ibinaba ang system clock, at muling i-calibrate ang baud rate nito nang naaayon. Gumagana lang ang awtomatikong pag-calibrate hanggang sa frequency ng system clock na 8kHz. Ang paglipat sa isang mas mababang system clock sa panahon ng isang debug session ay maaaring maging sanhi ng pagkawala ng contact sa target.

Kung kinakailangan, ang aWire baud rate ay maaaring paghigpitan sa pamamagitan ng pagtatakda ng aWire clock parameter. Gagana pa rin ang awtomatikong pag-detect, ngunit may ipapataw na halaga sa kisame sa mga resulta.

Ang anumang stabilizing capacitor na konektado sa RESET pin ay dapat na idiskonekta kapag gumagamit ng aWire dahil ito ay makagambala sa tamang operasyon ng interface. Inirerekomenda ang mahinang panlabas na pullup (10kΩ o mas mataas) sa linyang ito.

I-shutdown ang sleep mode

Ang ilang AVR UC3 device ay may internal regulator na maaaring gamitin sa 3.3V supply mode na may 1.8V regulated I/O lines. Nangangahulugan ito na pinapagana ng internal regulator ang core at karamihan sa I/O. Tanging Atmel AVR ONE! Sinusuportahan ng debugger ang pag-debug habang gumagamit ng mga sleep mode kung saan naka-shut off ang regulator na ito.

4.3.7. Paggamit ng EVTI / EVTO

Ang EVTI at EVTO pin ay hindi naa-access sa Atmel-ICE. Gayunpaman, maaari pa ring gamitin ang mga ito kasabay ng iba pang panlabas na kagamitan.

Maaaring gamitin ang EVTI para sa mga sumusunod na layunin:

- Maaaring pilitin ang target na ihinto ang pagpapatupad bilang tugon sa isang panlabas na kaganapan. Kung ang Event In Control (EIC) bits sa DC register ay isinulat sa 0b01, ang high-to-low transition sa EVTI pin ay bubuo ng breakpoint condition. Dapat manatiling mababa ang EVTI para sa isang ikot ng orasan ng CPU upang matiyak na ang isang breakpoint ay Ang External Breakpoint bit (EXB) sa DS ay nakatakda kapag nangyari ito.

- Bumubuo ng mga trace synchronization na mensahe. Hindi ginagamit ng Atmel-ICE.

Maaaring gamitin ang EVTO para sa mga sumusunod na layunin:

- Isinasaad na ang CPU ay pumasok sa debug Ang pagtatakda ng EOS bits sa DC sa 0b01 ay nagiging sanhi ng EVTO pin na mahila pababa para sa isang CPU clock cycle kapag ang target na device ay pumasok sa debug mode. Ang signal na ito ay maaaring gamitin bilang trigger source para sa isang panlabas na oscilloscope.

- Isinasaad na ang CPU ay umabot sa isang breakpoint o watchpoint. Sa pamamagitan ng pagtatakda ng EOC bit sa isang katumbas na Breakpoint/Watchpoint Control Register, ang breakpoint o watchpoint status ay ipinahiwatig sa EVTO pin. Ang mga bit ng EOS sa DC ay dapat na nakatakda sa 0xb10 upang paganahin ang tampok na ito. Ang EVTO pin ay maaaring ikonekta sa isang panlabas na oscilloscope upang masuri ang watchpoint

- Bumubuo ng mga trace timing signal. Hindi ginagamit ng Atmel-ICE.

4.4 tinyAVR, megaAVR, at XMEGA Devices

Nagtatampok ang mga AVR device ng iba't ibang programming at debugging interface. Suriin ang datasheet ng device para sa mga sinusuportahang interface ng device na iyon.

- Ilang tinyAVR® ang mga device ay may TPI TPI ay maaaring gamitin para sa pagprograma ng device lamang, at ang mga device na ito ay walang kakayahan sa pag-debug ng on-chip.

- Ang ilang tinyAVR device at ilang megaAVR device ay may debugWIRE interface, na kumokonekta sa isang on-chip debug system na kilala bilang tinyOCD. Ang lahat ng mga device na may debugWIRE ay mayroon ding interface ng SPI para sa in-system

- Ang ilang megaAVR device ay may JTAG interface para sa programming at pag-debug, na may on-chip na debug system na kilala rin bilang Lahat ng device na may JTAG itinatampok din ang interface ng SPI bilang alternatibong interface para sa in-system programming.

- Ang lahat ng AVR XMEGA device ay may PDI interface para sa programming at ang ilang AVR XMEGA device ay mayroon ding JTAG interface na may magkaparehong pag-andar.

- Ang mga bagong tinyAVR device ay may interface ng UPDI, na ginagamit para sa programming at pag-debug

Talahanayan 4-9. Buod ng Mga Interface ng Programming at Pag-debug

|

|

UPDI | TPI | SPI | debugWIR E | JTAG | PDI | isang wire |

SWD |

| tinyAVR | Mga bagong device | Ilang device | Ilang device | Ilang device | ||||

| megaAV R | Lahat ng device | Ilang device | Ilang device | |||||

| AVR XMEGA | Ilang device | Lahat ng device | ||||||

| AVR UC | Lahat ng device | Ilang device | ||||||

| SAM | Ilang device | Lahat ng device |

4.4.1. JTAG Pisikal na Interface

Ang JTAG ang interface ay binubuo ng isang 4-wire Test Access Port (TAP) controller na sumusunod sa IEEE® 1149.1 pamantayan. Ang pamantayang IEEE ay binuo upang magbigay ng isang pamantayang pang-industriya na paraan upang mahusay na masuri ang pagkakakonekta ng circuit board (Boundary Scan). Pinalawak ng mga Atmel AVR at SAM na device ang functionality na ito para isama ang buong Programming at On-chip Debugging na suporta.

Larawan 4-9. JTAG Mga Pangunahing Kaalaman sa Interface 4.4.2. Kumokonekta sa isang JTAG Target

4.4.2. Kumokonekta sa isang JTAG Target

Ang Atmel-ICE ay nilagyan ng dalawang 50-mil 10-pin na JTAG mga konektor. Ang parehong mga konektor ay direktang konektado sa kuryente, ngunit umaayon sa dalawang magkaibang mga pinout; ang AVR JTAG header at ang ARM Cortex Debug header. Dapat piliin ang connector batay sa pinout ng target na board, at hindi sa target na uri ng MCU – para sa halampAng isang SAM device na naka-mount sa isang AVR STK600 stack ay dapat gumamit ng AVR header.

Ang inirerekomendang pinout para sa 10-pin na AVR JTAG connector ay ipinapakita sa Figure 4-6.

Ang inirerekomendang pinout para sa 10-pin ARM Cortex Debug connector ay ipinapakita sa Figure 4-2.

Direktang koneksyon sa isang karaniwang 10-pin 50-mil na header

Gamitin ang 50-mil 10-pin flat cable (kasama sa ilang kit) para direktang kumonekta sa isang board na sumusuporta sa ganitong uri ng header. Gamitin ang AVR connector port sa Atmel-ICE para sa mga header na may AVR pinout, at ang SAM connector port para sa mga header na sumusunod sa ARM Cortex Debug header pinout.

Ang mga pinout para sa parehong 10-pin connector port ay ipinapakita sa ibaba.

Koneksyon sa isang karaniwang 10-pin 100-mil na header

Gumamit ng karaniwang 50-mil hanggang 100-mil na adaptor para kumonekta sa 100-mil na mga header. Maaaring gamitin ang adapter board (kasama sa ilang kit) para sa layuning ito, o bilang kahalili ang JTAGMaaaring gamitin ang ICE3 adapter para sa mga target ng AVR.

![]() Mahalaga:

Mahalaga:

Ang JTAGAng ICE3 100-mil adapter ay hindi magagamit sa SAM connector port, dahil ang mga pin 2 at 10 (AVR GND) sa adapter ay konektado.

Koneksyon sa isang custom na 100-mil na header

Kung ang iyong target na board ay walang sumusunod na 10-pin na JTAG header sa 50- o 100-mil, maaari kang mag-map sa isang custom na pinout gamit ang 10-pin na "mini-squid" cable (kasama sa ilang kit), na nagbibigay ng access sa sampung indibidwal na 100-mil socket.

Koneksyon sa isang 20-pin na 100-mil na header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa mga target na may 20-pin 100-mil na header.

Talahanayan 4-10. Atmel-ICE JTAG Paglalarawan ng Pin

| Pangalan | AVR port pin | SAM port pin | Paglalarawan |

| TCK | 1 | 4 | Pagsubok na Orasan (signal ng orasan mula sa Atmel-ICE papunta sa target na device). |

| TMS | 5 | 2 | Test Mode Select (control signal mula sa Atmel-ICE papunta sa target na device). |

| TDI | 9 | 8 | Test Data In (data na ipinadala mula sa Atmel-ICE papunta sa target na device). |

| TDO | 3 | 6 | Test Data Out (data na ipinadala mula sa target na device papunta sa Atmel-ICE). |

| nTRST | 8 | – | Test Reset (opsyonal, sa ilang AVR device lang). Ginamit upang i-reset ang JTAG TAP controller. |

| nSRST | 6 | 10 | I-reset (opsyonal). Ginagamit para i-reset ang target na device. Inirerekomenda ang pagkonekta sa pin na ito dahil pinapayagan nito ang Atmel-ICE na hawakan ang target na device sa isang estado ng pag-reset, na maaaring maging mahalaga sa pag-debug sa ilang partikular na sitwasyon. |

| VTG | 4 | 1 | Target voltage sanggunian. Ang Atmel-ICE samples ang target voltage sa pin na ito upang paganahin nang tama ang mga level converter. Ang Atmel-ICE ay kumukuha ng mas mababa sa 3mA mula sa pin na ito sa debugWIRE mode at mas mababa sa 1mA sa iba pang mga mode. |

| GND | 2, 10 | 3, 5, 9 | Lupa. Dapat na konektado ang lahat upang matiyak na ang Atmel-ICE at ang target na device ay nagbabahagi ng parehong ground reference. |

4.4.3.SPI Pisikal na Interface

Ginagamit ng In-System Programming ang target na Atmel AVR's internal SPI (Serial Peripheral Interface) upang mag-download ng code sa flash at EEPROM na mga alaala. Ito ay hindi isang debugging interface. Kapag nagdidisenyo ng isang application PCB, na kinabibilangan ng AVR na may interface ng SPI, ang pinout na ipinapakita sa figure sa ibaba ay dapat gamitin.

Larawan 4-10. SPI Header Pinout 4.4.4. Pagkonekta sa isang SPI Target

4.4.4. Pagkonekta sa isang SPI Target

Ang inirerekomendang pinout para sa 6-pin na SPI connector ay ipinapakita sa Figure 4-10.

Koneksyon sa isang 6-pin 100-mil SPI header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang standard na 100-mil SPI header.

Koneksyon sa isang 6-pin 50-mil SPI header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang standard na 50-mil SPI header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Anim na koneksyon ang kinakailangan, tulad ng inilarawan sa talahanayan sa ibaba.

![]() Mahalaga:

Mahalaga:

Ang interface ng SPI ay epektibong hindi pinagana kapag ang debugWIRE enable fuse (DWEN) ay na-program, kahit na ang SPIEN fuse ay naka-program din. Upang muling paganahin ang interface ng SPI, ang command na 'disable debugWIRE' ay dapat na ibigay habang nasa isang debugWIRE debugging session. Ang hindi pagpapagana ng debugWIRE sa ganitong paraan ay nangangailangan na ang SPIEN fuse ay naka-program na. Kung nabigo ang Atmel Studio na i-disable ang debugWIRE, malamang dahil HINDI naka-program ang SPIEN fuse. Kung ito ang kaso, kinakailangang gumamit ng high-voltage programming interface upang i-program ang SPIEN fuse.

![]() impormasyon:

impormasyon:

Ang interface ng SPI ay madalas na tinutukoy bilang "ISP", dahil ito ang unang In System Programming interface sa mga produkto ng Atmel AVR. Available na ngayon ang iba pang mga interface para sa In System Programming.

Talahanayan 4-11. Atmel-ICE SPI Pin Mapping

| Atmel-ICE AVR port pin | Mga target na pin | Mini-squid pin |

SPI pinout |

| Pin 1 (TCK) | SCK | 1 | 3 |

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | MISO | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | / I-reset | 6 | 5 |

| Pin 7 (hindi konektado) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | DAWDLE | 9 | 4 |

| Pin 10 (GND) | 0 |

4.4.5. PDI

Ang Program and Debug Interface (PDI) ay isang interface ng pagmamay-ari ng Atmel para sa panlabas na programming at on-chip na pag-debug ng isang device. Ang PDI Physical ay isang 2-pin na interface na nagbibigay ng bi-directional half-duplex synchronous na komunikasyon sa target na device.

Kapag nagdidisenyo ng isang application PCB, na kinabibilangan ng Atmel AVR na may PDI interface, ang pinout na ipinapakita sa figure sa ibaba ay dapat gamitin. Ang isa sa mga 6-pin na adapter na ibinigay kasama ng Atmel-ICE kit ay maaaring gamitin upang ikonekta ang Atmel-ICE probe sa application na PCB.

Larawan 4-11. Pinout ng PDI Header 4.4.6.Pagkonekta sa isang PDI Target

4.4.6.Pagkonekta sa isang PDI Target

Ang inirerekomendang pinout para sa 6-pin PDI connector ay ipinapakita sa Figure 4-11.

Koneksyon sa isang 6-pin 100-mil PDI header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang karaniwang 100-mil PDI header.

Koneksyon sa isang 6-pin 50-mil PDI header

Gamitin ang adapter board (kasama sa ilang kit) upang kumonekta sa isang karaniwang 50-mil na PDI header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Apat na koneksyon ang kailangan, gaya ng inilarawan sa talahanayan sa ibaba.

![]() Mahalaga:

Mahalaga:

Ang kinakailangang pinout ay iba sa JTAGICE mkII JTAG probe, kung saan nakakonekta ang PDI_DATA sa pin 9. Ang Atmel-ICE ay katugma sa pinout na ginamit ng Atmel-ICE, JTAGICE3, AVR ONE!, at AVR Dragon™ mga produkto.

Talahanayan 4-12. Atmel-ICE PDI Pin Mapping

|

Atmel-ICE AVR port pin |

Mga target na pin | Mini-squid pin |

Atmel STK600 PDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | PDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (hindi konektado) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.7. Pisikal na Interface ng UPDI

Ang Unified Program and Debug Interface (UPDI) ay isang interface ng pagmamay-ari ng Atmel para sa panlabas na programming at on-chip na pag-debug ng isang device. Ito ay isang kahalili sa PDI 2-wire physical interface, na matatagpuan sa lahat ng AVR XMEGA device. Ang UPDI ay isang single-wire interface na nagbibigay ng bi-directional half-duplex asynchronous na komunikasyon sa target na device para sa mga layunin ng programming at debugging.

Kapag nagdidisenyo ng PCB ng application, na kinabibilangan ng Atmel AVR na may interface ng UPDI, dapat gamitin ang pinout na ipinapakita sa ibaba. Ang isa sa mga 6-pin na adapter na ibinigay kasama ng Atmel-ICE kit ay maaaring gamitin upang ikonekta ang Atmel-ICE probe sa application na PCB.

Larawan 4-12. UPDI Header Pinout 4.4.7.1 UPDI at /RESET

4.4.7.1 UPDI at /RESET

Ang UPDI one-wire interface ay maaaring isang dedikadong pin o isang shared pin, depende sa target na AVR device. Kumonsulta sa datasheet ng device para sa karagdagang impormasyon.

Kapag ang interface ng UPDI ay nasa isang nakabahaging pin, maaaring i-configure ang pin na maging UPDI, /RESET, o GPIO sa pamamagitan ng pagtatakda ng mga fuse ng RSTPINCFG[1:0].

Ang RSTPINCFG[1:0] fuse ay may mga sumusunod na configuration, gaya ng inilarawan sa datasheet. Ang mga praktikal na implikasyon ng bawat pagpili ay ibinibigay dito.

Talahanayan 4-13. RSTPINCFG[1:0] Fuse Configuration

| RSPINCFG[1:0] | Configuration |

Paggamit |

| 00 | GPIO | Pangkalahatang layunin ng I/O pin. Upang ma-access ang UPDI, isang 12V pulse ay dapat ilapat sa pin na ito. Walang available na external reset source. |

| 01 | UPDI | Nakalaang programming at debugging pin. Walang available na external reset source. |

| 10 | I-reset | I-reset ang input ng signal. Upang ma-access ang UPDI, isang 12V pulse ay dapat ilapat sa pin na ito. |

| 11 | Nakareserba | NA |

Tandaan: Ang mga mas lumang AVR device ay may programming interface, na kilala bilang “High-Voltage Programming” (parehong umiiral ang mga serial at parallel na variant.) Sa pangkalahatan, ang interface na ito ay nangangailangan ng 12V na ilapat sa /RESET pin para sa tagal ng session ng programming. Ang interface ng UPDI ay isang ganap na naiibang interface. Ang UPDI pin ay pangunahing isang programming at debugging pin, na maaaring pagsamahin upang magkaroon ng alternatibong function (/RESET o GPIO). Kung napili ang alternatibong function, kinakailangan ang 12V pulse sa pin na iyon upang muling maisaaktibo ang paggana ng UPDI.

Tandaan: Kung ang isang disenyo ay nangangailangan ng pagbabahagi ng signal ng UPDI dahil sa mga hadlang sa pin, ang mga hakbang ay dapat gawin upang matiyak na ang aparato ay maaaring ma-program. Upang matiyak na ang signal ng UPDI ay maaaring gumana nang tama, gayundin upang maiwasan ang pinsala sa mga panlabas na bahagi mula sa pulso ng 12V, inirerekumenda na idiskonekta ang anumang mga bahagi sa pin na ito kapag sinusubukang i-debug o i-program ang device. Magagawa ito gamit ang isang 0Ω risistor, na naka-mount bilang default at inalis o pinapalitan ng isang pin header habang nagde-debug. Ang configuration na ito ay epektibong nangangahulugan na ang programming ay dapat gawin bago i-mount ang device.

![]() Mahalaga: Hindi sinusuportahan ng Atmel-ICE ang 12V sa linya ng UPDI. Sa madaling salita, kung ang UPDI pin ay na-configure bilang GPIO o RESET, hindi magagawang paganahin ng Atmel-ICE ang interface ng UPDI.

Mahalaga: Hindi sinusuportahan ng Atmel-ICE ang 12V sa linya ng UPDI. Sa madaling salita, kung ang UPDI pin ay na-configure bilang GPIO o RESET, hindi magagawang paganahin ng Atmel-ICE ang interface ng UPDI.

4.4.8.Pagkonekta sa isang Target ng UPDI

Ang inirerekomendang pinout para sa 6-pin na UPDI connector ay ipinapakita sa Figure 4-12.

Koneksyon sa isang 6-pin 100-mil UPDI header

Gamitin ang 6-pin 100-mil tap sa flat cable (kasama sa ilang kit) para kumonekta sa isang standard na 100-mil UPDI header.

Koneksyon sa isang 6-pin 50-mil UPDI header

Gamitin ang adapter board (kasama sa ilang kit) para kumonekta sa isang standard na 50-mil UPDI header.

Koneksyon sa isang custom na 100-mil na header

Ang 10-pin na mini-squid cable ay dapat gamitin para kumonekta sa pagitan ng Atmel-ICE AVR connector port at ng target board. Tatlong koneksyon ang kinakailangan, tulad ng inilarawan sa talahanayan sa ibaba.

Talahanayan 4-14. Atmel-ICE UPDI Pin Mapping

| Atmel-ICE AVR port pin | Mga target na pin | Mini-squid pin |

Atmel STK600 UPDI pinout |

| Pin 1 (TCK) | 1 | ||

| Pin 2 (GND) | GND | 2 | 6 |

| Pin 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pin 4 (VTG) | VTG | 4 | 2 |

| Pin 5 (TMS) | 5 | ||

| Pin 6 (nSRST) | [/RESET sense] | 6 | 5 |

| Pin 7 (Hindi konektado) | 7 | ||

| Pin 8 (nTRST) | 8 | ||

| Pin 9 (TDI) | 9 | ||

| Pin 10 (GND) | 0 |

4.4.9 Pisikal na Interface ng TPI

Ang TPI ay isang programming-only na interface para sa ilang AVR ATtiny device. Ito ay hindi isang debugging interface, at ang mga device na ito ay walang kakayahan sa OCD. Kapag nagdidisenyo ng isang application PCB na may kasamang AVR na may TPI interface, ang pinout na ipinapakita sa figure sa ibaba ay dapat gamitin.

Larawan 4-13. TPI Header Pinout 4.4.10.Pagkonekta sa isang Target ng TPI

4.4.10.Pagkonekta sa isang Target ng TPI