ICE デバッガー プログラマー

ICE デバッガー プログラマー

ユーザーガイド プログラマーとデバッガー

プログラマーとデバッガー

アトメルICE

ユーザーガイド

Atmel-ICE デバッガー

Atmel-ICE は、オンチップ デバッグ機能を備えた ARM® Cortex®-M ベースの Atmel ®SAM および Atmel AVR マイクロコントローラーをデバッグおよびプログラミングするための強力な開発ツールです。

サポート対象:

- 両方の J でのすべての Atmel AVR 32 ビット マイクロコントローラーのプログラミングとオンチップ デバッグTAG および aWire インターフェイス

- 両方の J でのすべての Atmel AVR XMEGA® ファミリ デバイスのプログラミングとオンチップ デバッグTAG および PDI 2 線式インターフェース

- プログラミング(JTAG、SPI、UPDI) およびすべての Atmel AVR 8 ビット マイクロコントローラーのデバッグ。TAG、debugWIRE または UPDI インターフェイス

- SWD と J の両方でのすべての Atmel SAM ARM Cortex-M ベースのマイクロコントローラーのプログラミングとデバッグTAG インターフェース

- このインターフェースをサポートするすべての Atmel tinyAVR® 8 ビット マイクロコントローラーのプログラミング (TPI)

このファームウェア リリースでサポートされているデバイスとインターフェイスの完全なリストについては、Atmel Studio ユーザー ガイドのサポートされているデバイス リストを参照してください。

導入

1.1。 Atmel-ICE の紹介

Atmel-ICE は、オンチップ デバッグ機能を備えた ARM Cortex-M ベースの Atmel SAM および Atmel AVR マイクロコントローラーをデバッグおよびプログラミングするための強力な開発ツールです。

サポート対象:

- 両方の J でのすべての Atmel AVR UC3 マイクロコントローラーのプログラミングとオンチップ デバッグTAG および aWire インターフェイス

- すべての AVR XMEGA ファミリ デバイスのプログラミングとオンチップ デバッグを両方の J で実行TAG および PDI 2wire インターフェース

- プログラミング(JTAG および SPI) および両方の J で OCD をサポートするすべての AVR 8 ビット マイクロコントローラーのデバッグTAG または debugWIRE インターフェイス

- SWD と J の両方でのすべての Atmel SAM ARM Cortex-M ベースのマイクロコントローラーのプログラミングとデバッグTAG インターフェース

- このインターフェイスをサポートするすべての Atmel tinyAVR 8 ビット マイクロコントローラーのプログラミング (TPI)

1.2. Atmel-ICE 機能

- Atmel Studio と完全互換

- すべての Atmel AVR UC3 32 ビット マイクロコントローラーのプログラミングとデバッグをサポート

- すべての 8 ビット AVR XMEGA デバイスのプログラミングとデバッグをサポート

- OCD を備えたすべての 8 ビット Atmel megaAVR® および tinyAVR デバイスのプログラミングとデバッグをサポート

- すべての SAM ARM Cortex-M ベースのマイクロコントローラのプログラミングとデバッグをサポート

- 目標稼働量tag1.62V~5.5Vの範囲

- debugWIRE インターフェイスを使用する場合はターゲット VTref から 3mA 未満、他のすべてのインターフェイスでは 1mA 未満の消費

- JをサポートTAG 32kHz~7.5MHzのクロック周波数

- 32kHz~7.5MHzのPDIクロック周波数をサポート

- 4kbit/s から 0.5Mbit/s までの debugWIRE ボーレートをサポート

- 7.5kbit/s から 7Mbit/s までの aWire ボーレートをサポート

- 8kHz~5MHzのSPIクロック周波数をサポート

- 最大 750kbit/s の UPDI ボーレートをサポート

- 32kHz~10MHzのSWDクロック周波数をサポート

- USB 2.0 高速ホスト インターフェイス

- 最大 3MB/秒の ITM シリアル トレース キャプチャ

- デバッグまたはプログラミングを行っていないときは、DGI SPI および USART インターフェイスをサポート

- 10 ピン 50 ミル J をサポートTAG AVR と Cortex の両方のピン配列を持つコネクタ。 標準プローブ ケーブルは、AVR 6 ピン ISP/PDI/TPI 100 ミル ヘッダーと 10 ピン 50 ミルをサポートします。 6 ピン 50 ミル、10 ピン 100 ミル、および 20 ピン 100 ミル ヘッダーをサポートするアダプタを使用できます。 さまざまなケーブルとアダプターを備えたいくつかのキット オプションを利用できます。

1.3. システム要件

Atmel-ICE ユニットは、フロントエンド デバッグ環境 Atmel Studio バージョン 6.2 以降がコンピュータにインストールされていることを必要とします。

Atmel-ICE は、提供された USB ケーブルまたは認定された Micro-USB ケーブルを使用してホスト コンピュータに接続する必要があります。

Atmel-ICE で始める

2.1. フルキット内容

Atmel-ICE フル キットには以下のアイテムが含まれます。

- Atmel-ICEユニット

- USBケーブル(1.8m、ハイスピード、Micro-B)

- 50 ミル AVR、100 ミル AVR/SAM、および 100 ミル 20 ピン SAM アダプタを含むアダプタ ボード

- 10 ピン 50 ミル コネクタおよび 6 ピン 100 ミル コネクタ付き IDC フラット ケーブル

- 50 x 10 ミル ソケットを備えた 10 ミル 100 ピン ミニ イカ ケーブル

図 2-1。 Atmel-ICE フルキットの内容 2.2. 基本キット内容

2.2. 基本キット内容

Atmel-ICE 基本キットには以下のアイテムが含まれています。

- Atmel-ICEユニット

- USBケーブル(1.8m、ハイスピード、Micro-B)

- 10 ピン 50 ミル コネクタおよび 6 ピン 100 ミル コネクタ付き IDC フラット ケーブル

図 2-2。 Atmel-ICE 基本キットの内容 2.3. PCBA キットの内容

2.3. PCBA キットの内容

Atmel-ICE PCBA キットには以下のアイテムが含まれています。

- プラスチックカプセル化のない Atmel-ICE ユニット

図 2-3。 Atmel-ICE PCBA キットの内容 2.4. スペアパーツキット

2.4. スペアパーツキット

以下のスペアパーツキットが利用可能です:

- アダプターキット

- ケーブルキット

図 2-4。 Atmel-ICE アダプター キットの内容 2.5.キットオーバーview

2.5.キットオーバーview

Atmel-ICE キットのオプションは、ここに図式的に示されています。

図 2-6。 Atmel-ICE キットオーバーview 2.6. Atmel-ICE の組み立て

2.6. Atmel-ICE の組み立て

Atmel-ICE ユニットは、ケーブルが取り付けられていない状態で出荷されます。 フル キットには、次の XNUMX つのケーブル オプションが用意されています。

- 50 mil 10 ピン IDC フラット ケーブル、6 ピン ISP および 10 ピン コネクタ付き

- 50 x 10 ミル ソケットを備えた 10 ミル 100 ピン ミニ イカ ケーブル

図 2-7。 Atmel-ICE ケーブル ほとんどの場合、50 ミルの 10 ピン IDC フラット ケーブルを使用して、10 ピンまたは 6 ピン コネクタにネイティブに接続するか、アダプタ ボードを介して接続できます。 XNUMX つの小さな PCBA に XNUMX つのアダプターが付属しています。 以下のアダプターが含まれています。

ほとんどの場合、50 ミルの 10 ピン IDC フラット ケーブルを使用して、10 ピンまたは 6 ピン コネクタにネイティブに接続するか、アダプタ ボードを介して接続できます。 XNUMX つの小さな PCBA に XNUMX つのアダプターが付属しています。 以下のアダプターが含まれています。

- 100mil 10 ピン JTAG/SWDアダプター

- 100 ミル 20 ピン SAM JTAG/SWDアダプター

- 50 ミル 6 ピン SPI/debugWIRE/PDI/aWire アダプタ

図 2-8。 Atmel-ICE アダプター 注記:

注記:

50ミルJTAG アダプターは提供されていません。これは、50 ミルの 10 ピン IDC ケーブルを使用して 50 ミルの JTAG ヘッダ。 50 ミルの 10 ピン コネクタに使用されるコンポーネントの部品番号については、「Atmel-ICE ターゲット コネクタの部品番号」を参照してください。

6 ピン ISP/PDI ヘッダーは、10 ピン IDC ケーブルの一部として含まれています。 この終端は、不要な場合は切断できます。

Atmel-ICE をデフォルト構成に組み立てるには、以下に示すように 10 ピン 50 ミル IDC ケーブルをユニットに接続します。 ケーブルの赤いワイヤ (ピン 1) がエンクロージャの青いベルトの三角形のインジケータと揃うようにケーブルの向きを合わせてください。 ケーブルはユニットから上向きに接続する必要があります。 ターゲットのピン配置に対応するポート (AVR または SAM) に接続してください。

図 2-9。 Atmel-ICE ケーブル接続 図 2-10。 Atmel-ICE AVR プローブ接続

図 2-10。 Atmel-ICE AVR プローブ接続

図 2-11。 Atmel-ICE SAM プローブ接続

図 2-11。 Atmel-ICE SAM プローブ接続 2.7. Atmel-ICE を開く

2.7. Atmel-ICE を開く

注記:

通常の操作では、Atmel-ICE ユニットを開いてはいけません。 ユニットの開封は、自己責任で行ってください。

帯電防止対策を講じる必要があります。

Atmel-ICE 筐体は、XNUMX つの別個のプラスチック コンポーネント (トップ カバー、ボトム カバー、および青いベルト) で構成され、これらは組み立て中に一緒にスナップされます。 ユニットを開くには、青色のベルトの開口部に大型のマイナス ドライバーを挿入し、内側に力を加えて軽くひねるだけです。 他のスナッパの穴でこのプロセスを繰り返すと、トップ カバーが外れます。

図 2-12。 Atmel-ICE を開く (1)

図 2-13。 Atmel-ICE を開く (2)

図 2-13。 Atmel-ICE を開く (2)

図 2-14。 Atmel-ICE を開く(3)

図 2-14。 Atmel-ICE を開く(3) ユニットを再度閉じるには、上部カバーと下部カバーを正しく合わせ、しっかりと押します。

ユニットを再度閉じるには、上部カバーと下部カバーを正しく合わせ、しっかりと押します。

2.8。 Atmel-ICE への電力供給

Atmel-ICE は USB バス vol によって給電されます。tage. 動作に必要な電流は 100mA 未満であるため、USB ハブを介して給電できます。 ユニットがプラグインされると、電源 LED が点灯します。アクティブなプログラミングまたはデバッグ セッションで接続されていない場合、ユニットは低電力消費モードに入り、コンピュータのバッテリーを節約します。 Atmel-ICE の電源を切ることはできません。使用していないときはプラグを抜く必要があります。

2.9。 ホスト コンピュータへの接続

Atmel-ICE は、主に標準の HID インターフェースを使用して通信し、ホスト コンピューターに特別なドライバーを必要としません。 Atmel-ICE の高度なデータ ゲートウェイ機能を使用するには、必ずホスト コンピュータに USB ドライバをインストールしてください。 これは、Atmel が無料で提供するフロントエンド ソフトウェアをインストールするときに自動的に行われます。 見る ウェブサイト 詳細については、最新のフロントエンド ソフトウェアをダウンロードしてください。

Atmel-ICE は、提供された USB ケーブルまたは適切な USB 認証マイクロ ケーブルを使用して、ホスト コンピュータの利用可能な USB ポートに接続する必要があります。 Atmel-ICE には USB 2.0 準拠のコントローラーが含まれており、フルスピード モードとハイスピード モードの両方で動作できます。 最良の結果を得るには、提供されたケーブルを使用してホスト コンピュータの USB 2.0 準拠の高速ハブに Atmel-ICE を直接接続します。

2.10. USB ドライバーのインストール

2.10.1. ウィンドウ

Microsoft® Windows® を実行しているコンピュータに Atmel-ICE をインストールする場合、Atmel-ICE が最初に差し込まれたときに USB ドライバがロードされます。

注記:

初めてユニットを接続する前に、必ずフロントエンド ソフトウェア パッケージをインストールしてください。

正常にインストールされると、Atmel-ICE はデバイス マネージャに「ヒューマン インターフェイス デバイス」として表示されます。

Atmel-ICE の接続

3.1. AVR および SAM ターゲット デバイスへの接続

Atmel-ICE には、50 つの 10 ミル XNUMX ピン J ピンが装備されています。TAG コネクタ。 両方のコネクタは直接電気的に接続されていますが、XNUMX つの異なるピン配列に準拠しています。 AVR JTAG ヘッダーと ARM Cortex Debug ヘッダー。 コネクタは、ターゲット MCU のタイプではなく、ターゲット ボードのピン配置に基づいて選択する必要があります。ampAVR STK® 600 スタックにマウントされた SAM デバイスは、AVR ヘッダーを使用する必要があります。

さまざまな Atmel-ICE キットで、さまざまなケーブルとアダプターが利用できます。 オーバーview の接続オプションが表示されます。

図 3-1。 Atmel-ICE 接続オプション 赤いワイヤは、1 ピン 10 ミル コネクタのピン 50 を示します。 1 ピン 6 ミル コネクタのピン 100 は、コネクタがケーブルから見えるときにキーイングの右側に配置されます。 アダプタの各コネクタのピン 1 は、白い点でマークされています。 次の図は、デバッグ ケーブルのピン配置を示しています。 A とマークされたコネクタはデバッガに接続し、B 側はターゲット ボードに接続します。

赤いワイヤは、1 ピン 10 ミル コネクタのピン 50 を示します。 1 ピン 6 ミル コネクタのピン 100 は、コネクタがケーブルから見えるときにキーイングの右側に配置されます。 アダプタの各コネクタのピン 1 は、白い点でマークされています。 次の図は、デバッグ ケーブルのピン配置を示しています。 A とマークされたコネクタはデバッガに接続し、B 側はターゲット ボードに接続します。

図 3-2。 デバッグ ケーブルのピン配列

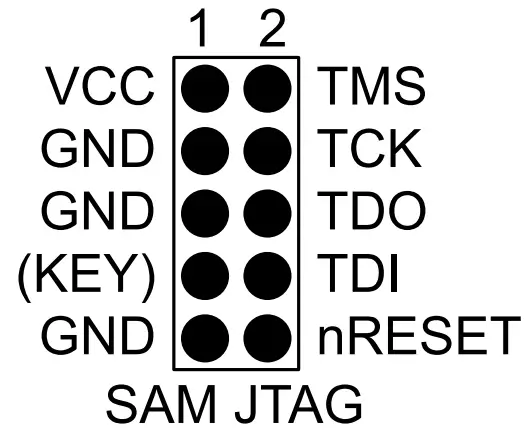

3.2. Jへの接続TAG ターゲット

3.2. Jへの接続TAG ターゲット

Atmel-ICE には、50 つの 10 ミル XNUMX ピン J ピンが装備されています。TAG コネクタ。 両方のコネクタは直接電気的に接続されていますが、XNUMX つの異なるピン配列に準拠しています。 AVR JTAG ヘッダーと ARM Cortex Debug ヘッダー。 コネクタは、ターゲット MCU のタイプではなく、ターゲット ボードのピン配置に基づいて選択する必要があります。ampAVR STK600 スタックにマウントされた SAM デバイスは AVR ヘッダーを使用する必要があります。

10 ピン AVR J の推奨ピン配置TAG コネクタを図 4-6 に示します。 10 ピン ARM Cortex デバッグ コネクタの推奨ピン配置を図 4-2 に示します。

標準の 10 ピン 50 ミル ヘッダーへの直接接続

50 ミルの 10 ピン フラット ケーブル (一部のキットに含まれる) を使用して、このヘッダー タイプをサポートするボードに直接接続します。 AVR ピン配列を持つヘッダーには Atmel-ICE の AVR コネクタ ポートを使用し、ARM Cortex Debug ヘッダー ピン配列に準拠するヘッダーには SAM コネクタ ポートを使用します。

両方の 10 ピン コネクタ ポートのピン配置を以下に示します。

標準の 10 ピン 100 ミル ヘッダーへの接続

標準の 50 ミルから 100 ミルへのアダプターを使用して、100 ミルのヘッダーに接続します。 この目的には、アダプタ ボード (一部のキットに含まれる) を使用できます。TAGICE3 アダプターは、AVR ターゲットに使用できます。

![]() 重要:

重要:

JTAGICE3 100 ミル アダプタは、アダプタのピン 2 と 10 (AVR GND) が接続されているため、SAM コネクタ ポートでは使用できません。

カスタム 100 ミル ヘッダーへの接続

ターゲット ボードに準拠した 10 ピン J ピンがない場合TAG ヘッダーを 50 ミルまたは 100 ミルの場合、10 ピンの「ミニ イカ」ケーブル (一部のキットに含まれています) を使用してカスタム ピン配列にマッピングできます。これにより、100 個の個別の XNUMX ミル ソケットにアクセスできます。

20 ピン 100 ミル ヘッドへの接続r

アダプター ボード (一部のキットに含まれる) を使用して、20 ピン 100 ミル ヘッダーのターゲットに接続します。

表 3-1. Atmel-ICE JTAG ピンの説明

| 名前 | AVR ポートピン | サム ポートピン | 説明 |

| TCK | 1 | 4 | テスト クロック (Atmel-ICE からターゲット デバイスへのクロック信号)。 |

| テレメトリ | 5 | 2 | テスト モード選択 (Atmel-ICE からターゲット デバイスへの制御信号)。 |

| TDI | 9 | 8 | Test Data In (Atmel-ICE からターゲット デバイスに送信されたデータ)。 |

| TDO | 3 | 6 | Test Data Out (ターゲット デバイスから Atmel-ICE に送信されたデータ)。 |

| ntrst | 8 | – | テスト リセット (オプション、一部の AVR デバイスのみ)。 Jのリセットに使用TAG タップコントローラー。 |

| nSRST | 6 | 10 | リセット (オプション)。 ターゲット デバイスをリセットするために使用します。 Atmel-ICE がターゲット デバイスをリセット状態に保持できるようにするため、このピンを接続することをお勧めします。これは、特定のシナリオでのデバッグに不可欠です。 |

| VTGE の | 4 | 1 | ターゲットvoltag参照してください。 Atmel-ICE のamples ターゲット ボリュームtagレベル コンバータに正しく電力を供給するために、このピンに e を接続します。 Atmel-ICE は、debugWIRE モードではこのピンから 3mA 未満、その他のモードでは 1mA 未満しか消費しません。 |

| グランド | 2、10 | 3、5、9 | 接地。 Atmel-ICE とターゲット デバイスが同じグランド基準を共有することを保証するために、すべてを接続する必要があります。 |

3.3. aWire ターゲットへの接続

aWire インターフェイスは、VCC と GND に加えて XNUMX つのデータ ラインのみを必要とします。 ターゲットでは、この行は nRESET 行ですが、デバッガーは J を使用します。TAG データラインとしての TDO ライン。

6 ピン aWire コネクタの推奨ピン配置を図 4-8 に示します。

6 ピン 100 ミル aWire ヘッダーへの接続

標準の 6 ミル aWire ヘッダーに接続するには、フラット ケーブル (一部のキットに含まれる) の 100 ピン 100 ミル タップを使用します。

6 ピン 50 ミル aWire ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、標準の 50 ミル aWire ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

表 3-2. Atmel-ICE aWire ピン マッピング

|

Atmel-ICE AVR ポート ピン |

ターゲットピン | ミニイカピン |

aWire ピン配列 |

| ピン 1 (TCK) | 1 | ||

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | データ | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 | ||

| ピン 6 (nSRST) | 6 | ||

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | 9 | ||

| ピン10(GND) | 0 |

3.4。 PDI ターゲットへの接続

6 ピン PDI コネクタの推奨ピン配置を図 4-11 に示します。

6 ピン 100 ミル PDI ヘッダーへの接続

標準の 6 ミル PDI ヘッダーに接続するには、フラット ケーブル (一部のキットに含まれる) の 100 ピン 100 ミル タップを使用します。

6 ピン 50 ミル PDI ヘッダーへの接続

アダプタ ボード (一部のキットに含まれる) を使用して、標準の 50 ミル PDI ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

![]() 重要:

重要:

必要なピン配列は J とは異なります。TAGICE mkⅡ JTAG ここで、PDI_DATA はピン 9 に接続されます。 Atmel-ICE は、Atmel-ICE、J によって使用されるピン配置と互換性があります。TAGICE3、AVR ONE!、および AVR Dragon™ 製品。

表 3-3。 Atmel-ICE PDI ピン マッピング

| Atmel-ICE AVR ポート ピン | ターゲットピン | ミニイカピン |

aWire ピン配列 |

| ピン 1 (TCK) | 1 | ||

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | データ | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 | ||

| ピン 6 (nSRST) | 6 | ||

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | 9 | ||

| ピン10(GND) | 0 |

3.4 PDI ターゲットへの接続

6 ピン PDI コネクタの推奨ピン配置を図 4-11 に示します。

6 ピン 100 ミル PDI ヘッダーへの接続

標準の 6 ミル PDI ヘッダーに接続するには、フラット ケーブル (一部のキットに含まれる) の 100 ピン 100 ミル タップを使用します。

6 ピン 50 ミル PDI ヘッダーへの接続

アダプタ ボード (一部のキットに含まれる) を使用して、標準の 50 ミル PDI ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

![]() 重要:

重要:

必要なピン配列は J とは異なります。TAGICE mkⅡ JTAG ここで、PDI_DATA はピン 9 に接続されます。 Atmel-ICE は、Atmel-ICE、J によって使用されるピン配置と互換性があります。TAGICE3、AVR ONE!、AVR Dragon™ 製品。

表 3-3。 Atmel-ICE PDI ピン マッピング

| Atmel-ICE AVR ポートピン | ターゲットピン | ミニイカピン | Atmel STK600 PDI ピン配列 |

| ピン 1 (TCK) | 1 | ||

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | PDI_DATA | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 | ||

| ピン 6 (nSRST) | PDI_CLK | 6 | 5 |

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | 9 | ||

| ピン10(GND) | 0 |

3.5 UPDI ターゲットへの接続

6 ピン UPDI コネクタの推奨ピン配置を図 4-12 に示します。

6 ピン 100 ミル UPDI ヘッダーへの接続

標準の 6 ミル UPDI ヘッダーに接続するには、フラット ケーブル (一部のキットに含まれる) の 100 ピン 100 ミル タップを使用します。

6 ピン 50 ミル UPDI ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、標準の 50 ミル UPDI ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

表 3-4。 Atmel-ICE UPDI ピン マッピング

| Atmel-ICE AVR ポートピン | ターゲットピン | ミニイカピン |

Atmel STK600 UPDI ピン配列 |

| ピン 1 (TCK) | 1 | ||

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | UPDI_DATA | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 | ||

| ピン 6 (nSRST) | 【/RESETセンス】 | 6 | 5 |

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | 9 | ||

| ピン10(GND) | 0 |

3.6 debugWIRE ターゲットへの接続

6 ピン debugWIRE (SPI) コネクタの推奨ピン配置を表 3-6 に示します。

6 ピン 100 ミル SPI ヘッダーへの接続

標準の 6 ミル SPI ヘッダーに接続するには、フラット ケーブル (一部のキットに含まれる) の 100 ピン 100 ミル タップを使用します。

6 ピン 50 ミル SPI ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、標準の 50 ミル SPI ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 表 3-5 に示すように、XNUMX つの接続が必要です。

debugWIRE インターフェイスには XNUMX 本の信号線 (RESET) しか必要ありませんが、VCC と GND を正しく動作させるには、SPI プログラミングを使用して debugWIRE インターフェイスを有効または無効にできるように、完全な SPI コネクタにアクセスすることをお勧めします。

DWEN ヒューズが有効な場合、OCD モジュールが RESET ピンを制御できるようにするために、SPI インターフェースが内部的にオーバーライドされます。 debugWIRE OCD はそれ自体を一時的に無効にすることができ (Atmel Studio のプロパティ ダイアログのデバッグ タブのボタンを使用)、RESET ラインの制御を解放します。 その後、SPI インターフェースが再び使用可能になり (SPIEN ヒューズがプログラムされている場合のみ)、SPI インターフェースを使用して DWEN ヒューズをプログラム解除できるようになります。 DWEN ヒューズのプログラムを解除する前に電源を切り替えると、debugWIRE モジュールが再び RESET ピンを制御します。

注記:

Atmel Studio に DWEN ヒューズの設定とクリアを処理させるだけにすることを強くお勧めします。

ターゲットAVRデバイスのロックビットがプログラムされている場合、debugWIREインターフェースを使用することはできません。 DWEN ヒューズをプログラムする前にロックビットがクリアされていることを常に確認し、DWEN ヒューズがプログラムされている間は決してロックビットを設定しないでください。 debugWIRE イネーブル ヒューズ (DWEN) とロックビットの両方が設定されている場合、High Vol を使用できます。tage チップ消去を実行するようにプログラミングし、ロックビットをクリアします。

ロックビットがクリアされると、debugWIRE インターフェイスが再び有効になります。 SPI インターフェイスは、DWEN ヒューズがプログラムされていない場合、ヒューズの読み取り、署名の読み取り、およびチップ消去の実行のみが可能です。

表 3-5. Atmel-ICE debugWIRE ピン マッピング

| Atmel-ICE AVR ポートピン | ターゲットピン |

ミニイカピン |

| ピン 1 (TCK) | 1 | |

| ピン2(GND) | グランド | 2 |

| ピン 3 (TDO) | 3 | |

| ピン 4 (VTG) | VTGE の | 4 |

| ピン 5 (TMS) | 5 | |

| ピン 6 (nSRST) | リセット | 6 |

| ピン 7 (未接続) | 7 | |

| ピン 8 (nTRST) | 8 | |

| ピン 9 (TDI) | 9 | |

| ピン10(GND) | 0 |

3.7 SPI ターゲットへの接続

6 ピン SPI コネクタの推奨ピン配置を図 4-10 に示します。

6 ピン 100 ミル SPI ヘッダーへの接続

標準の 6 ミル SPI ヘッダーに接続するには、フラット ケーブル (一部のキットに含まれる) の 100 ピン 100 ミル タップを使用します。

6 ピン 50 ミル SPI ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、標準の 50 ミル SPI ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

![]() 重要:

重要:

SPIEN ヒューズもプログラムされている場合でも、debugWIRE イネーブル ヒューズ (DWEN) がプログラムされると、SPI インターフェイスは実質的に無効になります。 SPI インターフェイスを再度有効にするには、debugWIRE デバッグ セッション中に「debugWIRE を無効にする」コマンドを発行する必要があります。 この方法で debugWIRE を無効にするには、SPIEN ヒューズが既にプログラムされている必要があります。 Atmel Studio が debugWIRE の無効化に失敗した場合、SPIEN ヒューズがプログラムされていない可能性があります。 この場合は、高容量を使用する必要があります。tagSPIEN ヒューズをプログラムするためのプログラミング インターフェイス。

![]() 情報:

情報:

SPI インターフェースは、Atmel AVR 製品の最初のイン システム プログラミング インターフェースであるため、しばしば「ISP」と呼ばれます。 イン システム プログラミングで他のインターフェイスを使用できるようになりました。

表 3-6。 Atmel-ICE SPI ピン マッピング

| Atmel-ICE AVR ポート ピン | ターゲットピン | ミニイカピン |

SPI ピン配列 |

| ピン 1 (TCK) | SCK | 1 | 3 |

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | 味噌 | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 | ||

| ピン 6 (nSRST) | / RESET | 6 | 5 |

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | MOSI | 9 | 4 |

| ピン10(GND) | 0 |

3.8 TPI ターゲットへの接続

6 ピン TPI コネクタの推奨ピン配置を図 4-13 に示します。

6 ピン 100 ミル TPI ヘッダーへの接続

フラット ケーブル (一部のキットに含まれる) の 6 ピン 100 ミル タップを使用して、標準の 100 ミル TPI ヘッダーに接続します。

6 ピン 50 ミル TPI ヘッダーへの接続

アダプタ ボード (一部のキットに含まれる) を使用して、標準の 50 ミル TPI ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

表 3-7。 Atmel-ICE TPI ピン マッピング

| Atmel-ICE AVR ポート ピン | ターゲットピン | ミニイカピン |

TPI ピン配列 |

| ピン 1 (TCK) | クロック | 1 | 3 |

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | データ | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 |

| ピン 6 (nSRST) | / RESET | 6 | 5 |

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | 9 | ||

| ピン10(GND) | 0 |

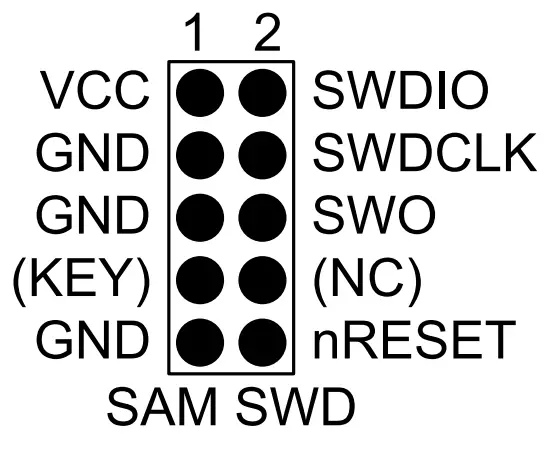

3.9 SWD ターゲットへの接続

ARM SWD インターフェイスは、J のサブセットです。TAG TCK および TMS ピンを使用するインターフェイス。つまり、SWD デバイスに接続する場合、10 ピン JTAG コネクタは技術的に使用できます。 アームJTAG およびAVR JTAG ただし、コネクタはピン互換性がないため、使用中のターゲット ボードのレイアウトに依存します。 STK600またはAVR Jを利用したボードを使用する場合TAG Atmel-ICE の AVR コネクタ ポートを使用する必要があります。 ARM J を使用するボードに接続する場合TAG Atmel-ICE の SAM コネクタ ポートを使用する必要があります。

10 ピン Cortex Debug コネクタの推奨ピン配置を図 4-4 に示します。

10 ピン 50 ミル Cortex ヘッダーへの接続

フラット ケーブル (一部のキットに付属) を使用して、標準の 50 ミル Cortex ヘッダーに接続します。

10 ピン 100 ミル Cortex レイアウト ヘッダーへの接続

アダプタ ボード (一部のキットに含まれる) を使用して、100 ミルの Cortex ピン配置ヘッダーに接続します。

20 ピン 100 ミル SAM ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、20 ピン 100 ミル SAM ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR または SAM コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

表 3-8. Atmel-ICE SWD ピン マッピング

| 名前 | AVR ポートピン | サム ポートピン | 説明 |

| SWDC LK | 1 | 4 | シリアル ワイヤ デバッグ クロック。 |

| スディオ | 5 | 2 | シリアル ワイヤ デバッグ データ入力/出力。 |

| スウェーデン | 3 | 6 | シリアル ワイヤ出力 (オプション - すべてのデバイスに実装されているわけではありません)。 |

| nSRST | 6 | 10 | リセットします。 |

| VTGE の | 4 | 1 | ターゲットvoltag参照してください。 |

| グランド | 2、10 | 3、5、9 | 地面。 |

3.10 データ ゲートウェイ インターフェイスへの接続

Atmel-ICE は、デバッグおよびプログラミングが使用されていない場合、限定されたデータ ゲートウェイ インターフェース (DGI) をサポートします。 機能は、Atmel EDBG デバイスを搭載した Atmel Xplained Pro キットに見られるものと同じです。

Data Gateway Interface は、ターゲット デバイスからコンピュータにデータをストリーミングするためのインターフェイスです。 これは、アプリケーションのデバッグや、ターゲット デバイスで実行されているアプリケーションの機能のデモンストレーションを支援することを目的としています。

DGI は、データ ストリーミング用の複数のチャネルで構成されています。 Atmel-ICE は以下のモードをサポートします:

- USART

- SPI

表 3-9。 Atmel-ICE DGI USART ピン配列

|

AVR ポート |

サムポート | DGI USART ピン |

説明 |

| 3 | 6 | TX | Atmel-ICE からターゲット デバイスにピンを送信します。 |

| 4 | 1 | VTGE の | ターゲットvoltage(参照巻tage) |

| 8 | 7 | RX | ターゲット デバイスから Atmel-ICE へのピンの受信 |

| 9 | 8 | クロック | USARTクロック |

| 2、10 | 3、5、9 | グランド | 地面 |

表 3-10。 Atmel-ICE DGI SPI ピン配列

|

AVR ポート |

サムポート | DGI SPI ピン |

説明 |

| 1 | 4 | SCK | SPIクロック |

| 3 | 6 | 味噌 | マスターインスレーブアウト |

| 4 | 1 | VTGE の | ターゲットvoltage(参照巻tage) |

| 5 | 2 | nCS | チップ セレクト アクティブ ロー |

| 9 | 8 | MOSI | マスターアウトスレーブイン |

| 2、10 | 3、5、9 | グランド | 地面 |

![]() 重要: SPI と USART インターフェースを同時に使用することはできません。

重要: SPI と USART インターフェースを同時に使用することはできません。

![]() 重要: DGI とプログラミングまたはデバッグを同時に使用することはできません。

重要: DGI とプログラミングまたはデバッグを同時に使用することはできません。

オンチップデバッグ

4.1 はじめに

オンチップデバッグ

オンチップ デバッグ モジュールは、開発者が外部開発プラットフォームから (通常はデバッガーまたはデバッグ アダプターと呼ばれるデバイスを介して) デバイスでの実行を監視および制御できるようにするシステムです。

OCD システムを使用すると、ターゲット システムの正確な電気特性とタイミング特性を維持しながらアプリケーションを実行でき、条件付きまたは手動で実行を停止し、プログラム フローとメモリを検査できます。

実行モード

実行モードでは、コードの実行は Atmel-ICE から完全に独立しています。 Atmel-ICE はターゲット デバイスを継続的に監視して、ブレーク条件が発生したかどうかを確認します。 これが発生すると、OCD システムはデバッグ インターフェイスを介してデバイスに問い合わせます。 view デバイスの内部状態。

停止モード

ブレークポイントに到達すると、プログラムの実行は停止しますが、一部の I/O はブレークポイントが発生していないかのように実行を継続する場合があります。 例えばampつまり、ブレークポイントに達したときに USART 送信が開始されたと仮定します。 この場合、たとえコアが停止モードにあるとしても、USART は転送を完了するために全速力で実行し続けます。

ハードウェアブレークポイント

ターゲット OCD モジュールには、ハードウェアに実装された多数のプログラム カウンター コンパレーターが含まれています。 プログラム カウンタがコンパレータ レジスタの XNUMX つに格納されている値と一致すると、OCD は停止モードに入ります。 ハードウェア ブレークポイントは OCD モジュールに専用のハードウェアを必要とするため、使用可能なブレークポイントの数は、ターゲットに実装されている OCD モジュールのサイズによって異なります。 通常、このようなハードウェア コンパレータの XNUMX つが、内部使用のためにデバッガによって「予約」されています。

ソフトウェアブレークポイント

ソフトウェア ブレークポイントは、ターゲット デバイスのプログラム メモリに配置される BREAK 命令です。 この命令がロードされると、プログラムの実行が中断され、OCD は停止モードに入ります。 実行を継続するには、OCD から「開始」コマンドを発行する必要があります。 すべての Atmel デバイスに BREAK 命令をサポートする OCD モジュールがあるわけではありません。

4.2 J を持つ SAM デバイスTAG/SWD

すべての SAM デバイスは、プログラミングとデバッグ用の SWD インターフェイスを備えています。 さらに、一部の SAM デバイスには JTAG 同一の機能を持つインターフェース。 そのデバイスのサポートされているインターフェイスについては、デバイスのデータシートを確認してください。

4.2.1.ARM CoreSight コンポーネント

Atmel ARM Cortex-M ベースのマイクロコントローラーは、CoreSight 準拠の OCD コンポーネントを実装しています。 これらのコンポーネントの機能は、デバイスによって異なります。 詳細については、デバイスのデータシートと、ARM が提供する CoreSight のドキュメントを参照してください。

4.2.1. じTAG 物理インターフェース

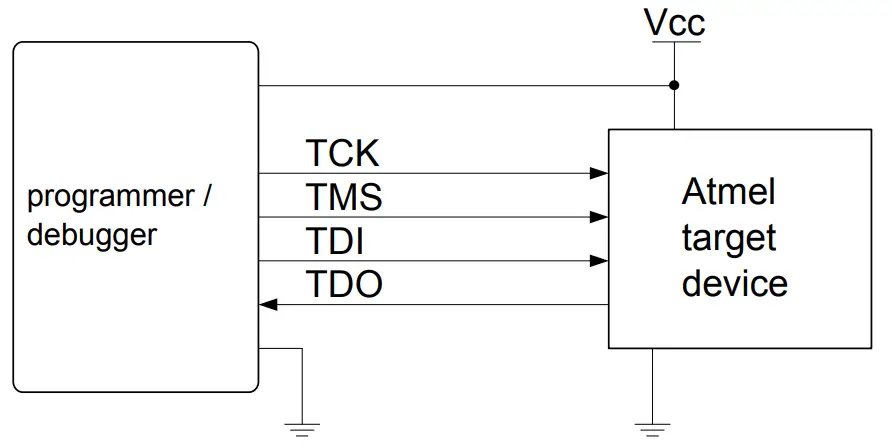

JTAG インターフェイスは、IEEE に準拠した 4 線式テスト アクセス ポート (TAP) コントローラーで構成されます。® 1149.1 標準。 IEEE 標準は、回路基板の接続性を効率的にテストするための業界標準の方法 (バウンダリ スキャン) を提供するために開発されました。 Atmel AVR および SAM デバイスは、この機能を拡張して、完全なプログラミングおよびオンチップ デバッグのサポートを含めました。

図 4-1。 JTAG インターフェイスの基本

4.2.2.1 サム・JTAG ピン配置 (Cortex-M デバッグ コネクタ)

J を備えた Atmel SAM を含むアプリケーション PCB を設計する場合TAG 下の図に示すようにピン配置を使用することをお勧めします。 特定のキットに含まれるケーブルとアダプタに応じて、このピン配置の 100 ミルと 50 ミルの両方のバリエーションがサポートされます。

図 4-2。 サム・ジェイTAG ヘッダーのピン配列

表 4-1. サム・ジェイTAG ピンの説明

| 名前 | ピン |

説明 |

| TCK | 4 | テスト クロック (Atmel-ICE からターゲット デバイスへのクロック信号)。 |

| テレメトリ | 2 | テスト モード選択 (Atmel-ICE からターゲット デバイスへの制御信号)。 |

| TDI | 8 | Test Data In (Atmel-ICE からターゲット デバイスに送信されたデータ)。 |

| TDO | 6 | Test Data Out (ターゲット デバイスから Atmel-ICE に送信されたデータ)。 |

| nリセット | 10 | リセット (オプション)。 ターゲット デバイスをリセットするために使用します。 Atmel-ICE がターゲット デバイスをリセット状態に保持できるようにするため、このピンを接続することをお勧めします。これは、特定のシナリオでのデバッグに不可欠です。 |

| VTGE の | 1 | ターゲットvoltag参照してください。 Atmel-ICE のamples ターゲット ボリュームtagレベル コンバータに正しく電力を供給するために、このピンに e を接続します。 このモードでは、Atmel-ICE はこのピンから 1mA 未満しか消費しません。 |

| グランド | 3、5、9 | 接地。 Atmel-ICE とターゲット デバイスが同じグランド基準を共有することを保証するために、すべてを接続する必要があります。 |

| 鍵 | 7 | 内部で AVR コネクタの TRST ピンに接続されています。 接続しないことをお勧めします。 |

![]() ヒント: ピン 1 と GND の間にデカップリング コンデンサを含めることを忘れないでください。

ヒント: ピン 1 と GND の間にデカップリング コンデンサを含めることを忘れないでください。

4.2.2.2 ジェフTAG デイジー 連鎖

JTAG インターフェイスを使用すると、デイジー チェーン構成で複数のデバイスを XNUMX つのインターフェイスに接続できます。 ターゲット デバイスはすべて、同じ電源ボリュームから電力を供給されている必要があります。tage、共通の接地ノードを共有し、下の図に示すように接続する必要があります。

図 4-3。 JTAG デイジーチェーン

デイジー チェーンでデバイスを接続する場合は、次の点を考慮する必要があります。

- すべてのデバイスは共通のグランドを共有し、Atmel-ICE プローブの GND に接続する必要があります

- すべてのデバイスが同じターゲット ボリュームで動作している必要がありますtage. Atmel-ICE 上の VTG は、このボリュームに接続する必要がありますtage.

- TMS と TCK は並列に接続されています。 TDI と TDO をシリアル接続

- Atmel-ICE プローブの nSRST は、チェーン内のデバイスのいずれかがその J を無効にする場合、デバイスの RESET に接続する必要があります。TAG ポート

- 「前のデバイス」は、Jの数を指しますTAG TDI 信号がターゲット デバイスに到達する前にデイジー チェーンで通過する必要があるデバイス。 同様に、「後のデバイス」は、Atmel-ICE TDO に到達する前に、信号がターゲット デバイスの後に通過しなければならないデバイスの数です。

- 「前」と「後」の命令ビットは、すべての J の合計を指します。TAG デイジー チェーンでターゲット デバイスの前後に接続されているデバイスの命令レジスタの長さ

- IR の長さの合計 (前の命令ビット + Atmel ターゲット デバイスの IR の長さ + 後の命令ビット) は、最大 256 ビットに制限されています。 チェーン内のデバイスの数は、前後で 15 個に制限されています。

![]() ヒント:

ヒント:

デイジーチェーンexampル: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Atmel AVR XMEGA に接続するには® デバイスの場合、デイジー チェーン設定は次のとおりです。

- 以前のデバイス: 1

- 後のデバイス: 1

- 前の命令ビット: 4 (8 ビット AVR デバイスには 4 つの IR ビットがあります)

- 後の命令ビット: 5 (32 ビット AVR デバイスには 5 つの IR ビットがあります)

表 4-2. Atmel MCU の IR 長

| デバイスタイプ | 赤外線の長さ |

| AVR 8 ビット | 4ビット |

| AVR 32 ビット | 5ビット |

| サム | 4ビット |

4.2.3. Jへの接続TAG ターゲット

Atmel-ICE には、50 つの 10 ミル XNUMX ピン J ピンが装備されています。TAG コネクタ。 両方のコネクタは直接電気的に接続されていますが、XNUMX つの異なるピン配列に準拠しています。 AVR JTAG ヘッダーと ARM Cortex Debug ヘッダー。 コネクタは、ターゲット MCU のタイプではなく、ターゲット ボードのピン配置に基づいて選択する必要があります。ampAVR STK600 スタックにマウントされた SAM デバイスは AVR ヘッダーを使用する必要があります。

10 ピン AVR J の推奨ピン配置TAG コネクタを図 4-6 に示します。

10 ピン ARM Cortex デバッグ コネクタの推奨ピン配置を図 4-2 に示します。

標準の 10 ピン 50 ミル ヘッダーへの直接接続

50 ミルの 10 ピン フラット ケーブル (一部のキットに含まれる) を使用して、このヘッダー タイプをサポートするボードに直接接続します。 AVR ピン配列を持つヘッダーには Atmel-ICE の AVR コネクタ ポートを使用し、ARM Cortex Debug ヘッダー ピン配列に準拠するヘッダーには SAM コネクタ ポートを使用します。

両方の 10 ピン コネクタ ポートのピン配置を以下に示します。

標準の 10 ピン 100 ミル ヘッダーへの接続

標準の 50 ミルから 100 ミルへのアダプターを使用して、100 ミルのヘッダーに接続します。 この目的には、アダプタ ボード (一部のキットに含まれる) を使用できます。TAGICE3 アダプターは、AVR ターゲットに使用できます。

![]() 重要:

重要:

JTAGICE3 100 ミル アダプタは、アダプタのピン 2 と 10 (AVR GND) が接続されているため、SAM コネクタ ポートでは使用できません。

カスタム 100 ミル ヘッダーへの接続

ターゲット ボードに準拠した 10 ピン J ピンがない場合TAG ヘッダーを 50 ミルまたは 100 ミルの場合、10 ピンの「ミニ イカ」ケーブル (一部のキットに含まれています) を使用してカスタム ピン配列にマッピングできます。これにより、100 個の個別の XNUMX ミル ソケットにアクセスできます。

20 ピン 100 ミル ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、20 ピン 100 ミル ヘッダーのターゲットに接続します。

表 4-3. Atmel-ICE JTAG ピンの説明

| 名前 | AVR ポートピン | サム ポートピン | 説明 |

| TCK | 1 | 4 | テスト クロック (Atmel-ICE からターゲット デバイスへのクロック信号)。 |

| テレメトリ | 5 | 2 | テスト モード選択 (Atmel-ICE からターゲット デバイスへの制御信号)。 |

| TDI | 9 | 8 | Test Data In (Atmel-ICE からターゲット デバイスに送信されたデータ)。 |

| TDO | 3 | 6 | Test Data Out (ターゲット デバイスから Atmel-ICE に送信されたデータ)。 |

| ntrst | 8 | – | テスト リセット (オプション、一部の AVR デバイスのみ)。 Jのリセットに使用TAG タップコントローラー。 |

| nSRST | 6 | 10 | リセット (オプション)。 ターゲット デバイスをリセットするために使用します。 Atmel-ICE がターゲット デバイスをリセット状態に保持できるようにするため、このピンを接続することをお勧めします。これは、特定のシナリオでのデバッグに不可欠です。 |

| VTGE の | 4 | 1 | ターゲットvoltag参照してください。 Atmel-ICE のamples ターゲット ボリュームtagレベル コンバータに正しく電力を供給するために、このピンに e を接続します。 Atmel-ICE は、debugWIRE モードではこのピンから 3mA 未満、その他のモードでは 1mA 未満しか消費しません。 |

| グランド | 2、10 | 3、5、9 | 接地。 Atmel-ICE とターゲット デバイスが同じグランド基準を共有することを保証するために、すべてを接続する必要があります。 |

4.2.4. SWD 物理インターフェイス

ARM SWD インターフェイスは、J のサブセットです。TAG インターフェイス、TCK および TMS ピンを使用します。 アームJTAG およびAVR JTAG ただし、コネクタはピン互換性がないため、SWD または J を備えた SAM デバイスを使用するアプリケーション PCB を設計する場合TAG 下図に示す ARM ピン配置を使用することをお勧めします。 Atmel-ICE の SAM コネクタ ポートは、このピン配置に直接接続できます。

図 4-4。 推奨ARM SWD/JTAG ヘッダーのピン配列

Atmel-ICE は、UART 形式の ITM トレースをホスト コンピューターにストリーミングできます。 トレースは、10 ピン ヘッダーの TRACE/SWO ピンでキャプチャされます (JTAG TDO ピン)。 データは Atmel-ICE の内部でバッファリングされ、HID インターフェースを介してホスト コンピュータに送信されます。 信頼できる最大データ転送速度は約 3MB/秒です。

4.2.5. SWD ターゲットへの接続

ARM SWD インターフェイスは、J のサブセットです。TAG TCK および TMS ピンを使用するインターフェイス。つまり、SWD デバイスに接続する場合、10 ピン JTAG コネクタは技術的に使用できます。 アームJTAG およびAVR JTAG ただし、コネクタはピン互換性がないため、使用中のターゲット ボードのレイアウトに依存します。 STK600またはAVR Jを利用したボードを使用する場合TAG Atmel-ICE の AVR コネクタ ポートを使用する必要があります。 ARM J を使用するボードに接続する場合TAG Atmel-ICE の SAM コネクタ ポートを使用する必要があります。

10 ピン Cortex Debug コネクタの推奨ピン配置を図 4-4 に示します。

10 ピン 50 ミル Cortex ヘッダーへの接続

フラット ケーブル (一部のキットに付属) を使用して、標準の 50 ミル Cortex ヘッダーに接続します。

10 ピン 100 ミル Cortex レイアウト ヘッダーへの接続

アダプタ ボード (一部のキットに含まれる) を使用して、100 ミルの Cortex ピン配置ヘッダーに接続します。

20 ピン 100 ミル SAM ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、20 ピン 100 ミル SAM ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR または SAM コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

表 4-4. Atmel-ICE SWD ピン マッピング

| 名前 | AVR ポートピン | サム ポートピン | 説明 |

| SWDC LK | 1 | 4 | シリアル ワイヤ デバッグ クロック。 |

| スディオ | 5 | 2 | シリアル ワイヤ デバッグ データ入力/出力。 |

| スウェーデン | 3 | 6 | シリアル ワイヤ出力 (オプション - すべてのデバイスに実装されているわけではありません)。 |

| nSRST | 6 | 10 | リセットします。 |

| VTGE の | 4 | 1 | ターゲットvoltag参照してください。 |

| グランド | 2、10 | 3、5、9 | 地面。 |

4.2.6 特別な考慮事項

ERASEピン

一部の SAM デバイスには、完全なチップ消去を実行し、セキュリティ ビットが設定されているデバイスのロックを解除するためにアサートされる ERASE ピンが含まれています。 この機能は、フラッシュ コントローラだけでなくデバイス自体にも結合されており、ARM コアの一部ではありません。

ERASE ピンはデバッグ ヘッダーの一部ではないため、Atmel-ICE はこの信号をアサートしてデバイスのロックを解除することができません。 このような場合、ユーザーはデバッグ セッションを開始する前に手動で消去を実行する必要があります。

物理インターフェース JTAG インタフェース

Atmel-ICE が J を有効にできるように、RESET ラインは常に接続されている必要があります。TAG インタフェース。

SWDインターフェース

Atmel-ICE が SWD インターフェースを有効にできるように、RESET ラインは常に接続されている必要があります。

4.3 J付きのAVR UC3デバイスTAG/ワイヤー

すべての AVR UC3 デバイスは JTAG プログラミングおよびデバッグ用のインターフェイス。 さらに、一部の AVR UC3 デバイスは、単一のワイヤを使用して同一の機能を備えた aWire インターフェースを備えています。 そのデバイスのサポートされているインターフェイスについては、デバイスのデータシートを確認してください

4.3.1 Atmel AVR UC3 オンチップ デバッグ システム

Atmel AVR UC3 OCD システムは、Nexus 2.0 標準 (IEEE-ISTO 5001™-2003) に従って設計されています。これは、32 ビット マイクロコントローラー向けの非常に柔軟で強力なオープン オンチップ デバッグ標準です。 次の機能をサポートしています。

- Nexus 準拠のデバッグ ソリューション

- OCD はあらゆる CPU 速度をサポートします

- XNUMX つのプログラム カウンター ハードウェア ブレークポイント

- XNUMX つのデータ ブレークポイント

- ブレークポイントはウォッチポイントとして設定可能

- ハードウェア ブレークポイントを組み合わせて、範囲をブレークすることができます

- 無制限の数のユーザー プログラム ブレークポイント (BREAK を使用)

- リアルタイム プログラム カウンター分岐トレース、データ トレース、プロセス トレース (パラレル トレース キャプチャ ポートを備えたデバッガーでのみサポート)

AVR UC3 OCD システムに関する詳細については、AVR32UC テクニカル リファレンス マニュアルを参照してください。 www.atmel.com/uc3.

4.3.2. じTAG 物理インターフェース

JTAG インターフェイスは、IEEE に準拠した 4 線式テスト アクセス ポート (TAP) コントローラーで構成されます。® 1149.1 標準。 IEEE 標準は、回路基板の接続性を効率的にテストするための業界標準の方法 (バウンダリ スキャン) を提供するために開発されました。 Atmel AVR および SAM デバイスは、この機能を拡張して、完全なプログラミングおよびオンチップ デバッグのサポートを含めました。

図 4-5。 JTAG インターフェイスの基本

4.3.2.1 エイブイアール JTAG ピン配置

J を備えた Atmel AVR を含むアプリケーション PCB を設計する場合TAG 下の図に示すようにピン配置を使用することをお勧めします。 特定のキットに含まれるケーブルとアダプタに応じて、このピン配置の 100 ミルと 50 ミルの両方のバリエーションがサポートされます。

図 4-6。 AVR JTAG ヘッダーのピン配列

テーブル 4-5. AVR JTAG ピンの説明

| 名前 | ピン |

説明 |

| TCK | 1 | テスト クロック (Atmel-ICE からターゲット デバイスへのクロック信号)。 |

| テレメトリ | 5 | テスト モード選択 (Atmel-ICE からターゲット デバイスへの制御信号)。 |

| TDI | 9 | Test Data In (Atmel-ICE からターゲット デバイスに送信されたデータ)。 |

| TDO | 3 | Test Data Out (ターゲット デバイスから Atmel-ICE に送信されたデータ)。 |

| ntrst | 8 | テスト リセット (オプション、一部の AVR デバイスのみ)。 Jのリセットに使用TAG タップコントローラー。 |

| nSRST | 6 | リセット (オプション)。 ターゲット デバイスをリセットするために使用します。 Atmel-ICE がターゲット デバイスをリセット状態に保持できるようにするため、このピンを接続することをお勧めします。これは、特定のシナリオでのデバッグに不可欠です。 |

| VTGE の | 4 | ターゲットvoltag参照してください。 Atmel-ICE のamples ターゲット ボリュームtagレベル コンバータに正しく電力を供給するために、このピンに e を接続します。 Atmel-ICE は、debugWIRE モードではこのピンから 3mA 未満、その他のモードでは 1mA 未満しか消費しません。 |

| グランド | 2、10 | 接地。 Atmel-ICE とターゲット デバイスが同じグランド基準を共有することを保証するために、両方を接続する必要があります。 |

![]() ヒント: ピン 4 と GND の間にデカップリング コンデンサを含めることを忘れないでください。

ヒント: ピン 4 と GND の間にデカップリング コンデンサを含めることを忘れないでください。

4.3.2.2 ジェフTAG デイジー 連鎖

JTAG インターフェイスを使用すると、デイジー チェーン構成で複数のデバイスを XNUMX つのインターフェイスに接続できます。 ターゲット デバイスはすべて、同じ電源ボリュームから電力を供給されている必要があります。tage、共通の接地ノードを共有し、下の図に示すように接続する必要があります。

図 4-7。 JTAG デイジーチェーン

デイジー チェーンでデバイスを接続する場合は、次の点を考慮する必要があります。

- すべてのデバイスは共通のグランドを共有し、Atmel-ICE プローブの GND に接続する必要があります

- すべてのデバイスが同じターゲット ボリュームで動作している必要がありますtage. Atmel-ICE 上の VTG は、このボリュームに接続する必要がありますtage.

- TMS と TCK は並列に接続されています。 TDI と TDO はシリアル チェーンで接続されています。

- Atmel-ICE プローブの nSRST は、チェーン内のデバイスのいずれかがその J を無効にする場合、デバイスの RESET に接続する必要があります。TAG ポート

- 「前のデバイス」は、Jの数を指しますTAG TDI 信号がターゲット デバイスに到達する前にデイジー チェーンで通過する必要があるデバイス。 同様に、「後のデバイス」は、Atmel-ICE TDO に到達する前に、信号がターゲット デバイスの後に通過しなければならないデバイスの数です。

- 「前」と「後」の命令ビットは、すべての J の合計を指します。TAG デイジー チェーンでターゲット デバイスの前後に接続されているデバイスの命令レジスタの長さ

- IR の長さの合計 (前の命令ビット + Atmel ターゲット デバイスの IR の長さ + 後の命令ビット) は、最大 256 ビットに制限されています。 チェーン内のデバイスの数は、前後で 15 個に制限されています。

ヒント:

デイジーチェーンexampル: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Atmel AVR XMEGA に接続するには® デバイスの場合、デイジー チェーン設定は次のとおりです。

- 以前のデバイス: 1

- 後のデバイス: 1

- 前の命令ビット: 4 (8 ビット AVR デバイスには 4 つの IR ビットがあります)

- 後の命令ビット: 5 (32 ビット AVR デバイスには 5 つの IR ビットがあります)

表 4-6。 Atmel MCUS の IR 長

| デバイスタイプ | 赤外線の長さ |

| AVR 8 ビット | 4ビット |

| AVR 32 ビット | 5ビット |

| サム | 4ビット |

4.3.3.Jへの接続TAG ターゲット

Atmel-ICE には、50 つの 10 ミル XNUMX ピン J ピンが装備されています。TAG コネクタ。 両方のコネクタは直接電気的に接続されていますが、XNUMX つの異なるピン配列に準拠しています。 AVR JTAG ヘッダーと ARM Cortex Debug ヘッダー。 コネクタは、ターゲット MCU のタイプではなく、ターゲット ボードのピン配置に基づいて選択する必要があります。ampAVR STK600 スタックにマウントされた SAM デバイスは AVR ヘッダーを使用する必要があります。

10 ピン AVR J の推奨ピン配置TAG コネクタを図 4-6 に示します。

10 ピン ARM Cortex デバッグ コネクタの推奨ピン配置を図 4-2 に示します。

標準の 10 ピン 50 ミル ヘッダーへの直接接続

50 ミルの 10 ピン フラット ケーブル (一部のキットに含まれる) を使用して、このヘッダー タイプをサポートするボードに直接接続します。 AVR ピン配列を持つヘッダーには Atmel-ICE の AVR コネクタ ポートを使用し、ARM Cortex Debug ヘッダー ピン配列に準拠するヘッダーには SAM コネクタ ポートを使用します。

両方の 10 ピン コネクタ ポートのピン配置を以下に示します。

標準の 10 ピン 100 ミル ヘッダーへの接続

標準の 50 ミルから 100 ミルへのアダプターを使用して、100 ミルのヘッダーに接続します。 この目的には、アダプタ ボード (一部のキットに含まれる) を使用できます。TAGICE3 アダプターは、AVR ターゲットに使用できます。

![]() 重要:

重要:

JTAGICE3 100 ミル アダプタは、アダプタのピン 2 と 10 (AVR GND) が接続されているため、SAM コネクタ ポートでは使用できません。

カスタム 100 ミル ヘッダーへの接続

ターゲット ボードに準拠した 10 ピン J ピンがない場合TAG ヘッダーを 50 ミルまたは 100 ミルの場合、10 ピンの「ミニ イカ」ケーブル (一部のキットに含まれています) を使用してカスタム ピン配列にマッピングできます。これにより、100 個の個別の XNUMX ミル ソケットにアクセスできます。

20 ピン 100 ミル ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、20 ピン 100 ミル ヘッダーのターゲットに接続します。

表 4-7. Atmel-ICE JTAG ピンの説明

|

名前 |

AVR ポート ピン | SAM ポート ピン |

説明 |

| TCK | 1 | 4 | テスト クロック (Atmel-ICE からターゲット デバイスへのクロック信号)。 |

| テレメトリ | 5 | 2 | テスト モード選択 (Atmel-ICE からターゲット デバイスへの制御信号)。 |

| TDI | 9 | 8 | Test Data In (Atmel-ICE からターゲット デバイスに送信されたデータ)。 |

| TDO | 3 | 6 | Test Data Out (ターゲット デバイスから Atmel-ICE に送信されたデータ)。 |

| ntrst | 8 | – | テスト リセット (オプション、一部の AVR デバイスのみ)。 Jのリセットに使用TAG タップコントローラー。 |

| nSRST | 6 | 10 | リセット (オプション)。 ターゲット デバイスをリセットするために使用します。 Atmel-ICE がターゲット デバイスをリセット状態に保持できるようにするため、このピンを接続することをお勧めします。これは、特定のシナリオでのデバッグに不可欠です。 |

| VTGE の | 4 | 1 | ターゲットvoltag参照してください。 Atmel-ICE のamples ターゲット ボリュームtagレベル コンバータに正しく電力を供給するために、このピンに e を接続します。 Atmel-ICE は、debugWIRE モードではこのピンから 3mA 未満、その他のモードでは 1mA 未満しか消費しません。 |

| グランド | 2、10 | 3、5、9 | 接地。 Atmel-ICE とターゲット デバイスが同じグランド基準を共有することを保証するために、すべてを接続する必要があります。 |

4.3.4 aWire 物理インターフェイス

aWire インターフェースは、AVR デバイスの RESET ワイヤを利用して、プログラミングとデバッグ機能を可能にします。 ピンのデフォルト RESET 機能を無効にする特別なイネーブル シーケンスが Atmel-ICE によって送信されます。 -4. 特定のキットに含まれるケーブルとアダプタに応じて、このピン配置の 8 ミルと 100 ミルの両方のバリエーションがサポートされます。

図 4-8。 aWire ヘッダーのピン配列

![]() ヒント:

ヒント:

aWire は半二重インターフェイスであるため、方向を変更する際の誤ったスタート ビット検出を回避するために、RESET ラインに 47kΩ 程度のプルアップ抵抗を接続することをお勧めします。

aWire インターフェイスは、プログラミング インターフェイスとデバッグ インターフェイスの両方として使用できます。 10ピンJを介して利用可能なOCDシステムのすべての機能TAG インターフェイスには、aWire を使用してアクセスすることもできます。

4.3.5 aWire ターゲットへの接続

aWire インターフェイスは、V に加えて XNUMX つのデータ ラインのみを必要とします。CC およびGND。 ターゲットでは、この行は nRESET 行ですが、デバッガーは J を使用します。TAG データラインとしての TDO ライン。

6 ピン aWire コネクタの推奨ピン配置を図 4-8 に示します。

6 ピン 100 ミル aWire ヘッダーへの接続

標準の 6 ミル aWire ヘッダーに接続するには、フラット ケーブル (一部のキットに含まれる) の 100 ピン 100 ミル タップを使用します。

6 ピン 50 ミル aWire ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、標準の 50 ミル aWire ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

表 4-8. Atmel-ICE aWire ピン マッピング

| Atmel-ICE AVR ポート ピン | ターゲットピン | ミニイカピン |

aWire ピン配列 |

| ピン 1 (TCK) | 1 | ||

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | データ | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 | ||

| ピン 6 (nSRST) | 6 | ||

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | 9 | ||

| ピン10(GND) | 0 |

4.3.6. 特別な考慮事項

JTAG インタフェース

一部の Atmel AVR UC3 デバイスでは、JTAG ポートはデフォルトでは有効になっていません。 これらのデバイスを使用する場合、Atmel-ICE が J デバイスを有効にできるように RESET ラインを接続することが不可欠です。TAG インタフェース。

aWireインターフェース

aWire 通信のボー レートは、システム クロックの周波数に依存します。これは、これら 8 つのドメイン間でデータを同期する必要があるためです。 Atmel-ICE は、システム クロックが低下したことを自動的に検出し、それに応じてボー レートを再調整します。 自動キャリブレーションは、XNUMXkHz のシステム クロック周波数までしか機能しません。 デバッグ セッション中に低いシステム クロックに切り替えると、ターゲットとの接続が失われる可能性があります。

必要に応じて、aWire クロック パラメータを設定することにより、aWire ボー レートを制限できます。 自動検出は引き続き機能しますが、結果に上限値が課されます。

aWire を使用する場合は、RESET ピンに接続されている安定化コンデンサを切断する必要があります。これは、インターフェイスの正常な動作を妨げるためです。 このラインには弱い外部プルアップ (10kΩ 以上) を使用することをお勧めします。

シャットダウンスリープモード

一部の AVR UC3 デバイスには、3.3V 安定化 I/O ラインを使用して 1.8V 電源モードで使用できる内部レギュレータがあります。 これは、内部レギュレータがコアとほとんどの I/O の両方に電力を供給することを意味します。 Atmel AVR ONEだけ! デバッガーは、このレギュレーターがオフになっているスリープ モードを使用している間のデバッグをサポートします。

4.3.7. EVTI / EVTO の使用法

EVTI および EVTO ピンは、Atmel-ICE ではアクセスできません。 ただし、他の外部機器と組み合わせて使用することはできます。

EVTI は、次の目的で使用できます。

- ターゲットは、外部イベントに応答して強制的に実行を停止できます。 DC レジスタのイベント イン コントロール (EIC) ビットが 0b01 に書き込まれると、EVTI ピンのハイからローへの遷移によってブレークポイント条件が生成されます。 EVTI は、ブレークポイントが確実に XNUMX つの CPU クロック サイクルの間 Low のままである必要があります。これが発生すると、DS の外部ブレークポイント ビット (EXB) がセットされます。

- トレース同期メッセージを生成しています。 Atmel-ICE では使用されません。

EVTO は、次の目的で使用できます。

- CPU がデバッグ モードに入ったことを示す DC の EOS ビットを 0b01 に設定すると、ターゲット デバイスがデバッグ モードに入るときに、EVTO ピンが XNUMX CPU クロック サイクルの間 Low になります。 この信号は、外部オシロスコープのトリガー ソースとして使用できます。

- CPU がブレークポイントまたはウォッチポイントに到達したことを示します。 対応するブレークポイント/ウォッチポイント制御レジスタの EOC ビットを設定することにより、ブレークポイントまたはウォッチポイントのステータスが EVTO ピンに示されます。 この機能を有効にするには、DC の EOS ビットを 0xb10 に設定する必要があります。 その後、EVTO ピンを外部オシロスコープに接続して、ウォッチポイントを調べることができます。

- トレース タイミング信号の生成。 Atmel-ICE では使用されません。

4.4 tinyAVR、megaAVR、XMEGA デバイス

AVR デバイスは、さまざまなプログラミングおよびデバッグ インターフェイスを備えています。 そのデバイスのサポートされているインターフェイスについては、デバイスのデータシートを確認してください。

- いくつかのtinyAVR® デバイスには TPI があります TPI はデバイスのプログラミングにのみ使用でき、これらのデバイスにはオンチップ デバッグ機能がまったくありません。

- 一部の tinyAVR デバイスと一部の megaAVR デバイスには、tinyOCD として知られるオンチップ デバッグ システムに接続する debugWIRE インターフェイスがあります。 debugWIRE を備えたすべてのデバイスには、インシステム用の SPI インターフェイスもあります。

- 一部の megaAVR デバイスには JTAG オンチップ デバッグ システムを備えたプログラミングおよびデバッグ用のインターフェイスTAG また、インシステム プログラミング用の代替インターフェイスとして SPI インターフェイスも備えています。

- すべての AVR XMEGA デバイスにはプログラミング用の PDI インターフェースがあり、一部の AVR XMEGA デバイスには J インターフェイスもあります。TAG 同一の機能を持つインターフェイス。

- 新しい tinyAVR デバイスには、プログラミングとデバッグに使用される UPDI インターフェースがあります。

表 4-9。 プログラミングおよびデバッグ インターフェイスのまとめ

|

|

UPDI | TP1 の | SPI | デバッグWIR E | JTAG | PD-I | ワイヤー |

スウェーデン |

| tinyAVR | 新しいデバイス | 一部のデバイス | 一部のデバイス | 一部のデバイス | ||||

| メガAV R | すべてのデバイス | 一部のデバイス | 一部のデバイス | |||||

| AVRXメガ | 一部のデバイス | すべてのデバイス | ||||||

| AVR UC | すべてのデバイス | 一部のデバイス | ||||||

| サム | 一部のデバイス | すべてのデバイス |

4.4.1. じTAG 物理インターフェース

JTAG インターフェイスは、IEEE に準拠した 4 線式テスト アクセス ポート (TAP) コントローラーで構成されます。® 1149.1 標準。 IEEE 標準は、回路基板の接続性を効率的にテストするための業界標準の方法 (バウンダリ スキャン) を提供するために開発されました。 Atmel AVR および SAM デバイスは、この機能を拡張して、完全なプログラミングおよびオンチップ デバッグのサポートを含めました。

図 4-9。 JTAG インターフェイスの基本 4.4.2. Jへの接続TAG ターゲット

4.4.2. Jへの接続TAG ターゲット

Atmel-ICE には、50 つの 10 ミル XNUMX ピン J ピンが装備されています。TAG コネクタ。 両方のコネクタは直接電気的に接続されていますが、XNUMX つの異なるピン配列に準拠しています。 AVR JTAG ヘッダーと ARM Cortex Debug ヘッダー。 コネクタは、ターゲット MCU のタイプではなく、ターゲット ボードのピン配置に基づいて選択する必要があります。ampAVR STK600 スタックにマウントされた SAM デバイスは AVR ヘッダーを使用する必要があります。

10 ピン AVR J の推奨ピン配置TAG コネクタを図 4-6 に示します。

10 ピン ARM Cortex デバッグ コネクタの推奨ピン配置を図 4-2 に示します。

標準の 10 ピン 50 ミル ヘッダーへの直接接続

50 ミルの 10 ピン フラット ケーブル (一部のキットに含まれる) を使用して、このヘッダー タイプをサポートするボードに直接接続します。 AVR ピン配列を持つヘッダーには Atmel-ICE の AVR コネクタ ポートを使用し、ARM Cortex Debug ヘッダー ピン配列に準拠するヘッダーには SAM コネクタ ポートを使用します。

両方の 10 ピン コネクタ ポートのピン配置を以下に示します。

標準の 10 ピン 100 ミル ヘッダーへの接続

標準の 50 ミルから 100 ミルへのアダプターを使用して、100 ミルのヘッダーに接続します。 この目的には、アダプタ ボード (一部のキットに含まれる) を使用できます。TAGICE3 アダプターは、AVR ターゲットに使用できます。

![]() 重要:

重要:

JTAGICE3 100 ミル アダプタは、アダプタのピン 2 と 10 (AVR GND) が接続されているため、SAM コネクタ ポートでは使用できません。

カスタム 100 ミル ヘッダーへの接続

ターゲット ボードに準拠した 10 ピン J ピンがない場合TAG ヘッダーを 50 ミルまたは 100 ミルの場合、10 ピンの「ミニ イカ」ケーブル (一部のキットに含まれています) を使用してカスタム ピン配列にマッピングできます。これにより、100 個の個別の XNUMX ミル ソケットにアクセスできます。

20 ピン 100 ミル ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、20 ピン 100 ミル ヘッダーのターゲットに接続します。

表 4-10. Atmel-ICE JTAG ピンの説明

| 名前 | AVR ポートピン | サム ポートピン | 説明 |

| TCK | 1 | 4 | テスト クロック (Atmel-ICE からターゲット デバイスへのクロック信号)。 |

| テレメトリ | 5 | 2 | テスト モード選択 (Atmel-ICE からターゲット デバイスへの制御信号)。 |

| TDI | 9 | 8 | Test Data In (Atmel-ICE からターゲット デバイスに送信されたデータ)。 |

| TDO | 3 | 6 | Test Data Out (ターゲット デバイスから Atmel-ICE に送信されたデータ)。 |

| ntrst | 8 | – | テスト リセット (オプション、一部の AVR デバイスのみ)。 Jのリセットに使用TAG タップコントローラー。 |

| nSRST | 6 | 10 | リセット (オプション)。 ターゲット デバイスをリセットするために使用します。 Atmel-ICE がターゲット デバイスをリセット状態に保持できるようにするため、このピンを接続することをお勧めします。これは、特定のシナリオでのデバッグに不可欠です。 |

| VTGE の | 4 | 1 | ターゲットvoltag参照してください。 Atmel-ICE のamples ターゲット ボリュームtagレベル コンバータに正しく電力を供給するために、このピンに e を接続します。 Atmel-ICE は、debugWIRE モードではこのピンから 3mA 未満、その他のモードでは 1mA 未満しか消費しません。 |

| グランド | 2、10 | 3、5、9 | 接地。 Atmel-ICE とターゲット デバイスが同じグランド基準を共有することを保証するために、すべてを接続する必要があります。 |

4.4.3.SPI 物理インターフェイス

インシステム プログラミングは、ターゲット Atmel AVR の内部 SPI (シリアル ペリフェラル インターフェイス) を使用して、コードをフラッシュおよび EEPROM メモリにダウンロードします。 これはデバッグ インターフェイスではありません。 SPI インターフェースを備えた AVR を含むアプリケーション PCB を設計する場合、下図に示すピン配列を使用する必要があります。

図 4-10。 SPI ヘッダーのピン配列 4.4.4. SPI ターゲットへの接続

4.4.4. SPI ターゲットへの接続

6 ピン SPI コネクタの推奨ピン配置を図 4-10 に示します。

6 ピン 100 ミル SPI ヘッダーへの接続

標準の 6 ミル SPI ヘッダーに接続するには、フラット ケーブル (一部のキットに含まれる) の 100 ピン 100 ミル タップを使用します。

6 ピン 50 ミル SPI ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、標準の 50 ミル SPI ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

![]() 重要:

重要:

SPIEN ヒューズもプログラムされている場合でも、debugWIRE イネーブル ヒューズ (DWEN) がプログラムされると、SPI インターフェイスは実質的に無効になります。 SPI インターフェイスを再度有効にするには、debugWIRE デバッグ セッション中に「debugWIRE を無効にする」コマンドを発行する必要があります。 この方法で debugWIRE を無効にするには、SPIEN ヒューズが既にプログラムされている必要があります。 Atmel Studio が debugWIRE の無効化に失敗した場合、SPIEN ヒューズがプログラムされていない可能性があります。 この場合は、高容量を使用する必要があります。tagSPIEN ヒューズをプログラムするためのプログラミング インターフェイス。

![]() 情報:

情報:

SPI インターフェースは、Atmel AVR 製品の最初のイン システム プログラミング インターフェースであるため、しばしば「ISP」と呼ばれます。 イン システム プログラミングで他のインターフェイスを使用できるようになりました。

表 4-11。 Atmel-ICE SPI ピン マッピング

| Atmel-ICE AVR ポート ピン | ターゲットピン | ミニイカピン |

SPI ピン配列 |

| ピン 1 (TCK) | SCK | 1 | 3 |

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | 味噌 | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 | ||

| ピン 6 (nSRST) | / RESET | 6 | 5 |

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | MOSI | 9 | 4 |

| ピン10(GND) | 0 |

4.4.5. PDI

プログラムおよびデバッグ インターフェイス (PDI) は、デバイスの外部プログラミングおよびオンチップ デバッグ用の Atmel 独自のインターフェイスです。 PDI 物理は、ターゲット デバイスとの双方向半二重同期通信を提供する 2 ピン インターフェイスです。

PDI インターフェースを備えた Atmel AVR を含むアプリケーション PCB を設計する場合、下図に示すピン配列を使用する必要があります。 Atmel-ICE キットで提供される 6 ピン アダプタの XNUMX つを使用して、Atmel-ICE プローブをアプリケーション PCB に接続できます。

図 4-11。 PDI ヘッダーのピン配列 4.4.6.PDI ターゲットへの接続

4.4.6.PDI ターゲットへの接続

6 ピン PDI コネクタの推奨ピン配置を図 4-11 に示します。

6 ピン 100 ミル PDI ヘッダーへの接続

標準の 6 ミル PDI ヘッダーに接続するには、フラット ケーブル (一部のキットに含まれる) の 100 ピン 100 ミル タップを使用します。

6 ピン 50 ミル PDI ヘッダーへの接続

アダプタ ボード (一部のキットに含まれる) を使用して、標準の 50 ミル PDI ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

![]() 重要:

重要:

必要なピン配列は J とは異なります。TAGICE mkⅡ JTAG ここで、PDI_DATA はピン 9 に接続されます。 Atmel-ICE は、Atmel-ICE、J によって使用されるピン配置と互換性があります。TAGICE3、AVR ONE!、AVR Dragon™ 製品。

表 4-12。 Atmel-ICE PDI ピン マッピング

|

Atmel-ICE AVR ポートピン |

ターゲットピン | ミニイカピン |

Atmel STK600 PDI ピン配列 |

| ピン 1 (TCK) | 1 | ||

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | PDI_DATA | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 | ||

| ピン 6 (nSRST) | PDI_CLK | 6 | 5 |

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | 9 | ||

| ピン10(GND) | 0 |

4.4.7. UPDI 物理インターフェイス

統合プログラムおよびデバッグ インターフェイス (UPDI) は、デバイスの外部プログラミングおよびオンチップ デバッグ用の Atmel 独自のインターフェイスです。 これは、すべての AVR XMEGA デバイスに見られる PDI 2 線物理インターフェイスの後継です。 UPDI は、プログラミングとデバッグの目的でターゲット デバイスとの双方向半二重非同期通信を提供する単線インターフェイスです。

UPDI インターフェースを備えた Atmel AVR を含むアプリケーション PCB を設計する場合、以下に示すピン配列を使用する必要があります。 Atmel-ICE キットで提供される 6 ピン アダプタの XNUMX つを使用して、Atmel-ICE プローブをアプリケーション PCB に接続できます。

図 4-12。 UPDI ヘッダーのピン配列 4.4.7.1 UPDI と /RESET

4.4.7.1 UPDI と /RESET

UPDI 単線インターフェースは、対象の AVR デバイスに応じて、専用ピンまたは共有ピンにすることができます。 詳細については、デバイスのデータシートを参照してください。

UPDI インターフェイスが共有ピン上にある場合、RSTPINCFG[1:0] ヒューズを設定することにより、ピンを UPDI、/RESET、または GPIO のいずれかに設定できます。

RSTPINCFG[1:0] ヒューズには、データシートに記載されているように、次の構成があります。 ここでは、各選択の実際的な意味を示します。

表 4-13. RSTPINCFG[1:0] ヒューズの設定

| RSTPINCFG[1:0] | 構成 |

使用法 |

| 00 | GPIO | 汎用 I/O ピン。 UPDI にアクセスするには、このピンに 12V パルスを印加する必要があります。 外部リセット ソースは使用できません。 |

| 01 | UPDI | 専用のプログラミングおよびデバッグ ピン。 外部リセット ソースは使用できません。 |

| 10 | リセット | リセット信号入力。 UPDI にアクセスするには、このピンに 12V パルスを印加する必要があります。 |

| 11 | 予約済み | NA |

注記: 古い AVR デバイスには、「High-Vol」として知られるプログラミング インターフェイスがあります。tage プログラミング」 (シリアルとパラレルの両方のバリエーションが存在します。) 一般に、このインターフェイスでは、プログラミング セッションの間、/RESET ピンに 12V を印加する必要があります。 UPDI インターフェイスは、まったく異なるインターフェイスです。 UPDI ピンは、主にプログラミングおよびデバッグ用のピンであり、融合して別の機能 (/RESET または GPIO) を持つことができます。 代替機能が選択された場合、UPDI 機能を再度アクティブにするために、そのピンに 12V パルスが必要です。

注記: ピンの制約のために設計で UPDI 信号を共有する必要がある場合は、デバイスを確実にプログラムできるようにするための手順を実行する必要があります。 UPDI 信号が正しく機能することを確認し、12V パルスによる外部コンポーネントへの損傷を回避するために、デバイスのデバッグまたはプログラミングを試みるときは、このピンのコンポーネントをすべて切断することをお勧めします。 これは 0Ω 抵抗を使用して行うことができます。この抵抗はデフォルトで取り付けられており、デバッグ中にピンヘッダーによって削除または置き換えられます。 この構成は、事実上、デバイスを取り付ける前にプログラミングを行う必要があることを意味します。

![]() 重要: Atmel-ICE は UPDI ラインで 12V をサポートしません。 言い換えれば、UPDI ピンが GPIO または RESET として設定されている場合、Atmel-ICE は UPDI インターフェースを有効にすることができません。

重要: Atmel-ICE は UPDI ラインで 12V をサポートしません。 言い換えれば、UPDI ピンが GPIO または RESET として設定されている場合、Atmel-ICE は UPDI インターフェースを有効にすることができません。

4.4.8.UPDI ターゲットへの接続

6 ピン UPDI コネクタの推奨ピン配置を図 4-12 に示します。

6 ピン 100 ミル UPDI ヘッダーへの接続

標準の 6 ミル UPDI ヘッダーに接続するには、フラット ケーブル (一部のキットに含まれる) の 100 ピン 100 ミル タップを使用します。

6 ピン 50 ミル UPDI ヘッダーへの接続

アダプター ボード (一部のキットに含まれる) を使用して、標準の 50 ミル UPDI ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

表 4-14。 Atmel-ICE UPDI ピン マッピング

| Atmel-ICE AVR ポートピン | ターゲットピン | ミニイカピン |

Atmel STK600 UPDI ピン配列 |

| ピン 1 (TCK) | 1 | ||

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | UPDI_DATA | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 | ||

| ピン 6 (nSRST) | 【/RESETセンス】 | 6 | 5 |

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | 9 | ||

| ピン10(GND) | 0 |

4.4.9 TPI 物理インターフェース

TPI は、一部の AVR ATtiny デバイス用のプログラミング専用インターフェイスです。 これはデバッグ インターフェイスではなく、これらのデバイスには OCD 機能がありません。 TPI インターフェースを備えた AVR を含むアプリケーション PCB を設計する場合、下図に示すピン配置を使用する必要があります。

図 4-13。 TPI ヘッダーのピン配列 4.4.10.TPI ターゲットへの接続

4.4.10.TPI ターゲットへの接続

6 ピン TPI コネクタの推奨ピン配置を図 4-13 に示します。

6 ピン 100 ミル TPI ヘッダーへの接続

フラット ケーブル (一部のキットに含まれる) の 6 ピン 100 ミル タップを使用して、標準の 100 ミル TPI ヘッダーに接続します。

6 ピン 50 ミル TPI ヘッダーへの接続

アダプタ ボード (一部のキットに含まれる) を使用して、標準の 50 ミル TPI ヘッダーに接続します。

カスタム 100 ミル ヘッダーへの接続

Atmel-ICE AVR コネクタ ポートとターゲット ボード間の接続には、10 ピンのミニ イカ ケーブルを使用する必要があります。 次の表に示すように、XNUMX つの接続が必要です。

表 4-15。 Atmel-ICE TPI ピン マッピング

| Atmel-ICE AVR ポート ピン | ターゲットピン | ミニイカピン |

TPI ピン配列 |

| ピン 1 (TCK) | クロック | 1 | 3 |

| ピン2(GND) | グランド | 2 | 6 |

| ピン 3 (TDO) | データ | 3 | 1 |

| ピン 4 (VTG) | VTGE の | 4 | 2 |

| ピン 5 (TMS) | 5 | ||

| ピン 6 (nSRST) | / RESET | 6 | 5 |

| ピン 7 (未接続) | 7 | ||

| ピン 8 (nTRST) | 8 | ||

| ピン 9 (TDI) | 9 | ||

| ピン10(GND) | 0 |

4.4.11. 高度なデバッグ (AVR JTAG /debugWIRE デバイス)

I/O ペリフェラル

プログラムの実行がブレークポイントによって停止されても、ほとんどの I/O 周辺機器は引き続き実行されます。 元ample: UART 送信中にブレークポイントに到達すると、送信が完了し、対応するビットが設定されます。 TXC (送信完了) フラグが設定され、コードの次の XNUMX つのステップで使用可能になりますが、実際のデバイスでは通常後で発生します。

すべての I/O モジュールは、次の XNUMX つの例外を除いて、停止モードで引き続き実行されます。

- タイマー/カウンター (ソフトウェア フロントエンドを使用して構成可能)

- ウォッチドッグ タイマー (デバッグ中のリセットを防ぐために常に停止)

シングル ステッピング I/O アクセス

I/O は停止モードで実行し続けるため、特定のタイミングの問題を回避するように注意する必要があります。 例えばampファイル、コード:

このコードを正常に実行すると、TEMP レジスタは 0xAA を読み戻せません。ampIN作戦が主導。 正しい値が PIN レジスタに存在することを保証するために、NOP 命令を OUT 命令と IN 命令の間に配置する必要があります。

ただし、OCD を介してこの関数をシングル ステップすると、シングル ステップ中にコアが停止している場合でも I/O がフル スピードで実行されるため、このコードは常に PIN レジスタに 0xAA を与えます。

シングルステップとタイミング

特定のレジスタは、制御信号を有効にした後、所定のサイクル数内で読み書きする必要があります。 I/O クロックとペリフェラルは停止モードでもフル スピードで動作し続けるため、このようなコードを XNUMX ステップ実行してもタイミング要件を満たせません。 XNUMX つの単一ステップの間で、I/O クロックは数百万サイクルを実行した可能性があります。 このようなタイミング要件でレジスタの読み取りまたは書き込みを正常に行うには、読み取りまたは書き込みシーケンス全体を、デバイスをフルスピードで実行するアトミック操作として実行する必要があります。 これは、マクロまたは関数呼び出しを使用してコードを実行するか、デバッグ環境で run-to-cursor 関数を使用して実行できます。

16 ビットレジスタへのアクセス

Atmel AVR ペリフェラルは通常、16 ビット データ バス (例: 8 ビット タイマーの TCNTn) を介してアクセスできるいくつかの 16 ビット レジスタを含んでいます。 16 ビット レジスタは、16 つの読み取りまたは書き込み操作を使用してバイト アクセスする必要があります。 XNUMX ビット アクセスの途中で中断したり、この状況をシングル ステップで通過したりすると、誤った値が生じる可能性があります。

制限付き I/O レジスタ アクセス

一部のレジスタは、その内容に影響を与えずに読み取ることができません。 このようなレジスタには、読み取りによってクリアされるフラグを含むもの、またはバッファリングされたデータ レジスタ (例: UDR) が含まれます。 ソフトウェア フロントエンドは、停止モードのときにこれらのレジスタの読み取りを防止して、OCD デバッグの非侵入型の性質を維持します。 さらに、一部のレジスタは、副作用が発生しない限り安全に書き込むことができません。これらのレジスタは読み取り専用です。 例えばamp上:

- フラグ レジスタ。フラグは任意のレジスタに「1」を書き込むことでクリアされます。これらのレジスタは読み取り専用です。

- UDR および SPDR レジスタは、モジュールの状態に影響を与えずに読み取ることはできません。 これらのレジスタは

4.4.12. megaAVR の特別な考慮事項

ソフトウェア ブレークポイント

それはOCDモジュールの初期のバージョンを含んでいるので、ATmega128[A]はソフトウェア ブレークポイントのためのBREAK命令の使用を支援しません。

JTAG クロック

デバッグ セッションを開始する前に、ターゲット クロック周波数をソフトウェア フロントエンドで正確に指定する必要があります。 同期の理由から、JTAG 信頼性の高いデバッグを行うには、TCK 信号をターゲット クロック周波数の XNUMX/XNUMX 未満にする必要があります。 J 経由でプログラミングする場合TAG インターフェイスでは、TCK 周波数は、実際に使用されているクロック周波数ではなく、ターゲット デバイスの最大周波数定格によって制限されます。

内部 RC オシレータを使用する場合、周波数はデバイスによって異なり、温度と V の影響を受けることに注意してください。CC 変化します。 ターゲット クロック周波数を指定するときは慎重に行ってください。

JTAGEN および OCDEN ヒューズ

JTAG J を使用してインターフェイスを有効にします。TAGデフォルトでプログラムされている EN ヒューズ。 これにより、J へのアクセスが許可されます。TAG プログラミングインターフェース。 このメカニズムにより、OCDEN ヒューズをプログラムできます (デフォルトでは、OCDEN はプログラムされていません)。 これにより、OCD へのアクセスが可能になり、デバイスのデバッグが容易になります。 ソフトウェア フロントエンドは、セッションの終了時に OCDEN ヒューズがプログラムされていないことを常に保証し、OCD モジュールによる不要な電力消費を制限します。 Jの場合TAGEN ヒューズが意図せず無効になりました。SPI または High Vol を使用してのみ再度有効にすることができますtage プログラミング方法。

Jの場合TAGEN ヒューズがプログラムされ、JTAG JTD ビットを設定することにより、インターフェイスをファームウェアで無効にすることができます。 これにより、コードがデバッグ不能になるため、デバッグ セッションを試みるときは実行しないでください。 デバッグ セッションの開始時にそのようなコードが Atmel AVR デバイスで既に実行されている場合、Atmel-ICE は接続中に RESET ラインをアサートします。 このラインが正しく配線されている場合、ターゲットの AVR デバイスを強制的にリセットし、J を許可します。TAG 繋がり。

Jの場合TAG インターフェイスが有効になっている場合、JTAG ピンを別のピン機能に使用することはできません。 彼らは献身的であり続けます JTAG Jのいずれかまでピン留めTAG プログラム コードから JTD ビットを設定するか、J ビットをクリアすることにより、インターフェイスが無効になります。TAGプログラミング インターフェイスを介した EN ヒューズ。

![]() ヒント:

ヒント:

Atmel-ICE が RESET ラインをアサートし、J を再度有効にできるようにするために、プログラミング ダイアログとデバッグ オプション ダイアログの両方で「外部リセットを使用する」チェックボックスを必ずチェックしてください。TAG J を無効にするコードを実行しているデバイスのインターフェイスTAG JTD ビットを設定することにより、インターフェース

IDR/OCDR イベント

IDR (インアウト データ レジスタ) は OCDR (オン チップ デバッグ レジスタ) とも呼ばれ、デバッグ セッション中に停止モードにあるときに MCU に情報を読み書きするためにデバッガによって広く使用されます。 実行モードのアプリケーション プログラムがデバッグ中の AVR デバイスの OCDR レジスタに 50 バイトのデータを書き込むと、Atmel-ICE はこの値を読み出してソフトウェア フロントエンドのメッセージ ウィンドウに表示します。 OCDR レジスタは XNUMXms ごとにポーリングされるため、より高い頻度で書き込みを行っても信頼できる結果は得られません。 デバッグ中に AVR デバイスの電源が失われると、誤った OCDR イベントが報告されることがあります。 これは、Atmel-ICE がまだデバイスをターゲット ボリュームとしてポーリングしている可能性があるために発生します。tage が AVR の最小動作容量を下回るtage.

4.4.13. AVR XMEGAの特別な考慮事項

OCD とクロッキング

MCU が停止モードに入ると、OCD クロックが MCU クロックとして使用されます。 OCD クロックは JTAG Jの場合TCKTAG インターフェイスが使用されているか、または PDI インターフェイスが使用されている場合は PDI_CLK。

停止モードの I/O モジュール

以前の Atmel megaAVR デバイスとは対照的に、XMEGA では I/O モジュールは停止モードで停止します。 これは、USART 送信が中断され、タイマー (および PWM) が停止されることを意味します。

ハードウェア ブレークポイント

XNUMX つのアドレス コンパレータと XNUMX つの値コンパレータの XNUMX つのハードウェア ブレークポイント コンパレータがあります。 特定の制限があります。

- すべてのブレークポイントは同じタイプ (プログラムまたはデータ) でなければなりません

- すべてのデータ ブレークポイントは、同じメモリ領域 (I/O、SRAM、または XRAM) にある必要があります。

- アドレス範囲が使用されている場合、ブレークポイントは XNUMX つしか存在できません

設定できるさまざまな組み合わせを次に示します。

- XNUMX つの単一データまたはプログラム アドレス ブレークポイント

- XNUMX つのデータまたはプログラム アドレス範囲のブレークポイント

- 単一の値を比較する XNUMX つの単一データ アドレス ブレークポイント

- アドレス範囲、値範囲、またはその両方を持つ XNUMX つのデータ ブレークポイント

Atmel Studio は、ブレークポイントを設定できない場合とその理由を教えてくれます。 ソフトウェア ブレークポイントが使用可能な場合、データ ブレークポイントはプログラム ブレークポイントよりも優先されます。

外部リセットと PDI 物理

PDI 物理インターフェイスは、リセット ラインをクロックとして使用します。 デバッグ中は、リセット プルアップを 10k 以上にするか、削除する必要があります。 リセット コンデンサはすべて取り外す必要があります。 他の外部リセット ソースは切断する必要があります。

ATxmegaA1 rev H 以前のスリープを伴うデバッグ

ATxmegaA1 デバイスの初期のバージョンには、デバイスが特定のスリープ モードにある間に OCD が有効になるのを妨げるバグが存在していました。 OCD を再度有効にするには、次の XNUMX つの回避策があります。

- Atmel-ICE に入ります。 [ツール] メニューのオプションを開き、[デバイスの再プログラミング時に常に外部リセットを有効にする] を有効にします。

- チップ消去を実行する

このバグを引き起こすスリープ モードは次のとおりです。

- パワーダウン

- パワーセーブ

- 待機する

- 延長待機

4.4.1.debugWIRE の特別な考慮事項

debugWIRE 通信ピン (dW) は、物理的に外部リセット (RESET) と同じピンに配置されています。 したがって、debugWIRE インターフェイスが有効な場合、外部リセット ソースはサポートされません。

debugWIRE インターフェイスを機能させるには、ターゲット デバイスで debugWIRE イネーブル ヒューズ (DWEN) を設定する必要があります。 Atmel AVR デバイスが工場から出荷されるとき、このヒューズはデフォルトでプログラムされていません。 debugWIRE インターフェイス自体を使用してこのヒューズを設定することはできません。 DWEN ヒューズを設定するには、SPI モードを使用する必要があります。 必要な SPI ピンが接続されていれば、ソフトウェア フロントエンドがこれを自動的に処理します。 Atmel Studio プログラミング ダイアログから SPI プログラミングを使用して設定することもできます。

どちらか: debugWIRE 部分でデバッグ セッションを開始しようとします。 debugWIRE インターフェースが有効化されていない場合、Atmel Studio は再試行を提案するか、SPI プログラミングを使用して debugWIRE を有効化しようとします。 完全な SPI ヘッダーが接続されている場合、debugWIRE が有効になり、ターゲットの電源をオンにするように求められます。 これは、ヒューズの変更を有効にするために必要です。

または: SPI モードでプログラミング ダイアログを開き、署名が正しいデバイスと一致することを確認します。 DWEN ヒューズをチェックして、debugWIRE を有効にします。

![]() 重要:

重要:

SPIEN ヒューズをプログラムしたままにし、RSTDISBL ヒューズをプログラムしないことが重要です。 これを行わないと、デバイスが debugWIRE モードで停止し、High Vol になります。tagDWEN 設定を元に戻すには、プログラミングが必要です。

debugWIRE インターフェイスを無効にするには、High Vol を使用します。tagDWEN ヒューズをプログラム解除するための e プログラミング。 または、SPIEN ヒューズが設定されている場合、debugWIRE インターフェイス自体を使用してそれ自体を一時的に無効にします。これにより、SPI プログラミングを実行できるようになります。

![]() 重要:

重要:

SPIEN ヒューズがプログラムされたままになっていない場合、Atmel Studio はこの操作を完了できず、High Voltage プログラミングを使用する必要があります。

デバッグ セッション中に、[Debug] メニューから [Disable debugWIRE and Close] メニュー オプションを選択します。 DebugWIRE は一時的に無効になり、Atmel Studio は SPI プログラミングを使用して DWEN ヒューズのプログラムを解除します。

DWEN ヒューズをプログラムすると、クロック システムの一部をすべてのスリープ モードで動作させることができます。 これにより、スリープ モード中の AVR の消費電力が増加します。 したがって、debugWIRE を使用しない場合、DWEN ヒューズは常に無効にする必要があります。

debugWIRE を使用するターゲット アプリケーション PCB を設計する場合、正しく動作させるために次の点を考慮する必要があります。

- dW/(RESET) ラインのプルアップ抵抗は 10kΩ より小さく (強く) してはなりません。 debugWIRE 機能にはプルアップ抵抗は必要ありません。

- debugWIRE を使用する場合は、RESET ピンに接続されている安定化コンデンサを切断する必要があります。インターフェイスの正常な動作を妨げるためです。

- インターフェースの正しい動作に干渉する可能性があるため、RESET ライン上のすべての外部リセット ソースまたはその他のアクティブ ドライバを切断する必要があります。

ターゲット デバイスでロック ビットをプログラムしないでください。 debugWIRE インターフェイスでは、正しく機能するためにロック ビットをクリアする必要があります。

4.4.15. debugWIRE ソフトウェア ブレークポイント

Atmel megaAVR (JTAG) OCD。 これは、デバッグ目的でユーザーが使用できるプログラム カウンター ブレークポイント コンパレーターがないことを意味します。 run-to-cursor およびシングルステップ操作の目的でそのようなコンパレーターが XNUMX つ存在しますが、追加のユーザーブレークポイントはハードウェアでサポートされていません。

代わりに、デバッガは AVR BREAK 命令を使用する必要があります。 この命令は FLASH に置くことができ、実行のためにロードされると、AVR CPU は停止モードに入ります。 デバッグ中にブレークポイントをサポートするには、デバッガーは、ユーザーがブレークポイントを要求するポイントで BREAK 命令を FLASH に挿入する必要があります。 元の命令は、後で置き換えるためにキャッシュする必要があります。

BREAK 命令をシングル ステップ オーバーする場合、デバッガは、プログラムの動作を維持するために、元のキャッシュされた命令を実行する必要があります。 極端な場合、BREAK を FLASH から削除して後で置き換える必要があります。 これらのシナリオはすべて、ブレークポイントからのシングル ステップ実行時に明らかな遅延を引き起こす可能性があり、ターゲット クロック周波数が非常に低い場合に悪化します。

したがって、可能であれば、次のガイドラインに従うことをお勧めします。

- デバッグ中は常に、できるだけ高い頻度でターゲットを実行してください。 debugWIRE 物理インターフェイスは、ターゲット クロックからクロックされます。

- ブレークポイントの追加と削除の数を最小限に抑えるようにしてください。それぞれのターゲットで FLASH ページを置き換える必要があるためです。

- 一度に少数のブレークポイントを追加または削除して、FLASH ページの書き込み操作の数を最小限に抑えます。

- 可能であれば、ダブルワード命令にブレークポイントを配置しないでください

4.4.16. debugWIRE と DWEN Fuse を理解する

有効にすると、debugWIRE インターフェイスはデバイスの /RESET ピンを制御します。これにより、このピンも必要とする SPI インターフェイスと相互に排他的になります。 debugWIRE モジュールを有効または無効にする場合は、次の XNUMX つの方法のいずれかに従います。

- Atmel Studio に処理を任せる (推奨)

- DWEN を手動で設定およびクリアします (上級ユーザーのみ注意してください!)

![]() 重要: DWEN を手動で操作する場合、High-Vol を使用する必要がないように、SPIEN ヒューズを設定したままにしておくことが重要です。tag電子プログラミング

重要: DWEN を手動で操作する場合、High-Vol を使用する必要がないように、SPIEN ヒューズを設定したままにしておくことが重要です。tag電子プログラミング

図 4-14。 debugWIRE と DWEN Fuse を理解する 4.4.17.TinyX-OCD (UPDI) の特別な考慮事項

4.4.17.TinyX-OCD (UPDI) の特別な考慮事項

UPDI データ ピン (UPDI_DATA) は、対象の AVR デバイスに応じて、専用ピンまたは共有ピンにすることができます。 共有 UPDI ピンは 12V トレラントで、/RESET または GPIO として使用するように構成できます。 これらの構成でピンを使用する方法の詳細については、UPDI 物理インターフェイスを参照してください。

CRCSCAN モジュール (Cyclic Redundancy Check Memory Scan) を含むデバイスでは、デバッグ中にこのモジュールを連続バックグラウンド モードで使用しないでください。 OCD モジュールのハードウェア ブレークポイント コンパレータ リソースは限られているため、さらに多くのブレークポイントが必要な場合、またはソースレベル コードのステップ実行中にも、BREAK 命令をフラッシュ (ソフトウェア ブレークポイント) に挿入できます。 CRC モジュールは、このブレークポイントをフラッシュ メモリの内容の破損として誤って検出する可能性があります。

CRCSCAN モジュールは、ブート前に CRC スキャンを実行するように構成することもできます。 CRC が一致しない場合、デバイスは起動せず、ロックされた状態のように見えます。 この状態からデバイスを回復する唯一の方法は、完全なチップ消去を実行し、有効なフラッシュ イメージをプログラムするか、プリブート CRCSCAN を無効にすることです。 (単純なチップ消去は、CRC が無効なブランク フラッシュになるため、デバイスはまだ起動しません。) この状態でデバイスをチップ消去する場合、Atmel Studio は CRCSCAN ヒューズを自動的に無効にします。

UPDI インターフェイスが使用されるターゲット アプリケーション PCB を設計する場合、正しく動作するために次の点を考慮する必要があります。

- UPDI ラインのプルアップ抵抗は 10kΩ より小さく (強く) してはなりません。 プルダウン抵抗は使用しないか、UPDI を使用する場合は削除する必要があります。 UPDI 物理はプッシュプル対応であるため、ラインがオフになったときに誤ってスタート ビットがトリガーされるのを防ぐために、弱いプルアップ抵抗のみが必要です。

- UPDI ピンを RESET ピンとして使用する場合、インタフェースの正しい動作を妨げるため、UPDI を使用する際に安定化コンデンサを切断する必要があります。

- UPDI ピンを RESET または GPIO ピンとして使用する場合、インターフェイスの正しい動作に干渉する可能性があるため、プログラミングまたはデバッグ中にライン上のすべての外部ドライバーを切断する必要があります。

ハードウェアの説明

5.1.LED

Atmel-ICE の上部パネルには、現在のデバッグまたはプログラミング セッションのステータスを示す XNUMX つの LED があります。

テーブル 5-1. LED

| 導かれた | 関数 |

説明 |

| 左 | ターゲットパワー | ターゲットの電源が OK の場合は緑色。 点滅は、ターゲットの電源エラーを示します。 プログラミング/デバッグ セッション接続が開始されるまで点灯しません。 |

| 真ん中 | 主電源 | メインボードの電源が正常な場合は赤。 |

| 右 | 状態 | ターゲットが実行中/ステッピング中は緑色に点滅します。 ターゲット停止時はOFF。 |

5.2。 後面パネル

Atmel-ICE のリア パネルには Micro-B USB コネクタがあります。 5.3. ボトムパネル

5.3. ボトムパネル

Atmel-ICE の底部パネルには、シリアル番号と製造日を示すステッカーがあります。 技術サポートを求める場合は、これらの詳細を含めてください。 5.4 .アーキテクチャの説明

5.4 .アーキテクチャの説明

Atmel-ICE アーキテクチャは、図 5-1 のブロック図に示されています。

図 5-1。 Atmel-ICE ブロック図 5.4.1. Atmel-ICE メインボード

5.4.1. Atmel-ICE メインボード

電源は USB バスから Atmel-ICE に供給され、ステップダウン スイッチ モード レギュレータによって 3.3V に調整されます。 VTG ピンは基準入力としてのみ使用され、別の電源が可変 vol に給電します。tagオンボード レベル コンバーターの e 側。 Atmel-ICE メイン ボードの心臓部は Atmel AVR UC3 マイクロコントローラー AT32UC3A4256 で、処理されるタスクに応じて 1MHz から 60MHz で動作します。 マイクロコントローラにはオンチップの USB 2.0 高速モジュールが含まれており、デバッガとの間で高いデータ スループットを実現します。

Atmel-ICE とターゲット デバイス間の通信は、ターゲットの動作ボリューム間で信号をシフトするレベル コンバーターのバンクを介して行われます。tage と内部ボリュームtagAtmel-ICE の e レベル。 また、信号経路にはツェナーオーバーボルがありますtage 保護ダイオード、直列終端抵抗、誘導フィルタ、および ESD 保護ダイオード。 すべての信号チャネルは 1.62V ~ 5.5V の範囲で動作できますが、Atmel-ICE ハードウェアはより高いボリュームを駆動できません。tag5.0V以上。 最大動作周波数は、使用するターゲット インターフェイスによって異なります。

5.4.2.Atmel-ICE ターゲット コネクタ

Atmel-ICE にはアクティブなプローブがありません。 50 ミルの IDC ケーブルを使用して、ターゲット アプリケーションに直接接続するか、一部のキットに含まれるアダプタを介して接続します。 配線とアダプタの詳細については、「Atmel-ICE の組み立て」セクションを参照してください。

5.4.3. Atmel-ICE ターゲット コネクタの部品番号

Atmel-ICE 50 ミル IDC ケーブルをターゲット ボードに直接接続するには、標準の 50 ミル 10 ピン ヘッダーで十分です。 キットに含まれるアダプタ ボードで使用されているものなど、ターゲットに接続するときに正しい方向を確保するために、キー付きヘッダーを使用することをお勧めします。

このヘッダーの部品番号は次のとおりです: SAMTEC の FTSH-105-01-L-DV-KAP

ソフトウェア統合

6.1. アトメルスタジオ

6.1.1. Atmel Studio でのソフトウェア統合

Atmel Studio は、Windows 環境で Atmel AVR および Atmel SAM アプリケーションを作成およびデバッグするための統合開発環境 (IDE) です。 Atmel Studio は、プロジェクト管理ツール、ソースを提供します。 file C/C++、プログラミング、エミュレーション、およびオンチップ デバッグ用のエディター、シミュレーター、アセンブラー、およびフロントエンド。

Atmel Studio バージョン 6.2 以降を Atmel-ICE と組み合わせて使用する必要があります。

6.1.2. プログラミングオプション

Atmel Studio は、Atmel-ICE を使用して Atmel AVR および Atmel SAM ARM デバイスのプログラミングをサポートします。 プログラミング ダイアログは、J を使用するように構成できます。TAG、aWire、SPI、PDI、TPI、SWD モード (選択したターゲット デバイスに応じて)。

クロック周波数を構成する場合、さまざまなインターフェイスとターゲット ファミリにさまざまなルールが適用されます。

- SPI プログラミングは、ターゲット クロックを利用します。 ターゲット デバイスが現在動作している周波数の XNUMX 分の XNUMX 未満になるようにクロック周波数を構成します。

- JTAG これは、プログラミング クロック周波数がデバイス自体の最大動作周波数に制限されることを意味します。 (通常は 16MHz)

- 両方の J での AVR XMEGA プログラミングTAG また、PDI インターフェイスはプログラマによってクロックされます。 これは、プログラミング クロック周波数がデバイスの最大動作周波数 (通常は 32MHz) に制限されることを意味します。

- J での AVR UC3 プログラミングTAG インターフェイスはプログラマによってクロックされます。 これは、プログラミング クロック周波数がデバイス自体の最大動作周波数に制限されることを意味します。 (33MHz限定)

- aWire インターフェース上の AVR UC3 プログラミングは、ターゲット デバイスの SAB バス速度によって最適な周波数が与えられます。 Atmel-ICE デバッガは、この基準を満たすように aWire ボーレートを自動的に調整します。 通常は必要ありませんが、ユーザーは必要に応じて最大ボーレートを制限できます (ノイズの多い環境など)。

- SWD インターフェイスでの SAM デバイスのプログラミングは、プログラマによってクロックされます。 Atmel-ICE がサポートする最大周波数は 2MHz です。 周波数は、ターゲット CPU 周波数の 10 倍 (fSWD ≤ 10fSYSCLK) を超えてはなりません。

6.1.3.デバッグオプション

Atmel Studio を使用して Atmel AVR デバイスをデバッグする場合、プロジェクト プロパティの [ツール] タブ view いくつかの重要な設定オプションが含まれています。 詳細な説明が必要なオプションについては、こちらで詳しく説明しています。

ターゲット クロック周波数

J を介して Atmel megaAVR デバイスの信頼性の高いデバッグを実現するには、ターゲット クロック周波数を正確に設定することが不可欠です。TAG インターフェース。 この設定は、デバッグ中のアプリケーションで AVR ターゲット デバイスの最低動作周波数の XNUMX 分の XNUMX 未満にする必要があります。 詳細については、megaAVR の特別な考慮事項を参照してください。

debugWIRE ターゲット デバイスでのデバッグ セッションは、ターゲット デバイス自体によってクロックされるため、周波数設定は必要ありません。 Atmel-ICE は、デバッグ セッションの開始時に通信するための正しいボー レートを自動的に選択します。 ただし、ノイズの多いデバッグ環境に関連する信頼性の問題が発生している場合、一部のツールは、debugWIRE の速度を「推奨」設定の一部に強制する可能性を提供します。

AVR XMEGA ターゲット デバイスでのデバッグ セッションは、デバイス自体の最大速度 (通常 32MHz) までクロックできます。

J を介した AVR UC3 ターゲット デバイスでのデバッグ セッションTAG インターフェイスは、デバイス自体の最大速度 (33MHz に制限) までクロックできます。 ただし、最適な周波数は、ターゲット デバイスの現在の SAB クロックよりわずかに低くなります。

aWire インターフェースを介した UC3 ターゲット デバイスでのデバッグ セッションは、Atmel-ICE 自体によって最適なボー レートに自動的に調整されます。 ただし、ノイズの多いデバッグ環境に関連する信頼性の問題が発生している場合、一部のツールは、aWire 速度を構成可能な制限未満に強制する可能性を提供します。

SWD インターフェースを介した SAM ターゲット デバイスでのデバッグ セッションは、CPU クロックの最大 2 倍でクロックできます (ただし、最大 XNUMXMHz に制限されます)。

EEPROM を保持

デバッグ セッション前のターゲットの再プログラミング中に EEPROM が消去されないようにするには、このオプションを選択します。

外部リセットを使用する

ターゲット アプリケーションが J を無効にする場合TAG インターフェイスでは、プログラミング中に外部リセットを Low にする必要があります。 このオプションを選択すると、外部リセットを使用するかどうかを繰り返し尋ねられることを回避できます。

6.2 コマンドラインユーティリティ

Atmel Studio には、Atmel-ICE を使用してターゲットをプログラムするために使用できる atprogram と呼ばれるコマンド ライン ユーティリティが付属しています。 Atmel Studio のインストール中に、「Atmel Studio 7.0. Command Prompt」は、スタート メニューの Atmel フォルダに作成されました。 このショートカットをダブルクリックすると、コマンド プロンプトが開き、プログラミング コマンドを入力できます。 コマンド ライン ユーティリティは、フォルダ Atmel/Atmel Studio 7.0/atbackend/ の Atmel Studio インストール パスにインストールされます。

コマンド ライン ユーティリティのヘルプを表示するには、次のコマンドを入力します。

atprogram –ヘルプ

高度なデバッグ技術

7.1. Atmel AVR UC3 ターゲット

7.1.1. EVTI / EVTO の使用法

EVTI および EVTO ピンは、Atmel-ICE ではアクセスできません。 ただし、他の外部機器と組み合わせて使用することはできます。

EVTI は、次の目的で使用できます。

- ターゲットは、外部イベントに応答して強制的に実行を停止できます。 DC レジスタのイベント イン コントロール (EIC) ビットが 0b01 に書き込まれると、EVTI ピンのハイからローへの遷移によってブレークポイント条件が生成されます。 EVTI は、ブレークポイントが確実に XNUMX つの CPU クロック サイクルの間 Low のままである必要があります。これが発生すると、DS の外部ブレークポイント ビット (EXB) がセットされます。

- トレース同期メッセージを生成しています。 Atmel-ICE では使用されません。 EVTO は、次の目的で使用できます。

- CPU がデバッグ モードに入ったことを示す DC の EOS ビットを 0b01 に設定すると、ターゲット デバイスがデバッグ モードに入るときに、EVTO ピンが XNUMX CPU クロック サイクルの間 Low になります。 この信号は、外部オシロスコープのトリガー ソースとして使用できます。

- CPU がブレークポイントまたはウォッチポイントに到達したことを示します。 対応するブレークポイント/ウォッチポイント制御レジスタの EOC ビットを設定することにより、ブレークポイントまたはウォッチポイントのステータスが EVTO ピンに示されます。 この機能を有効にするには、DC の EOS ビットを 0xb10 に設定する必要があります。 その後、EVTO ピンを外部オシロスコープに接続して、ウォッチポイントを調べることができます。

- トレース タイミング信号の生成。 Atmel-ICE では使用されません。

7.2 debugWIRE ターゲット

7.2.1.debugWIRE ソフトウェア ブレークポイント

Atmel megaAVR (JTAG) OCD。 これは、デバッグ目的でユーザーが使用できるプログラム カウンター ブレークポイント コンパレーターがないことを意味します。 run-to-cursor およびシングルステップ操作の目的でそのようなコンパレーターが XNUMX つ存在しますが、追加のユーザーブレークポイントはハードウェアでサポートされていません。

代わりに、デバッガは AVR BREAK 命令を使用する必要があります。 この命令は FLASH に置くことができ、実行のためにロードされると、AVR CPU は停止モードに入ります。 デバッグ中にブレークポイントをサポートするには、デバッガーは、ユーザーがブレークポイントを要求するポイントで BREAK 命令を FLASH に挿入する必要があります。 元の命令は、後で置き換えるためにキャッシュする必要があります。

BREAK 命令をシングル ステップ オーバーする場合、デバッガは、プログラムの動作を維持するために、元のキャッシュされた命令を実行する必要があります。 極端な場合、BREAK を FLASH から削除して後で置き換える必要があります。 これらのシナリオはすべて、ブレークポイントからのシングル ステップ実行時に明らかな遅延を引き起こす可能性があり、ターゲット クロック周波数が非常に低い場合に悪化します。

したがって、可能であれば、次のガイドラインに従うことをお勧めします。

- デバッグ中は常に、できるだけ高い頻度でターゲットを実行してください。 debugWIRE 物理インターフェイスは、ターゲット クロックからクロックされます。

- ブレークポイントの追加と削除の数を最小限に抑えるようにしてください。それぞれのターゲットで FLASH ページを置き換える必要があるためです。

- 一度に少数のブレークポイントを追加または削除して、FLASH ページの書き込み操作の数を最小限に抑えます。

- 可能であれば、ダブルワード命令にブレークポイントを配置しないでください

リリース履歴と既知の問題

8.1 .ファームウェアのリリース履歴

表 8-1. 公開ファームウェアのリビジョン

| ファームウェアのバージョン (XNUMX 進数) | 日付 |

関連する変更 |

| 1.36 | 29.09.2016 | UPDI インターフェイス (tinyX デバイス) のサポートを追加 USB エンドポイントのサイズを構成可能にしました |

| 1.28 | 27.05.2015 | SPI および USART DGI インターフェイスのサポートが追加されました。 SWDの速度が向上しました。 マイナーなバグ修正。 |

| 1.22 | 03.10.2014 | コードのプロファイリングを追加しました。 Jに関連する問題を修正TAG 64 命令ビットを超えるデイジー チェーン。 ARM リセット拡張の修正。 ターゲットの電源 LED の問題を修正しました。 |

| 1.13 | 08.04.2014 | JTAG クロック周波数修正。 長い SUT を使用した debugWIRE の修正。 発振器キャリブレーション コマンドを修正しました。 |

| 1.09 | 12.02.2014 | Atmel-ICE の最初のリリース。 |

8.2. Atmel-ICE に関する既知の問題

8.2.1.一般

- 最初の Atmel-ICE バッチには弱い USB がありました。 新しいリビジョンが新しくより堅牢な USB コネクタで作成されました。 暫定的な解決策として、機械的安定性を向上させるために、最初のバージョンのすでに製造されたユニットにエポキシ接着剤が適用されました。

8.2.2. Atmel AVR XMEGA OCD 固有の問題

- ATxmegaA1 ファミリでは、リビジョン G 以降のみがサポートされています。

8.2.1. Atmel AVR – デバイス固有の問題

- デバッグ セッション中に ATmega32U6 の電源を入れ直すと、デバイスとの接続が失われる可能性があります。

製品コンプライアンス

9.1. RoHSおよびWEEE

Atmel-ICE とすべてのアクセサリは、RoHS 指令 (2002/95/EC) と WEEE 指令 (2002/96/EC) の両方に従って製造されています。

9.2. CEおよびFCC

Atmel-ICE ユニットは、必須要件および指令のその他の関連条項に従ってテストされています。

- 指令 2004/108/EC (クラス B)

- FCC パート 15 サブパート B

- 2002/95/EC (RoHS、WEEE)

評価には次の基準が使用されます。

- EN 61000-6-1(2007)

- EN 61000-6-3 (2007) + A1 (2011)

- FCC CFR 47 パート 15 (2013)

技術的構造 File は次の場所にあります:

この製品からの電磁放射を最小限に抑えるために、あらゆる努力が払われています。 ただし、特定の条件下では、システム (対象のアプリケーション回路に接続されたこの製品) は、上記の規格で許可されている最大値を超える個々の電磁成分周波数を放出する場合があります。 エミッションの頻度と大きさは、製品が使用されるターゲット アプリケーションのレイアウトとルーティングを含むいくつかの要因によって決まります。

改訂履歴

|

Doc。 牧師 |

日付 |

コメント |

| 42330C | 10/2016 | UPDI インターフェイスを追加し、ファームウェアのリリース履歴を更新 |

| 42330B | 03/2016 | • オンチップデバッグの章を改訂 • リリース履歴と既知の問題の章のファームウェア リリース履歴の新しいフォーマット • デバッグ ケーブルのピン配置を追加 |

| 42330A | 06/2014 | 最初のドキュメントリリース |

アトメル®、Atmel ロゴとその組み合わせ、無限の可能性を実現®、AVR®、メガAVR®、STK®、tinyAVR®、XMEGA®、およびその他は、米国およびその他の国における Atmel Corporation の登録商標または商標です。 腕®、ARM コネクテッド® ロゴ、コーテックス®、その他は ARM Ltd. の登録商標または商標です。 Windows® は、米国およびその他の国における Microsoft Corporation の登録商標です。 その他の用語および製品名は、他社の商標である場合があります。

免責事項: この文書の情報は、Atmel 製品に関連して提供されています。 禁反言またはその他の方法による明示的または黙示的なライセンスは、この文書によって、または Atmel 製品の販売に関連して付与されるものではありません。 ATMEL での販売に関する ATMEL 利用規約に規定されている場合を除きます。 WEBサイト、ATMEL は一切の責任を負わず、商品性、特定の目的への適合性、または非侵害の黙示の保証を含むがこれらに限定されない、その製品に関する明示的、黙示的、または法定の保証を否認します。 ATMEL は、いかなる場合も、使用または使用不能に起因するいかなる直接的、間接的、結果的、懲罰的、特別または偶発的な損害 (損失と利益、事業の中断、または情報の損失に対する損害を含むがこれらに限定されない) に対しても責任を負わないものとします。この文書は、ATMEL が助言を受けていたとしても

そのような損害の可能性について。 Atmel は、このドキュメントの内容の正確性または完全性に関して表明または保証を行わず、いつでも予告なしに仕様および製品の説明を変更する権利を留保します。 Atmel は、ここに含まれる情報を更新する約束をしません。 特に別段の規定がない限り、Atmel 製品は自動車用途には適しておらず、また使用してはなりません。 Atmel 製品は、生命をサポートまたは維持することを目的としたアプリケーションのコンポーネントとして使用することを意図、承認、または保証していません。

セーフティ クリティカル、ミリタリー、およびオートモーティブ アプリケーションの免責事項: Atmel 製品は、そのような製品の故障が重大な人身傷害または死亡に至ることが合理的に予想されるアプリケーション向けに設計されておらず、使用されません (「セーフティ クリティカルアプリケーション」) Atmel 役員の特定の書面による同意なしに。 安全性が重要なアプリケーションには、生命維持装置およびシステム、核施設および兵器システムの運用のための機器またはシステムが含まれますが、これらに限定されません。 Atmel 製品は、特に Atmel が軍用グレードとして指定しない限り、軍用または航空宇宙用途または環境で使用するように設計されておらず、意図されていません。 Atmel 製品は、特に Atmel が自動車グレードとして指定しない限り、自動車アプリケーションで使用するように設計されておらず、意図されていません。

アトメル株式会社

アトメル株式会社

1600 Technology Drive、サンノゼ、CA 95110 USA

T:(+1)(408)441.0311

ファックス: (+1)(408) 436.4200

ウェブサイト

© 2016 アトメル株式会社。

Rev.: Atmel-42330C-Atmel-ICE_ユーザー ガイド-10/2016

![]()

ドキュメント / リソース

|

Atmel Atmel-ICE デバッガー プログラマー [pdf] ユーザーガイド Atmel-ICE デバッガー プログラマー、Atmel-ICE、デバッガー プログラマー、プログラマー |