Programadores de depuração ICE

Programadores de depuração ICE

Guia do usuário Programadores e Depuradores

Programadores e Depuradores

Atmel-ICE

GUIA DO USUÁRIO

O depurador Atmel-ICE

O Atmel-ICE é uma poderosa ferramenta de desenvolvimento para depuração e programação de microcontroladores Atmel ®SAM e Atmel AVR baseados em ARM® Cortex®-M com capacidade ® On-Chip Debug.

Ele suporta:

- Programação e depuração no chip de todos os microcontroladores Atmel AVR de 32 bits em JTAG e interfaces aWire

- Programação e depuração no chip de todos os dispositivos da família Atmel AVR XMEGA® em JTAG e interfaces PDI de 2 fios

- Programação (JTAG, SPI, UPDI) e depuração de todos os microcontroladores Atmel AVR de 8 bits com suporte a OCD em JTAG, interfaces debugWIRE ou UPDI

- Programação e depuração de todos os microcontroladores Atmel SAM ARM Cortex-M baseados em SWD e JTAG Interfaces

- Programação (TPI) de todos os microcontroladores Atmel tinyAVR® de 8 bits com suporte para esta interface

Consulte a lista de dispositivos compatíveis no Guia do usuário do Atmel Studio para obter uma lista completa de dispositivos e interfaces compatíveis com esta versão de firmware.

Introdução

1.1. Introdução ao Atmel-ICE

O Atmel-ICE é uma poderosa ferramenta de desenvolvimento para depuração e programação de microcontroladores Atmel SAM e Atmel AVR baseados em ARM Cortex-M com capacidade de depuração no chip.

Ele suporta:

- Programação e depuração no chip de todos os microcontroladores Atmel AVR UC3 em JTAG e interfaces aWire

- Programação e depuração no chip de todos os dispositivos da família AVR XMEGA em JTAG e interfaces PDI 2 fios

- Programação (JTAG e SPI) e depuração de todos os microcontroladores AVR de 8 bits com suporte a OCD em JTAG ou interfaces debugWIRE

- Programação e depuração de todos os microcontroladores Atmel SAM ARM Cortex-M baseados em SWD e JTAG Interfaces

- Programação (TPI) de todos os microcontroladores Atmel tinyAVR de 8 bits com suporte para esta interface

1.2. Recursos do Atmel-ICE

- Totalmente compatível com Atmel Studio

- Suporta programação e depuração de todos os microcontroladores Atmel AVR UC3 de 32 bits

- Suporta programação e depuração de todos os dispositivos AVR XMEGA de 8 bits

- Suporta programação e depuração de todos os dispositivos Atmel megaAVR® e tinyAVR de 8 bits com TOC

- Suporta programação e depuração de todos os microcontroladores baseados em SAM ARM Cortex-M

- Volume operacional alvotagFaixa de 1.62 V a 5.5 V

- Consome menos de 3mA do Vtref alvo ao usar a interface debugWIRE e menos de 1mA para todas as outras interfaces

- Suporta JTAG frequências de clock de 32kHz a 7.5MHz

- Suporta frequências de clock PDI de 32kHz a 7.5MHz

- Suporta taxas de transmissão debugWIRE de 4 kbit/s a 0.5 Mbit/s

- Suporta taxas de transmissão aWire de 7.5 kbit/s a 7 Mbit/s

- Suporta frequências de clock SPI de 8kHz a 5MHz

- Suporta taxas de transmissão UPDI de até 750kbit/s

- Suporta frequências de relógio SWD de 32kHz a 10MHz

- Interface de host USB 2.0 de alta velocidade

- Captura de rastreamento serial ITM em até 3 MB/s

- Suporta interfaces DGI SPI e USART quando não estiver depurando ou programando

- Suporta 10 pinos 50 mil JTAG conector com pinagens AVR e Cortex. O cabo de sonda padrão suporta cabeçotes AVR de 6 pinos ISP/PDI/TPI de 100 mil, bem como cabeçotes de 10 pinos de 50 mil. Um adaptador está disponível para suportar headers de 6 pinos 50 mil, 10 pinos 100 mil e 20 pinos 100 mil. Várias opções de kit estão disponíveis com diferentes cabos e adaptadores.

1.3. Requisitos do sistema

A unidade Atmel-ICE requer que um ambiente de depuração de front-end Atmel Studio versão 6.2 ou posterior esteja instalado em seu computador.

O Atmel-ICE deve ser conectado ao computador host usando o cabo USB fornecido ou um cabo Micro-USB certificado.

Introdução ao Atmel-ICE

2.1. Conteúdo do Kit Completo

O kit completo Atmel-ICE contém estes itens:

- Unidade Atmel-ICE

- Cabo USB (1.8 m, alta velocidade, Micro-B)

- Placa adaptadora contendo adaptadores AVR de 50 mil, AVR/SAM de 100 mil e adaptadores SAM de 100 pinos de 20 mil

- Cabo plano IDC com conector de 10 pinos e 50 mil e conector de 6 pinos e 100 mil

- Cabo mini squid de 50 pinos de 10 mil com soquetes de 10 x 100 mil

Figura 2-1. Conteúdo do kit completo Atmel-ICE 2.2. Conteúdo do kit básico

2.2. Conteúdo do kit básico

O kit básico Atmel-ICE contém estes itens:

- Unidade Atmel-ICE

- Cabo USB (1.8 m, alta velocidade, Micro-B)

- Cabo plano IDC com conector de 10 pinos e 50 mil e conector de 6 pinos e 100 mil

Figura 2-2. Conteúdo do kit básico Atmel-ICE 2.3. Conteúdo do Kit PCBA

2.3. Conteúdo do Kit PCBA

O kit Atmel-ICE PCBA contém estes itens:

- Unidade Atmel-ICE sem encapsulamento plástico

Figura 2-3. Conteúdo do kit Atmel-ICE PCBA 2.4. Kits de peças de reposição

2.4. Kits de peças de reposição

Os seguintes kits de peças de reposição estão disponíveis:

- Kit adaptador

- kit de cabos

Figura 2-4. Conteúdo do kit do adaptador Atmel-ICE 2.5. Fim do kitview

2.5. Fim do kitview

As opções do kit Atmel-ICE são mostradas esquematicamente aqui:

Figura 2-6. Kit Atmel-ICE Overview 2.6. Montando o Atmel-ICE

2.6. Montando o Atmel-ICE

A unidade Atmel-ICE é enviada sem cabos conectados. Duas opções de cabo são fornecidas no kit completo:

- Cabo plano IDC de 50 pinos de 10 mil com ISP de 6 pinos e conectores de 10 pinos

- Cabo mini-squid de 50 pinos de 10 mil com soquetes de 10 x 100 mil

Figura 2-7. Cabos Atmel-ICE Para a maioria das finalidades, o cabo plano IDC de 50 pinos de 10 mil pode ser usado, conectando-se nativamente aos conectores de 10 ou 6 pinos ou conectando-o por meio da placa adaptadora. Três adaptadores são fornecidos em um pequeno PCBA. Os seguintes adaptadores estão incluídos:

Para a maioria das finalidades, o cabo plano IDC de 50 pinos de 10 mil pode ser usado, conectando-se nativamente aos conectores de 10 ou 6 pinos ou conectando-o por meio da placa adaptadora. Três adaptadores são fornecidos em um pequeno PCBA. Os seguintes adaptadores estão incluídos:

- 100 mil 10 pinos JTAG/Adaptador SWD

- 100 mil 20 pinos SAM JTAG/Adaptador SWD

- Adaptador SPI/debugWIRE/PDI/aWire de 50 mil 6 pinos

Figura 2-8. Adaptadores Atmel-ICE Observação:

Observação:

A 50 mil JTAG adaptador não foi fornecido - isso ocorre porque o cabo IDC de 50 pinos de 10 mil pode ser usado para conectar diretamente a um J de 50 milTAG cabeçalho. Para obter o número de peça do componente usado para o conector de 50 pinos de 10 mil, consulte Atmel-ICE Target Connectors Part Numbers.

O cabeçalho ISP/PDI de 6 pinos está incluído como parte do cabo IDC de 10 pinos. Esta terminação pode ser cortada se não for necessária.

Para montar seu Atmel-ICE em sua configuração padrão, conecte o cabo IDC de 10 pinos e 50 mil à unidade conforme mostrado abaixo. Certifique-se de orientar o cabo de forma que o fio vermelho (pino 1) do cabo fique alinhado com o indicador triangular na faixa azul do gabinete. O cabo deve ser conectado para cima da unidade. Certifique-se de conectar à porta correspondente à pinagem do seu alvo – AVR ou SAM.

Figura 2-9. Conexão de cabo Atmel-ICE Figura 2-10. Conexão de Sonda Atmel-ICE AVR

Figura 2-10. Conexão de Sonda Atmel-ICE AVR

Figura 2-11. Conexão de Sonda Atmel-ICE SAM

Figura 2-11. Conexão de Sonda Atmel-ICE SAM 2.7. Abertura do Atmel-ICE

2.7. Abertura do Atmel-ICE

Observação:

Para operação normal, a unidade Atmel-ICE não deve ser aberta. A abertura da unidade é feita por sua conta e risco.

Precauções antiestáticas devem ser tomadas.

O gabinete do Atmel-ICE consiste em três componentes plásticos separados – tampa superior, tampa inferior e correia azul – que são encaixados durante a montagem. Para abrir a unidade, basta inserir uma chave de fenda grande nas aberturas do cinto azul, aplicar alguma pressão para dentro e torcer suavemente. Repita o processo nos outros orifícios do snapper e a tampa superior se soltará.

Figura 2-12. Abrindo o Atmel-ICE (1)

Figura 2-13. Abrindo o Atmel-ICE (2)

Figura 2-13. Abrindo o Atmel-ICE (2)

Figura 2-14. Abrindo o Atmel-ICE(3)

Figura 2-14. Abrindo o Atmel-ICE(3) Para fechar a unidade novamente, simplesmente alinhe as tampas superior e inferior corretamente e pressione firmemente uma contra a outra.

Para fechar a unidade novamente, simplesmente alinhe as tampas superior e inferior corretamente e pressione firmemente uma contra a outra.

2.8. Alimentando o Atmel-ICE

O Atmel-ICE é alimentado pelo barramento USB voltage. Ele requer menos de 100mA para operar e, portanto, pode ser alimentado por um hub USB. O LED de energia acenderá quando a unidade estiver conectada. Quando não estiver conectada em uma programação ativa ou sessão de depuração, a unidade entrará no modo de baixo consumo de energia para preservar a bateria do seu computador. O Atmel-ICE não pode ser desligado – ele deve ser desconectado quando não estiver em uso.

2.9. Conectando ao computador host

O Atmel-ICE se comunica principalmente usando uma interface HID padrão e não requer um driver especial no computador host. Para usar a funcionalidade avançada do Data Gateway do Atmel-ICE, certifique-se de instalar o driver USB no computador host. Isso é feito automaticamente ao instalar o software front-end fornecido gratuitamente pela Atmel. Ver www.atmel.com para mais informações ou para baixar o software front-end mais recente.

O Atmel-ICE deve ser conectado a uma porta USB disponível no computador host usando o cabo USB fornecido ou um microcabo certificado USB adequado. O Atmel-ICE contém um controlador compatível com USB 2.0 e pode operar nos modos de velocidade total e alta velocidade. Para obter melhores resultados, conecte o Atmel-ICE diretamente a um hub de alta velocidade compatível com USB 2.0 no computador host usando o cabo fornecido.

2.10. Instalação do Driver USB

2.10.1. Janelas

Ao instalar o Atmel-ICE em um computador executando o Microsoft® Windows®, o driver USB é carregado quando o Atmel-ICE é conectado pela primeira vez.

Observação:

Certifique-se de instalar os pacotes de software front-end antes de conectar a unidade pela primeira vez.

Depois de instalado com sucesso, o Atmel-ICE aparecerá no gerenciador de dispositivos como um “Dispositivo de interface humana”.

Conectando o Atmel-ICE

3.1. Conectando-se a dispositivos de destino AVR e SAM

O Atmel-ICE é equipado com dois conectores J de 50 mil e 10 pinosTAG conectores. Ambos os conectores são diretamente conectados eletricamente, mas obedecem a duas pinagens diferentes; o AVR JTAG cabeçalho e o cabeçalho ARM Cortex Debug. O conector deve ser selecionado com base na pinagem da placa de destino e não no tipo de MCU de destino - por exemploamparquivo um dispositivo SAM montado em uma pilha AVR STK® 600 deve usar o cabeçalho AVR.

Vários cabos e adaptadores estão disponíveis nos diferentes kits Atmel-ICE. acabouview de opções de conexão é mostrado.

Figura 3-1. Opções de conexão Atmel-ICE O fio vermelho marca o pino 1 do conector de 10 pinos e 50 mil. O pino 1 do conector de 6 pinos de 100 mil é colocado à direita da codificação quando o conector é visto do cabo. O pino 1 de cada conector no adaptador é marcado com um ponto branco. A figura abaixo mostra a pinagem do cabo de depuração. O conector marcado como A se conecta ao depurador enquanto o lado B se conecta à placa de destino.

O fio vermelho marca o pino 1 do conector de 10 pinos e 50 mil. O pino 1 do conector de 6 pinos de 100 mil é colocado à direita da codificação quando o conector é visto do cabo. O pino 1 de cada conector no adaptador é marcado com um ponto branco. A figura abaixo mostra a pinagem do cabo de depuração. O conector marcado como A se conecta ao depurador enquanto o lado B se conecta à placa de destino.

Figura 3-2. Pinagem do cabo de depuração

3.2. Conectando a um JTAG Alvo

3.2. Conectando a um JTAG Alvo

O Atmel-ICE é equipado com dois conectores J de 50 mil e 10 pinosTAG conectores. Ambos os conectores são diretamente conectados eletricamente, mas obedecem a duas pinagens diferentes; o AVR JTAG cabeçalho e o cabeçalho ARM Cortex Debug. O conector deve ser selecionado com base na pinagem da placa de destino e não no tipo de MCU de destino - por exemploampum dispositivo SAM montado em uma pilha AVR STK600 deve usar o cabeçalho AVR.

A pinagem recomendada para o AVR J de 10 pinosTAG conector é mostrado na Figura 4-6. A pinagem recomendada para o conector ARM Cortex Debug de 10 pinos é mostrada na Figura 4-2.

Conexão direta a um cabeçote padrão de 10 pinos e 50 mil

Use o cabo plano de 50 pinos de 10 mil (incluído em alguns kits) para conectar diretamente a uma placa compatível com esse tipo de cabeçalho. Use a porta do conector AVR no Atmel-ICE para cabeçalhos com a pinagem AVR e a porta do conector SAM para cabeçalhos em conformidade com a pinagem de cabeçalho ARM Cortex Debug.

As pinagens para ambas as portas do conector de 10 pinos são mostradas abaixo.

Conexão a um cabeçote padrão de 10 pinos e 100 mil

Use um adaptador padrão de 50 mil para 100 mil para conectar a plataformas de 100 mil. Uma placa adaptadora (incluída em alguns kits) pode ser usada para essa finalidade ou, alternativamente, o JTAGO adaptador ICE3 pode ser usado para alvos AVR.

![]() Importante:

Importante:

O JTAGO adaptador ICE3 de 100 mil não pode ser usado com a porta do conector SAM, pois os pinos 2 e 10 (AVR GND) no adaptador estão conectados.

Conexão a um cabeçalho personalizado de 100 mil

Se sua placa de destino não tiver um conector J de 10 pinos compatívelTAG cabeçalho em 50 ou 100 mil, você pode mapear para uma pinagem personalizada usando o cabo “mini-squid” de 10 pinos (incluído em alguns kits), que dá acesso a dez soquetes individuais de 100 mil.

Conexão a um cabeçote de 20 pinos e 100 milr

Use a placa adaptadora (incluída em alguns kits) para conectar alvos com um cabeçalho de 20 pinos e 100 mil.

Tabela 3-1. Atmel-ICE JTAG Descrição do Pin

| Nome | AVR pino da porta | SÃO pino da porta | Descrição |

| TCK | 1 | 4 | Relógio de teste (sinal de relógio do Atmel-ICE para o dispositivo de destino). |

| EMT (Transmissão Transmissível) | 5 | 2 | Seleção do modo de teste (sinal de controle do Atmel-ICE para o dispositivo de destino). |

| TDI | 9 | 8 | Test Data In (dados transmitidos do Atmel-ICE para o dispositivo de destino). |

| TDO | 3 | 6 | Test Data Out (dados transmitidos do dispositivo de destino para o Atmel-ICE). |

| nTRST | 8 | – | Reinicialização de teste (opcional, apenas em alguns dispositivos AVR). Usado para redefinir o JTAG controlador TAP. |

| nSRST | 6 | 10 | Redefinir (opcional). Usado para redefinir o dispositivo de destino. A conexão desse pino é recomendada, pois permite que o Atmel-ICE mantenha o dispositivo de destino em um estado de redefinição, o que pode ser essencial para a depuração em determinados cenários. |

| VTG | 4 | 1 | Volume alvotage referência. O Atmel-ICE samples o alvo voltage neste pino para alimentar corretamente os conversores de nível. O Atmel-ICE consome menos de 3 mA desse pino no modo debugWIRE e menos de 1 mA em outros modos. |

| Terra | 2, 10 | 3, 5, 9 | Chão. Todos devem estar conectados para garantir que o Atmel-ICE e o dispositivo de destino compartilhem a mesma referência de aterramento. |

3.3. Conectando a um alvo aWire

A interface aWire requer apenas uma linha de dados além de VCC e GND. No alvo, esta linha é a linha nRESET, embora o depurador use o JTAG Linha TDO como a linha de dados.

A pinagem recomendada para o conector aWire de 6 pinos é mostrada na Figura 4-8.

Conexão a um conector aWire de 6 pinos e 100 mil

Use a derivação de 6 pinos de 100 mil no cabo plano (incluído em alguns kits) para conectar a um cabeçote aWire padrão de 100 mil.

Conexão a um conector aWire de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote aWire padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. São necessárias três conexões, conforme descrito na tabela abaixo.

Tabela 3-2. Mapeamento de pinos Atmel-ICE aWire

|

Pinos de porta Atmel-ICE AVR |

Alfinetes alvo | Pino de minilula |

pinagem aWire |

| Pino 1 (TCK) | 1 | ||

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | DADOS | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 | ||

| Pino 6 (nSRST) | 6 | ||

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | 9 | ||

| Pino 10 (GND) | 0 |

3.4. Conectando a um Alvo PDI

A pinagem recomendada para o conector PDI de 6 pinos é mostrada na Figura 4-11.

Conexão a um cabeçalho PDI de 6 pinos e 100 mil

Use a derivação de 6 milésimos de 100 pinos no cabo plano (incluído em alguns kits) para conectar a um cabeçote PDI padrão de 100 mil.

Conexão a um cabeçalho PDI de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote PDI padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. Quatro conexões são necessárias, conforme descrito na tabela abaixo.

![]() Importante:

Importante:

A pinagem necessária é diferente do JTAGICE mkII JTAG sonda, onde PDI_DATA está conectado ao pino 9. O Atmel-ICE é compatível com a pinagem usada pelo Atmel-ICE, JTAGProdutos ICE3, AVR ONE! e AVR Dragon™.

Tabela 3-3. Mapeamento de pinos Atmel-ICE PDI

| Pinos de porta Atmel-ICE AVR | Alfinetes alvo | Pino de minilula |

pinagem aWire |

| Pino 1 (TCK) | 1 | ||

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | DADOS | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 | ||

| Pino 6 (nSRST) | 6 | ||

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | 9 | ||

| Pino 10 (GND) | 0 |

3.4 Conectando a um Alvo PDI

A pinagem recomendada para o conector PDI de 6 pinos é mostrada na Figura 4-11.

Conexão a um cabeçalho PDI de 6 pinos e 100 mil

Use a derivação de 6 milésimos de 100 pinos no cabo plano (incluído em alguns kits) para conectar a um cabeçote PDI padrão de 100 mil.

Conexão a um cabeçalho PDI de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote PDI padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. Quatro conexões são necessárias, conforme descrito na tabela abaixo.

![]() Importante:

Importante:

A pinagem necessária é diferente do JTAGICE mkII JTAG sonda, onde PDI_DATA está conectado ao pino 9. O Atmel-ICE é compatível com a pinagem usada pelo Atmel-ICE, JTAGICE3, AVR ONE! e AVR Dragon™ produtos.

Tabela 3-3. Mapeamento de pinos Atmel-ICE PDI

| Pino da porta Atmel-ICE AVR | Alfinetes alvo | Pino de minilula | Pinagem Atmel STK600 PDI |

| Pino 1 (TCK) | 1 | ||

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | PDI_DADOS | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 | ||

| Pino 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | 9 | ||

| Pino 10 (GND) | 0 |

3.5 Conectando a um alvo UPDI

A pinagem recomendada para o conector UPDI de 6 pinos é mostrada na Figura 4-12.

Conexão a um cabeçalho UPDI de 6 pinos e 100 mil

Use a derivação de 6 pinos de 100 mil no cabo plano (incluído em alguns kits) para conectar a um cabeçote UPDI padrão de 100 mil.

Conexão a um cabeçalho UPDI de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote UPDI padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. São necessárias três conexões, conforme descrito na tabela abaixo.

Tabela 3-4. Mapeamento de pinos Atmel-ICE UPDI

| Pino da porta Atmel-ICE AVR | Alfinetes alvo | Pino de minilula |

Pinagem Atmel STK600 UPDI |

| Pino 1 (TCK) | 1 | ||

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 | ||

| Pino 6 (nSRST) | [/sentido REINICIALIZAR] | 6 | 5 |

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | 9 | ||

| Pino 10 (GND) | 0 |

3.6 Conectando a um alvo debugWIRE

A pinagem recomendada para o conector debugWIRE (SPI) de 6 pinos é mostrada na Tabela 3-6.

Conexão a um cabeçalho SPI de 6 pinos e 100 mil

Use a derivação de 6 pinos de 100 mil no cabo plano (incluído em alguns kits) para conectar a um conector SPI padrão de 100 mil.

Conexão a um cabeçalho SPI de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote SPI padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. São necessárias três conexões, conforme descrito na Tabela 3-5.

Embora a interface debugWIRE exija apenas uma linha de sinal (RESET), VCC e GND para operar corretamente, é aconselhável ter acesso ao conector SPI completo para que a interface debugWIRE possa ser ativada e desativada usando a programação SPI.

Quando o fusível DWEN está ativado, a interface SPI é substituída internamente para que o módulo OCD tenha controle sobre o pino RESET. O OCD debugWIRE é capaz de se desativar temporariamente (usando o botão na guia de depuração na caixa de diálogo de propriedades no Atmel Studio), liberando assim o controle da linha RESET. A interface SPI fica novamente disponível (somente se o fusível SPIEN estiver programado), permitindo que o fusível DWEN seja desprogramado usando a interface SPI. Se a energia for alternada antes que o fusível DWEN seja desprogramado, o módulo debugWIRE assumirá novamente o controle do pino RESET.

Observação:

É altamente recomendável simplesmente deixar que o Atmel Studio cuide da configuração e limpeza do fusível DWEN.

Não é possível usar a interface debugWIRE se os lockbits no dispositivo AVR de destino estiverem programados. Certifique-se sempre de que os lockbits foram apagados antes de programar o fusível DWEN e nunca defina os lockbits enquanto o fusível DWEN estiver programado. Se o fusível de habilitação debugWIRE (DWEN) e os lockbits estiverem definidos, pode-se usar o High Voltage Programação para fazer um chip erase, e assim limpar os lockbits.

Quando os lockbits forem apagados, a interface debugWIRE será reativada. A Interface SPI só é capaz de ler fusíveis, ler assinatura e executar um apagamento de chip quando o fusível DWEN estiver desprogramado.

Tabela 3-5. Atmel-ICE debugWIRE Pin Mapping

| Pino da porta Atmel-ICE AVR | Alfinetes alvo |

Pino de minilula |

| Pino 1 (TCK) | 1 | |

| Pino 2 (GND) | Terra | 2 |

| Pino 3 (TDO) | 3 | |

| Pino 4 (VTG) | VTG | 4 |

| Pino 5 (TMS) | 5 | |

| Pino 6 (nSRST) | REINICIAR | 6 |

| Pino 7 (não conectado) | 7 | |

| Pino 8 (nTRST) | 8 | |

| Pino 9 (TDI) | 9 | |

| Pino 10 (GND) | 0 |

3.7 Conectando a um alvo SPI

A pinagem recomendada para o conector SPI de 6 pinos é mostrada na Figura 4-10.

Conexão a um cabeçalho SPI de 6 pinos e 100 mil

Use a derivação de 6 pinos de 100 mil no cabo plano (incluído em alguns kits) para conectar a um conector SPI padrão de 100 mil.

Conexão a um cabeçalho SPI de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote SPI padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. Seis conexões são necessárias, conforme descrito na tabela abaixo.

![]() Importante:

Importante:

A interface SPI é efetivamente desabilitada quando o fusível habilitado debugWIRE (DWEN) é programado, mesmo que o fusível SPIEN também esteja programado. Para reativar a interface SPI, o comando 'disable debugWIRE' deve ser emitido durante uma sessão de depuração debugWIRE. Desativar o debugWIRE dessa maneira requer que o fusível SPIEN já esteja programado. Se o Atmel Studio não desativar o debugWIRE, é provável que o fusível SPIEN NÃO esteja programado. Se este for o caso, é necessário usar um alto-voltagInterface de programação para programar o fusível SPIEN.

![]() Informações:

Informações:

A interface SPI costuma ser chamada de “ISP”, pois foi a primeira interface de programação do sistema nos produtos Atmel AVR. Outras interfaces estão agora disponíveis para programação no sistema.

Tabela 3-6. Mapeamento de pinos Atmel-ICE SPI

| Pinos de porta Atmel-ICE AVR | Alfinetes alvo | Pino de minilula |

Pinagem SPI |

| Pino 1 (TCK) | SCK | 1 | 3 |

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | MISO | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 | ||

| Pino 6 (nSRST) | /REDEFINIR | 6 | 5 |

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | MOSI | 9 | 4 |

| Pino 10 (GND) | 0 |

3.8 Conectando a um alvo TPI

A pinagem recomendada para o conector TPI de 6 pinos é mostrada na Figura 4-13.

Conexão a um cabeçalho TPI de 6 pinos e 100 mil

Use a derivação de 6 milésimos de 100 pinos no cabo plano (incluído em alguns kits) para conectar a um cabeçote TPI padrão de 100 mil.

Conexão a um cabeçalho TPI de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote TPI padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. Seis conexões são necessárias, conforme descrito na tabela abaixo.

Tabela 3-7. Mapeamento de pinos TPI Atmel-ICE

| Pinos de porta Atmel-ICE AVR | Alfinetes alvo | Pino de minilula |

pinagem TPI |

| Pino 1 (TCK) | RELÓGIO | 1 | 3 |

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | DADOS | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 |

| Pino 6 (nSRST) | /REDEFINIR | 6 | 5 |

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | 9 | ||

| Pino 10 (GND) | 0 |

3.9 Conectando a um alvo SWD

A interface ARM SWD é um subconjunto do JTAG interface, fazendo uso dos pinos TCK e TMS, o que significa que ao conectar a um dispositivo SWD, o J de 10 pinosTAG conector pode ser tecnicamente usado. O ARM JTAG e AVR JTAG os conectores não são, no entanto, compatíveis com pinos, portanto, isso depende do layout da placa de destino em uso. Ao usar um STK600 ou uma placa fazendo uso do AVR JTAG pinagem, a porta do conector AVR no Atmel-ICE deve ser usada. Ao conectar a uma placa, que faz uso do ARM JTAG pinagem, a porta do conector SAM no Atmel-ICE deve ser usada.

A pinagem recomendada para o conector Cortex Debug de 10 pinos é mostrada na Figura 4-4.

Conexão a um cabeçalho Cortex de 10 pinos e 50 mil

Use o cabo plano (incluído em alguns kits) para conectar a um cabeçalho Cortex padrão de 50 mil.

Conexão a um cabeçalho Cortex-layout de 10 pinos e 100 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote de pinagem Cortex de 100 mil.

Conexão a um cabeçalho SAM de 20 pinos e 100 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um conector SAM de 20 pinos e 100 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR ou SAM e a placa de destino. Seis conexões são necessárias, conforme descrito na tabela abaixo.

Tabela 3-8. Atmel-ICE SWD Pin Mapeamento

| Nome | AVR pino da porta | SÃO pino da porta | Descrição |

| SWDC LK | 1 | 4 | Relógio de depuração de fio serial. |

| SWDIO | 5 | 2 | Entrada/saída de dados de depuração de fio serial. |

| OSSO | 3 | 6 | Saída de fio serial (opcional - não implementado em todos os dispositivos). |

| nSRST | 6 | 10 | Reiniciar. |

| VTG | 4 | 1 | Volume alvotage referência. |

| Terra | 2, 10 | 3, 5, 9 | Chão. |

3.10 Conectando à interface do gateway de dados

O Atmel-ICE oferece suporte a uma interface de gateway de dados (DGI) limitada quando a depuração e a programação não estão em uso. A funcionalidade é idêntica à encontrada nos kits Atmel Xplained Pro alimentados pelo dispositivo Atmel EDBG.

A Data Gateway Interface é uma interface para transmissão de dados do dispositivo de destino para um computador. Isso serve como uma ajuda na depuração do aplicativo, bem como para demonstração de recursos no aplicativo em execução no dispositivo de destino.

O DGI consiste em vários canais para streaming de dados. O Atmel-ICE suporta os seguintes modos:

- USART

- SPI

Tabela 3-9. Pinagem Atmel-ICE DGI USART

|

porta AVR |

porta SAM | Pino DGI USART |

Descrição |

| 3 | 6 | TX | Transmitir pin do Atmel-ICE para o dispositivo de destino |

| 4 | 1 | VTG | Volume alvotage (vol de referênciatage) |

| 8 | 7 | RX | Receber pin do dispositivo de destino para Atmel-ICE |

| 9 | 8 | CLK | Relógio USART |

| 2, 10 | 3, 5, 9 | Terra | Chão |

Tabela 3-10. Pinagem Atmel-ICE DGI SPI

|

porta AVR |

porta SAM | Pino DGI SPI |

Descrição |

| 1 | 4 | SCK | Relógio SPI |

| 3 | 6 | MISO | Mestre em Escravo |

| 4 | 1 | VTG | Volume alvotage (vol de referênciatage) |

| 5 | 2 | nCS | Chip select ativo baixo |

| 9 | 8 | MOSI | Mestre para fora, escravo para dentro |

| 2, 10 | 3, 5, 9 | Terra | Chão |

![]() Importante: As interfaces SPI e USART não podem ser usadas simultaneamente.

Importante: As interfaces SPI e USART não podem ser usadas simultaneamente.

![]() Importante: DGI e programação ou depuração não podem ser usados simultaneamente.

Importante: DGI e programação ou depuração não podem ser usados simultaneamente.

Depuração no chip

4.1 Introdução

Depuração no chip

Um módulo de depuração on-chip é um sistema que permite que um desenvolvedor monitore e controle a execução em um dispositivo de uma plataforma de desenvolvimento externa, geralmente por meio de um dispositivo conhecido como depurador ou adaptador de depuração.

Com um sistema OCD, o aplicativo pode ser executado mantendo as características elétricas e de temporização exatas no sistema de destino, podendo interromper a execução condicional ou manualmente e inspecionar o fluxo e a memória do programa.

Modo de execução

No modo Run, a execução do código é totalmente independente do Atmel-ICE. O Atmel-ICE monitorará continuamente o dispositivo de destino para ver se ocorreu uma condição de interrupção. Quando isso acontecer, o sistema OCD irá interrogar o dispositivo através de sua interface de depuração, permitindo que o usuário view o estado interno do dispositivo.

Modo Parado

Quando um ponto de interrupção é atingido, a execução do programa é interrompida, mas algumas E/S podem continuar a ser executadas como se nenhum ponto de interrupção tivesse ocorrido. por example, suponha que uma transmissão USART acaba de ser iniciada quando um ponto de interrupção é atingido. Neste caso, o USART continua a funcionar em velocidade máxima completando a transmissão, mesmo que o núcleo esteja no modo parado.

Pontos de Interrupção de Hardware

O módulo OCD de destino contém vários comparadores de contador de programa implementados no hardware. Quando o contador do programa coincide com o valor armazenado em um dos registradores do comparador, o OCD entra no modo parado. Como os pontos de interrupção de hardware requerem hardware dedicado no módulo OCD, o número de pontos de interrupção disponíveis depende do tamanho do módulo OCD implementado no destino. Normalmente, um desses comparadores de hardware é 'reservado' pelo depurador para uso interno.

Breakpoints de software

Um ponto de interrupção de software é uma instrução BREAK colocada na memória do programa no dispositivo de destino. Quando esta instrução é carregada, a execução do programa é interrompida e o OCD entra no modo parado. Para continuar a execução, um comando “iniciar” deve ser dado pelo OCD. Nem todos os dispositivos Atmel possuem módulos OCD que suportam a instrução BREAK.

4.2 Dispositivos SAM com JTAG/SWD

Todos os dispositivos SAM apresentam a interface SWD para programação e depuração. Além disso, alguns dispositivos SAM apresentam um JTAG interface com funcionalidade idêntica. Verifique a folha de dados do dispositivo para obter as interfaces suportadas desse dispositivo.

4.2.1. Componentes do ARM CoreSight

Os microcontroladores Atmel ARM Cortex-M implementam componentes OCD compatíveis com CoreSight. Os recursos desses componentes podem variar de dispositivo para dispositivo. Para obter mais informações, consulte a folha de dados do dispositivo, bem como a documentação do CoreSight fornecida pela ARM.

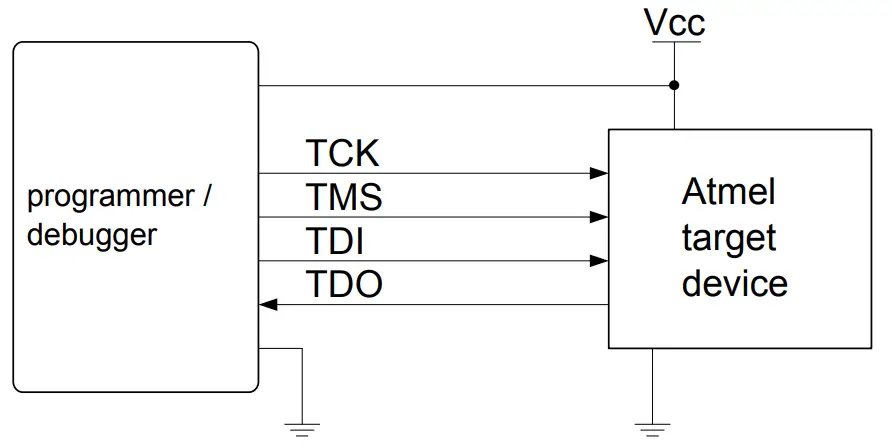

4.2.1. EuTAG Interface física

O JTAG A interface consiste em um controlador de porta de acesso de teste (TAP) de 4 fios compatível com o padrão IEEE® 1149.1 padrão. O padrão IEEE foi desenvolvido para fornecer uma maneira padrão da indústria de testar com eficiência a conectividade da placa de circuito (Boundary Scan). Os dispositivos Atmel AVR e SAM ampliaram essa funcionalidade para incluir suporte completo de programação e depuração no chip.

Figura 4-1. JTAG Interface Básica

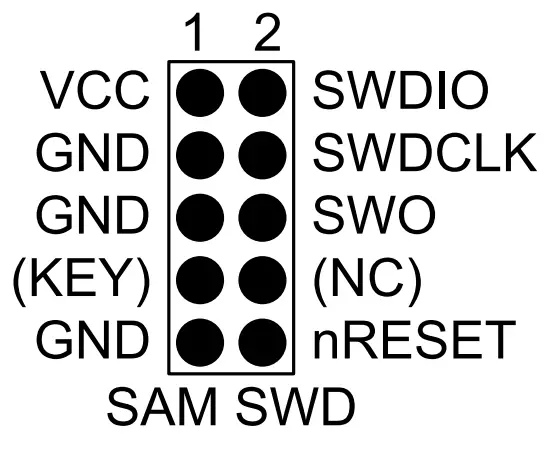

4.2.2.1 SAMJTAG Pinagem (conector de depuração Cortex-M)

Ao projetar um PCB de aplicativo que inclui um Atmel SAM com o JTAG interface, recomenda-se usar a pinagem conforme a figura abaixo. As variantes de 100 mil e 50 mil desta pinagem são suportadas, dependendo do cabeamento e dos adaptadores incluídos no kit específico.

Figura 4-2. SAMJTAG Pinagem do cabeçalho

Tabela 4-1. SAM JTAG Descrição do Pin

| Nome | Alfinete |

Descrição |

| TCK | 4 | Relógio de teste (sinal de relógio do Atmel-ICE para o dispositivo de destino). |

| EMT (Transmissão Transmissível) | 2 | Seleção do modo de teste (sinal de controle do Atmel-ICE para o dispositivo de destino). |

| TDI | 8 | Test Data In (dados transmitidos do Atmel-ICE para o dispositivo de destino). |

| TDO | 6 | Test Data Out (dados transmitidos do dispositivo de destino para o Atmel-ICE). |

| nRESET | 10 | Redefinir (opcional). Usado para redefinir o dispositivo de destino. A conexão desse pino é recomendada, pois permite que o Atmel-ICE mantenha o dispositivo de destino em um estado de redefinição, o que pode ser essencial para a depuração em determinados cenários. |

| VTG | 1 | Volume alvotage referência. O Atmel-ICE samples o alvo voltage neste pino para alimentar corretamente os conversores de nível. O Atmel-ICE consome menos de 1 mA deste pino neste modo. |

| Terra | 3, 5, 9 | Chão. Todos devem estar conectados para garantir que o Atmel-ICE e o dispositivo de destino compartilhem a mesma referência de aterramento. |

| CHAVE | 7 | Conectado internamente ao pino TRST no conector AVR. Recomendado como não conectado. |

![]() Dica: Lembre-se de incluir um capacitor de desacoplamento entre o pino 1 e o GND.

Dica: Lembre-se de incluir um capacitor de desacoplamento entre o pino 1 e o GND.

4.2.2.2 JTAG Margarida Encadeamento

O JTAG interface permite que vários dispositivos sejam conectados a uma única interface em uma configuração em cadeia. Os dispositivos de destino devem ser todos alimentados pelo mesmo volume de alimentaçãotage, compartilham um nó de terra comum, e devem ser conectados conforme a figura abaixo.

Figura 4-3. JTAG Cadeia de margaridas

Ao conectar dispositivos em cadeia, os seguintes pontos devem ser considerados:

- Todos os dispositivos devem compartilhar um aterramento comum, conectado ao GND na sonda Atmel-ICE

- Todos os dispositivos devem estar operando no mesmo vol alvotage. O VTG no Atmel-ICE deve ser conectado a este voltage.

- TMS e TCK são conectados em paralelo; TDI e TDO estão conectados em série

- nSRST na sonda Atmel-ICE deve ser conectado ao RESET nos dispositivos se algum dos dispositivos na cadeia desabilitar seu JTAG porta

- “Dispositivos antes” refere-se ao número de JTAG dispositivos pelos quais o sinal TDI tem que passar na cadeia antes de atingir o dispositivo de destino. Da mesma forma, “dispositivos após” é o número de dispositivos pelos quais o sinal deve passar após o dispositivo de destino antes de atingir o Atmel-ICE TDO

- “Bits de instrução “antes” e “depois” referem-se à soma total de todos os JTAG comprimentos de registro de instrução dos dispositivos, que são conectados antes e depois do dispositivo de destino na cadeia

- O comprimento total do IR (bits de instrução antes + comprimento do IR do dispositivo de destino Atmel + bits de instrução depois) é limitado a um máximo de 256 bits. O número de dispositivos na cadeia é limitado a 15 antes e 15 depois.

![]() Dica:

Dica:

encadeamento examparquivo: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Para se conectar ao Atmel AVR XMEGA® dispositivo, as configurações daisy chain são:

- Dispositivos antes: 1

- Dispositivos depois: 1

- Bits de instrução antes: 4 (dispositivos AVR de 8 bits têm 4 bits IR)

- Bits de instrução após: 5 (dispositivos AVR de 32 bits têm 5 bits IR)

Tabela 4-2. Comprimentos IR de Atmel MCUs

| Tipo de dispositivo | comprimento IR |

| AVR de 8 bits | 4 bits |

| AVR de 32 bits | 5 bits |

| SÃO | 4 bits |

4.2.3. Conectando a um JTAG Alvo

O Atmel-ICE é equipado com dois conectores J de 50 mil e 10 pinosTAG conectores. Ambos os conectores são diretamente conectados eletricamente, mas obedecem a duas pinagens diferentes; o AVR JTAG cabeçalho e o cabeçalho ARM Cortex Debug. O conector deve ser selecionado com base na pinagem da placa de destino e não no tipo de MCU de destino - por exemploampum dispositivo SAM montado em uma pilha AVR STK600 deve usar o cabeçalho AVR.

A pinagem recomendada para o AVR J de 10 pinosTAG conector é mostrado na Figura 4-6.

A pinagem recomendada para o conector ARM Cortex Debug de 10 pinos é mostrada na Figura 4-2.

Conexão direta a um cabeçote padrão de 10 pinos e 50 mil

Use o cabo plano de 50 pinos de 10 mil (incluído em alguns kits) para conectar diretamente a uma placa compatível com esse tipo de cabeçalho. Use a porta do conector AVR no Atmel-ICE para cabeçalhos com a pinagem AVR e a porta do conector SAM para cabeçalhos em conformidade com a pinagem de cabeçalho ARM Cortex Debug.

As pinagens para ambas as portas do conector de 10 pinos são mostradas abaixo.

Conexão a um cabeçote padrão de 10 pinos e 100 mil

Use um adaptador padrão de 50 mil para 100 mil para conectar a plataformas de 100 mil. Uma placa adaptadora (incluída em alguns kits) pode ser usada para essa finalidade ou, alternativamente, o JTAGO adaptador ICE3 pode ser usado para alvos AVR.

![]() Importante:

Importante:

O JTAGO adaptador ICE3 de 100 mil não pode ser usado com a porta do conector SAM, pois os pinos 2 e 10 (AVR GND) no adaptador estão conectados.

Conexão a um cabeçalho personalizado de 100 mil

Se sua placa de destino não tiver um conector J de 10 pinos compatívelTAG cabeçalho em 50 ou 100 mil, você pode mapear para uma pinagem personalizada usando o cabo “mini-squid” de 10 pinos (incluído em alguns kits), que dá acesso a dez soquetes individuais de 100 mil.

Conexão a um cabeçalho de 20 mil de 100 pinos

Use a placa adaptadora (incluída em alguns kits) para conectar alvos com um cabeçalho de 20 pinos e 100 mil.

Tabela 4-3. Atmel-ICE JTAG Descrição do Pin

| Nome | AVR pino da porta | SÃO pino da porta | Descrição |

| TCK | 1 | 4 | Relógio de teste (sinal de relógio do Atmel-ICE para o dispositivo de destino). |

| EMT (Transmissão Transmissível) | 5 | 2 | Seleção do modo de teste (sinal de controle do Atmel-ICE para o dispositivo de destino). |

| TDI | 9 | 8 | Test Data In (dados transmitidos do Atmel-ICE para o dispositivo de destino). |

| TDO | 3 | 6 | Test Data Out (dados transmitidos do dispositivo de destino para o Atmel-ICE). |

| nTRST | 8 | – | Reinicialização de teste (opcional, apenas em alguns dispositivos AVR). Usado para redefinir o JTAG controlador TAP. |

| nSRST | 6 | 10 | Redefinir (opcional). Usado para redefinir o dispositivo de destino. A conexão desse pino é recomendada, pois permite que o Atmel-ICE mantenha o dispositivo de destino em um estado de redefinição, o que pode ser essencial para a depuração em determinados cenários. |

| VTG | 4 | 1 | Volume alvotage referência. O Atmel-ICE samples o alvo voltage neste pino para alimentar corretamente os conversores de nível. O Atmel-ICE consome menos de 3 mA desse pino no modo debugWIRE e menos de 1 mA em outros modos. |

| Terra | 2, 10 | 3, 5, 9 | Chão. Todos devem estar conectados para garantir que o Atmel-ICE e o dispositivo de destino compartilhem a mesma referência de aterramento. |

4.2.4. SWD Interface Física

A interface ARM SWD é um subconjunto do JTAG interface, fazendo uso de pinos TCK e TMS. O ARM JTAG e AVR JTAG os conectores não são, no entanto, compatíveis com pinos; portanto, ao projetar um PCB de aplicativo, que usa um dispositivo SAM com SWD ou JTAG interface, recomenda-se usar a pinagem ARM mostrada na figura abaixo. A porta do conector SAM no Atmel-ICE pode se conectar diretamente a esta pinagem.

Figura 4-4. Recomendado ARM SWD/JTAG Pinagem do cabeçalho

O Atmel-ICE é capaz de transmitir rastreamento ITM no formato UART para o computador host. O rastreamento é capturado no pino TRACE/SWO do cabeçalho de 10 pinos (JTAG pino TDO). Os dados são armazenados em buffer internamente no Atmel-ICE e enviados pela interface HID para o computador host. A taxa de dados máxima confiável é de cerca de 3 MB/s.

4.2.5. Conectando a um alvo SWD

A interface ARM SWD é um subconjunto do JTAG interface, fazendo uso dos pinos TCK e TMS, o que significa que ao conectar a um dispositivo SWD, o J de 10 pinosTAG conector pode ser tecnicamente usado. O ARM JTAG e AVR JTAG os conectores não são, no entanto, compatíveis com pinos, portanto, isso depende do layout da placa de destino em uso. Ao usar um STK600 ou uma placa fazendo uso do AVR JTAG pinagem, a porta do conector AVR no Atmel-ICE deve ser usada. Ao conectar a uma placa, que faz uso do ARM JTAG pinagem, a porta do conector SAM no Atmel-ICE deve ser usada.

A pinagem recomendada para o conector Cortex Debug de 10 pinos é mostrada na Figura 4-4.

Conexão a um cabeçalho Cortex de 10 pinos e 50 mil

Use o cabo plano (incluído em alguns kits) para conectar a um cabeçalho Cortex padrão de 50 mil.

Conexão a um cabeçalho Cortex-layout de 10 pinos e 100 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote de pinagem Cortex de 100 mil.

Conexão a um cabeçalho SAM de 20 pinos e 100 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um conector SAM de 20 pinos e 100 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR ou SAM e a placa de destino. Seis conexões são necessárias, conforme descrito na tabela abaixo.

Tabela 4-4. Atmel-ICE SWD Pin Mapeamento

| Nome | AVR pino da porta | SÃO pino da porta | Descrição |

| SWDC LK | 1 | 4 | Relógio de depuração de fio serial. |

| SWDIO | 5 | 2 | Entrada/saída de dados de depuração de fio serial. |

| OSSO | 3 | 6 | Saída de fio serial (opcional - não implementado em todos os dispositivos). |

| nSRST | 6 | 10 | Reiniciar. |

| VTG | 4 | 1 | Volume alvotage referência. |

| Terra | 2, 10 | 3, 5, 9 | Chão. |

4.2.6 Considerações Especiais

APAGAR pino

Alguns dispositivos SAM incluem um pino ERASE que é ativado para executar um apagamento completo do chip e desbloquear dispositivos nos quais o bit de segurança está definido. Esse recurso é acoplado ao próprio dispositivo, bem como ao controlador de flash e não faz parte do núcleo ARM.

O pino ERASE NÃO faz parte de nenhum cabeçalho de depuração e, portanto, o Atmel-ICE não pode ativar esse sinal para desbloquear um dispositivo. Nesses casos, o usuário deve executar o apagamento manualmente antes de iniciar uma sessão de depuração.

Interfaces físicas JTAG interface

A linha RESET deve estar sempre conectada para que o Atmel-ICE possa habilitar o JTAG interface.

Interface SWD

A linha RESET deve estar sempre conectada para que o Atmel-ICE possa habilitar a interface SWD.

4.3 Dispositivos AVR UC3 com JTAG/um fio

Todos os dispositivos AVR UC3 apresentam o JTAG interface para programação e depuração. Além disso, alguns dispositivos AVR UC3 apresentam a interface aWire com funcionalidade idêntica usando um único fio. Verifique a folha de dados do dispositivo para obter as interfaces suportadas desse dispositivo

4.3.1 Sistema de depuração no chip Atmel AVR UC3

O sistema Atmel AVR UC3 OCD foi projetado de acordo com o padrão Nexus 2.0 (IEEE-ISTO 5001™-2003), que é um padrão de depuração em chip aberto altamente flexível e poderoso para microcontroladores de 32 bits. Ele suporta os seguintes recursos:

- Solução de depuração compatível com Nexus

- OCD suporta qualquer velocidade de CPU

- Seis pontos de interrupção de hardware do contador de programa

- Dois pontos de interrupção de dados

- Breakpoints podem ser configurados como watchpoints

- Os pontos de interrupção de hardware podem ser combinados para interromper os intervalos

- Número ilimitado de pontos de interrupção do programa do usuário (usando BREAK)

- Rastreamento de desvio de contador de programa em tempo real, rastreamento de dados, rastreamento de processo (suportado apenas por depuradores com porta de captura de rastreamento paralela)

Para obter mais informações sobre o sistema AVR UC3 OCD, consulte os Manuais de Referência Técnica AVR32UC, localizados em www.atmel.com/uc3.

4.3.2. EuTAG Interface física

O JTAG A interface consiste em um controlador de porta de acesso de teste (TAP) de 4 fios compatível com o padrão IEEE® 1149.1 padrão. O padrão IEEE foi desenvolvido para fornecer uma maneira padrão da indústria de testar com eficiência a conectividade da placa de circuito (Boundary Scan). Os dispositivos Atmel AVR e SAM ampliaram essa funcionalidade para incluir suporte completo de programação e depuração no chip.

Figura 4-5. JTAG Interface Básica

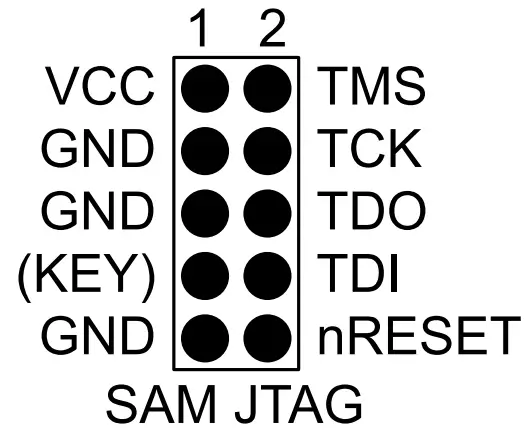

4.3.2.1 AVR JTAG Pinagem

Ao projetar um PCB de aplicação, que inclui um Atmel AVR com o JTAG interface, recomenda-se usar a pinagem conforme a figura abaixo. As variantes de 100 mil e 50 mil desta pinagem são suportadas, dependendo do cabeamento e dos adaptadores incluídos no kit específico.

Figura 4-6. AVR JTAG Pinagem do cabeçalho

Mesa 4-5. AVR JTAG Descrição do Pin

| Nome | Alfinete |

Descrição |

| TCK | 1 | Relógio de teste (sinal de relógio do Atmel-ICE para o dispositivo de destino). |

| EMT (Transmissão Transmissível) | 5 | Seleção do modo de teste (sinal de controle do Atmel-ICE para o dispositivo de destino). |

| TDI | 9 | Test Data In (dados transmitidos do Atmel-ICE para o dispositivo de destino). |

| TDO | 3 | Test Data Out (dados transmitidos do dispositivo de destino para o Atmel-ICE). |

| nTRST | 8 | Reinicialização de teste (opcional, apenas em alguns dispositivos AVR). Usado para redefinir o JTAG controlador TAP. |

| nSRST | 6 | Redefinir (opcional). Usado para redefinir o dispositivo de destino. A conexão desse pino é recomendada, pois permite que o Atmel-ICE mantenha o dispositivo de destino em um estado de redefinição, o que pode ser essencial para a depuração em determinados cenários. |

| VTG | 4 | Volume alvotage referência. O Atmel-ICE samples o alvo voltage neste pino para alimentar corretamente os conversores de nível. O Atmel-ICE consome menos de 3 mA desse pino no modo debugWIRE e menos de 1 mA em outros modos. |

| Terra | 2, 10 | Chão. Ambos devem estar conectados para garantir que o Atmel-ICE e o dispositivo de destino compartilhem a mesma referência de aterramento. |

![]() Dica: Lembre-se de incluir um capacitor de desacoplamento entre o pino 4 e o GND.

Dica: Lembre-se de incluir um capacitor de desacoplamento entre o pino 4 e o GND.

4.3.2.2 JTAG Margarida Encadeamento

O JTAG interface permite que vários dispositivos sejam conectados a uma única interface em uma configuração em cadeia. Os dispositivos de destino devem ser todos alimentados pelo mesmo volume de alimentaçãotage, compartilham um nó de terra comum, e devem ser conectados conforme a figura abaixo.

Figura 4-7. JTAG Cadeia de margaridas

Ao conectar dispositivos em cadeia, os seguintes pontos devem ser considerados:

- Todos os dispositivos devem compartilhar um aterramento comum, conectado ao GND na sonda Atmel-ICE

- Todos os dispositivos devem estar operando no mesmo vol alvotage. O VTG no Atmel-ICE deve ser conectado a este voltage.

- TMS e TCK são conectados em paralelo; TDI e TDO estão conectados em uma cadeia serial.

- nSRST na sonda Atmel-ICE deve ser conectado ao RESET nos dispositivos se algum dos dispositivos na cadeia desabilitar seu JTAG porta

- “Dispositivos antes” refere-se ao número de JTAG dispositivos pelos quais o sinal TDI tem que passar na cadeia antes de atingir o dispositivo de destino. Da mesma forma, “dispositivos após” é o número de dispositivos pelos quais o sinal deve passar após o dispositivo de destino antes de atingir o Atmel-ICE TDO

- “Bits de instrução “antes” e “depois” referem-se à soma total de todos os JTAG comprimentos de registro de instrução dos dispositivos, que são conectados antes e depois do dispositivo de destino na cadeia

- O comprimento total do IR (bits de instrução antes + comprimento do IR do dispositivo de destino Atmel + bits de instrução depois) é limitado a um máximo de 256 bits. O número de dispositivos na cadeia é limitado a 15 antes e 15 depois.

Dica:

encadeamento examparquivo: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Para se conectar ao Atmel AVR XMEGA® dispositivo, as configurações daisy chain são:

- Dispositivos antes: 1

- Dispositivos depois: 1

- Bits de instrução antes: 4 (dispositivos AVR de 8 bits têm 4 bits IR)

- Bits de instrução após: 5 (dispositivos AVR de 32 bits têm 5 bits IR)

Tabela 4-6. Comprimentos IV do Atmel MCUS

| Tipo de dispositivo | comprimento IR |

| AVR de 8 bits | 4 bits |

| AVR de 32 bits | 5 bits |

| SÃO | 4 bits |

4.3.3. Conectando a um JTAG Alvo

O Atmel-ICE é equipado com dois conectores J de 50 mil e 10 pinosTAG conectores. Ambos os conectores são diretamente conectados eletricamente, mas obedecem a duas pinagens diferentes; o AVR JTAG cabeçalho e o cabeçalho ARM Cortex Debug. O conector deve ser selecionado com base na pinagem da placa de destino e não no tipo de MCU de destino - por exemploampum dispositivo SAM montado em uma pilha AVR STK600 deve usar o cabeçalho AVR.

A pinagem recomendada para o AVR J de 10 pinosTAG conector é mostrado na Figura 4-6.

A pinagem recomendada para o conector ARM Cortex Debug de 10 pinos é mostrada na Figura 4-2.

Conexão direta a um cabeçote padrão de 10 pinos e 50 mil

Use o cabo plano de 50 pinos de 10 mil (incluído em alguns kits) para conectar diretamente a uma placa compatível com esse tipo de cabeçalho. Use a porta do conector AVR no Atmel-ICE para cabeçalhos com a pinagem AVR e a porta do conector SAM para cabeçalhos em conformidade com a pinagem de cabeçalho ARM Cortex Debug.

As pinagens para ambas as portas do conector de 10 pinos são mostradas abaixo.

Conexão a um cabeçote padrão de 10 pinos e 100 mil

Use um adaptador padrão de 50 mil para 100 mil para conectar a plataformas de 100 mil. Uma placa adaptadora (incluída em alguns kits) pode ser usada para essa finalidade ou, alternativamente, o JTAGO adaptador ICE3 pode ser usado para alvos AVR.

![]() Importante:

Importante:

O JTAGO adaptador ICE3 de 100 mil não pode ser usado com a porta do conector SAM, pois os pinos 2 e 10 (AVR GND) no adaptador estão conectados.

Conexão a um cabeçalho personalizado de 100 mil

Se sua placa de destino não tiver um conector J de 10 pinos compatívelTAG cabeçalho em 50 ou 100 mil, você pode mapear para uma pinagem personalizada usando o cabo “mini-squid” de 10 pinos (incluído em alguns kits), que dá acesso a dez soquetes individuais de 100 mil.

Conexão a um cabeçalho de 20 mil de 100 pinos

Use a placa adaptadora (incluída em alguns kits) para conectar alvos com um cabeçalho de 20 pinos e 100 mil.

Tabela 4-7. Atmel-ICE JTAG Descrição do Pin

|

Nome |

Pino da porta AVR | pino da porta SAM |

Descrição |

| TCK | 1 | 4 | Relógio de teste (sinal de relógio do Atmel-ICE para o dispositivo de destino). |

| EMT (Transmissão Transmissível) | 5 | 2 | Seleção do modo de teste (sinal de controle do Atmel-ICE para o dispositivo de destino). |

| TDI | 9 | 8 | Test Data In (dados transmitidos do Atmel-ICE para o dispositivo de destino). |

| TDO | 3 | 6 | Test Data Out (dados transmitidos do dispositivo de destino para o Atmel-ICE). |

| nTRST | 8 | – | Reinicialização de teste (opcional, apenas em alguns dispositivos AVR). Usado para redefinir o JTAG controlador TAP. |

| nSRST | 6 | 10 | Redefinir (opcional). Usado para redefinir o dispositivo de destino. A conexão desse pino é recomendada, pois permite que o Atmel-ICE mantenha o dispositivo de destino em um estado de redefinição, o que pode ser essencial para a depuração em determinados cenários. |

| VTG | 4 | 1 | Volume alvotage referência. O Atmel-ICE samples o alvo voltage neste pino para alimentar corretamente os conversores de nível. O Atmel-ICE consome menos de 3 mA desse pino no modo debugWIRE e menos de 1 mA em outros modos. |

| Terra | 2, 10 | 3, 5, 9 | Chão. Todos devem estar conectados para garantir que o Atmel-ICE e o dispositivo de destino compartilhem a mesma referência de aterramento. |

4.3.4 Interface Física aWire

A interface aWire faz uso do fio RESET do dispositivo AVR para permitir funções de programação e depuração. Uma sequência de ativação especial é transmitida pelo Atmel-ICE, que desativa a funcionalidade RESET padrão do pino. Ao projetar um PCB de aplicativo, que inclui um Atmel AVR com a interface aWire, é recomendável usar a pinagem conforme mostrado na Figura 4 -8. As variantes de 100 mil e 50 mil desta pinagem são suportadas, dependendo do cabeamento e dos adaptadores incluídos no kit específico.

Figura 4-8. pinagem do cabeçalho aWire

![]() Dica:

Dica:

Uma vez que aWire é uma interface half-duplex, um resistor pull-up na linha RESET na ordem de 47kΩ é recomendado para evitar detecção de bit de início falso ao mudar de direção.

A interface aWire pode ser usada como interface de programação e depuração. Todos os recursos do sistema OCD disponíveis através do J de 10 pinosTAG interface também pode ser acessada usando aWire.

4.3.5 Conectando a um alvo aWire

A interface aWire requer apenas uma linha de dados além de VCC e GND. No alvo, esta linha é a linha nRESET, embora o depurador use o JTAG Linha TDO como a linha de dados.

A pinagem recomendada para o conector aWire de 6 pinos é mostrada na Figura 4-8.

Conexão a um conector aWire de 6 pinos e 100 mil

Use a derivação de 6 pinos de 100 mil no cabo plano (incluído em alguns kits) para conectar a um cabeçote aWire padrão de 100 mil.

Conexão a um conector aWire de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote aWire padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. São necessárias três conexões, conforme descrito na tabela abaixo.

Tabela 4-8. Mapeamento de pinos Atmel-ICE aWire

| Pinos de porta Atmel-ICE AVR | Alfinetes alvo | Pino de minilula |

pinagem aWire |

| Pino 1 (TCK) | 1 | ||

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | DADOS | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 | ||

| Pino 6 (nSRST) | 6 | ||

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | 9 | ||

| Pino 10 (GND) | 0 |

4.3.6. Considerações especiais

JTAG interface

Em alguns dispositivos Atmel AVR UC3, o JTAG A porta não está habilitada por padrão. Ao usar esses dispositivos é essencial conectar a linha RESET para que o Atmel-ICE possa habilitar o JTAG interface.

interface aWire

A taxa de transmissão das comunicações aWire depende da frequência do relógio do sistema, pois os dados devem ser sincronizados entre esses dois domínios. O Atmel-ICE detectará automaticamente que o relógio do sistema foi reduzido e recalibrará sua taxa de transmissão de acordo. A calibração automática só funciona até uma frequência de relógio do sistema de 8 kHz. Mudar para um relógio de sistema mais baixo durante uma sessão de depuração pode fazer com que o contato com o alvo seja perdido.

Se necessário, a taxa de transmissão aWire pode ser restringida configurando o parâmetro aWire clock. A detecção automática ainda funcionará, mas um valor máximo será imposto aos resultados.

Qualquer capacitor estabilizador conectado ao pino RESET deve ser desconectado ao usar aWire, pois irá interferir na operação correta da interface. Recomenda-se um pullup externo fraco (10kΩ ou superior) nesta linha.

Desligar o modo de suspensão

Alguns dispositivos AVR UC3 possuem um regulador interno que pode ser usado no modo de alimentação de 3.3 V com linhas de E/S reguladas de 1.8 V. Isso significa que o regulador interno alimenta o núcleo e a maior parte das E/S. Somente Atmel AVR UM! o depurador oferece suporte à depuração durante o uso de modos de suspensão em que este regulador está desligado.

4.3.7. Uso de EVTI/EVTO

Os pinos EVTI e EVTO não são acessíveis no Atmel-ICE. No entanto, eles ainda podem ser usados em conjunto com outros equipamentos externos.

O EVTI pode ser usado para os seguintes propósitos:

- O destino pode ser forçado a interromper a execução em resposta a um evento externo. Se os bits Event In Control (EIC) no registro DC forem gravados em 0b01, a transição de alto para baixo no pino EVTI gerará uma condição de ponto de interrupção. O EVTI deve permanecer baixo por um ciclo de clock da CPU para garantir que um ponto de interrupção seja O bit de ponto de interrupção externo (EXB) no DS é definido quando isso ocorre.

- Gerando mensagens de sincronização de rastreamento. Não usado pelo Atmel-ICE.

O EVTO pode ser usado para os seguintes fins:

- Indicando que a CPU entrou na depuração Definir os bits EOS em DC para 0b01 faz com que o pino EVTO seja puxado para baixo por um ciclo de clock da CPU quando o dispositivo de destino entra no modo de depuração. Este sinal pode ser usado como uma fonte de disparo para um osciloscópio externo.

- Indicando que a CPU atingiu um ponto de interrupção ou ponto de controle. Ao definir o bit EOC em um registro de controle de ponto de interrupção/ponto de controle correspondente, o status do ponto de interrupção ou ponto de controle é indicado no pino EVTO. Os bits EOS em DC devem ser definidos como 0xb10 para habilitar esse recurso. O pino EVTO pode então ser conectado a um osciloscópio externo para examinar o ponto de controle

- Gerando sinais de temporização de rastreamento. Não usado pelo Atmel-ICE.

4.4 dispositivos tinyAVR, megaAVR e XMEGA

Os dispositivos AVR apresentam várias interfaces de programação e depuração. Verifique a folha de dados do dispositivo para obter as interfaces suportadas desse dispositivo.

- Alguns minúsculos AVR® os dispositivos têm um TPI O TPI pode ser usado apenas para programar o dispositivo e esses dispositivos não têm capacidade de depuração no chip.

- Alguns dispositivos tinyAVR e alguns dispositivos megaAVR têm a interface debugWIRE, que se conecta a um sistema de depuração no chip conhecido como tinyOCD. Todos os dispositivos com debugWIRE também possuem a interface SPI para

- Alguns dispositivos megaAVR têm um JTAG interface para programação e depuração, com um sistema de depuração on-chip também conhecido como All devices with JTAG também apresentam a interface SPI como uma interface alternativa para programação no sistema.

- Todos os dispositivos AVR XMEGA possuem a interface PDI para programação e alguns dispositivos AVR XMEGA também possuem um JTAG interface com funcionalidade idêntica.

- Os novos dispositivos tinyAVR possuem uma interface UPDI, que é usada para programação e depuração

Tabela 4-9. Resumo de interfaces de programação e depuração

|

|

UPDI | ITP | SPI | depurar WIR E | JTAG | PDI | um fio |

SWD |

| minúsculoAVR | Novos dispositivos | Alguns dispositivos | Alguns dispositivos | Alguns dispositivos | ||||

| megaAV R | Todos os dispositivos | Alguns dispositivos | Alguns dispositivos | |||||

| AVR XMEGA | Alguns dispositivos | Todos os dispositivos | ||||||

| AVR UC | Todos os dispositivos | Alguns dispositivos | ||||||

| SÃO | Alguns dispositivos | Todos os dispositivos |

4.4.1. EuTAG Interface física

O JTAG A interface consiste em um controlador de porta de acesso de teste (TAP) de 4 fios compatível com o padrão IEEE® 1149.1 padrão. O padrão IEEE foi desenvolvido para fornecer uma maneira padrão da indústria de testar com eficiência a conectividade da placa de circuito (Boundary Scan). Os dispositivos Atmel AVR e SAM ampliaram essa funcionalidade para incluir suporte completo de programação e depuração no chip.

Figura 4-9. JTAG Interface Básica 4.4.2. Conectando a um JTAG Alvo

4.4.2. Conectando a um JTAG Alvo

O Atmel-ICE é equipado com dois conectores J de 50 mil e 10 pinosTAG conectores. Ambos os conectores são diretamente conectados eletricamente, mas obedecem a duas pinagens diferentes; o AVR JTAG cabeçalho e o cabeçalho ARM Cortex Debug. O conector deve ser selecionado com base na pinagem da placa de destino e não no tipo de MCU de destino - por exemploampum dispositivo SAM montado em uma pilha AVR STK600 deve usar o cabeçalho AVR.

A pinagem recomendada para o AVR J de 10 pinosTAG conector é mostrado na Figura 4-6.

A pinagem recomendada para o conector ARM Cortex Debug de 10 pinos é mostrada na Figura 4-2.

Conexão direta a um cabeçote padrão de 10 pinos e 50 mil

Use o cabo plano de 50 pinos de 10 mil (incluído em alguns kits) para conectar diretamente a uma placa compatível com esse tipo de cabeçalho. Use a porta do conector AVR no Atmel-ICE para cabeçalhos com a pinagem AVR e a porta do conector SAM para cabeçalhos em conformidade com a pinagem de cabeçalho ARM Cortex Debug.

As pinagens para ambas as portas do conector de 10 pinos são mostradas abaixo.

Conexão a um cabeçote padrão de 10 pinos e 100 mil

Use um adaptador padrão de 50 mil para 100 mil para conectar a plataformas de 100 mil. Uma placa adaptadora (incluída em alguns kits) pode ser usada para essa finalidade ou, alternativamente, o JTAGO adaptador ICE3 pode ser usado para alvos AVR.

![]() Importante:

Importante:

O JTAGO adaptador ICE3 de 100 mil não pode ser usado com a porta do conector SAM, pois os pinos 2 e 10 (AVR GND) no adaptador estão conectados.

Conexão a um cabeçalho personalizado de 100 mil

Se sua placa de destino não tiver um conector J de 10 pinos compatívelTAG cabeçalho em 50 ou 100 mil, você pode mapear para uma pinagem personalizada usando o cabo “mini-squid” de 10 pinos (incluído em alguns kits), que dá acesso a dez soquetes individuais de 100 mil.

Conexão a um cabeçalho de 20 mil de 100 pinos

Use a placa adaptadora (incluída em alguns kits) para conectar alvos com um cabeçalho de 20 pinos e 100 mil.

Tabela 4-10. Atmel-ICE JTAG Descrição do Pin

| Nome | AVR pino da porta | SÃO pino da porta | Descrição |

| TCK | 1 | 4 | Relógio de teste (sinal de relógio do Atmel-ICE para o dispositivo de destino). |

| EMT (Transmissão Transmissível) | 5 | 2 | Seleção do modo de teste (sinal de controle do Atmel-ICE para o dispositivo de destino). |

| TDI | 9 | 8 | Test Data In (dados transmitidos do Atmel-ICE para o dispositivo de destino). |

| TDO | 3 | 6 | Test Data Out (dados transmitidos do dispositivo de destino para o Atmel-ICE). |

| nTRST | 8 | – | Reinicialização de teste (opcional, apenas em alguns dispositivos AVR). Usado para redefinir o JTAG controlador TAP. |

| nSRST | 6 | 10 | Redefinir (opcional). Usado para redefinir o dispositivo de destino. A conexão desse pino é recomendada, pois permite que o Atmel-ICE mantenha o dispositivo de destino em um estado de redefinição, o que pode ser essencial para a depuração em determinados cenários. |

| VTG | 4 | 1 | Volume alvotage referência. O Atmel-ICE samples o alvo voltage neste pino para alimentar corretamente os conversores de nível. O Atmel-ICE consome menos de 3 mA desse pino no modo debugWIRE e menos de 1 mA em outros modos. |

| Terra | 2, 10 | 3, 5, 9 | Chão. Todos devem estar conectados para garantir que o Atmel-ICE e o dispositivo de destino compartilhem a mesma referência de aterramento. |

4.4.3. Interface Física SPI

A Programação no Sistema usa a SPI (Serial Peripheral Interface) interna do Atmel AVR de destino para fazer o download do código nas memórias flash e EEPROM. Não é uma interface de depuração. Ao projetar um PCB de aplicação, que inclui um AVR com a interface SPI, a pinagem mostrada na figura abaixo deve ser usada.

Figura 4-10. Pinagem do Cabeçalho SPI 4.4.4. Conectando-se a um alvo SPI

4.4.4. Conectando-se a um alvo SPI

A pinagem recomendada para o conector SPI de 6 pinos é mostrada na Figura 4-10.

Conexão a um cabeçalho SPI de 6 pinos e 100 mil

Use a derivação de 6 pinos de 100 mil no cabo plano (incluído em alguns kits) para conectar a um conector SPI padrão de 100 mil.

Conexão a um cabeçalho SPI de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote SPI padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. Seis conexões são necessárias, conforme descrito na tabela abaixo.

![]() Importante:

Importante:

A interface SPI é efetivamente desabilitada quando o fusível habilitado debugWIRE (DWEN) é programado, mesmo que o fusível SPIEN também esteja programado. Para reativar a interface SPI, o comando 'disable debugWIRE' deve ser emitido durante uma sessão de depuração debugWIRE. Desativar o debugWIRE dessa maneira requer que o fusível SPIEN já esteja programado. Se o Atmel Studio não desativar o debugWIRE, é provável que o fusível SPIEN NÃO esteja programado. Se este for o caso, é necessário usar um alto-voltagInterface de programação para programar o fusível SPIEN.

![]() Informações:

Informações:

A interface SPI costuma ser chamada de “ISP”, pois foi a primeira interface de programação do sistema nos produtos Atmel AVR. Outras interfaces estão agora disponíveis para programação no sistema.

Tabela 4-11. Mapeamento de pinos Atmel-ICE SPI

| Pinos de porta Atmel-ICE AVR | Alfinetes alvo | Pino de minilula |

Pinagem SPI |

| Pino 1 (TCK) | SCK | 1 | 3 |

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | MISO | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 | ||

| Pino 6 (nSRST) | /REDEFINIR | 6 | 5 |

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | MOSI | 9 | 4 |

| Pino 10 (GND) | 0 |

4.4.5. PDI

A Interface de Programação e Depuração (PDI) é uma interface proprietária da Atmel para programação externa e depuração no chip de um dispositivo. PDI Physical é uma interface de 2 pinos que fornece uma comunicação síncrona bidirecional half-duplex com o dispositivo de destino.

Ao projetar um PCB de aplicação, que inclui um Atmel AVR com a interface PDI, a pinagem mostrada na figura abaixo deve ser usada. Um dos adaptadores de 6 pinos fornecidos com o kit Atmel-ICE pode então ser usado para conectar a sonda Atmel-ICE ao PCB do aplicativo.

Figura 4-11. Pinagem do Cabeçalho PDI 4.4.6. Conectando a um Alvo PDI

4.4.6. Conectando a um Alvo PDI

A pinagem recomendada para o conector PDI de 6 pinos é mostrada na Figura 4-11.

Conexão a um cabeçalho PDI de 6 pinos e 100 mil

Use a derivação de 6 milésimos de 100 pinos no cabo plano (incluído em alguns kits) para conectar a um cabeçote PDI padrão de 100 mil.

Conexão a um cabeçalho PDI de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote PDI padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. Quatro conexões são necessárias, conforme descrito na tabela abaixo.

![]() Importante:

Importante:

A pinagem necessária é diferente do JTAGICE mkII JTAG sonda, onde PDI_DATA está conectado ao pino 9. O Atmel-ICE é compatível com a pinagem usada pelo Atmel-ICE, JTAGICE3, AVR ONE! e AVR Dragon™ produtos.

Tabela 4-12. Mapeamento de pinos Atmel-ICE PDI

|

Pino da porta Atmel-ICE AVR |

Alfinetes alvo | Pino de minilula |

Pinagem Atmel STK600 PDI |

| Pino 1 (TCK) | 1 | ||

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | PDI_DADOS | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 | ||

| Pino 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | 9 | ||

| Pino 10 (GND) | 0 |

4.4.7. Interface Física UPDI

O Unified Program and Debug Interface (UPDI) é uma interface proprietária da Atmel para programação externa e depuração no chip de um dispositivo. É o sucessor da interface física PDI de 2 fios, encontrada em todos os dispositivos AVR XMEGA. UPDI é uma interface de fio único que fornece uma comunicação assíncrona bidirecional half-duplex com o dispositivo de destino para fins de programação e depuração.

Ao projetar um PCB de aplicação, que inclui um Atmel AVR com a interface UPDI, a pinagem mostrada abaixo deve ser usada. Um dos adaptadores de 6 pinos fornecidos com o kit Atmel-ICE pode então ser usado para conectar a sonda Atmel-ICE ao PCB do aplicativo.

Figura 4-12. Pinagem do cabeçalho UPDI 4.4.7.1 UPDI e /RESET

4.4.7.1 UPDI e /RESET

A interface de um fio UPDI pode ser um pino dedicado ou um pino compartilhado, dependendo do dispositivo AVR de destino. Consulte a folha de dados do dispositivo para obter mais informações.

Quando a interface UPDI está em um pino compartilhado, o pino pode ser configurado para ser UPDI, /RESET ou GPIO configurando os fusíveis RSTPINCFG[1:0].

Os fusíveis RSTPINCFG[1:0] possuem as seguintes configurações, conforme descrito no datasheet. As implicações práticas de cada escolha são dadas aqui.

Tabela 4-13. RSTPINCFG[1:0] Configuração do fusível

| RSTPINCFG[1:0] | Configuração |

Uso |

| 00 | GPIO | Pino de E/S de uso geral. Para acessar UPDI, um pulso de 12V deve ser aplicado a este pino. Nenhuma fonte de reinicialização externa está disponível. |

| 01 | UPDI | Programação dedicada e pino de depuração. Nenhuma fonte de reinicialização externa está disponível. |

| 10 | Reiniciar | Reiniciar a entrada do sinal. Para acessar UPDI, um pulso de 12V deve ser aplicado a este pino. |

| 11 | Reservado | NA |

Observação: Dispositivos AVR mais antigos possuem uma interface de programação, conhecida como “High-Voltage Programming” (existem variantes serial e paralela.) Em geral, esta interface requer 12 V para ser aplicada ao pino /RESET durante a sessão de programação. A interface UPDI é uma interface totalmente diferente. O pino UPDI é principalmente um pino de programação e depuração, que pode ser fundido para ter uma função alternativa (/RESET ou GPIO). Se a função alternativa for selecionada, um pulso de 12 V será necessário nesse pino para reativar a funcionalidade UPDI.

Observação: Se um projeto exigir o compartilhamento do sinal UPDI devido a restrições de pinos, devem ser tomadas medidas para garantir que o dispositivo possa ser programado. Para garantir que o sinal UPDI funcione corretamente, bem como para evitar danos aos componentes externos do pulso de 12V, é recomendável desconectar todos os componentes neste pino ao tentar depurar ou programar o dispositivo. Isso pode ser feito usando um resistor de 0Ω, que é montado por padrão e removido ou substituído por um cabeçote de pino durante a depuração. Esta configuração significa efetivamente que a programação deve ser feita antes de montar o dispositivo.

![]() Importante: O Atmel-ICE não suporta 12V na linha UPDI. Em outras palavras, se o pino UPDI tiver sido configurado como GPIO ou RESET, o Atmel-ICE não poderá habilitar a interface UPDI.

Importante: O Atmel-ICE não suporta 12V na linha UPDI. Em outras palavras, se o pino UPDI tiver sido configurado como GPIO ou RESET, o Atmel-ICE não poderá habilitar a interface UPDI.

4.4.8. Conectando-se a um alvo UPDI

A pinagem recomendada para o conector UPDI de 6 pinos é mostrada na Figura 4-12.

Conexão a um cabeçalho UPDI de 6 pinos e 100 mil

Use a derivação de 6 pinos de 100 mil no cabo plano (incluído em alguns kits) para conectar a um cabeçote UPDI padrão de 100 mil.

Conexão a um cabeçalho UPDI de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote UPDI padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. São necessárias três conexões, conforme descrito na tabela abaixo.

Tabela 4-14. Mapeamento de pinos Atmel-ICE UPDI

| Pino da porta Atmel-ICE AVR | Alfinetes alvo | Pino de minilula |

Pinagem Atmel STK600 UPDI |

| Pino 1 (TCK) | 1 | ||

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 | ||

| Pino 6 (nSRST) | [/sentido REINICIALIZAR] | 6 | 5 |

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | 9 | ||

| Pino 10 (GND) | 0 |

4.4.9 Interface Física TPI

TPI é uma interface somente de programação para alguns dispositivos AVR ATtiny. Não é uma interface de depuração e esses dispositivos não possuem capacidade de OCD. Ao projetar um PCB de aplicação que inclua um AVR com a interface TPI, a pinagem mostrada na figura abaixo deve ser usada.

Figura 4-13. Pinagem do Cabeçalho TPI 4.4.10. Conectando a um alvo TPI

4.4.10. Conectando a um alvo TPI

A pinagem recomendada para o conector TPI de 6 pinos é mostrada na Figura 4-13.

Conexão a um cabeçalho TPI de 6 pinos e 100 mil

Use a derivação de 6 milésimos de 100 pinos no cabo plano (incluído em alguns kits) para conectar a um cabeçote TPI padrão de 100 mil.

Conexão a um cabeçalho TPI de 6 pinos e 50 mil

Use a placa adaptadora (incluída em alguns kits) para conectar a um cabeçote TPI padrão de 50 mil.

Conexão a um cabeçalho personalizado de 100 mil

O cabo mini-squid de 10 pinos deve ser usado para conectar entre a porta do conector Atmel-ICE AVR e a placa de destino. Seis conexões são necessárias, conforme descrito na tabela abaixo.

Tabela 4-15. Mapeamento de pinos TPI Atmel-ICE

| Pinos de porta Atmel-ICE AVR | Alfinetes alvo | Pino de minilula |

pinagem TPI |

| Pino 1 (TCK) | RELÓGIO | 1 | 3 |

| Pino 2 (GND) | Terra | 2 | 6 |

| Pino 3 (TDO) | DADOS | 3 | 1 |

| Pino 4 (VTG) | VTG | 4 | 2 |

| Pino 5 (TMS) | 5 | ||

| Pino 6 (nSRST) | /REDEFINIR | 6 | 5 |

| Pino 7 (não conectado) | 7 | ||

| Pino 8 (nTRST) | 8 | ||

| Pino 9 (TDI) | 9 | ||

| Pino 10 (GND) | 0 |

4.4.11. Depuração Avançada (AVR JTAG /dispositivos debugWIRE)

Periféricos de E/S

A maioria dos periféricos de E/S continuará a funcionar mesmo que a execução do programa seja interrompida por um ponto de interrupção. Example: Se um ponto de interrupção for atingido durante uma transmissão UART, a transmissão será concluída e os bits correspondentes definidos. O sinalizador TXC (transmissão completa) será definido e estará disponível na próxima etapa única do código, embora normalmente aconteça mais tarde em um dispositivo real.

Todos os módulos de E/S continuarão a funcionar no modo parado com as duas exceções a seguir:

- Temporizador/Contadores (configuráveis usando o front-end do software)

- Watchdog Timer (sempre parado para evitar reinicializações durante a depuração)

Acesso de E/S de passo único

Como a E/S continua a funcionar no modo parado, deve-se tomar cuidado para evitar certos problemas de temporização. por example, o código: