Programistoj de ICE Senĉirmiloj

Programistoj de ICE Senĉirmiloj

Uzantgvidilo Programistoj kaj Sencimigiloj

Programistoj kaj Sencimigiloj

Atmel-ICE

GVIDILO DE UZANTO

La Atmel-ICE Erarserĉilo

Atmel-ICE estas potenca disvolva ilo por sencimigi kaj programi ARM® Cortex®-M bazitajn sur Atmel ®SAM kaj Atmel AVR mikroregiloj kun ® On-Chip Debug-kapablo.

Ĝi subtenas:

- Programado kaj sur-blata senararigado de ĉiuj Atmel AVR 32-bitaj mikroregiloj sur ambaŭ JTAG kaj aWire-interfacoj

- Programado kaj sur-blata senararigado de ĉiuj Atmel AVR XMEGA®-familiaj aparatoj sur ambaŭ JTAG kaj PDI-2-drataj interfacoj

- Programado (JTAG, SPI, UPDI) kaj senararigado de ĉiuj Atmel AVR 8-bitaj mikroregiloj kun OCD-subteno sur ambaŭ JTAG, debugWIRE aŭ UPDI-interfacoj

- Programado kaj senararigado de ĉiuj mikroregiloj bazitaj sur Atmel SAM ARM Cortex-M sur kaj SWD kaj JTAG interfacoj

- Programado (TPI) de ĉiuj Atmel tinyAVR® 8-bitaj mikroregiloj kun subteno por ĉi tiu interfaco

Konsultu la liston de subtenataj aparatoj en la Uzantgvidilo de Atmel Studio por kompleta listo de aparatoj kaj interfacoj subtenataj de ĉi tiu firmware-eldono.

Enkonduko

1.1. Enkonduko al la Atmel-ICE

Atmel-ICE estas potenca disvolva ilo por senararigado kaj programado de mikroregiloj Atmel SAM kaj Atmel AVR bazitaj sur ARM Cortex-M kun kapablo On-Chip Debug.

Ĝi subtenas:

- Programado kaj sur-blata senararigado de ĉiuj Atmel AVR UC3 mikroregiloj sur ambaŭ JTAG kaj aWire-interfacoj

- Programado kaj sur-blata senararigado de ĉiuj AVR XMEGA-familiaparatoj sur ambaŭ JTAG kaj PDI 2wire-interfacoj

- Programado (JTAG kaj SPI) kaj senararigado de ĉiuj AVR 8-bitaj mikroregiloj kun OCD-subteno sur ambaŭ JTAG aŭ debugWIRE interfacoj

- Programado kaj senararigado de ĉiuj mikroregiloj bazitaj sur Atmel SAM ARM Cortex-M sur kaj SWD kaj JTAG interfacoj

- Programado (TPI) de ĉiuj Atmel tinyAVR 8-bitaj mikroregiloj kun subteno por ĉi tiu interfaco

1.2. Trajtoj de Atmel-ICE

- Plene kongrua kun Atmel Studio

- Subtenas programadon kaj senararigadon de ĉiuj Atmel AVR UC3 32-bitaj mikroregiloj

- Subtenas programadon kaj senararigon de ĉiuj 8-bitaj AVR XMEGA-aparatoj

- Subtenas programadon kaj senararigon de ĉiuj 8-bitaj Atmel megaAVR® kaj etajAVR-aparatoj kun OCD

- Subtenas programadon kaj senararigon de ĉiuj mikroregiloj bazitaj sur SAM ARM Cortex-M

- Celo operacia voltage gamo de 1.62V ĝis 5.5V

- Ĉerpas malpli ol 3mA de cela VTref kiam vi uzas debugWIRE-interfacon kaj malpli ol 1mA por ĉiuj aliaj interfacoj

- Subtenas JTAG horloĝfrekvencoj de 32kHz ĝis 7.5MHz

- Subtenas PDI-horloĝfrekvencojn de 32kHz ĝis 7.5MHz

- Elportas debugWIRE-baŭdrapidecojn de 4kbit/s ĝis 0.5Mbit/s

- Elportas aWire-baŭdrapidecojn de 7.5kbit/s ĝis 7Mbit/s

- Subtenas SPI-horloĝfrekvencojn de 8kHz ĝis 5MHz

- Elportas UPDI-baŭdrapidecojn de ĝis 750 kbit/s

- Elportas SWD-horloĝfrekvencojn de 32kHz ĝis 10MHz

- USB 2.0 altrapida gastiga interfaco

- ITM-seria spurkapto ĝis 3MB/s

- Subtenas interfacojn DGI SPI kaj USART kiam ne cimigas aŭ programadon

- Elportas 10-stiftojn 50-mil JTAG konektilo kun kaj AVR kaj Cortex pinouts. La norma sonda kablo subtenas AVR 6-stiftajn ISP/PDI/TPI 100-mil-kapojn same kiel 10-pintajn 50-mil. Adaptilo disponeblas por subteni 6-pinglaj 50-mil, 10-pinglaj 100-mil, kaj 20-pinglaj 100-mil-kapoj. Pluraj ilaj opcioj estas haveblaj kun malsamaj kabladoj kaj adaptiloj.

1.3. Sistemaj Postuloj

La Atmel-ICE-unuo postulas, ke antaŭfina sencimiga medio Atmel Studio versio 6.2 aŭ poste estas instalita en via komputilo.

La Atmel-ICE devus esti konektita al la gastiga komputilo per la USB-kablo provizita, aŭ atestita Mikro-USB-kablo.

Komencu kun la Atmel-ICE

2.1. Plena Kit Enhavo

La plena ilaro Atmel-ICE enhavas ĉi tiujn erojn:

- Atmel-ICE-unuo

- USB-kablo (1.8m, altrapida, Micro-B)

- Adaptiltabulo enhavanta 50-mil AVR, 100-mil AVR/SAM, kaj 100-mil 20-stiftajn SAM-adaptilojn

- IDC plata kablo kun 10-stifta 50-mil konektilo kaj 6-stifta 100-mil konektilo

- 50-mil 10-stifta mini kalmarkablo kun 10 x 100-mil ingoj

Figuro 2-1. Atmel-ICE Plena Kit Enhavo 2.2. Baza Kit Enhavo

2.2. Baza Kit Enhavo

La baza ilaro Atmel-ICE enhavas ĉi tiujn erojn:

- Atmel-ICE-unuo

- USB-kablo (1.8m, altrapida, Micro-B)

- IDC plata kablo kun 10-stifta 50-mil konektilo kaj 6-stifta 100-mil konektilo

Figuro 2-2. Enhavo de Baza Kit de Atmel-ICE 2.3. PCBA Ilaro Enhavo

2.3. PCBA Ilaro Enhavo

La ilaro Atmel-ICE PCBA enhavas ĉi tiujn erojn:

- Atmel-ICE-unuo sen plasta enkapsuligo

Figuro 2-3. Atmel-ICE PCBA Kit Enhavo 2.4. Rezervaj Partaj Ilaro

2.4. Rezervaj Partaj Ilaro

La jenaj rezervaj ilaroj haveblas:

- Adaptilaro

- Kablo-kompleto

Figuro 2-4. Enhavo de Atmel-ICE Adapter Kit 2.5. Kit Superview

2.5. Kit Superview

La opcioj de ilaro Atmel-ICE estas montritaj diagrame ĉi tie:

Figuro 2-6. Atmel-ICE Kit Superview 2.6. Kunvenado de la Atmel-ICE

2.6. Kunvenado de la Atmel-ICE

La Atmel-ICE-unuo estas ekspedita sen kabloj alkroĉitaj. Du kablaj elektoj estas provizitaj en la plena ilaro:

- 50-mil 10-stifta IDC-plata kablo kun 6-stifta ISP kaj 10-stiftaj konektiloj

- 50-mil 10-stifta mini-kalmarkablo kun 10 x 100-mil ingoj

Figuro 2-7. Atmel-ICE-Kabloj Por plej multaj celoj, la 50-mil 10-stifta IDC-plata kablo povas esti uzata, konektante aŭ denaske al ĝiaj 10-stiftaj aŭ 6-stiftaj konektiloj, aŭ konektante per la adaptila tabulo. Tri adaptiloj estas provizitaj sur unu malgranda PCBA. La sekvaj adaptiloj estas inkluzivitaj:

Por plej multaj celoj, la 50-mil 10-stifta IDC-plata kablo povas esti uzata, konektante aŭ denaske al ĝiaj 10-stiftaj aŭ 6-stiftaj konektiloj, aŭ konektante per la adaptila tabulo. Tri adaptiloj estas provizitaj sur unu malgranda PCBA. La sekvaj adaptiloj estas inkluzivitaj:

- 100-mil 10-stifta JTAG/SWD-adaptilo

- 100-mil 20-stifta SAM JTAG/SWD-adaptilo

- 50-mil 6-stifta SPI/debugWIRE/PDI/aWire-adaptilo

Figuro 2-8. Atmel-ICE-Adaptiloj Notu:

Notu:

50-mil JTAG adaptilo ne estis provizita - ĉi tio estas ĉar la 50-mil 10-stifta IDC-kablo povas esti uzata por konekti rekte al 50-mil J.TAG kaplinio. Por la partnumero de la komponento uzita por la 50-mil 10-stifta konektilo, vidu Atmel-ICE Target Connectors Part Numbers.

La 6-stifta ISP/PDI-kapo estas inkluzivita kiel parto de la 10-stifta IDC-kablo. Ĉi tiu fino povas esti fortranĉita se ĝi ne estas postulata.

Por kunmeti vian Atmel-ICE en ĝian defaŭltan agordon, konektu la 10-pintan 50-mil IDC-kablon al la unuo kiel montrite sube. Nepre orientu la kablon tiel ke la ruĝa drato (pinglo 1) sur la kablo akordiĝu kun la triangula indikilo sur la blua zono de la enfermaĵo. La kablo devus konekti supren de la unuo. Nepre konektiĝu al la haveno responda al la pinout de via celo - AVR aŭ SAM.

Figuro 2-9. Atmel-ICE Kablo-Konekto Figuro 2-10. Atmel-ICE AVR Probe Connection

Figuro 2-10. Atmel-ICE AVR Probe Connection

Figuro 2-11. Atmel-ICE SAM Probe Connection

Figuro 2-11. Atmel-ICE SAM Probe Connection 2.7. Malfermante la Atmel-ICE

2.7. Malfermante la Atmel-ICE

Notu:

Por normala funkciado, la Atmel-ICE-unuo ne devas esti malfermita. Malfermo de la unuo estas farita je via propra risko.

Oni devas preni kontraŭstatikajn antaŭzorgojn.

La ĉemetaĵo de Atmel-ICE konsistas el tri apartaj plastaj komponentoj - supra kovrilo, malsupra kovrilo kaj blua zono - kiuj estas kunigitaj dum kunigo. Por malfermi la unuon, simple enmetu grandan platan ŝraŭbturnilon en la aperturojn en la blua zono, apliku iom da interna premo kaj tordu milde. Ripetu la procezon sur la aliaj lutjanaj truoj, kaj la supra kovrilo aperos.

Figuro 2-12. Malfermante la Atmel-ICE (1)

Figuro 2-13. Malfermante la Atmel-ICE (2)

Figuro 2-13. Malfermante la Atmel-ICE (2)

Figuro 2-14. Malfermante la Atmel-ICE(3)

Figuro 2-14. Malfermante la Atmel-ICE(3) Por fermi la unuon denove, simple vicigu la suprajn kaj malsuprajn kovrilojn ĝuste, kaj premu firme kune.

Por fermi la unuon denove, simple vicigu la suprajn kaj malsuprajn kovrilojn ĝuste, kaj premu firme kune.

2.8. Funkciigante la Atmel-ICE

La Atmel-ICE estas funkciigita per la USB-buso voltage. Ĝi postulas malpli ol 100mA por funkcii, kaj tial povas esti funkciigita per USB-nabo. La elektra LED lumiĝos kiam la unuo estas enŝovita. Kiam ne estas konektita en aktiva programado aŭ senarariga sesio, la unuo eniros malaltan konsuman reĝimon por konservi la kuirilaron de via komputilo. La Atmel-ICE ne povas esti malŝaltita - ĝi devus esti malŝaltita kiam ne estas uzata.

2.9. Konektante al la Gastiganta Komputilo

La Atmel-ICE komunikas ĉefe uzante norman HID-interfacon, kaj ne postulas specialan ŝoforon sur la gastiga komputilo. Por uzi la altnivelan Data Gateway-funkcion de la Atmel-ICE, nepre instalu la USB-ŝoforon sur la gastiga komputilo. Ĉi tio fariĝas aŭtomate kiam oni instalas la antaŭfinan programaron senpage provizitan de Atmel. Vidu www.atmel.com por pliaj informoj aŭ por elŝuti la plej novan antaŭfinan programaron.

La Atmel-ICE devas esti konektita al disponebla USB-haveno en la gastiga komputilo per la USB-kablo provizita, aŭ taŭga USB-atestita mikrokablo. La Atmel-ICE enhavas USB 2.0 konforman regilon, kaj povas funkcii en ambaŭ plenrapidaj kaj altrapidaj reĝimoj. Por plej bonaj rezultoj, konektu la Atmel-ICE rekte al USB 2.0 konforma altrapida nabo sur la gastiga komputilo per la kablo provizita.

2.10. Instalado de USB-ŝoforoj

2.10.1. Vindozo

Kiam oni instalas la Atmel-ICE sur komputilon kun Microsoft® Windows®, la USB-ŝoforo estas ŝarĝita kiam la Atmel-ICE unue estas enŝovita.

Notu:

Nepre instalu la antaŭfinajn programarpakaĵojn antaŭ ol enŝalti la unuon por la unua fojo.

Post kiam sukcese instalita, la Atmel-ICE aperos en la aparata administranto kiel "Homa Interfaca Aparato".

Konektante la Atmel-ICE

3.1. Konektante al AVR kaj SAM Celaj Aparatoj

La Atmel-ICE estas ekipita per du 50-mil 10-stiftoj JTAG konektiloj. Ambaŭ konektiloj estas rekte elektre konektitaj, sed konformas al du malsamaj pinouts; la AVR JTAG kaplinio kaj la kaplinio ARM Cortex Debug. La konektilo devus esti elektita surbaze de la pinout de la cela tabulo, kaj ne la cela MCU-tipo - ekzample SAM-aparato muntita en AVR STK® 600 stako devus uzi la AVR-kapon.

Diversaj kabladoj kaj adaptiloj estas haveblaj en la malsamaj Atmel-ICE-kompletoj. An superview de konekto-opcioj estas montrata.

Figuro 3-1. Atmel-ICE-Konekto-Ebloj La ruĝa drato markas pinglon 1 de la 10-stifta 50-mil konektilo. Pinglo 1 de la 6-stifta 100-mil konektilo estas metita dekstren de la klavado kiam la konektilo vidiĝas de la kablo. Pinglo 1 de ĉiu konektilo sur la adaptilo estas markita per blanka punkto. La malsupra figuro montras la pinout de la sencimiga kablo. La konektilo markis A ŝtopas en la erarserĉilon dum la B-flanko ŝtopas en la celtabulo.

La ruĝa drato markas pinglon 1 de la 10-stifta 50-mil konektilo. Pinglo 1 de la 6-stifta 100-mil konektilo estas metita dekstren de la klavado kiam la konektilo vidiĝas de la kablo. Pinglo 1 de ĉiu konektilo sur la adaptilo estas markita per blanka punkto. La malsupra figuro montras la pinout de la sencimiga kablo. La konektilo markis A ŝtopas en la erarserĉilon dum la B-flanko ŝtopas en la celtabulo.

Figuro 3-2. Sencimigi Kablo Pinout

3.2. Konektante al JTAG Celo

3.2. Konektante al JTAG Celo

La Atmel-ICE estas ekipita per du 50-mil 10-stiftoj JTAG konektiloj. Ambaŭ konektiloj estas rekte elektre konektitaj, sed konformas al du malsamaj pinouts; la AVR JTAG kaplinio kaj la kaplinio ARM Cortex Debug. La konektilo devus esti elektita surbaze de la pinout de la cela tabulo, kaj ne la cela MCU-tipo - ekzample SAM-aparato muntita en AVR STK600-stako devus uzi la AVR-kapon.

La rekomendita pinout por la 10-stifta AVR JTAG konektilo estas montrita en Figuro 4-6. La rekomendita pinout por la 10-stifta ARM Cortex Debug-konektilo estas montrita en Figuro 4-2.

Rekta konekto al norma 10-pingla 50-mil-kapo

Uzu la 50-mil 10-stiftan platan kablon (inkluzivita en iuj ilaroj) por konekti rekte al tabulo subtenanta ĉi tiun kaplinian tipon. Uzu la AVR-konektilo-havenon sur la Atmel-ICE por kaplinioj kun la AVR-pinout, kaj la SAM-konektila haveno por kaplinioj konformaj al la ARM Cortex Debug-kapa pinouto.

La pinouts por ambaŭ 10-stiftaj konektilhavenoj estas montritaj sube.

Konekto al norma 10-pingla 100-mil-kapo

Uzu norman adaptilon de 50-mil ĝis 100-mil por konekti al 100-mil-kapoj. Adaptilestraro (inkluzivita en kelkaj ilaroj) povas esti uzita por tiu celo, aŭ alternative la JTAGICE3-adaptilo povas esti uzata por AVR-celoj.

![]() Grava:

Grava:

La JTAGICE3 100-mil-adaptilo ne povas esti uzata kun la SAM-konektila haveno, ĉar pingloj 2 kaj 10 (AVR GND) sur la adaptilo estas konektitaj.

Konekto al kutima 100-mila kaplinio

Se via cela tabulo ne havas kongruan 10-pinglan JTAG kaplinio en 50- aŭ 100-mil, vi povas mapi al kutima pinout per la 10-pingla "mini-kalmaro" kablo (inkluzivita en iuj ilaroj), kiu donas aliron al dek individuaj 100-mil ingoj.

Konekto al 20-pingla 100-mil-kapor

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al celoj kun 20-pingla 100-mil-kapo.

Tabelo 3-1. Atmel-ICE JTAG Pinglo Priskribo

| Nomo | AVR baborda pinglo | SAM baborda pinglo | Priskribo |

| TCK | 1 | 4 | Testa Horloĝo (horloĝsignalo de la Atmel-ICE en la cela aparaton). |

| TMS | 5 | 2 | Test Mode Select (kontrolsignalo de la Atmel-ICE en la cela aparato). |

| TDI | 9 | 8 | Test Data In (datenoj transdonitaj de la Atmel-ICE en la cela aparaton). |

| TDO | 3 | 6 | Test Data Out (datenoj transdonitaj de la cela aparato en la Atmel-ICE). |

| nTRST | 8 | – | Test Restarigi (laŭvola, nur ĉe iuj AVR-aparatoj). Uzita por restarigi la JTAG TAP-regilo. |

| nSRST | 6 | 10 | Restarigi (laŭvola). Uzita por restarigi la celan aparaton. Konekti ĉi tiun pinglon estas rekomendita, ĉar ĝi permesas al la Atmel-ICE teni la celatan aparaton en restarigita stato, kio povas esti esenca por sencimigi en certaj scenaroj. |

| VTG | 4 | 1 | Celo voltage referenco. La Atmel-ICE samples la celo voltage sur ĉi tiu pinglo por funkciigi la nivelkonvertilojn ĝuste. La Atmel-ICE ĉerpas malpli ol 3mA de ĉi tiu pinglo en debugWIRE-reĝimo kaj malpli ol 1mA en aliaj reĝimoj. |

| GND | 2, 10 | 3, 5, 9 | Tero. Ĉiuj devas esti konektitaj por certigi, ke la Atmel-ICE kaj la cela aparato kunhavas la saman teran referencon. |

3.3. Konektante al aWire Celo

La aWire-interfaco postulas nur unu datumlinion krom VCC kaj GND. Sur la celo ĉi tiu linio estas la linio nRESET, kvankam la erarserĉilo uzas la JTAG TDO-linio kiel la datumlinio.

La rekomendita pinout por la 6-pingla aWire-konektilo estas montrita en Figuro 4-8.

Konekto al 6-pingla 100-mil aWire-kapo

Uzu la 6-pinglan 100-milan kranon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mil aWire-kapo.

Konekto al 6-pingla 50-mil aWire-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al norma 50-mil aWire-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Tri konektoj estas bezonataj, kiel priskribite en la suba tabelo.

Tabelo 3-2. Atmel-ICE aWire Pin Mapping

|

Atmel-ICE AVR havenpingloj |

Celstiftoj | Mini-kalmaro pinglo |

aDrato pinout |

| Pinglo 1 (TCK) | 1 | ||

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | DATUMO | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 | ||

| Pinglo 6 (nSRST) | 6 | ||

| Pinglo 7 (Ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | 9 | ||

| Pinglo 10 (GND) | 0 |

3.4. Konektante al PDI-Celo

La rekomendita pinout por la 6-pingla PDI-konektilo estas montrita en Figuro 4-11.

Konekto al 6-pingla 100-mil PDI-kapo

Uzu la 6-pintan 100-mil-frapon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mil PDI-kapo.

Konekto al 6-pingla 50-mil PDI-kapo

Uzu la adaptiltabulo (inkluzivita en iuj ilaroj) por konekti al norma 50-mil PDI-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Kvar konektoj estas bezonataj, kiel priskribite en la suba tabelo.

![]() Grava:

Grava:

La pinout necesa estas diferenca de la JTAGICE mkII JTAG sondilo, kie PDI_DATA estas konektita al pinglo 9. La Atmel-ICE estas kongrua kun la pinout uzata de la Atmel-ICE, JTAGProduktoj ICE3, AVR ONE! kaj AVR Dragon™.

Tabelo 3-3. Atmel-ICE PDI Pin-mapado

| Atmel-ICE AVR havenpingloj | Celstiftoj | Mini-kalmaro pinglo |

aDrato pinout |

| Pinglo 1 (TCK) | 1 | ||

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | DATUMO | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 | ||

| Pinglo 6 (nSRST) | 6 | ||

| Pinglo 7 (Ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | 9 | ||

| Pinglo 10 (GND) | 0 |

3.4 Konekti al PDI-Celo

La rekomendita pinout por la 6-pingla PDI-konektilo estas montrita en Figuro 4-11.

Konekto al 6-pingla 100-mil PDI-kapo

Uzu la 6-pintan 100-mil-frapon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mil PDI-kapo.

Konekto al 6-pingla 50-mil PDI-kapo

Uzu la adaptiltabulo (inkluzivita en iuj ilaroj) por konekti al norma 50-mil PDI-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Kvar konektoj estas bezonataj, kiel priskribite en la suba tabelo.

![]() Grava:

Grava:

La pinout necesa estas diferenca de la JTAGICE mkII JTAG sondilo, kie PDI_DATA estas konektita al pinglo 9. La Atmel-ICE estas kongrua kun la pinout uzata de la Atmel-ICE, JTAGICE3, AVR UNU!, kaj AVR Dragon™ produktoj.

Tabelo 3-3. Atmel-ICE PDI Pin-mapado

| Atmel-ICE AVR havenstifto | Celstiftoj | Mini-kalmaro pinglo | Atmel STK600 PDI pinout |

| Pinglo 1 (TCK) | 1 | ||

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | PDI_DATA | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 | ||

| Pinglo 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pinglo 7 (ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | 9 | ||

| Pinglo 10 (GND) | 0 |

3.5 Konekti al UPDI Celo

La rekomendita pinout por la 6-pingla UPDI-konektilo estas montrita en Figuro 4-12.

Konekto al 6-pingla 100-mil UPDI-kapo

Uzu la 6-pinglan 100-milan kranon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mila UPDI-kapo.

Konekto al 6-pingla 50-mil UPDI-kapo

Uzu la adaptiltabulo (inkluzivita en iuj ilaroj) por konekti al norma 50-mil UPDI-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Tri konektoj estas bezonataj, kiel priskribite en la suba tabelo.

Tabelo 3-4. Atmel-ICE UPDI Pin-Mapado

| Atmel-ICE AVR havenstifto | Celstiftoj | Mini-kalmaro pinglo |

Atmel STK600 UPDI pinout |

| Pinglo 1 (TCK) | 1 | ||

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 | ||

| Pinglo 6 (nSRST) | [/RESETigi sencon] | 6 | 5 |

| Pinglo 7 (Ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | 9 | ||

| Pinglo 10 (GND) | 0 |

3.6 Konekti al debugWIRE Celo

La rekomendita pinout por la 6-pingla debugWIRE (SPI) konektilo estas montrita en Tabelo 3-6.

Konekto al 6-pingla 100-mil SPI-kapo

Uzu la 6-pinglan 100-mil-frapon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mil SPI-kapo.

Konekto al 6-pingla 50-mil SPI-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al norma 50-mil SPI-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Tri konektoj estas postulataj, kiel priskribite en Tabelo 3-5.

Kvankam la debugWIRE-interfaco nur postulas unu signallinion (RESET), VCC kaj GND por funkcii ĝuste, estas konsilite havi aliron al la plena SPI-konektilo por ke la debugWIRE-interfaco povas esti ebligita kaj malŝaltita uzante SPI-programadon.

Kiam la DWEN-fuzeo estas ebligita, la SPI-interfaco estas anstataŭita interne por ke la OCD-modulo havu kontrolon super la RESET-pinglo. La debugWIRE OCD kapablas malŝalti sin provizore (uzante la butonon sur la sencimiga langeto en la propriet-dialogo en Atmel Studio), tiel liberigante kontrolon de la RESET-linio. La SPI-interfaco tiam estas havebla denove (nur se la SPIEN-fuzeo estas programita), permesante al la DWEN-fuzeo esti ne-programita uzante la SPI-interfacon. Se potenco estas ŝanĝita antaŭ ol la DWEN-fuzeo estas neprogramita, la debugWIRE-modulo denove prenos kontrolon de la RESET-stifto.

Notu:

Estas tre konsilite simple lasi Atmel Studion prizorgi agordon kaj malplenigon de la DWEN-fuzeo.

Ne eblas uzi la interfacon debugWIRE se la lockbits sur la cela AVR-aparato estas programitaj. Ĉiam certigu, ke la lockbits estas purigitaj antaŭ programado de la DWEN-fuzeo kaj neniam agordu la lockbits dum la DWEN-fuzeo estas programita. Se kaj la debugWIRE ebligas fuzeo (DWEN) kaj lockbits estas fiksitaj, oni povas uzi High Voltage Programado fari blaton viŝi, kaj tiel malbari la lockbits.

Kiam la lockbits estas malbaritaj la debugWIRE-interfaco estos reebligita. La SPI-Interfaco kapablas nur legi fuzeojn, legi subskribon kaj elfari pecetviŝadon kiam la DWEN-fuzeo estas neprogramita.

Tabelo 3-5. Atmel-ICE debugWIRE Pin-Mapado

| Atmel-ICE AVR havenstifto | Celstiftoj |

Mini-kalmaro pinglo |

| Pinglo 1 (TCK) | 1 | |

| Pinglo 2 (GND) | GND | 2 |

| Pinglo 3 (TDO) | 3 | |

| Pinglo 4 (VTG) | VTG | 4 |

| Pinglo 5 (TMS) | 5 | |

| Pinglo 6 (nSRST) | RESET | 6 |

| Pinglo 7 (Ne konektita) | 7 | |

| Pinglo 8 (nTRST) | 8 | |

| Stifto 9 (TDI) | 9 | |

| Pinglo 10 (GND) | 0 |

3.7 Konekti al SPI-Celo

La rekomendita pinout por la 6-pingla SPI-konektilo estas montrita en Figuro 4-10.

Konekto al 6-pingla 100-mil SPI-kapo

Uzu la 6-pinglan 100-mil-frapon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mil SPI-kapo.

Konekto al 6-pingla 50-mil SPI-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al norma 50-mil SPI-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Ses konektoj estas bezonataj, kiel priskribite en la suba tabelo.

![]() Grava:

Grava:

La SPI-interfaco estas efike malfunkciigita kiam la debugWIRE ebliga fuzeo (DWEN) estas programita, eĉ se SPIEN-fuzeo ankaŭ estas programita. Por reebligi la SPI-interfacon, la komando 'malŝalti debugWIRE' devas esti eligita dum en debugWIRE-sencimiga sesio. Malebligi debugWIRE tiamaniere postulas ke la SPIEN-fuzeo jam estas programita. Se Atmel Studio malsukcesas malŝalti debugWIRE, estas verŝajne ĉar la SPIEN-fuzeo NE estas programita. Se ĉi tio estas la kazo, necesas uzi alt-voltage programa interfaco por programi la SPIEN-fuzeon.

![]() Informoj:

Informoj:

La SPI-interfaco ofte estas referita kiel "ISP", ĉar ĝi estis la unua In System Programming-interfaco sur Atmel AVR-produktoj. Aliaj interfacoj nun estas haveblaj por En System Programming.

Tabelo 3-6. Atmel-ICE SPI Pint-Mapado

| Atmel-ICE AVR havenpingloj | Celstiftoj | Mini-kalmaro pinglo |

SPI pinout |

| Pinglo 1 (TCK) | SCK | 1 | 3 |

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | MISO | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 | ||

| Pinglo 6 (nSRST) | /RESETIGI | 6 | 5 |

| Pinglo 7 (ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | MOSI | 9 | 4 |

| Pinglo 10 (GND) | 0 |

3.8 Konekti al TPI-Celo

La rekomendita pinout por la 6-pingla TPI-konektilo estas montrita en Figuro 4-13.

Konekto al 6-pingla 100-mil TPI-kapo

Uzu la 6-pinglan 100-milan kranon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mil TPI-kapo.

Konekto al 6-pingla 50-mil TPI-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al norma 50-mil TPI-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Ses konektoj estas bezonataj, kiel priskribite en la suba tabelo.

Tabelo 3-7. Atmel-ICE TPI Pinglo-Mapado

| Atmel-ICE AVR havenpingloj | Celstiftoj | Mini-kalmaro pinglo |

TPI pinout |

| Pinglo 1 (TCK) | HORLOĜO | 1 | 3 |

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | DATUMO | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 |

| Pinglo 6 (nSRST) | /RESETIGI | 6 | 5 |

| Pinglo 7 (ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | 9 | ||

| Pinglo 10 (GND) | 0 |

3.9 Konekti al SWD Celo

La ARM SWD-interfaco estas subaro de la JTAG interfaco, uzante la TCK- kaj TMS-stiftojn, kio signifas, ke kiam li konektas al SWD-aparato, la 10-stifta JTAG konektilo povas teknike esti uzata. La BRAKO JTAG kaj AVR JTAG konektiloj estas, aliflanke, ne pin-kongruaj, tiel ke tio dependas de la aranĝo de la celtabulo en uzo. Kiam vi uzas STK600 aŭ tabulon uzante la AVR JTAG pinout, la AVR-konektila haveno sur la Atmel-ICE devas esti uzata. Konektante al tabulo, kiu uzas la ARM JTAG pinout, la SAM-konektila haveno sur la Atmel-ICE devas esti uzata.

La rekomendita pinout por la 10-pingla Cortex Debug-konektilo estas montrita en Figuro 4-4.

Konekto al 10-pingla 50-mil Cortex-kapo

Uzu la platan kablon (inkluzivita en iuj ilaroj) por konekti al norma 50-mil Cortex-kapo.

Konekto al 10-pingla 100-mil Cortex-aranĝa kaplinio

Uzu la adaptiltabulo (inkluzivita en iuj ilaroj) por konekti al 100-mil Cortex-pinout-kapo.

Konekto al 20-pingla 100-mil SAM-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al 20-pingla 100-mil SAM-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR aŭ SAM-konektila haveno kaj la cela tabulo. Ses konektoj estas bezonataj, kiel priskribite en la suba tabelo.

Tablo 3-8. Atmel-ICE SWD Pin-mapado

| Nomo | AVR baborda pinglo | SAM baborda pinglo | Priskribo |

| SWDC LK | 1 | 4 | Seria Drato Sencimiga Horloĝo. |

| SWDIO | 5 | 2 | Seria Drato Sencimiga Datumoj Enigo/Eligo. |

| SWO | 3 | 6 | Seria Drata Eligo (laŭvola - ne efektivigita sur ĉiuj aparatoj). |

| nSRST | 6 | 10 | Restarigi. |

| VTG | 4 | 1 | Celo voltage referenco. |

| GND | 2, 10 | 3, 5, 9 | Tero. |

3.10 Konekti al Data Gateway Interface

La Atmel-ICE subtenas limigitan Data Gateway Interface (DGI) kiam senararigado kaj programado ne estas uzataj. Funkcio estas identa al tiu trovita sur Atmel Xplained Pro ilaroj funkciigitaj de la Atmel EDBG-aparato.

La Data Gateway Interface estas interfaco por flui datumoj de la cela aparato al komputilo. Ĉi tio estas intencita kiel helpo en aplika elpurigado kaj ankaŭ por pruvo de funkcioj en la aplikaĵo funkcianta sur la cela aparato.

DGI konsistas el multoblaj kanaloj por datumfluo. La Atmel-ICE subtenas la sekvajn reĝimojn:

- USART

- SPI

Tablo 3-9. Atmel-ICE DGI USART Pinout

|

AVR-haveno |

SAM-haveno | DGI USART pinglo |

Priskribo |

| 3 | 6 | TX | Transsendu pinglo de Atmel-ICE al la cela aparato |

| 4 | 1 | VTG | Celo voltage (referenco voltage) |

| 8 | 7 | RX | Ricevu pinglo de la cela aparato al Atmel-ICE |

| 9 | 8 | CLK | USART-horloĝo |

| 2, 10 | 3, 5, 9 | GND | Tero |

Tablo 3-10. Atmel-ICE DGI SPI Pinout

|

AVR-haveno |

SAM-haveno | DGI SPI-pinglo |

Priskribo |

| 1 | 4 | SCK | SPI-horloĝo |

| 3 | 6 | MISO | Majstro In Slave Out |

| 4 | 1 | VTG | Celo voltage (referenco voltage) |

| 5 | 2 | nCS | Peceto elekta aktiva malalta |

| 9 | 8 | MOSI | Majstro Ekstere Sklavo En |

| 2, 10 | 3, 5, 9 | GND | Tero |

![]() Grava: SPI kaj USART-interfacoj ne povas esti uzataj samtempe.

Grava: SPI kaj USART-interfacoj ne povas esti uzataj samtempe.

![]() Grava: DGI kaj programado aŭ senararigado ne povas esti uzataj samtempe.

Grava: DGI kaj programado aŭ senararigado ne povas esti uzataj samtempe.

Sencimigado sur-blato

4.1 Enkonduko

Sencimigado sur-blato

Sur-blata sencimiga modulo estas sistemo permesanta al programisto monitori kaj kontroli ekzekuton sur aparato de ekstera evoluplatformo, kutime per aparato konata kiel erarserĉilo aŭ sencimiga adaptilo.

Kun OCD-sistemo la aplikiĝo povas esti efektivigita konservante precizajn elektrajn kaj tempajn karakterizaĵojn en la celsistemo, dum povante ĉesigi ekzekuton kondiĉe aŭ mane kaj inspekti programfluon kaj memoron.

Kura Reĝimo

Kiam en Run-reĝimo, la ekzekuto de kodo estas tute sendependa de la Atmel-ICE. La Atmel-ICE kontinue monitoros la celan aparaton por vidi ĉu paŭzokondiĉo okazis. Kiam tio okazas, la OCD-sistemo pridemandas la aparaton per sia sencimiga interfaco, permesante al la uzanto view la interna stato de la aparato.

Haltita Reĝimo

Kiam rompopunkto estas atingita, la programekzekuto estas haltita, sed iu I/O povas daŭri funkcii kvazaŭ neniu rompopunkto estus okazinta. Por ekzample, supozu ke USART elsendo ĵus estis komencita kiam rompopunkto estas atingita. En ĉi tiu kazo la USART daŭre funkcias plenrapide kompletigante la dissendon, kvankam la kerno estas en haltigita reĝimo.

Aparataro Breakpoints

La cela OCD-modulo enhavas kelkajn programajn nombrilo-komparilojn efektivigitajn en la aparataro. Kiam la programa nombrilo kongruas kun la valoro stokita en unu el la komparregistroj, la OCD eniras haltigitan reĝimon. Ĉar hardvaraj romppunktoj postulas diligentan aparataron sur la OCD-modulo, la nombro da romppunktoj haveblaj dependas de la grandeco de la OCD-modulo efektivigita sur la celo. Kutime unu tia aparatara komparilo estas 'rezervita' de la erarserĉilo por interna uzo.

Programaro Breakpoints

Programaro-romppunkto estas BREAK-instrukcio metita en programmemoron sur la cela aparato. Kiam ĉi tiu instrukcio estas ŝarĝita, la ekzekuto de la programo rompiĝos kaj la OCD eniras haltigitan reĝimon. Por daŭrigi la ekzekuton, "komenco" komando devas esti donita de la OCD. Ne ĉiuj Atmel-aparatoj havas OCD-modulojn subtenantajn la BREAK-instrukcion.

4.2 SAM-Aparatoj kun JTAG/SWD

Ĉiuj SAM-aparatoj havas la SWD-interfacon por programado kaj senararigado. Krome, kelkaj SAM-aparatoj havas JTAG interfaco kun identa funkcieco. Kontrolu la aparatan datenfolion por subtenataj interfacoj de tiu aparato.

4.2.1.ARM CoreSight Komponentoj

Atmel ARM Cortex-M-bazitaj mikroregiloj efektivigas CoreSight-konformajn OCD-komponentojn. La trajtoj de ĉi tiuj komponantoj povas varii de aparato al aparato. Por pliaj informoj konsultu la datenfolion de la aparato kaj ankaŭ CoreSight-dokumentadon provizitan de ARM.

4.2.1. JTAG Fizika Interfaco

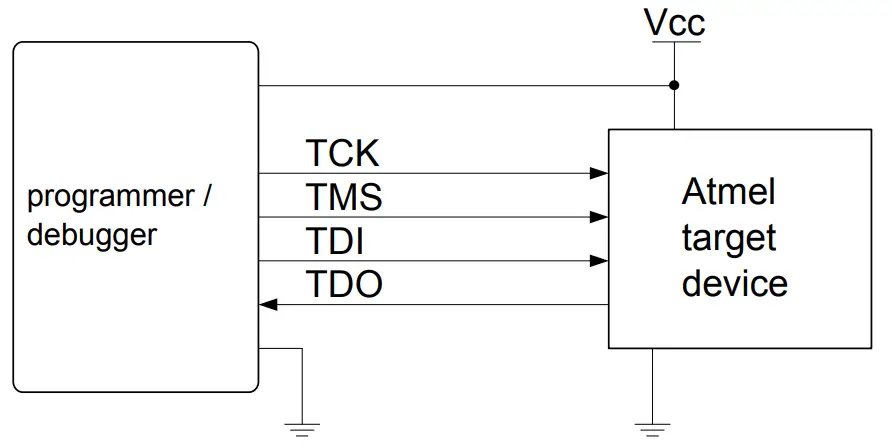

La JTAG interfaco konsistas el 4-drata Test Access Port (TAP) regilo kiu estas konforma al la IEEE® 1149.1 normo. La IEEE-normo estis evoluigita por disponigi industrinorman manieron efike testi cirkvitplatan konekteblecon (Boundary Scan). Atmel AVR kaj SAM-aparatoj etendis ĉi tiun funkcion por inkluzivi plenan Programadon kaj Sur-blatan Sencimigan subtenon.

Figuro 4-1. JTAG Interfacaj Bazoj

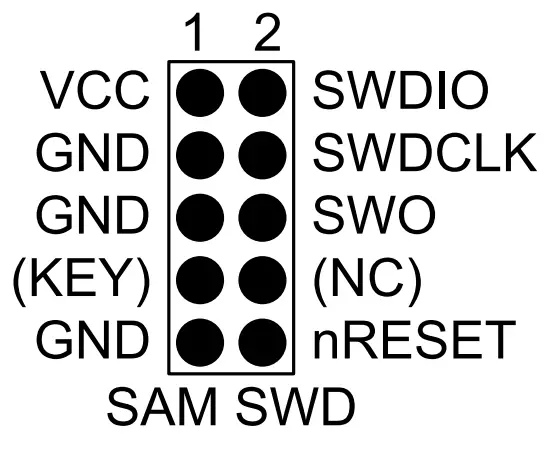

4.2.2.1 SAM JTAG Pinout (sencimiga konektilo Cortex-M)

Dum dizajnado de aplika PCB kiu inkluzivas Atmel SAM kun la JTAG interfaco, oni rekomendas uzi la pinout kiel montrita en la figuro malsupre. Ambaŭ 100-mil kaj 50-mil variantoj de ĉi tiu pinout estas subtenataj, depende de la kablado kaj adaptiloj inkluzivitaj kun la aparta ilaro.

Figuro 4-2. SAM JTAG Header Pinout

Tabelo 4-1. SAM JTAG Pinglo Priskribo

| Nomo | Pinglo |

Priskribo |

| TCK | 4 | Testa Horloĝo (horloĝsignalo de la Atmel-ICE en la cela aparaton). |

| TMS | 2 | Test Mode Select (kontrolsignalo de la Atmel-ICE en la cela aparato). |

| TDI | 8 | Test Data In (datenoj transdonitaj de la Atmel-ICE en la cela aparaton). |

| TDO | 6 | Test Data Out (datenoj transdonitaj de la cela aparato en la Atmel-ICE). |

| nRESET | 10 | Restarigi (laŭvola). Uzita por restarigi la celan aparaton. Konekti ĉi tiun pinglon estas rekomendita, ĉar ĝi permesas al la Atmel-ICE teni la celatan aparaton en restarigita stato, kio povas esti esenca por sencimigi en certaj scenaroj. |

| VTG | 1 | Celo voltage referenco. La Atmel-ICE samples la celo voltage sur ĉi tiu pinglo por funkciigi la nivelkonvertilojn ĝuste. La Atmel-ICE ĉerpas malpli ol 1mA de ĉi tiu pinglo en ĉi tiu reĝimo. |

| GND | 3, 5, 9 | Tero. Ĉiuj devas esti konektitaj por certigi, ke la Atmel-ICE kaj la cela aparato kunhavas la saman teran referencon. |

| Ŝlosilo | 7 | Konektita interne al la TRST-stifto sur la AVR-konektilo. Rekomendita kiel ne konektita. |

![]() Konsilo: Memoru inkluzivi malkunligan kondensilon inter pinglo 1 kaj GND.

Konsilo: Memoru inkluzivi malkunligan kondensilon inter pinglo 1 kaj GND.

4.2.2.2 JTAG Lekanto Ĉenado

La JTAG interfaco permesas ke pluraj aparatoj estu konektitaj al ununura interfaco en lekanteta agordo. La celaj aparatoj devas ĉiuj esti funkciigitaj per la sama provizo voltage, kunhavas komunan teran nodon, kaj devas esti ligitaj kiel montrite en la figuro malsupre.

Figuro 4-3. JTAG Lekanteto

Konektante aparatojn en lekanteta ĉeno, la sekvaj punktoj devas esti konsiderataj:

- Ĉiuj aparatoj devas kunhavi komunan teron, konektitan al GND sur la Atmel-ICE-sondilo

- Ĉiuj aparatoj devas funkcii sur la sama celo voltage. VTG sur la Atmel-ICE devas esti konektita al ĉi tiu voltage.

- TMS kaj TCK estas ligitaj paralele; TDI kaj TDO estas ligitaj en serialo

- nSRST sur la Atmel-ICE-sondilo devas esti konektita al RESET sur la aparatoj se iu el la aparatoj en la ĉeno malŝaltas ĝian J.TAG haveno

- "Aparatoj antaŭe" rilatas al la nombro da JTAG aparatoj, kiujn la TDI-signalo devas trapasi en la lekanteto antaŭ ol atingi la celan aparaton. Simile "aparatoj post" estas la nombro da aparatoj, kiujn la signalo devas trapasi post la cela aparato antaŭ ol atingi la Atmel-ICE TDO.

- "Instrukcioj "antaŭ" kaj "post" rilatas al la totala sumo de ĉiuj JTAG aparatoj' instrukcia registro longoj, kiuj estas konektitaj antaŭ kaj post la cela aparato en la lekanteto

- La totala IR-longo (instrukciaj bitoj antaŭ + Atmel-cel-aparato IR-longo + instrukciaj bitoj post) estas limigita al maksimumo de 256 bitoj. La nombro da aparatoj en la ĉeno estas limigita al 15 antaŭ kaj 15 post.

![]() Konsilo:

Konsilo:

Lekante ĉenante ekzample: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Por konektiĝi al la Atmel AVR XMEGA® aparato, la agordoj de lekanteto estas:

- Aparatoj antaŭe: 1

- Aparatoj post: 1

- Instrukcioj antaŭe: 4 (8-bitaj AVR-aparatoj havas 4 IR-bitojn)

- Instrukcioj post: 5 (32-bitaj AVR-aparatoj havas 5 IR-bitojn)

Tabelo 4-2. IR Longoj de Atmel MCUs

| Aparato tipo | IR-longo |

| AVR 8-bita | 4 bitoj |

| AVR 32-bita | 5 bitoj |

| SAM | 4 bitoj |

4.2.3. Konektante al JTAG Celo

La Atmel-ICE estas ekipita per du 50-mil 10-stiftoj JTAG konektiloj. Ambaŭ konektiloj estas rekte elektre konektitaj, sed konformas al du malsamaj pinouts; la AVR JTAG kaplinio kaj la kaplinio ARM Cortex Debug. La konektilo devus esti elektita surbaze de la pinout de la cela tabulo, kaj ne la cela MCU-tipo - ekzample SAM-aparato muntita en AVR STK600-stako devus uzi la AVR-kapon.

La rekomendita pinout por la 10-stifta AVR JTAG konektilo estas montrita en Figuro 4-6.

La rekomendita pinout por la 10-stifta ARM Cortex Debug-konektilo estas montrita en Figuro 4-2.

Rekta konekto al norma 10-pingla 50-mil-kapo

Uzu la 50-mil 10-stiftan platan kablon (inkluzivita en iuj ilaroj) por konekti rekte al tabulo subtenanta ĉi tiun kaplinian tipon. Uzu la AVR-konektilo-havenon sur la Atmel-ICE por kaplinioj kun la AVR-pinout, kaj la SAM-konektila haveno por kaplinioj konformaj al la ARM Cortex Debug-kapa pinouto.

La pinouts por ambaŭ 10-stiftaj konektilhavenoj estas montritaj sube.

Konekto al norma 10-pingla 100-mil-kapo

Uzu norman adaptilon de 50-mil ĝis 100-mil por konekti al 100-mil-kapoj. Adaptilestraro (inkluzivita en kelkaj ilaroj) povas esti uzita por tiu celo, aŭ alternative la JTAGICE3-adaptilo povas esti uzata por AVR-celoj.

![]() Grava:

Grava:

La JTAGICE3 100-mil-adaptilo ne povas esti uzata kun la SAM-konektila haveno, ĉar pingloj 2 kaj 10 (AVR GND) sur la adaptilo estas konektitaj.

Konekto al kutima 100-mila kaplinio

Se via cela tabulo ne havas kongruan 10-pinglan JTAG kaplinio en 50- aŭ 100-mil, vi povas mapi al kutima pinout per la 10-pingla "mini-kalmaro" kablo (inkluzivita en iuj ilaroj), kiu donas aliron al dek individuaj 100-mil ingoj.

Konekto al 20-pingla 100-mil-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al celoj kun 20-pingla 100-mil-kapo.

Tabelo 4-3. Atmel-ICE JTAG Pinglo Priskribo

| Nomo | AVR baborda pinglo | SAM baborda pinglo | Priskribo |

| TCK | 1 | 4 | Testa Horloĝo (horloĝsignalo de la Atmel-ICE en la cela aparaton). |

| TMS | 5 | 2 | Test Mode Select (kontrolsignalo de la Atmel-ICE en la cela aparato). |

| TDI | 9 | 8 | Test Data In (datenoj transdonitaj de la Atmel-ICE en la cela aparaton). |

| TDO | 3 | 6 | Test Data Out (datenoj transdonitaj de la cela aparato en la Atmel-ICE). |

| nTRST | 8 | – | Test Restarigi (laŭvola, nur ĉe iuj AVR-aparatoj). Uzita por restarigi la JTAG TAP-regilo. |

| nSRST | 6 | 10 | Restarigi (laŭvola). Uzita por restarigi la celan aparaton. Konekti ĉi tiun pinglon estas rekomendita, ĉar ĝi permesas al la Atmel-ICE teni la celatan aparaton en restarigita stato, kio povas esti esenca por sencimigi en certaj scenaroj. |

| VTG | 4 | 1 | Celo voltage referenco. La Atmel-ICE samples la celo voltage sur ĉi tiu pinglo por funkciigi la nivelkonvertilojn ĝuste. La Atmel-ICE ĉerpas malpli ol 3mA de ĉi tiu pinglo en debugWIRE-reĝimo kaj malpli ol 1mA en aliaj reĝimoj. |

| GND | 2, 10 | 3, 5, 9 | Tero. Ĉiuj devas esti konektitaj por certigi, ke la Atmel-ICE kaj la cela aparato kunhavas la saman teran referencon. |

4.2.4. SWD-Fizika Interfaco

La ARM SWD-interfaco estas subaro de la JTAG interfaco, uzante TCK kaj TMS-stiftojn. La BRAKO JTAG kaj AVR JTAG konektiloj estas, tamen, ne pin-kongruaj, do dum dizajnado de aplika PCB, kiu uzas SAM-aparaton kun SWD aŭ JTAG interfaco, oni rekomendas uzi la ARM-pinton montritan en la suba figuro. La SAM-konektila haveno sur la Atmel-ICE povas konekti rekte al ĉi tiu pinout.

Figuro 4-4. Rekomendita ARM SWD/JTAG Header Pinout

La Atmel-ICE kapablas elsendi UART-formatan ITM-spuron al la gastiga komputilo. Spuro estas kaptita sur la stifto TRACE/SWO de la 10-stifta kaplinio (JTAG TDO-stifto). Datenoj estas bufritaj interne sur la Atmel-ICE kaj estas senditaj tra la HID-interfaco al la gastiga komputilo. La maksimuma fidinda datumrapideco estas ĉirkaŭ 3MB/s.

4.2.5. Konektante al SWD Celo

La ARM SWD-interfaco estas subaro de la JTAG interfaco, uzante la TCK- kaj TMS-stiftojn, kio signifas, ke kiam li konektas al SWD-aparato, la 10-stifta JTAG konektilo povas teknike esti uzata. La BRAKO JTAG kaj AVR JTAG konektiloj estas, aliflanke, ne pin-kongruaj, tiel ke tio dependas de la aranĝo de la celtabulo en uzo. Kiam vi uzas STK600 aŭ tabulon uzante la AVR JTAG pinout, la AVR-konektila haveno sur la Atmel-ICE devas esti uzata. Konektante al tabulo, kiu uzas la ARM JTAG pinout, la SAM-konektila haveno sur la Atmel-ICE devas esti uzata.

La rekomendita pinout por la 10-pingla Cortex Debug-konektilo estas montrita en Figuro 4-4.

Konekto al 10-pingla 50-mil Cortex-kapo

Uzu la platan kablon (inkluzivita en iuj ilaroj) por konekti al norma 50-mil Cortex-kapo.

Konekto al 10-pingla 100-mil Cortex-aranĝa kaplinio

Uzu la adaptiltabulo (inkluzivita en iuj ilaroj) por konekti al 100-mil Cortex-pinout-kapo.

Konekto al 20-pingla 100-mil SAM-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al 20-pingla 100-mil SAM-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR aŭ SAM-konektila haveno kaj la cela tabulo. Ses konektoj estas bezonataj, kiel priskribite en la suba tabelo.

Tablo 4-4. Atmel-ICE SWD Pin-mapado

| Nomo | AVR baborda pinglo | SAM baborda pinglo | Priskribo |

| SWDC LK | 1 | 4 | Seria Drato Sencimiga Horloĝo. |

| SWDIO | 5 | 2 | Seria Drato Sencimiga Datumoj Enigo/Eligo. |

| SWO | 3 | 6 | Seria Drata Eligo (laŭvola - ne efektivigita sur ĉiuj aparatoj). |

| nSRST | 6 | 10 | Restarigi. |

| VTG | 4 | 1 | Celo voltage referenco. |

| GND | 2, 10 | 3, 5, 9 | Tero. |

4.2.6 Specialaj Konsideroj

ERASE pinglo

Kelkaj SAM-aparatoj inkluzivas ERASE-stifton, kiu estas asertita por plenumi kompletan peceton-viŝadon kaj malŝlosi aparatojn sur kiuj la sekurecbito estas metita. Ĉi tiu funkcio estas kunligita al la aparato mem same kiel al la fulmregilo kaj ne estas parto de la ARM-kerno.

La ERASE-pinglo NE estas parto de iu ajn sencimiga kaplinio, kaj la Atmel-ICE do ne povas aserti ĉi tiun signalon por malŝlosi aparaton. En tiaj kazoj la uzanto devus plenumi la forviŝon permane antaŭ ol komenci sencimigan sesion.

Fizikaj interfacoj JTAG interfaco

La RESET-linio ĉiam devas esti konektita por ke la Atmel-ICE povu ebligi la JTAG interfaco.

SWD-interfaco

La RESET-linio ĉiam devas esti konektita por ke la Atmel-ICE povu ebligi la SWD-interfacon.

4.3 AVR UC3-Aparatoj kun JTAG/aDrato

Ĉiuj AVR UC3-aparatoj havas la JTAG interfaco por programado kaj senararigado. Krome, kelkaj AVR UC3-aparatoj havas la aWire-interfacon kun identa funkcieco uzante ununuran draton. Kontrolu la aparatan datenfolion por subtenataj interfacoj de tiu aparato

4.3.1 Atmel AVR UC3 Sur-blata Sencimiga Sistemo

La Atmel AVR UC3 OCD-sistemo estas desegnita laŭ la Nexus 2.0 normo (IEEE-ISTO 5001™-2003), kiu estas tre fleksebla kaj potenca malferma sur-blata sencimiga normo por 32-bitaj mikroregiloj. Ĝi subtenas la sekvajn funkciojn:

- Nexus konforma sencimsolvo

- OCD subtenas ajnan CPU-rapidecon

- Ses programaj nombriloj de aparataro rompopunktoj

- Du datumoj rompopunktoj

- Rompopunktoj povas esti agorditaj kiel gvatopunktoj

- Aparataj rompopunktoj povas esti kombinitaj por doni paŭzon sur intervaloj

- Senlima nombro da uzantprogramaj rompopunktoj (uzante BREAK)

- Realtempa programo-nombrilo branĉspurado, datumspuro, procezspuro (subtenata nur de erarserĉiloj kun paralela spurkapta haveno)

Por pliaj informoj pri la AVR UC3 OCD-sistemo, konsultu la AVR32UC Teknikajn Referencajn Manlibrojn, situantajn sur www.atmel.com/uc3.

4.3.2. JTAG Fizika Interfaco

La JTAG interfaco konsistas el 4-drata Test Access Port (TAP) regilo kiu estas konforma al la IEEE® 1149.1 normo. La IEEE-normo estis evoluigita por disponigi industrinorman manieron efike testi cirkvitplatan konekteblecon (Boundary Scan). Atmel AVR kaj SAM-aparatoj etendis ĉi tiun funkcion por inkluzivi plenan Programadon kaj Sur-blatan Sencimigan subtenon.

Figuro 4-5. JTAG Interfacaj Bazoj

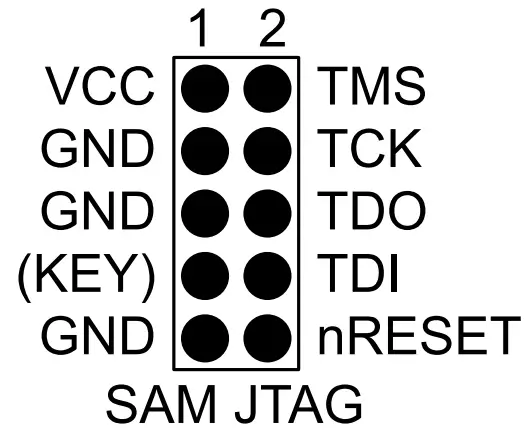

4.3.2.1 AVR JTAG Pinout

Dum desegnado de aplikaĵo PCB, kiu inkluzivas Atmel AVR kun la JTAG interfaco, oni rekomendas uzi la pinout kiel montrita en la figuro malsupre. Ambaŭ 100-mil kaj 50-mil variantoj de ĉi tiu pinout estas subtenataj, depende de la kablado kaj adaptiloj inkluzivitaj kun la aparta ilaro.

Figuro 4-6. AVR JTAG Header Pinout

Tablo 4-5. AVR JTAG Pinglo Priskribo

| Nomo | Pinglo |

Priskribo |

| TCK | 1 | Testa Horloĝo (horloĝsignalo de la Atmel-ICE en la cela aparaton). |

| TMS | 5 | Test Mode Select (kontrolsignalo de la Atmel-ICE en la cela aparato). |

| TDI | 9 | Test Data In (datenoj transdonitaj de la Atmel-ICE en la cela aparaton). |

| TDO | 3 | Test Data Out (datenoj transdonitaj de la cela aparato en la Atmel-ICE). |

| nTRST | 8 | Test Restarigi (laŭvola, nur ĉe iuj AVR-aparatoj). Uzita por restarigi la JTAG TAP-regilo. |

| nSRST | 6 | Restarigi (laŭvola). Uzita por restarigi la celan aparaton. Konekti ĉi tiun pinglon estas rekomendita, ĉar ĝi permesas al la Atmel-ICE teni la celatan aparaton en restarigita stato, kio povas esti esenca por sencimigi en certaj scenaroj. |

| VTG | 4 | Celo voltage referenco. La Atmel-ICE samples la celo voltage sur ĉi tiu pinglo por funkciigi la nivelkonvertilojn ĝuste. La Atmel-ICE ĉerpas malpli ol 3mA de ĉi tiu pinglo en debugWIRE-reĝimo kaj malpli ol 1mA en aliaj reĝimoj. |

| GND | 2, 10 | Tero. Ambaŭ devas esti konektitaj por certigi, ke la Atmel-ICE kaj la cela aparato kunhavas la saman teran referencon. |

![]() Konsilo: Memoru inkluzivi malkunligan kondensilon inter pinglo 4 kaj GND.

Konsilo: Memoru inkluzivi malkunligan kondensilon inter pinglo 4 kaj GND.

4.3.2.2 JTAG Lekanto Ĉenado

La JTAG interfaco permesas ke pluraj aparatoj estu konektitaj al ununura interfaco en lekanteta agordo. La celaj aparatoj devas ĉiuj esti funkciigitaj per la sama provizo voltage, kunhavas komunan teran nodon, kaj devas esti ligitaj kiel montrite en la figuro malsupre.

Figuro 4-7. JTAG Lekanteto

Konektante aparatojn en lekanteta ĉeno, la sekvaj punktoj devas esti konsiderataj:

- Ĉiuj aparatoj devas kunhavi komunan teron, konektitan al GND sur la Atmel-ICE-sondilo

- Ĉiuj aparatoj devas funkcii sur la sama celo voltage. VTG sur la Atmel-ICE devas esti konektita al ĉi tiu voltage.

- TMS kaj TCK estas ligitaj paralele; TDI kaj TDO estas ligitaj en seria ĉeno.

- nSRST sur la Atmel-ICE-sondilo devas esti konektita al RESET sur la aparatoj se iu el la aparatoj en la ĉeno malŝaltas ĝian J.TAG haveno

- "Aparatoj antaŭe" rilatas al la nombro da JTAG aparatoj, kiujn la TDI-signalo devas trapasi en la lekanteto antaŭ ol atingi la celan aparaton. Simile "aparatoj post" estas la nombro da aparatoj, kiujn la signalo devas trapasi post la cela aparato antaŭ ol atingi la Atmel-ICE TDO.

- "Instrukcioj "antaŭ" kaj "post" rilatas al la totala sumo de ĉiuj JTAG aparatoj' instrukcia registro longoj, kiuj estas konektitaj antaŭ kaj post la cela aparato en la lekanteto

- La totala IR-longo (instrukciaj bitoj antaŭ + Atmel-cel-aparato IR-longo + instrukciaj bitoj post) estas limigita al maksimumo de 256 bitoj. La nombro da aparatoj en la ĉeno estas limigita al 15 antaŭ kaj 15 post.

Konsilo:

Lekante ĉenante ekzample: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Por konektiĝi al la Atmel AVR XMEGA® aparato, la agordoj de lekanteto estas:

- Aparatoj antaŭe: 1

- Aparatoj post: 1

- Instrukcioj antaŭe: 4 (8-bitaj AVR-aparatoj havas 4 IR-bitojn)

- Instrukcioj post: 5 (32-bitaj AVR-aparatoj havas 5 IR-bitojn)

Tabelo 4-6. IR Longoj de Atmel MCUS

| Aparato tipo | IR-longo |

| AVR 8-bita | 4 bitoj |

| AVR 32-bita | 5 bitoj |

| SAM | 4 bitoj |

4.3.3.Konekti al JTAG Celo

La Atmel-ICE estas ekipita per du 50-mil 10-stiftoj JTAG konektiloj. Ambaŭ konektiloj estas rekte elektre konektitaj, sed konformas al du malsamaj pinouts; la AVR JTAG kaplinio kaj la kaplinio ARM Cortex Debug. La konektilo devus esti elektita surbaze de la pinout de la cela tabulo, kaj ne la cela MCU-tipo - ekzample SAM-aparato muntita en AVR STK600-stako devus uzi la AVR-kapon.

La rekomendita pinout por la 10-stifta AVR JTAG konektilo estas montrita en Figuro 4-6.

La rekomendita pinout por la 10-stifta ARM Cortex Debug-konektilo estas montrita en Figuro 4-2.

Rekta konekto al norma 10-pingla 50-mil-kapo

Uzu la 50-mil 10-stiftan platan kablon (inkluzivita en iuj ilaroj) por konekti rekte al tabulo subtenanta ĉi tiun kaplinian tipon. Uzu la AVR-konektilo-havenon sur la Atmel-ICE por kaplinioj kun la AVR-pinout, kaj la SAM-konektila haveno por kaplinioj konformaj al la ARM Cortex Debug-kapa pinouto.

La pinouts por ambaŭ 10-stiftaj konektilhavenoj estas montritaj sube.

Konekto al norma 10-pingla 100-mil-kapo

Uzu norman adaptilon de 50-mil ĝis 100-mil por konekti al 100-mil-kapoj. Adaptilestraro (inkluzivita en kelkaj ilaroj) povas esti uzita por tiu celo, aŭ alternative la JTAGICE3-adaptilo povas esti uzata por AVR-celoj.

![]() Grava:

Grava:

La JTAGICE3 100-mil-adaptilo ne povas esti uzata kun la SAM-konektila haveno, ĉar pingloj 2 kaj 10 (AVR GND) sur la adaptilo estas konektitaj.

Konekto al kutima 100-mila kaplinio

Se via cela tabulo ne havas kongruan 10-pinglan JTAG kaplinio en 50- aŭ 100-mil, vi povas mapi al kutima pinout per la 10-pingla "mini-kalmaro" kablo (inkluzivita en iuj ilaroj), kiu donas aliron al dek individuaj 100-mil ingoj.

Konekto al 20-pingla 100-mil-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al celoj kun 20-pingla 100-mil-kapo.

Tabelo 4-7. Atmel-ICE JTAG Pinglo Priskribo

|

Nomo |

AVR haveno pinglo | SAM-havenpinglo |

Priskribo |

| TCK | 1 | 4 | Testa Horloĝo (horloĝsignalo de la Atmel-ICE en la cela aparaton). |

| TMS | 5 | 2 | Test Mode Select (kontrolsignalo de la Atmel-ICE en la cela aparato). |

| TDI | 9 | 8 | Test Data In (datenoj transdonitaj de la Atmel-ICE en la cela aparaton). |

| TDO | 3 | 6 | Test Data Out (datenoj transdonitaj de la cela aparato en la Atmel-ICE). |

| nTRST | 8 | – | Test Restarigi (laŭvola, nur ĉe iuj AVR-aparatoj). Uzita por restarigi la JTAG TAP-regilo. |

| nSRST | 6 | 10 | Restarigi (laŭvola). Uzita por restarigi la celan aparaton. Konekti ĉi tiun pinglon estas rekomendita, ĉar ĝi permesas al la Atmel-ICE teni la celatan aparaton en restarigita stato, kio povas esti esenca por sencimigi en certaj scenaroj. |

| VTG | 4 | 1 | Celo voltage referenco. La Atmel-ICE samples la celo voltage sur ĉi tiu pinglo por funkciigi la nivelkonvertilojn ĝuste. La Atmel-ICE ĉerpas malpli ol 3mA de ĉi tiu pinglo en debugWIRE-reĝimo kaj malpli ol 1mA en aliaj reĝimoj. |

| GND | 2, 10 | 3, 5, 9 | Tero. Ĉiuj devas esti konektitaj por certigi, ke la Atmel-ICE kaj la cela aparato kunhavas la saman teran referencon. |

4.3.4 aDrata Fizika Interfaco

La aWire-interfaco uzas la RESET-draton de la AVR-aparato por permesi programajn kaj senararajn funkciojn. Speciala ebliga sekvenco estas elsendita de la Atmel-ICE, kiu malŝaltas la defaŭltan RESET-funkciecon de la pinglo. Dum desegnado de aplika PCB, kiu inkluzivas Atmel AVR kun la aWire-interfaco, oni rekomendas uzi la pinout kiel montrite en Figuro 4. —8. Ambaŭ 100-mil kaj 50-mil variantoj de ĉi tiu pinout estas subtenataj, depende de la kablado kaj adaptiloj inkluzivitaj kun la aparta ilaro.

Figuro 4-8. aWire Header Pinout

![]() Konsilo:

Konsilo:

Ĉar aWire estas duon-dupleksa interfaco, tirrezisto sur la RESET-linio en la ordo de 47kΩ estas rekomendita por eviti malveran start-bitan detekton kiam ŝanĝante direkton.

La aWire-interfaco povas esti uzata kiel interfaco de programado kaj senararigado. Ĉiuj ecoj de la OCD-sistemo haveblaj per la 10-stifta JTAG interfaco ankaŭ alireblas per aWire.

4.3.5 Konekti al aWire Celo

La aWire-interfaco postulas nur unu datumlinion aldone al VCC kaj GND. Sur la celo ĉi tiu linio estas la linio nRESET, kvankam la erarserĉilo uzas la JTAG TDO-linio kiel la datumlinio.

La rekomendita pinout por la 6-pingla aWire-konektilo estas montrita en Figuro 4-8.

Konekto al 6-pingla 100-mil aWire-kapo

Uzu la 6-pinglan 100-milan kranon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mil aWire-kapo.

Konekto al 6-pingla 50-mil aWire-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al norma 50-mil aWire-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Tri konektoj estas bezonataj, kiel priskribite en la suba tabelo.

Tabelo 4-8. Atmel-ICE aWire Pin Mapping

| Atmel-ICE AVR havenpingloj | Celstiftoj | Mini-kalmaro pinglo |

aDrato pinout |

| Pinglo 1 (TCK) | 1 | ||

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | DATUMO | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 | ||

| Pinglo 6 (nSRST) | 6 | ||

| Pinglo 7 (Ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | 9 | ||

| Pinglo 10 (GND) | 0 |

4.3.6. Specialaj Konsideroj

JTAG interfaco

Sur iuj Atmel AVR UC3-aparatoj la JTAG haveno ne estas ebligita defaŭlte. Kiam vi uzas ĉi tiujn aparatojn, estas esence konekti la RESET-linion por ke la Atmel-ICE povu ebligi la JTAG interfaco.

aWire-interfaco

La baudrapideco de aWire-komunikadoj dependas de la frekvenco de la sistema horloĝo, ĉar datenoj devas esti sinkronigitaj inter tiuj du domajnoj. La Atmel-ICE aŭtomate detektos, ke la sistema horloĝo estas malaltigita, kaj re-kalibros ĝian baudrapidecon laŭe. La aŭtomata kalibrado funkcias nur ĝis sistema horloĝfrekvenco de 8kHz. Ŝanĝi al pli malalta sistema horloĝo dum sencimsesio povas kaŭzi kontakton kun la celo esti perdita.

Se necese, la aWire-baŭdrapideco povas esti limigita per agordo de la aWire-horloĝparametro. Aŭtomata detekto ankoraŭ funkcios, sed plafona valoro estos trudita al la rezultoj.

Ajna stabiliga kondensilo ligita al la RESET-stifto devas esti malkonektita kiam vi uzas aWire ĉar ĝi malhelpos ĝustan funkciadon de la interfaco. Malforta ekstera tiriĝo (10kΩ aŭ pli alta) sur ĉi tiu linio estas rekomendita.

Malŝaltu dormreĝimon

Iuj AVR UC3-aparatoj havas internan reguligilon, kiu povas esti uzata en 3.3V-provizoreĝimo kun 1.8V reguligitaj I/O-linioj. Ĉi tio signifas, ke la interna reguligisto funkciigas kaj la kernon kaj la plej grandan parton de la I/O. Nur Atmel AVR ONE! elĉimilo subtenas sencimigon dum uzado de dormreĝimoj kie ĉi tiu reguligilo estas malŝaltita.

4.3.7. EVTI / EVTO Uzado

La stiftoj EVTI kaj EVTO ne estas alireblaj sur la Atmel-ICE. Tamen, ili ankoraŭ povas esti uzataj kune kun aliaj eksteraj ekipaĵoj.

EVTI povas esti uzata por la sekvaj celoj:

- La celo povas esti devigita ĉesigi ekzekuton en respondo al ekstera okazaĵo. Se la Event In Control (EIC) bitoj en la Dc-registro estas skribitaj al 0b01, alt-al-malalta transiro sur la EVTI-stifto generos rompopunktokondiĉon. EVTI devas resti malalta por unu CPU-horloĝciklo por garantii ke rompopunkto estas La Ekstera Breakpoint-bito (EXB) en DS estas metita kiam tio okazas.

- Generante spurajn sinkronigajn mesaĝojn. Ne uzata de la Atmel-ICE.

EVTO povas esti uzata por la sekvaj celoj:

- Indikante ke la CPU eniris sencimigon Agordi la EOS-bitojn en DC al 0b01 igas la EVTO-stifton esti tirita malalte por unu CPU-horloĝciklo kiam la cela aparato eniras sencimigan reĝimon. Ĉi tiu signalo povas esti uzata kiel ellasilfonto por ekstera osciloskopo.

- Indikante ke la CPU atingis rompopunkton aŭ observpunkton. Metante la EOC-biton en ekvivalentan Breakpoint/Watchpoint Control Register, la rompopunkto aŭ gvatpunkto statuso estas indikita sur la EVTO-stifto. La EOS-bitoj en DC devas esti agordita al 0xb10 por ebligi ĉi tiun funkcion. La EVTO-stifto tiam povas esti ligita al ekstera osciloskopo por ekzameni gardopunkton

- Generante spurajn tempajn signalojn. Ne uzata de la Atmel-ICE.

4.4 Aparatoj tinyAVR, megaAVR kaj XMEGA

AVR-aparatoj havas diversajn programajn kaj senararajn interfacojn. Kontrolu la aparatan datenfolion por subtenataj interfacoj de tiu aparato.

- Iu eta AVR® aparatoj havas TPI TPI povas esti uzata por programado de la aparato nur, kaj ĉi tiuj aparatoj tute ne havas sur-blatan sencimigan kapablon.

- Kelkaj tinyAVR-aparatoj kaj kelkaj megaAVR-aparatoj havas la debugWIRE-interfacon, kiu konektas al sur-blata sencimiga sistemo konata kiel tinyOCD. Ĉiuj aparatoj kun debugWIRE ankaŭ havas la SPI-interfacon por en-sistemo

- Iuj megaAVR-aparatoj havas JTAG interfaco por programado kaj senararigado, kun sur-blata sencimiga sistemo ankaŭ konata kiel Ĉiuj aparatoj kun JTAG ankaŭ prezentas la SPI-interfacon kiel alternativan interfacon por en-sistema programado.

- Ĉiuj AVR XMEGA-aparatoj havas la PDI-interfacon por programado kaj Kelkaj AVR-XMEGA-aparatoj ankaŭ havas J.TAG interfaco kun identa funkcieco.

- Novaj tinyAVR-aparatoj havas UPDI-interfacon, kiu estas uzata por programado kaj senararigado

Tabelo 4-9. Resumo pri Programado kaj Sencimiga Interfacoj

|

|

UPDI | TPI | SPI | debugWIR E | JTAG | PDI | aDrato |

SWD |

| etaAVR | Novaj aparatoj | Iuj aparatoj | Iuj aparatoj | Iuj aparatoj | ||||

| megaAV R | Ĉiuj aparatoj | Iuj aparatoj | Iuj aparatoj | |||||

| AVR XMEGA | Iuj aparatoj | Ĉiuj aparatoj | ||||||

| AVR UC | Ĉiuj aparatoj | Iuj aparatoj | ||||||

| SAM | Iuj aparatoj | Ĉiuj aparatoj |

4.4.1. JTAG Fizika Interfaco

La JTAG interfaco konsistas el 4-drata Test Access Port (TAP) regilo kiu estas konforma al la IEEE® 1149.1 normo. La IEEE-normo estis evoluigita por disponigi industrinorman manieron efike testi cirkvitplatan konekteblecon (Boundary Scan). Atmel AVR kaj SAM-aparatoj etendis ĉi tiun funkcion por inkluzivi plenan Programadon kaj Sur-blatan Sencimigan subtenon.

Figuro 4-9. JTAG Interfacaj Bazoj 4.4.2. Konektante al JTAG Celo

4.4.2. Konektante al JTAG Celo

La Atmel-ICE estas ekipita per du 50-mil 10-stiftoj JTAG konektiloj. Ambaŭ konektiloj estas rekte elektre konektitaj, sed konformas al du malsamaj pinouts; la AVR JTAG kaplinio kaj la kaplinio ARM Cortex Debug. La konektilo devus esti elektita surbaze de la pinout de la cela tabulo, kaj ne la cela MCU-tipo - ekzample SAM-aparato muntita en AVR STK600-stako devus uzi la AVR-kapon.

La rekomendita pinout por la 10-stifta AVR JTAG konektilo estas montrita en Figuro 4-6.

La rekomendita pinout por la 10-stifta ARM Cortex Debug-konektilo estas montrita en Figuro 4-2.

Rekta konekto al norma 10-pingla 50-mil-kapo

Uzu la 50-mil 10-stiftan platan kablon (inkluzivita en iuj ilaroj) por konekti rekte al tabulo subtenanta ĉi tiun kaplinian tipon. Uzu la AVR-konektilo-havenon sur la Atmel-ICE por kaplinioj kun la AVR-pinout, kaj la SAM-konektila haveno por kaplinioj konformaj al la ARM Cortex Debug-kapa pinouto.

La pinouts por ambaŭ 10-stiftaj konektilhavenoj estas montritaj sube.

Konekto al norma 10-pingla 100-mil-kapo

Uzu norman adaptilon de 50-mil ĝis 100-mil por konekti al 100-mil-kapoj. Adaptilestraro (inkluzivita en kelkaj ilaroj) povas esti uzita por tiu celo, aŭ alternative la JTAGICE3-adaptilo povas esti uzata por AVR-celoj.

![]() Grava:

Grava:

La JTAGICE3 100-mil-adaptilo ne povas esti uzata kun la SAM-konektila haveno, ĉar pingloj 2 kaj 10 (AVR GND) sur la adaptilo estas konektitaj.

Konekto al kutima 100-mila kaplinio

Se via cela tabulo ne havas kongruan 10-pinglan JTAG kaplinio en 50- aŭ 100-mil, vi povas mapi al kutima pinout per la 10-pingla "mini-kalmaro" kablo (inkluzivita en iuj ilaroj), kiu donas aliron al dek individuaj 100-mil ingoj.

Konekto al 20-pingla 100-mil-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al celoj kun 20-pingla 100-mil-kapo.

Tabelo 4-10. Atmel-ICE JTAG Pinglo Priskribo

| Nomo | AVR baborda pinglo | SAM baborda pinglo | Priskribo |

| TCK | 1 | 4 | Testa Horloĝo (horloĝsignalo de la Atmel-ICE en la cela aparaton). |

| TMS | 5 | 2 | Test Mode Select (kontrolsignalo de la Atmel-ICE en la cela aparato). |

| TDI | 9 | 8 | Test Data In (datenoj transdonitaj de la Atmel-ICE en la cela aparaton). |

| TDO | 3 | 6 | Test Data Out (datenoj transdonitaj de la cela aparato en la Atmel-ICE). |

| nTRST | 8 | – | Test Restarigi (laŭvola, nur ĉe iuj AVR-aparatoj). Uzita por restarigi la JTAG TAP-regilo. |

| nSRST | 6 | 10 | Restarigi (laŭvola). Uzita por restarigi la celan aparaton. Konekti ĉi tiun pinglon estas rekomendita, ĉar ĝi permesas al la Atmel-ICE teni la celatan aparaton en restarigita stato, kio povas esti esenca por sencimigi en certaj scenaroj. |

| VTG | 4 | 1 | Celo voltage referenco. La Atmel-ICE samples la celo voltage sur ĉi tiu pinglo por funkciigi la nivelkonvertilojn ĝuste. La Atmel-ICE ĉerpas malpli ol 3mA de ĉi tiu pinglo en debugWIRE-reĝimo kaj malpli ol 1mA en aliaj reĝimoj. |

| GND | 2, 10 | 3, 5, 9 | Tero. Ĉiuj devas esti konektitaj por certigi, ke la Atmel-ICE kaj la cela aparato kunhavas la saman teran referencon. |

4.4.3.SPI-Fizika Interfaco

En-Sistema Programado uzas la internan SPI (Serial Peripheral Interface) de la celo Atmel AVR por elŝuti kodon en la fulmajn kaj EEPROM-memorojn. Ĝi ne estas sencimiga interfaco. Dum desegnado de aplikaĵo PCB, kiu inkluzivas AVR kun la SPI-interfaco, la pinout kiel montrita en la figuro malsupre devus esti uzata.

Figuro 4-10. SPI Header Pinout 4.4.4. Konektante al SPI-Celo

4.4.4. Konektante al SPI-Celo

La rekomendita pinout por la 6-pingla SPI-konektilo estas montrita en Figuro 4-10.

Konekto al 6-pingla 100-mil SPI-kapo

Uzu la 6-pinglan 100-mil-frapon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mil SPI-kapo.

Konekto al 6-pingla 50-mil SPI-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al norma 50-mil SPI-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Ses konektoj estas bezonataj, kiel priskribite en la suba tabelo.

![]() Grava:

Grava:

La SPI-interfaco estas efike malfunkciigita kiam la debugWIRE ebliga fuzeo (DWEN) estas programita, eĉ se SPIEN-fuzeo ankaŭ estas programita. Por reebligi la SPI-interfacon, la komando 'malŝalti debugWIRE' devas esti eligita dum en debugWIRE-sencimiga sesio. Malebligi debugWIRE tiamaniere postulas ke la SPIEN-fuzeo jam estas programita. Se Atmel Studio malsukcesas malŝalti debugWIRE, estas verŝajne ĉar la SPIEN-fuzeo NE estas programita. Se ĉi tio estas la kazo, necesas uzi alt-voltage programa interfaco por programi la SPIEN-fuzeon.

![]() Informoj:

Informoj:

La SPI-interfaco ofte estas referita kiel "ISP", ĉar ĝi estis la unua In System Programming-interfaco sur Atmel AVR-produktoj. Aliaj interfacoj nun estas haveblaj por En System Programming.

Tabelo 4-11. Atmel-ICE SPI Pint-Mapado

| Atmel-ICE AVR havenpingloj | Celstiftoj | Mini-kalmaro pinglo |

SPI pinout |

| Pinglo 1 (TCK) | SCK | 1 | 3 |

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | MISO | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 | ||

| Pinglo 6 (nSRST) | /RESETIGI | 6 | 5 |

| Pinglo 7 (ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | MOSI | 9 | 4 |

| Pinglo 10 (GND) | 0 |

4.4.5. PDI

La Programo kaj Sencimiga Interfaco (PDI) estas Atmel proprieta interfaco por ekstera programado kaj sur-blata senararigado de aparato. PDI Physical estas 2-stifta interfaco disponiganta dudirektan duondupleksan sinkronan komunikadon kun la cela aparato.

Dum desegnado de aplikaĵo PCB, kiu inkluzivas Atmel AVR kun la PDI-interfaco, la pinout montrita en la figuro malsupre devus esti uzata. Unu el la 6-pinglaj adaptiloj provizitaj per la ilaro Atmel-ICE tiam povas esti uzata por konekti la sondilon Atmel-ICE al la aplika PCB.

Figuro 4-11. PDI Header Pinout 4.4.6.Konekti al PDI-Celo

4.4.6.Konekti al PDI-Celo

La rekomendita pinout por la 6-pingla PDI-konektilo estas montrita en Figuro 4-11.

Konekto al 6-pingla 100-mil PDI-kapo

Uzu la 6-pintan 100-mil-frapon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mil PDI-kapo.

Konekto al 6-pingla 50-mil PDI-kapo

Uzu la adaptiltabulo (inkluzivita en iuj ilaroj) por konekti al norma 50-mil PDI-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Kvar konektoj estas bezonataj, kiel priskribite en la suba tabelo.

![]() Grava:

Grava:

La pinout necesa estas diferenca de la JTAGICE mkII JTAG sondilo, kie PDI_DATA estas konektita al pinglo 9. La Atmel-ICE estas kongrua kun la pinout uzata de la Atmel-ICE, JTAGICE3, AVR UNU!, kaj AVR Dragon™ produktoj.

Tabelo 4-12. Atmel-ICE PDI Pin-mapado

|

Atmel-ICE AVR havenstifto |

Celstiftoj | Mini-kalmaro pinglo |

Atmel STK600 PDI pinout |

| Pinglo 1 (TCK) | 1 | ||

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | PDI_DATA | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 | ||

| Pinglo 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pinglo 7 (ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | 9 | ||

| Pinglo 10 (GND) | 0 |

4.4.7. UPDI-Fizika Interfaco

La Unuigita Programo kaj Sencimiga Interfaco (UPDI) estas proprieta interfaco de Atmel por ekstera programado kaj sur-blata senararigado de aparato. Ĝi estas posteulo de la PDI-2-drata fizika interfaco, kiu troviĝas sur ĉiuj AVR XMEGA-aparatoj. UPDI estas unu-drata interfaco disponiganta dudirektan duondupleksan nesinkronan komunikadon per la cela aparato por celoj de programado kaj senararigado.

Dum desegnado de aplikaĵo PCB, kiu inkluzivas Atmel AVR kun la UPDI-interfaco, la pinout montrita sube estu uzata. Unu el la 6-pinglaj adaptiloj provizitaj per la ilaro Atmel-ICE tiam povas esti uzata por konekti la sondilon Atmel-ICE al la aplika PCB.

Figuro 4-12. UPDI Header Pinout 4.4.7.1 UPDI kaj /RESET

4.4.7.1 UPDI kaj /RESET

La UPDI-unu-drata interfaco povas esti dediĉita pinglo aŭ komuna pinglo, depende de la cela AVR-aparato. Konsultu la datumfolion de la aparato por pliaj informoj.

Kiam la UPDI-interfaco estas sur komuna pinglo, la pinglo povas esti agordita por esti aŭ UPDI, /RESET, aŭ GPIO metante la RSTPINCFG[1:0] fuzeojn.

La RSTPINCFG[1:0] fuzeoj havas la sekvajn agordojn, kiel priskribite en la datenfolio. La praktikaj implicoj de ĉiu elekto estas donitaj ĉi tie.

Tablo 4-13. RSTPINCFG[1:0] Fuze Configuration

| RSTPINCFG[1:0] | Agordo |

Uzado |

| 00 | GPIO | Ĝenerala celo I/O pinglo. Por aliri UPDI, 12V pulso devas esti aplikita al ĉi tiu pinglo. Neniu ekstera rekomencigita fonto disponeblas. |

| 01 | UPDI | Dediĉita programado kaj sencimiga pinglo. Neniu ekstera rekomencigita fonto disponeblas. |

| 10 | Restarigi | Restarigi signalenigon. Por aliri UPDI, 12V pulso devas esti aplikita al ĉi tiu pinglo. |

| 11 | Rezervita | NA |

Notu: Pli malnovaj AVR-aparatoj havas programan interfacon, konatan kiel "High-Voltage Programado” (kaj seriaj kaj paralelaj variantoj ekzistas.) Ĝenerale ĉi tiu interfaco postulas 12V esti aplikata al la /RESET pinglo dum la daŭro de la programa sesio. La UPDI-interfaco estas tute malsama interfaco. La UPDI-stifto estas ĉefe programa kaj senarariga stifto, kiu povas esti kunfandita por havi alternativan funkcion (/RESET aŭ GPIO). Se la alternativa funkcio estas elektita tiam 12V pulso estas postulata sur tiu pinglo por reaktivigi la UPDI-funkciecon.

Notu: Se dezajno postulas la dividon de la UPDI-signalo pro pinglolimoj, paŝoj devas esti prenitaj por certigi ke la aparato povas esti programita. Por certigi, ke la UPDI-signalo povas funkcii ĝuste, kaj ankaŭ por eviti damaĝon al eksteraj komponantoj de la 12V-pulso, oni rekomendas malkonekti iujn ajn komponantojn sur ĉi tiu pinglo kiam oni provas sencimi aŭ programi la aparaton. Ĉi tio povas esti farita per 0Ω-rezistilo, kiu estas muntita defaŭlte kaj forigita aŭ anstataŭigita per pinglokapo dum senararigado. Ĉi tiu agordo efike signifas, ke programado devas esti farita antaŭ ol muntado de la aparato.

![]() Grava: La Atmel-ICE ne subtenas 12V sur la UPDI-linio. Alivorte, se la UPDI-pinglo estis agordita kiel GPIO aŭ RESET la Atmel-ICE ne povos ebligi la UPDI-interfacon.

Grava: La Atmel-ICE ne subtenas 12V sur la UPDI-linio. Alivorte, se la UPDI-pinglo estis agordita kiel GPIO aŭ RESET la Atmel-ICE ne povos ebligi la UPDI-interfacon.

4.4.8.Konekti al UPDI Celo

La rekomendita pinout por la 6-pingla UPDI-konektilo estas montrita en Figuro 4-12.

Konekto al 6-pingla 100-mil UPDI-kapo

Uzu la 6-pinglan 100-milan kranon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mila UPDI-kapo.

Konekto al 6-pingla 50-mil UPDI-kapo

Uzu la adaptiltabulo (inkluzivita en iuj ilaroj) por konekti al norma 50-mil UPDI-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Tri konektoj estas bezonataj, kiel priskribite en la suba tabelo.

Tabelo 4-14. Atmel-ICE UPDI Pin-Mapado

| Atmel-ICE AVR havenstifto | Celstiftoj | Mini-kalmaro pinglo |

Atmel STK600 UPDI pinout |

| Pinglo 1 (TCK) | 1 | ||

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | UPDI_DATA | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 | ||

| Pinglo 6 (nSRST) | [/RESETigi sencon] | 6 | 5 |

| Pinglo 7 (Ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | 9 | ||

| Pinglo 10 (GND) | 0 |

4.4.9 TPI-Fizika Interfaco

TPI estas nur programa interfaco por iuj AVR ATtiny-aparatoj. Ĝi ne estas sencimiga interfaco, kaj ĉi tiuj aparatoj ne havas OCD-kapablon. Dum desegnado de aplika PCB kiu inkluzivas AVR kun la TPI-interfaco, la pinout montrita en la figuro malsupre devus esti uzata.

Figuro 4-13. TPI Header Pinout 4.4.10.Konekti al TPI-Celo

4.4.10.Konekti al TPI-Celo

La rekomendita pinout por la 6-pingla TPI-konektilo estas montrita en Figuro 4-13.

Konekto al 6-pingla 100-mil TPI-kapo

Uzu la 6-pinglan 100-milan kranon sur la plata kablo (inkluzivita en iuj ilaroj) por konekti al norma 100-mil TPI-kapo.

Konekto al 6-pingla 50-mil TPI-kapo

Uzu la adaptilon (inkluzivita en iuj ilaroj) por konekti al norma 50-mil TPI-kapo.

Konekto al kutima 100-mila kaplinio

La 10-pingla kablo mini-kalmaro devus esti uzata por konekti inter la Atmel-ICE AVR-konektila haveno kaj la cela tabulo. Ses konektoj estas bezonataj, kiel priskribite en la suba tabelo.

Tabelo 4-15. Atmel-ICE TPI Pinglo-Mapado

| Atmel-ICE AVR havenpingloj | Celstiftoj | Mini-kalmaro pinglo |

TPI pinout |

| Pinglo 1 (TCK) | HORLOĜO | 1 | 3 |

| Pinglo 2 (GND) | GND | 2 | 6 |

| Pinglo 3 (TDO) | DATUMO | 3 | 1 |

| Pinglo 4 (VTG) | VTG | 4 | 2 |

| Pinglo 5 (TMS) | 5 | ||

| Pinglo 6 (nSRST) | /RESETIGI | 6 | 5 |

| Pinglo 7 (ne konektita) | 7 | ||

| Pinglo 8 (nTRST) | 8 | ||

| Stifto 9 (TDI) | 9 | ||

| Pinglo 10 (GND) | 0 |

4.4.11. Altnivela Sencimigo (AVR JTAG /debugWIRE-aparatoj)

I/O Ekstercentraloj

La plej multaj I/O-ekscentraloj daŭros funkcii kvankam la programekzekuto estas ĉesigita per rompopunkto. Ekzample: Se rompopunkto estas atingita dum transdono de UART, la transdono estos kompletigita kaj respondaj bitoj starigitaj. La flago TXC (transsendo kompleta) estos metita kaj disponebla sur la sekva ununura paŝo de la kodo kvankam ĝi normale okazus poste en reala aparato.

Ĉiuj I/O-moduloj daŭre funkcios en haltigita reĝimo kun la sekvaj du esceptoj:

- Temporizilo/Nombriloj (agordeblaj per la programara frontfino)

- Watchdog Timer (ĉiam haltigita por malhelpi rekomencigojn dum senararigado)

Unuopa Paŝa I/O-aliro

Ĉar la I/O daŭre funkcias en haltigita reĝimo, oni devas zorgi por eviti iujn tempoproblemojn. Por ekzample, la kodo:

Dum funkciado de ĉi tiu kodo normale, la TEMP-registro ne relegus 0xAA ĉar la datumoj ankoraŭ ne estus fiksitaj fizike al la pinglo antaŭ la tempo kiam ĝi estas s.ampgvidata de la IN-operacio. NOP-instrukcio devas esti metita inter la OUT kaj la IN-instrukcio por certigi ke la ĝusta valoro ĉeestas en la PIN-registro.

Tamen, kiam unuopa paŝado de ĉi tiu funkcio tra la OCD, ĉi tiu kodo ĉiam donos 0xAA en la PIN-registro ĉar la I/O funkcias plenrapide eĉ kiam la kerno estas haltigita dum la ununura paŝado.

Ununura paŝado kaj tempigo

Certaj registroj devas esti legitaj aŭ skribitaj ene de antaŭfiksita nombro da cikloj post ebligado de kontrolsignalo. Ĉar la I/O-horloĝo kaj ekstercentraj daŭre funkcias plenrapide en haltigita reĝimo, ununura paŝado tra tia kodo ne renkontos la tempopostulojn. Inter du ununuraj paŝoj, la I/O-horloĝo eble kuris milionojn da cikloj. Por sukcese legi aŭ skribi registrojn kun tiaj tempopostuloj, la tuta legado aŭ skriba sekvenco devus esti farita kiel atomoperacio kurante la aparaton plenrapide. Ĉi tio povas esti farita per uzado de makroo aŭ funkciovoko por ekzekuti la kodon, aŭ uzi la funkcion rul-al-kursoro en la sencimiga medio.

Aliro al 16-bitaj registroj

La Atmel AVR-ekscentraloj tipe enhavas plurajn 16-bitajn registrojn kiuj povas esti aliritaj per la 8-bita datenbuso (ekz.: TCNTn de 16-bita tempigilo). La 16-bita registro devas esti bajto alirita uzante du legado- aŭ skriboperaciojn. Rompi en la mezo de 16-bita aliro aŭ ununura paŝado tra ĉi tiu situacio povas rezultigi erarajn valorojn.

Restriktita I/O registra aliro

Iuj registroj ne povas esti legitaj sen tuŝi ilian enhavon. Tiaj registroj inkluzivas tiujn, kiuj enhavas flagojn, kiuj estas purigitaj per legado, aŭ bufritaj datenregistroj (ekz.: UDR). La programara fronto malhelpos legi ĉi tiujn registrojn kiam en haltigita reĝimo por konservi la celitan ne-trudeman naturon de OCD-sencimigo. Krome, kelkaj registroj ne povas sekure esti skribitaj sen kromefikoj okazantaj - tiuj registroj estas nurlegeblaj. Por ekzample:

- Flagaj registroj, kie flago estas forigita skribante '1' al iu ajn Ĉi tiuj registroj estas nurlegeblaj.

- UDR kaj SPDR-registroj ne povas esti legitaj sen influi la staton de la modulo. Ĉi tiuj registroj ne estas

4.4.12. megaAVR Specialaj Konsideroj

Programaraj rompopunktoj

Ĉar ĝi enhavas fruan version de la OCD-modulo, ATmega128[A] ne subtenas la uzon de la BREAK-instrukcio por programaraj rompopunktoj.

JTAG horloĝo

La cela horloĝfrekvenco devas esti precize specifita en la programara fronto antaŭ ol komenci sencimigan sesion. Pro sinkronigaj kialoj, la JTAG TCK-signalo devas esti malpli ol unu kvarono de la cela horloĝfrekvenco por fidinda senararigado. Dum programado per la JTAG interfaco, la TCK-frekvenco estas limigita per la maksimumfrekvenca takso de la cela aparato, kaj ne la fakta horloĝfrekvenco estanta uzita.

Kiam vi uzas la internan RC-oscilatoron, konsciu, ke la frekvenco povas varii de aparato al aparato kaj estas tuŝita de temperaturo kaj V.CC ŝanĝoj. Estu konservativa dum specifado de la cela horloĝfrekvenco.

JTAGEN kaj OCDEN fuzeoj

La JTAG interfaco estas ebligita uzante la JTAGEN fuzeo, kiu estas programita defaŭlte. Tio permesas aliron al la JTAG programa interfaco. Per ĉi tiu mekanismo, la OCDEN-fuzeo povas esti programita (defaŭlte OCDEN estas ne-programita). Ĉi tio permesas aliron al la OCD por faciligi sencimigi la aparaton. La programara fronto ĉiam certigos, ke la OCDEN-fuzeo estas lasita neprogramita dum fino de sesio, tiel limigante nenecesan elektrokonsumon de la OCD-modulo. Se la JTAGEN-fuzeo estas neintence malŝaltita, ĝi povas nur esti reebligita uzante SPI aŭ High Voltage programaj metodoj.

Se la JTAGEN-fuzeo estas programita, la JTAG interfaco ankoraŭ povas esti malŝaltita en firmvaro per agordo de la JTD-bito. Ĉi tio faros kodon nesencimigebla, kaj ne faru kiam vi provas sencimigan sesion. Se tia kodo jam efektiviĝas sur la Atmel AVR-aparato kiam oni komencas sencimigan sesion, la Atmel-ICE asertos la RESET-linion dum la konekto. Se ĉi tiu linio estas kabligita ĝuste, ĝi devigos la celitan AVR-aparaton restarigi, tiel permesante JTAG konekto.

Se la JTAG interfaco estas ebligita, la JTAG pingloj ne povas esti uzataj por alternativaj pinglaj funkcioj. Ili restos dediĉitaj JTAG pingloj ĝis aŭ la JTAG interfaco estas malfunkciigita metante la JTD-biton de la programkodo, aŭ malbarante la JTAGEN fuzio per programa interfaco.

![]() Konsilo:

Konsilo:

Nepre marku la markobutonon "uzu eksteran rekomencigon" kaj en la dialogo pri programado kaj en la dialogo pri sencimigaj opcioj por permesi al la Atmel-ICE aserti la linion RESET kaj reŝalti la J.TAG interfaco sur aparatoj, kiuj funkcias kodon, kiu malŝaltas la JTAG interfaco fiksante la JTD-biton.

IDR/OCDR-okazaĵoj

La IDR (In-out Data Register) ankaŭ estas konata kiel la OCDR (On Chip Debug Register), kaj estas uzita grandskale fare de la erarserĉilo por legi kaj skribi informojn al la MCU kiam en haltigita reĝimo dum sencimiga sesio. Kiam la aplikaĵa programo en rulreĝimo skribas bajton da datumoj al la OCDR-registro de la AVR-aparato estanta sencimigita, la Atmel-ICE legas ĉi tiun valoron kaj montras ĝin en la mesaĝfenestro de la programara fronto. La OCDR-registro estas balotita ĉiun 50ms, do skribi al ĝi je pli alta frekvenco NE donos fidindajn rezultojn. Kiam la AVR-aparato perdas potencon dum ĝi estas sencimigita, falsaj OCDR-okazaĵoj povas esti raportitaj. Ĉi tio okazas ĉar la Atmel-ICE ankoraŭ povas baloti la aparaton kiel la cela voltage falas sub la minimuman operacian volon de la AVRtage.

4.4.13. AVR XMEGA Specialaj Konsideroj

OCD kaj horloĝo