Lập trình viên gỡ lỗi ICE

Lập trình viên gỡ lỗi ICE

Hướng dẫn sử dụng Lập trình viên và trình gỡ lỗi

Lập trình viên và trình gỡ lỗi

Atmel-ICE

HƯỚNG DẪN SỬ DỤNG

Trình gỡ lỗi Atmel-ICE

Atmel-ICE là một công cụ phát triển mạnh mẽ để gỡ lỗi và lập trình vi điều khiển Atmel ®SAM và Atmel AVR dựa trên ARM® Cortex®-M với khả năng gỡ lỗi trên chip.

Nó hỗ trợ:

- Lập trình và gỡ lỗi trên chip của tất cả các bộ vi điều khiển Atmel AVR 32-bit trên cả JTAG và giao diện aWire

- Lập trình và gỡ lỗi trên chip của tất cả các thiết bị gia đình Atmel AVR XMEGA® trên cả JTAG và giao diện PDI 2 dây

- Lập trình (JTAG, SPI, UPDI) và gỡ lỗi tất cả các bộ vi điều khiển Atmel AVR 8-bit có hỗ trợ OCD trên cả JTAG, giao diện debugWIRE hoặc UPDI

- Lập trình và gỡ lỗi tất cả các bộ vi điều khiển dựa trên Atmel SAM ARM Cortex-M trên cả SWD và JTAG giao diện

- Lập trình (TPI) của tất cả các bộ vi điều khiển Atmel tinyAVR® 8-bit có hỗ trợ giao diện này

Tham khảo danh sách thiết bị được hỗ trợ trong Hướng dẫn sử dụng Atmel Studio để biết danh sách đầy đủ các thiết bị và giao diện được bản phát hành phần mềm này hỗ trợ.

Giới thiệu

1.1. Giới thiệu về Atmel-ICE

Atmel-ICE là một công cụ phát triển mạnh mẽ để gỡ lỗi và lập trình vi điều khiển Atmel SAM và Atmel AVR dựa trên ARM Cortex-M với khả năng gỡ lỗi trên chip.

Nó hỗ trợ:

- Lập trình và gỡ lỗi trên chip của tất cả các vi điều khiển Atmel AVR UC3 trên cả JTAG và giao diện aWire

- Lập trình và gỡ lỗi trên chip của tất cả các thiết bị họ AVR XMEGA trên cả JTAG và giao diện PDI 2 dây

- Lập trình (JTAG và SPI) và gỡ lỗi tất cả các bộ vi điều khiển AVR 8 bit có hỗ trợ OCD trên cả JTAG hoặc giao diện debugWIRE

- Lập trình và gỡ lỗi tất cả các bộ vi điều khiển dựa trên Atmel SAM ARM Cortex-M trên cả SWD và JTAG giao diện

- Lập trình (TPI) của tất cả các vi điều khiển Atmel tinyAVR 8-bit có hỗ trợ giao diện này

1.2. Tính năng của Atmel-ICE

- Hoàn toàn tương thích với Atmel Studio

- Hỗ trợ lập trình và gỡ lỗi tất cả các vi điều khiển Atmel AVR UC3 32-bit

- Hỗ trợ lập trình và gỡ lỗi tất cả các thiết bị AVR XMEGA 8-bit

- Hỗ trợ lập trình và gỡ lỗi tất cả các thiết bị Atmel megaAVR® và tinyAVR 8-bit có OCD

- Hỗ trợ lập trình và gỡ lỗi tất cả các bộ vi điều khiển dựa trên SAM ARM Cortex-M

- Mục tiêu hoạt động voltagDải điện áp từ 1.62V đến 5.5V

- Rút ít hơn 3mA từ VTref mục tiêu khi sử dụng giao diện debugWIRE và ít hơn 1mA cho tất cả các giao diện khác

- Hỗ trợ JTAG tần số xung nhịp từ 32kHz đến 7.5MHz

- Hỗ trợ tần số xung nhịp PDI từ 32kHz đến 7.5MHz

- Hỗ trợ tốc độ truyền debugWIRE từ 4kbit/giây đến 0.5Mbit/giây

- Hỗ trợ tốc độ truyền dữ liệu aWire từ 7.5kbit/giây đến 7Mbit/giây

- Hỗ trợ tần số xung nhịp SPI từ 8kHz đến 5MHz

- Hỗ trợ tốc độ truyền UPDI lên đến 750kbit/giây

- Hỗ trợ tần số xung nhịp SWD từ 32kHz đến 10MHz

- Giao diện máy chủ tốc độ cao USB 2.0

- Ghi lại dấu vết nối tiếp ITM với tốc độ lên tới 3MB/giây

- Hỗ trợ giao diện DGI SPI và USART khi không gỡ lỗi hoặc lập trình

- Hỗ trợ 10 chân 50 mil JTAG đầu nối với cả chân cắm AVR và Cortex. Cáp thăm dò tiêu chuẩn hỗ trợ đầu cắm ISP/PDI/TPI 6 mil 100 chân AVR cũng như đầu cắm 10 chân 50 mil 6 chân. Có sẵn bộ chuyển đổi để hỗ trợ đầu cắm 50 chân 10 mil, 100 chân 20 mil và 100 chân XNUMX mil. Có nhiều tùy chọn bộ dụng cụ với các loại cáp và bộ chuyển đổi khác nhau.

1.3. Yêu cầu hệ thống

Thiết bị Atmel-ICE yêu cầu máy tính của bạn phải cài đặt môi trường gỡ lỗi giao diện Atmel Studio phiên bản 6.2 trở lên.

Atmel-ICE phải được kết nối với máy chủ bằng cáp USB đi kèm hoặc cáp Micro-USB được chứng nhận.

Bắt đầu với Atmel-ICE

2.1. Nội dung đầy đủ của bộ sản phẩm

Bộ Atmel-ICE đầy đủ bao gồm các mục sau:

- Đơn vị Atmel-ICE

- Cáp USB (1.8m, tốc độ cao, Micro-B)

- Bo mạch điều hợp chứa bộ điều hợp AVR 50 mil, AVR/SAM 100 mil và SAM 100 chân 20 mil

- Cáp dẹt IDC với đầu nối 10 chân 50 mil và đầu nối 6 chân 100 mil

- Cáp mini squid 50 chân 10 mil với 10 ổ cắm 100 mil

Hình 2-1. Nội dung đầy đủ của Atmel-ICE 2.2. Nội dung cơ bản của bộ dụng cụ

2.2. Nội dung cơ bản của bộ dụng cụ

Bộ dụng cụ cơ bản Atmel-ICE bao gồm các mục sau:

- Đơn vị Atmel-ICE

- Cáp USB (1.8m, tốc độ cao, Micro-B)

- Cáp dẹt IDC với đầu nối 10 chân 50 mil và đầu nối 6 chân 100 mil

Hình 2-2. Nội dung của bộ Atmel-ICE cơ bản 2.3. Nội dung bộ PCBA

2.3. Nội dung bộ PCBA

Bộ PCBA Atmel-ICE bao gồm các mục sau:

- Đơn vị Atmel-ICE không có vỏ bọc nhựa

Hình 2-3. Nội dung của bộ PCBA Atmel-ICE 2.4. Bộ phụ tùng thay thế

2.4. Bộ phụ tùng thay thế

Các bộ phụ tùng thay thế sau đây hiện có sẵn:

- Bộ chuyển đổi

- bộ cáp

Hình 2-4. Nội dung của Bộ chuyển đổi Atmel-ICE 2.5. Bộ dụng cụ kết thúcview

2.5. Bộ dụng cụ kết thúcview

Các tùy chọn bộ Atmel-ICE được hiển thị dưới dạng sơ đồ ở đây:

Hình 2-6. Bộ Atmel-ICE Overview 2.6. Lắp ráp Atmel-ICE

2.6. Lắp ráp Atmel-ICE

Thiết bị Atmel-ICE được vận chuyển mà không kèm theo cáp. Có hai tùy chọn cáp được cung cấp trong bộ sản phẩm đầy đủ:

- Cáp dẹt IDC 50 chân 10 mil với ISP 6 chân và đầu nối 10 chân

- Cáp mini-squid 50 chân 10 mil với 10 ổ cắm 100 mil

Hình 2-7. Cáp Atmel-ICE Đối với hầu hết các mục đích, cáp phẳng IDC 50 chân 10 mil có thể được sử dụng, kết nối trực tiếp với đầu nối 10 chân hoặc 6 chân hoặc kết nối thông qua bảng bộ điều hợp. Có ba bộ điều hợp trên một PCBA nhỏ. Các bộ điều hợp sau đây được bao gồm:

Đối với hầu hết các mục đích, cáp phẳng IDC 50 chân 10 mil có thể được sử dụng, kết nối trực tiếp với đầu nối 10 chân hoặc 6 chân hoặc kết nối thông qua bảng bộ điều hợp. Có ba bộ điều hợp trên một PCBA nhỏ. Các bộ điều hợp sau đây được bao gồm:

- 100-mil 10-pin JTAG/Bộ chuyển đổi SWD

- 100-mil 20-pin SAM JTAG/Bộ chuyển đổi SWD

- Bộ chuyển đổi SPI/debugWIRE/PDI/aWire 50-pin 6 chân

Hình 2-8. Bộ điều hợp Atmel-ICE Ghi chú:

Ghi chú:

Một J 50 triệuTAG bộ chuyển đổi không được cung cấp – điều này là do cáp IDC 50 chân 10 mil có thể được sử dụng để kết nối trực tiếp với J 50 milTAG tiêu đề. Để biết số bộ phận của linh kiện được sử dụng cho đầu nối 50 chân 10 mil, hãy xem Số bộ phận của Đầu nối mục tiêu Atmel-ICE.

Đầu cắm ISP/PDI 6 chân được bao gồm như một phần của cáp IDC 10 chân. Đầu cắm này có thể bị cắt nếu không cần thiết.

Để lắp ráp Atmel-ICE của bạn vào cấu hình mặc định, hãy kết nối cáp IDC 10 chân 50 mil với thiết bị như minh họa bên dưới. Đảm bảo định hướng cáp sao cho dây màu đỏ (chân 1) trên cáp thẳng hàng với chỉ báo hình tam giác trên đai màu xanh của vỏ. Cáp phải kết nối hướng lên trên từ thiết bị. Đảm bảo kết nối với cổng tương ứng với chân cắm của mục tiêu của bạn – AVR hoặc SAM.

Hình 2-9. Kết nối cáp Atmel-ICE Hình 2-10. Kết nối đầu dò Atmel-ICE AVR

Hình 2-10. Kết nối đầu dò Atmel-ICE AVR

Hình 2-11. Kết nối đầu dò Atmel-ICE SAM

Hình 2-11. Kết nối đầu dò Atmel-ICE SAM 2.7. Mở Atmel-ICE

2.7. Mở Atmel-ICE

Ghi chú:

Đối với hoạt động bình thường, không được mở thiết bị Atmel-ICE. Việc mở thiết bị được thực hiện theo rủi ro của riêng bạn.

Cần phải thực hiện các biện pháp phòng ngừa tĩnh điện.

Vỏ Atmel-ICE bao gồm ba thành phần nhựa riêng biệt – nắp trên, nắp dưới và đai xanh – được đóng lại với nhau trong quá trình lắp ráp. Để mở thiết bị, chỉ cần lắp một tua vít dẹt lớn vào các lỗ trên đai xanh, ấn nhẹ vào trong và vặn nhẹ. Lặp lại quy trình trên các lỗ khóa khác và nắp trên sẽ bật ra.

Hình 2-12. Mở Atmel-ICE (1)

Hình 2-13. Mở Atmel-ICE (2)

Hình 2-13. Mở Atmel-ICE (2)

Hình 2-14. Mở Atmel-ICE(3)

Hình 2-14. Mở Atmel-ICE(3) Để đóng lại thiết bị, chỉ cần căn chỉnh nắp trên và nắp dưới cho đúng cách và ấn chặt vào nhau.

Để đóng lại thiết bị, chỉ cần căn chỉnh nắp trên và nắp dưới cho đúng cách và ấn chặt vào nhau.

2.8. Cung cấp năng lượng cho Atmel-ICE

Atmel-ICE được cung cấp năng lượng bởi bus USB voltage. Nó cần ít hơn 100mA để hoạt động và do đó có thể được cấp nguồn thông qua một hub USB. Đèn LED nguồn sẽ sáng khi thiết bị được cắm vào. Khi không được kết nối trong phiên lập trình hoặc gỡ lỗi đang hoạt động, thiết bị sẽ chuyển sang chế độ tiêu thụ điện năng thấp để bảo vệ pin máy tính của bạn. Không thể tắt nguồn Atmel-ICE – nên rút phích cắm khi không sử dụng.

2.9. Kết nối với máy chủ

Atmel-ICE giao tiếp chủ yếu bằng giao diện HID chuẩn và không yêu cầu trình điều khiển đặc biệt trên máy chủ. Để sử dụng chức năng Data Gateway nâng cao của Atmel-ICE, hãy đảm bảo cài đặt trình điều khiển USB trên máy chủ. Việc này được thực hiện tự động khi cài đặt phần mềm front-end miễn phí do Atmel cung cấp. Xem www.atmel.com để biết thêm thông tin hoặc tải xuống phần mềm giao diện mới nhất.

Atmel-ICE phải được kết nối với một cổng USB khả dụng trên máy chủ bằng cáp USB được cung cấp hoặc cáp micro USB được chứng nhận phù hợp. Atmel-ICE chứa bộ điều khiển tương thích USB 2.0 và có thể hoạt động ở cả chế độ tốc độ đầy đủ và tốc độ cao. Để có kết quả tốt nhất, hãy kết nối Atmel-ICE trực tiếp với hub tốc độ cao tương thích USB 2.0 trên máy chủ bằng cáp được cung cấp.

2.10. Cài đặt trình điều khiển USB

2.10.1. Cửa sổ

Khi cài đặt Atmel-ICE trên máy tính chạy Microsoft® Windows®, trình điều khiển USB sẽ được tải khi Atmel-ICE được cắm vào lần đầu tiên.

Ghi chú:

Hãy chắc chắn rằng bạn đã cài đặt các gói phần mềm giao diện trước khi cắm thiết bị vào lần đầu tiên.

Sau khi cài đặt thành công, Atmel-ICE sẽ xuất hiện trong trình quản lý thiết bị dưới dạng “Thiết bị giao diện người dùng”.

Kết nối Atmel-ICE

3.1. Kết nối với thiết bị AVR và SAM Target

Atmel-ICE được trang bị hai chân cắm J 50 mil 10 chânTAG đầu nối. Cả hai đầu nối đều được kết nối điện trực tiếp, nhưng tuân theo hai chân cắm khác nhau; AVR JTAG header và header ARM Cortex Debug. Đầu nối phải được chọn dựa trên chân cắm của bo mạch đích chứ không phải loại MCU đích – ví dụampthiết bị SAM được gắn trong ngăn xếp AVR STK® 600 phải sử dụng đầu cắm AVR.

Nhiều loại cáp và bộ chuyển đổi khác nhau có sẵn trong các bộ Atmel-ICE khác nhau. Mộtview của các tùy chọn kết nối được hiển thị.

Hình 3-1. Tùy chọn kết nối Atmel-ICE Dây màu đỏ đánh dấu chân 1 của đầu nối 10 chân 50 mil. Chân 1 của đầu nối 6 chân 100 mil được đặt ở bên phải của khóa khi đầu nối được nhìn thấy từ cáp. Chân 1 của mỗi đầu nối trên bộ chuyển đổi được đánh dấu bằng một chấm trắng. Hình bên dưới hiển thị chân cắm của cáp gỡ lỗi. Đầu nối được đánh dấu A cắm vào trình gỡ lỗi trong khi mặt B cắm vào bảng mục tiêu.

Dây màu đỏ đánh dấu chân 1 của đầu nối 10 chân 50 mil. Chân 1 của đầu nối 6 chân 100 mil được đặt ở bên phải của khóa khi đầu nối được nhìn thấy từ cáp. Chân 1 của mỗi đầu nối trên bộ chuyển đổi được đánh dấu bằng một chấm trắng. Hình bên dưới hiển thị chân cắm của cáp gỡ lỗi. Đầu nối được đánh dấu A cắm vào trình gỡ lỗi trong khi mặt B cắm vào bảng mục tiêu.

Hình 3-2. Sơ đồ chân cáp gỡ lỗi

3.2. Kết nối với JTAG Mục tiêu

3.2. Kết nối với JTAG Mục tiêu

Atmel-ICE được trang bị hai chân cắm J 50 mil 10 chânTAG đầu nối. Cả hai đầu nối đều được kết nối điện trực tiếp, nhưng tuân theo hai chân cắm khác nhau; AVR JTAG header và header ARM Cortex Debug. Đầu nối phải được chọn dựa trên chân cắm của bo mạch đích chứ không phải loại MCU đích – ví dụampthiết bị SAM được gắn trong ngăn xếp AVR STK600 phải sử dụng đầu cắm AVR.

Pinout được đề xuất cho AVR J 10 chânTAG đầu nối được hiển thị trong Hình 4-6. Sơ đồ chân cắm được khuyến nghị cho đầu nối ARM Cortex Debug 10 chân được hiển thị trong Hình 4-2.

Kết nối trực tiếp với đầu cắm 10 chân 50 mil tiêu chuẩn

Sử dụng cáp dẹt 50-mil 10 chân (có trong một số bộ sản phẩm) để kết nối trực tiếp với bo mạch hỗ trợ loại chân cắm này. Sử dụng cổng kết nối AVR trên Atmel-ICE cho các chân cắm có chân cắm AVR và cổng kết nối SAM cho các chân cắm tuân thủ chân cắm chân cắm ARM Cortex Debug.

Sơ đồ chân cắm cho cả hai cổng kết nối 10 chân được hiển thị bên dưới.

Kết nối với đầu cắm 10 chân 100 mil tiêu chuẩn

Sử dụng bộ chuyển đổi chuẩn 50 mil sang 100 mil để kết nối với đầu cắm 100 mil. Có thể sử dụng bảng chuyển đổi (có trong một số bộ dụng cụ) cho mục đích này hoặc thay thế bằng JTAGBộ điều hợp ICE3 có thể được sử dụng cho mục tiêu AVR.

![]() Quan trọng:

Quan trọng:

Chữ JTAGKhông thể sử dụng bộ chuyển đổi ICE3 100-mil với cổng kết nối SAM vì chân 2 và 10 (AVR GND) trên bộ chuyển đổi được kết nối.

Kết nối với đầu nối 100 mil tùy chỉnh

Nếu bo mạch mục tiêu của bạn không có đầu nối J 10 chân tương thíchTAG tiêu đề ở mức 50 hoặc 100 mil, bạn có thể ánh xạ tới một chân cắm tùy chỉnh bằng cáp “mini-squid” 10 chân (có trong một số bộ dụng cụ), cho phép truy cập vào mười ổ cắm 100 mil riêng lẻ.

Kết nối với đầu cắm 20 chân 100 milr

Sử dụng bảng chuyển đổi (có trong một số bộ dụng cụ) để kết nối với mục tiêu có đầu cắm 20 chân 100 mil.

Bảng 3-1. Atmel-ICE JTAG Mô tả Pin

| Tên | AVR chân cổng | SAM chân cổng | Sự miêu tả |

| TCK | 1 | 4 | Đồng hồ thử nghiệm (tín hiệu đồng hồ từ Atmel-ICE vào thiết bị mục tiêu). |

| TMS | 5 | 2 | Chọn chế độ kiểm tra (tín hiệu điều khiển từ Atmel-ICE vào thiết bị mục tiêu). |

| TDI | 9 | 8 | Dữ liệu thử nghiệm đầu vào (dữ liệu được truyền từ Atmel-ICE vào thiết bị mục tiêu). |

| TDO | 3 | 6 | Kiểm tra dữ liệu đầu ra (dữ liệu được truyền từ thiết bị mục tiêu vào Atmel-ICE). |

| nTRST | 8 | – | Kiểm tra lại (tùy chọn, chỉ có trên một số thiết bị AVR). Được sử dụng để thiết lập lại JTAG Bộ điều khiển TAP. |

| nSRST | 6 | 10 | Đặt lại (tùy chọn). Được sử dụng để đặt lại thiết bị mục tiêu. Nên kết nối chân này vì nó cho phép Atmel-ICE giữ thiết bị mục tiêu ở trạng thái đặt lại, điều này có thể cần thiết để gỡ lỗi trong một số trường hợp nhất định. |

| VTG | 4 | 1 | Mục tiêu voltage tham khảo. Atmel-ICE samples mục tiêu voltage trên chân này để cấp nguồn cho bộ chuyển đổi mức một cách chính xác. Atmel-ICE rút ít hơn 3mA từ chân này ở chế độ debugWIRE và ít hơn 1mA ở các chế độ khác. |

| GND | 2, 10 | 3, 5, 9 | Đất. Tất cả phải được kết nối để đảm bảo Atmel-ICE và thiết bị mục tiêu có cùng điểm tham chiếu đất. |

3.3. Kết nối với mục tiêu aWire

Giao diện aWire chỉ yêu cầu một đường dữ liệu ngoài VCC và GND. Trên mục tiêu, đường này là đường nRESET, mặc dù trình gỡ lỗi sử dụng JTAG Đường TDO đóng vai trò là đường dữ liệu.

Sơ đồ chân cắm được khuyến nghị cho đầu nối aWire 6 chân được hiển thị trong Hình 4-8.

Kết nối với đầu cắm aWire 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối aWire 100 mil tiêu chuẩn.

Kết nối với đầu cắm aWire 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ sản phẩm) để kết nối với đầu nối aWire 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có ba kết nối, như mô tả trong bảng bên dưới.

Bảng 3-2. Ánh xạ chân Atmel-ICE aWire

|

Chân cổng Atmel-ICE AVR |

Ghim mục tiêu | Mini-mực pin |

aPinout dây |

| Chân 1 (TCK) | 1 | ||

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | DỮ LIỆU | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 | ||

| Chân 6 (nSRST) | 6 | ||

| Pin 7 (Không kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | 9 | ||

| Chân 10 (GND) | 0 |

3.4. Kết nối với mục tiêu PDI

Sơ đồ chân cắm được khuyến nghị cho đầu nối PDI 6 chân được hiển thị trong Hình 4-11.

Kết nối với đầu cắm PDI 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối PDI 100 mil tiêu chuẩn.

Kết nối với đầu cắm PDI 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu cắm PDI 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có bốn kết nối, như mô tả trong bảng bên dưới.

![]() Quan trọng:

Quan trọng:

Pinout yêu cầu khác với JTAGICE mkII JTAG đầu dò, trong đó PDI_DATA được kết nối với chân 9. Atmel-ICE tương thích với chân cắm được sử dụng bởi Atmel-ICE, JTAGCác sản phẩm ICE3, AVR ONE! và AVR Dragon™.

Bảng 3-3. Ánh xạ chân Atmel-ICE PDI

| Chân cổng Atmel-ICE AVR | Ghim mục tiêu | Mini-mực pin |

aPinout dây |

| Chân 1 (TCK) | 1 | ||

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | DỮ LIỆU | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 | ||

| Chân 6 (nSRST) | 6 | ||

| Pin 7 (Không kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | 9 | ||

| Chân 10 (GND) | 0 |

3.4 Kết nối với mục tiêu PDI

Sơ đồ chân cắm được khuyến nghị cho đầu nối PDI 6 chân được hiển thị trong Hình 4-11.

Kết nối với đầu cắm PDI 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối PDI 100 mil tiêu chuẩn.

Kết nối với đầu cắm PDI 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu cắm PDI 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có bốn kết nối, như mô tả trong bảng bên dưới.

![]() Quan trọng:

Quan trọng:

Pinout yêu cầu khác với JTAGICE mkII JTAG đầu dò, trong đó PDI_DATA được kết nối với chân 9. Atmel-ICE tương thích với chân cắm được sử dụng bởi Atmel-ICE, JTAGICE3, AVR ONE!, và AVR Dragon™ các sản phẩm.

Bảng 3-3. Ánh xạ chân Atmel-ICE PDI

| Chân cổng Atmel-ICE AVR | Ghim mục tiêu | Mini-mực pin | Sơ đồ chân cắm PDI của Atmel STK600 |

| Chân 1 (TCK) | 1 | ||

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | DỮ LIỆU PDI | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 | ||

| Chân 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (không được kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | 9 | ||

| Chân 10 (GND) | 0 |

3.5 Kết nối với mục tiêu UPDI

Sơ đồ chân cắm được khuyến nghị cho đầu nối UPDI 6 chân được hiển thị trong Hình 4-12.

Kết nối với đầu cắm UPDI 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối UPDI 100 mil tiêu chuẩn.

Kết nối với đầu cắm UPDI 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu cắm UPDI 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có ba kết nối, như mô tả trong bảng bên dưới.

Bảng 3-4. Ánh xạ chân Atmel-ICE UPDI

| Chân cổng Atmel-ICE AVR | Ghim mục tiêu | Mini-mực pin |

Sơ đồ chân Atmel STK600 UPDI |

| Chân 1 (TCK) | 1 | ||

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | DỮ LIỆU CẬP NHẬT | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 | ||

| Chân 6 (nSRST) | [/RESET cảm giác] | 6 | 5 |

| Pin 7 (Không kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | 9 | ||

| Chân 10 (GND) | 0 |

3.6 Kết nối với mục tiêu debugWIRE

Sơ đồ chân cắm được khuyến nghị cho đầu nối debugWIRE (SPI) 6 chân được hiển thị trong Bảng 3-6.

Kết nối với đầu cắm SPI 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối SPI 100 mil tiêu chuẩn.

Kết nối với đầu cắm SPI 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu cắm SPI 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có ba kết nối, như mô tả trong Bảng 3-5.

Mặc dù giao diện debugWIRE chỉ yêu cầu một đường tín hiệu (RESET), VCC và GND để hoạt động chính xác, bạn nên truy cập vào toàn bộ đầu nối SPI để có thể bật và tắt giao diện debugWIRE bằng lập trình SPI.

Khi cầu chì DWEN được bật, giao diện SPI sẽ bị ghi đè bên trong để mô-đun OCD có thể kiểm soát chân RESET. OCD debugWIRE có khả năng tự tắt tạm thời (sử dụng nút trên tab gỡ lỗi trong hộp thoại thuộc tính trong Atmel Studio), do đó giải phóng quyền kiểm soát dòng RESET. Sau đó, giao diện SPI sẽ khả dụng trở lại (chỉ khi cầu chì SPIEN được lập trình), cho phép hủy lập trình cầu chì DWEN bằng giao diện SPI. Nếu nguồn được bật trước khi cầu chì DWEN được hủy lập trình, mô-đun debugWIRE sẽ lại kiểm soát chân RESET.

Ghi chú:

Bạn nên để Atmel Studio xử lý việc cài đặt và xóa cầu chì DWEN.

Không thể sử dụng giao diện debugWIRE nếu các bit khóa trên thiết bị AVR mục tiêu được lập trình. Luôn đảm bảo rằng các bit khóa được xóa trước khi lập trình cầu chì DWEN và không bao giờ đặt các bit khóa trong khi cầu chì DWEN được lập trình. Nếu cả cầu chì kích hoạt debugWIRE (DWEN) và các bit khóa đều được đặt, người ta có thể sử dụng High Voltage Lập trình để xóa chip và do đó xóa các bit khóa.

Khi các lockbit được xóa, giao diện debugWIRE sẽ được bật lại. Giao diện SPI chỉ có khả năng đọc cầu chì, đọc chữ ký và thực hiện xóa chip khi cầu chì DWEN không được lập trình.

Bảng 3-5. Ánh xạ chân Atmel-ICE debugWIRE

| Chân cổng Atmel-ICE AVR | Ghim mục tiêu |

Mini-mực pin |

| Chân 1 (TCK) | 1 | |

| Chân 2 (GND) | GND | 2 |

| Chân 3 (TDO) | 3 | |

| Chân 4 (VTG) | VTG | 4 |

| Chân 5 (TMS) | 5 | |

| Chân 6 (nSRST) | CÀI LẠI | 6 |

| Pin 7 (Không kết nối) | 7 | |

| Chân 8 (nTRST) | 8 | |

| Chân 9 (TDI) | 9 | |

| Chân 10 (GND) | 0 |

3.7 Kết nối với mục tiêu SPI

Sơ đồ chân cắm được khuyến nghị cho đầu nối SPI 6 chân được hiển thị trong Hình 4-10.

Kết nối với đầu cắm SPI 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối SPI 100 mil tiêu chuẩn.

Kết nối với đầu cắm SPI 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu cắm SPI 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có sáu kết nối, như mô tả trong bảng bên dưới.

![]() Quan trọng:

Quan trọng:

Giao diện SPI bị vô hiệu hóa hiệu quả khi cầu chì kích hoạt debugWIRE (DWEN) được lập trình, ngay cả khi cầu chì SPIEN cũng được lập trình. Để kích hoạt lại giao diện SPI, lệnh 'vô hiệu hóa debugWIRE' phải được đưa ra trong khi đang trong phiên gỡ lỗi debugWIRE. Việc vô hiệu hóa debugWIRE theo cách này yêu cầu cầu chì SPIEN đã được lập trình. Nếu Atmel Studio không vô hiệu hóa debugWIRE, thì có thể là do cầu chì SPIEN KHÔNG được lập trình. Nếu đúng như vậy, thì cần phải sử dụng mộttagGiao diện lập trình e để lập trình cầu chì SPIEN.

![]() Thông tin:

Thông tin:

Giao diện SPI thường được gọi là “ISP”, vì đây là giao diện Lập trình Trong Hệ thống đầu tiên trên các sản phẩm Atmel AVR. Các giao diện khác hiện có sẵn cho Lập trình Trong Hệ thống.

Bảng 3-6. Ánh xạ chân SPI Atmel-ICE

| Chân cổng Atmel-ICE AVR | Ghim mục tiêu | Mini-mực pin |

Chân cắm SPI |

| Chân 1 (TCK) | SCK | 1 | 3 |

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | MISO | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 | ||

| Chân 6 (nSRST) | /CÀI LẠI | 6 | 5 |

| Pin 7 (không được kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | DAWDLE | 9 | 4 |

| Chân 10 (GND) | 0 |

3.8 Kết nối với mục tiêu TPI

Sơ đồ chân cắm được khuyến nghị cho đầu nối TPI 6 chân được hiển thị trong Hình 4-13.

Kết nối với đầu cắm TPI 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối TPI 100 mil tiêu chuẩn.

Kết nối với đầu cắm TPI 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu nối TPI 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có sáu kết nối, như mô tả trong bảng bên dưới.

Bảng 3-7. Ánh xạ chân TPI Atmel-ICE

| Chân cổng Atmel-ICE AVR | Ghim mục tiêu | Mini-mực pin |

Chân cắm TPI |

| Chân 1 (TCK) | CÁI ĐỒNG HỒ | 1 | 3 |

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | DỮ LIỆU | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 |

| Chân 6 (nSRST) | /CÀI LẠI | 6 | 5 |

| Pin 7 (không được kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | 9 | ||

| Chân 10 (GND) | 0 |

3.9 Kết nối với mục tiêu SWD

Giao diện ARM SWD là một tập hợp con của JTAG giao diện, sử dụng các chân TCK và TMS, nghĩa là khi kết nối với thiết bị SWD, J 10 chânTAG về mặt kỹ thuật có thể sử dụng đầu nối. ARM JTAG và AVR JTAG Tuy nhiên, các đầu nối không tương thích với chân cắm, do đó điều này phụ thuộc vào cách bố trí của bảng mục tiêu đang sử dụng. Khi sử dụng STK600 hoặc bảng sử dụng AVR JTAG pinout, cổng kết nối AVR trên Atmel-ICE phải được sử dụng. Khi kết nối với bo mạch sử dụng ARM JTAG chân cắm, cổng kết nối SAM trên Atmel-ICE phải được sử dụng.

Sơ đồ chân cắm được đề xuất cho đầu nối Cortex Debug 10 chân được hiển thị trong Hình 4-4.

Kết nối với đầu cắm Cortex 10 chân 50 mil

Sử dụng cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu cắm Cortex 50 mil tiêu chuẩn.

Kết nối với đầu cắm Cortex-layout 10 chân 100 mil

Sử dụng bo mạch điều hợp (có trong một số bộ dụng cụ) để kết nối với chân cắm Cortex 100 mil.

Kết nối với đầu cắm SAM 20 chân 100 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu cắm SAM 20 chân 100 mil.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR hoặc SAM và bo mạch mục tiêu. Cần có sáu kết nối, như mô tả trong bảng bên dưới.

Bảng 3-8. Ánh xạ chân Atmel-ICE SWD

| Tên | AVR chân cổng | SAM chân cổng | Sự miêu tả |

| SWDC LK | 1 | 4 | Đồng hồ gỡ lỗi dây nối tiếp. |

| SWDIO | 5 | 2 | Đầu vào/Đầu ra dữ liệu gỡ lỗi dây nối tiếp. |

| SWO | 3 | 6 | Đầu ra dây nối tiếp (tùy chọn - không được triển khai trên tất cả các thiết bị). |

| nSRST | 6 | 10 | Cài lại. |

| VTG | 4 | 1 | Mục tiêu voltage tham khảo. |

| GND | 2, 10 | 3, 5, 9 | Đất. |

3.10 Kết nối với Giao diện Cổng dữ liệu

Atmel-ICE hỗ trợ Giao diện Cổng dữ liệu (DGI) hạn chế khi gỡ lỗi và lập trình không được sử dụng. Chức năng giống hệt với chức năng được tìm thấy trên bộ Atmel Xplained Pro được cung cấp bởi thiết bị Atmel EDBG.

Giao diện Data Gateway là giao diện để truyền dữ liệu từ thiết bị mục tiêu đến máy tính. Giao diện này có mục đích hỗ trợ gỡ lỗi ứng dụng cũng như để trình diễn các tính năng trong ứng dụng đang chạy trên thiết bị mục tiêu.

DGI bao gồm nhiều kênh để truyền dữ liệu. Atmel-ICE hỗ trợ các chế độ sau:

- USART

- SPI

Bảng 3-9. Sơ đồ chân Atmel-ICE DGI USART

|

Cổng AVR |

Cổng SAM | Chân cắm USART của DGI |

Sự miêu tả |

| 3 | 6 | TX | Truyền chân từ Atmel-ICE đến thiết bị mục tiêu |

| 4 | 1 | VTG | Mục tiêu voltage (tài liệu tham khảotage) |

| 8 | 7 | RX | Nhận mã pin từ thiết bị mục tiêu đến Atmel-ICE |

| 9 | 8 | CLK | Đồng hồ USART |

| 2, 10 | 3, 5, 9 | GND | Đất |

Bảng 3-10. Sơ đồ chân cắm SPI Atmel-ICE DGI

|

Cổng AVR |

Cổng SAM | Chân SPI DGI |

Sự miêu tả |

| 1 | 4 | SCK | Đồng hồ SPI |

| 3 | 6 | MISO | Chủ trong nô lệ ra |

| 4 | 1 | VTG | Mục tiêu voltage (tài liệu tham khảotage) |

| 5 | 2 | nCS | Chip chọn hoạt động thấp |

| 9 | 8 | DAWDLE | Làm chủ ra nô lệ trong |

| 2, 10 | 3, 5, 9 | GND | Đất |

![]() Quan trọng: Giao diện SPI và USART không thể sử dụng đồng thời.

Quan trọng: Giao diện SPI và USART không thể sử dụng đồng thời.

![]() Quan trọng: Không thể sử dụng DGI và lập trình hoặc gỡ lỗi cùng lúc.

Quan trọng: Không thể sử dụng DGI và lập trình hoặc gỡ lỗi cùng lúc.

Gỡ lỗi trên chip

4.1 Giới thiệu

Gỡ lỗi trên chip

Mô-đun gỡ lỗi trên chip là hệ thống cho phép nhà phát triển giám sát và kiểm soát việc thực thi trên thiết bị từ nền tảng phát triển bên ngoài, thường thông qua một thiết bị được gọi là trình gỡ lỗi hoặc bộ điều hợp gỡ lỗi.

Với hệ thống OCD, ứng dụng có thể được thực thi trong khi vẫn duy trì chính xác các đặc điểm về điện và thời gian trong hệ thống mục tiêu, đồng thời có thể dừng thực thi theo điều kiện hoặc thủ công và kiểm tra luồng chương trình và bộ nhớ.

Chế độ chạy

Khi ở chế độ Run, việc thực thi mã hoàn toàn độc lập với Atmel-ICE. Atmel-ICE sẽ liên tục theo dõi thiết bị mục tiêu để xem có xảy ra tình trạng ngắt không. Khi điều này xảy ra, hệ thống OCD sẽ thẩm vấn thiết bị thông qua giao diện gỡ lỗi của nó, cho phép người dùng view trạng thái bên trong của thiết bị.

Chế độ dừng

Khi đạt đến điểm dừng, chương trình sẽ dừng thực thi, nhưng một số I/O có thể tiếp tục chạy như thể không có điểm dừng nào xảy ra. Ví dụample, giả sử rằng một quá trình truyền USART vừa được bắt đầu khi đạt đến điểm dừng. Trong trường hợp này, USART tiếp tục chạy ở tốc độ tối đa để hoàn thành quá trình truyền, mặc dù lõi đang ở chế độ dừng.

Điểm dừng phần cứng

Mô-đun OCD mục tiêu chứa một số bộ so sánh bộ đếm chương trình được triển khai trong phần cứng. Khi bộ đếm chương trình khớp với giá trị được lưu trữ trong một trong các thanh ghi bộ so sánh, OCD sẽ chuyển sang chế độ dừng. Vì các điểm dừng phần cứng yêu cầu phần cứng chuyên dụng trên mô-đun OCD, nên số lượng điểm dừng khả dụng phụ thuộc vào kích thước của mô-đun OCD được triển khai trên mục tiêu. Thông thường, một bộ so sánh phần cứng như vậy được 'dành riêng' bởi trình gỡ lỗi để sử dụng nội bộ.

Điểm dừng phần mềm

Điểm dừng phần mềm là lệnh BREAK được đặt trong bộ nhớ chương trình trên thiết bị đích. Khi lệnh này được tải, quá trình thực thi chương trình sẽ bị ngắt và OCD sẽ chuyển sang chế độ dừng. Để tiếp tục thực thi, lệnh “start” phải được đưa ra từ OCD. Không phải tất cả các thiết bị Atmel đều có mô-đun OCD hỗ trợ lệnh BREAK.

4.2 Thiết bị SAM với JTAG/SWD

Tất cả các thiết bị SAM đều có giao diện SWD để lập trình và gỡ lỗi. Ngoài ra, một số thiết bị SAM có giao diện JTAG giao diện có chức năng giống hệt nhau. Kiểm tra bảng dữ liệu thiết bị để biết các giao diện được hỗ trợ của thiết bị đó.

4.2.1.Các thành phần ARM CoreSight

Bộ vi điều khiển dựa trên ARM Cortex-M của Atmel triển khai các thành phần OCD tuân thủ CoreSight. Các tính năng của các thành phần này có thể khác nhau tùy theo thiết bị. Để biết thêm thông tin, hãy tham khảo bảng dữ liệu của thiết bị cũng như tài liệu CoreSight do ARM cung cấp.

4.2.1.JTAG Giao diện vật lý

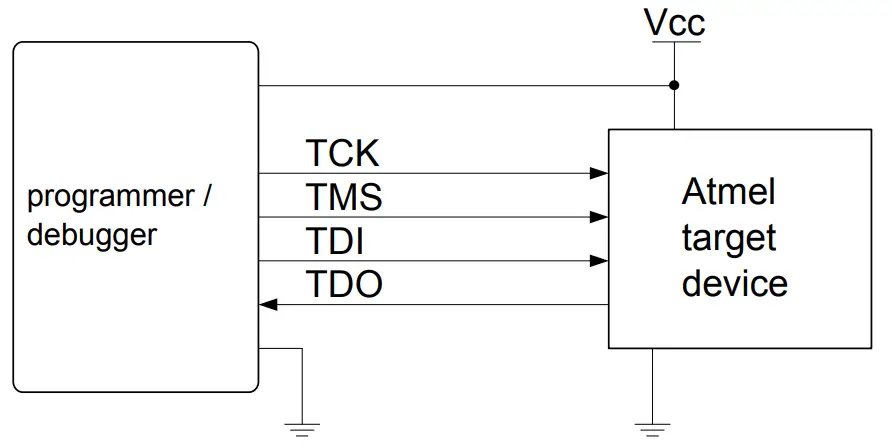

Chữ JTAG giao diện bao gồm bộ điều khiển Cổng truy cập thử nghiệm (TAP) 4 dây tuân thủ theo IEEE® Tiêu chuẩn 1149.1. Tiêu chuẩn IEEE được phát triển để cung cấp một cách thức chuẩn công nghiệp để kiểm tra hiệu quả khả năng kết nối của bảng mạch (Quét ranh giới). Các thiết bị Atmel AVR và SAM đã mở rộng chức năng này để bao gồm hỗ trợ Lập trình và Gỡ lỗi trên chip đầy đủ.

Hình 4-1. JTAG Kiến thức cơ bản về giao diện

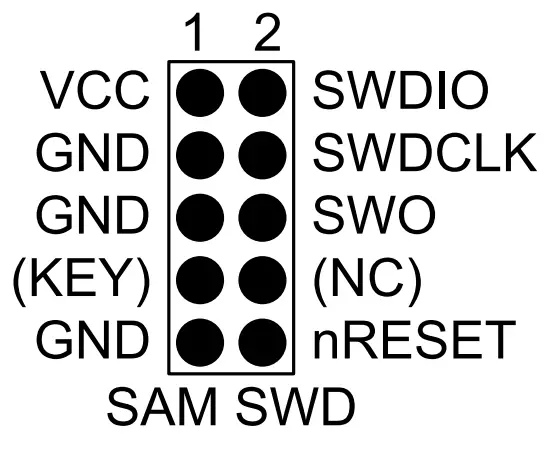

4.2.2.1 SAM JTAG Pinout (đầu nối gỡ lỗi Cortex-M)

Khi thiết kế một PCB ứng dụng bao gồm Atmel SAM với JTAG giao diện, nên sử dụng chân cắm như trong hình bên dưới. Cả hai biến thể 100 mil và 50 mil của chân cắm này đều được hỗ trợ, tùy thuộc vào hệ thống cáp và bộ điều hợp đi kèm với bộ sản phẩm cụ thể.

Hình 4-2. SAM JTAG Pinout đầu trang

Bảng 4-1. SAM JTAG Mô tả Pin

| Tên | Ghim |

Sự miêu tả |

| TCK | 4 | Đồng hồ thử nghiệm (tín hiệu đồng hồ từ Atmel-ICE vào thiết bị mục tiêu). |

| TMS | 2 | Chọn chế độ kiểm tra (tín hiệu điều khiển từ Atmel-ICE vào thiết bị mục tiêu). |

| TDI | 8 | Dữ liệu thử nghiệm đầu vào (dữ liệu được truyền từ Atmel-ICE vào thiết bị mục tiêu). |

| TDO | 6 | Kiểm tra dữ liệu đầu ra (dữ liệu được truyền từ thiết bị mục tiêu vào Atmel-ICE). |

| nĐẶT LẠI | 10 | Đặt lại (tùy chọn). Được sử dụng để đặt lại thiết bị mục tiêu. Nên kết nối chân này vì nó cho phép Atmel-ICE giữ thiết bị mục tiêu ở trạng thái đặt lại, điều này có thể cần thiết để gỡ lỗi trong một số trường hợp nhất định. |

| VTG | 1 | Mục tiêu voltage tham khảo. Atmel-ICE samples mục tiêu voltage trên chân này để cấp nguồn cho bộ chuyển đổi mức một cách chính xác. Atmel-ICE rút ít hơn 1mA từ chân này ở chế độ này. |

| GND | 3, 5, 9 | Đất. Tất cả phải được kết nối để đảm bảo Atmel-ICE và thiết bị mục tiêu có cùng điểm tham chiếu đất. |

| CHÌA KHÓA | 7 | Được kết nối bên trong với chân TRST trên đầu nối AVR. Khuyến nghị là không kết nối. |

![]() Mẹo: Nhớ lắp tụ điện tách rời giữa chân 1 và GND.

Mẹo: Nhớ lắp tụ điện tách rời giữa chân 1 và GND.

4.2.2.2 JTAG Cúc Chuỗi

Chữ JTAG giao diện cho phép nhiều thiết bị được kết nối với một giao diện duy nhất trong cấu hình chuỗi nối tiếp. Các thiết bị mục tiêu phải được cấp nguồn bởi cùng một vol cung cấptage, chia sẻ một nút đất chung và phải được kết nối như minh họa trong hình bên dưới.

Hình 4-3. JTAG Chuỗi hoa cúc

Khi kết nối các thiết bị theo kiểu chuỗi, cần lưu ý những điểm sau:

- Tất cả các thiết bị phải chia sẻ một mặt đất chung, được kết nối với GND trên đầu dò Atmel-ICE

- Tất cả các thiết bị phải hoạt động trên cùng một vol mục tiêutage. VTG trên Atmel-ICE phải được kết nối với vol nàytage.

- TMS và TCK được kết nối song song; TDI và TDO được kết nối nối tiếp

- nSRST trên đầu dò Atmel-ICE phải được kết nối với RESET trên các thiết bị nếu bất kỳ thiết bị nào trong chuỗi vô hiệu hóa J của nóTAG cảng

- “Thiết bị trước” đề cập đến số lượng JTAG các thiết bị mà tín hiệu TDI phải đi qua trong chuỗi liên kết trước khi đến thiết bị mục tiêu. Tương tự như vậy, “thiết bị sau” là số lượng thiết bị mà tín hiệu phải đi qua sau thiết bị mục tiêu trước khi đến Atmel-ICE TDO

- “Các bit hướng dẫn “trước” và “sau” đề cập đến tổng số của tất cả JTAG độ dài thanh ghi lệnh của thiết bị, được kết nối trước và sau thiết bị mục tiêu trong chuỗi nối tiếp

- Tổng chiều dài IR (bit hướng dẫn trước + chiều dài IR của thiết bị mục tiêu Atmel + bit hướng dẫn sau) bị giới hạn ở mức tối đa là 256 bit. Số lượng thiết bị trong chuỗi bị giới hạn ở mức 15 trước và 15 sau.

![]() Mẹo:

Mẹo:

Daisy xích lại cũamptập tin: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Để kết nối với Atmel AVR XMEGA® thiết bị, các thiết lập chuỗi nối tiếp là:

- Thiết bị trước: 1

- Thiết bị sau: 1

- Các bit hướng dẫn trước: 4 (các thiết bị AVR 8 bit có 4 bit IR)

- Các bit hướng dẫn sau: 5 (các thiết bị AVR 32 bit có 5 bit IR)

Bảng 4-2. Chiều dài IR của MCU Atmel

| Loại thiết bị | Chiều dài IR |

| AVR 8-bit | 4 bit |

| AVR 32-bit | 5 bit |

| SAM | 4 bit |

4.2.3. Kết nối với JTAG Mục tiêu

Atmel-ICE được trang bị hai chân cắm J 50 mil 10 chânTAG đầu nối. Cả hai đầu nối đều được kết nối điện trực tiếp, nhưng tuân theo hai chân cắm khác nhau; AVR JTAG header và header ARM Cortex Debug. Đầu nối phải được chọn dựa trên chân cắm của bo mạch đích chứ không phải loại MCU đích – ví dụampthiết bị SAM được gắn trong ngăn xếp AVR STK600 phải sử dụng đầu cắm AVR.

Pinout được đề xuất cho AVR J 10 chânTAG Đầu nối được thể hiện ở Hình 4-6.

Sơ đồ chân cắm được đề xuất cho đầu nối ARM Cortex Debug 10 chân được hiển thị trong Hình 4-2.

Kết nối trực tiếp với đầu cắm 10 chân 50 mil tiêu chuẩn

Sử dụng cáp dẹt 50-mil 10 chân (có trong một số bộ sản phẩm) để kết nối trực tiếp với bo mạch hỗ trợ loại chân cắm này. Sử dụng cổng kết nối AVR trên Atmel-ICE cho các chân cắm có chân cắm AVR và cổng kết nối SAM cho các chân cắm tuân thủ chân cắm chân cắm ARM Cortex Debug.

Sơ đồ chân cắm cho cả hai cổng kết nối 10 chân được hiển thị bên dưới.

Kết nối với đầu cắm 10 chân 100 mil tiêu chuẩn

Sử dụng bộ chuyển đổi chuẩn 50 mil sang 100 mil để kết nối với đầu cắm 100 mil. Có thể sử dụng bảng chuyển đổi (có trong một số bộ dụng cụ) cho mục đích này hoặc thay thế bằng JTAGBộ điều hợp ICE3 có thể được sử dụng cho mục tiêu AVR.

![]() Quan trọng:

Quan trọng:

Chữ JTAGKhông thể sử dụng bộ chuyển đổi ICE3 100-mil với cổng kết nối SAM vì chân 2 và 10 (AVR GND) trên bộ chuyển đổi được kết nối.

Kết nối với đầu nối 100 mil tùy chỉnh

Nếu bo mạch mục tiêu của bạn không có đầu nối J 10 chân tương thíchTAG tiêu đề ở mức 50 hoặc 100 mil, bạn có thể ánh xạ tới một chân cắm tùy chỉnh bằng cáp “mini-squid” 10 chân (có trong một số bộ dụng cụ), cho phép truy cập vào mười ổ cắm 100 mil riêng lẻ.

Kết nối với đầu cắm 20 chân 100 mil

Sử dụng bảng chuyển đổi (có trong một số bộ dụng cụ) để kết nối với mục tiêu có đầu cắm 20 chân 100 mil.

Bảng 4-3. Atmel-ICE JTAG Mô tả Pin

| Tên | AVR chân cổng | SAM chân cổng | Sự miêu tả |

| TCK | 1 | 4 | Đồng hồ thử nghiệm (tín hiệu đồng hồ từ Atmel-ICE vào thiết bị mục tiêu). |

| TMS | 5 | 2 | Chọn chế độ kiểm tra (tín hiệu điều khiển từ Atmel-ICE vào thiết bị mục tiêu). |

| TDI | 9 | 8 | Dữ liệu thử nghiệm đầu vào (dữ liệu được truyền từ Atmel-ICE vào thiết bị mục tiêu). |

| TDO | 3 | 6 | Kiểm tra dữ liệu đầu ra (dữ liệu được truyền từ thiết bị mục tiêu vào Atmel-ICE). |

| nTRST | 8 | – | Kiểm tra lại (tùy chọn, chỉ có trên một số thiết bị AVR). Được sử dụng để thiết lập lại JTAG Bộ điều khiển TAP. |

| nSRST | 6 | 10 | Đặt lại (tùy chọn). Được sử dụng để đặt lại thiết bị mục tiêu. Nên kết nối chân này vì nó cho phép Atmel-ICE giữ thiết bị mục tiêu ở trạng thái đặt lại, điều này có thể cần thiết để gỡ lỗi trong một số trường hợp nhất định. |

| VTG | 4 | 1 | Mục tiêu voltage tham khảo. Atmel-ICE samples mục tiêu voltage trên chân này để cấp nguồn cho bộ chuyển đổi mức một cách chính xác. Atmel-ICE rút ít hơn 3mA từ chân này ở chế độ debugWIRE và ít hơn 1mA ở các chế độ khác. |

| GND | 2, 10 | 3, 5, 9 | Đất. Tất cả phải được kết nối để đảm bảo Atmel-ICE và thiết bị mục tiêu có cùng điểm tham chiếu đất. |

4.2.4. Giao diện vật lý SWD

Giao diện ARM SWD là một tập hợp con của JTAG giao diện, sử dụng các chân TCK và TMS. ARM JTAG và AVR JTAG Tuy nhiên, các đầu nối không tương thích với chân cắm, vì vậy khi thiết kế PCB ứng dụng, sử dụng thiết bị SAM với SWD hoặc JTAG giao diện, nên sử dụng chân cắm ARM được hiển thị trong hình bên dưới. Cổng kết nối SAM trên Atmel-ICE có thể kết nối trực tiếp với chân cắm này.

Hình 4-4. ARM SWD/J được đề xuấtTAG Pinout đầu trang

Atmel-ICE có khả năng truyền phát dấu vết ITM định dạng UART đến máy chủ. Dấu vết được ghi lại trên chân TRACE/SWO của đầu cắm 10 chân (JTAG Chân TDO). Dữ liệu được lưu trữ đệm nội bộ trên Atmel-ICE và được gửi qua giao diện HID đến máy chủ. Tốc độ dữ liệu đáng tin cậy tối đa là khoảng 3MB/giây.

4.2.5. Kết nối với mục tiêu SWD

Giao diện ARM SWD là một tập hợp con của JTAG giao diện, sử dụng các chân TCK và TMS, nghĩa là khi kết nối với thiết bị SWD, J 10 chânTAG về mặt kỹ thuật có thể sử dụng đầu nối. ARM JTAG và AVR JTAG Tuy nhiên, các đầu nối không tương thích với chân cắm, do đó điều này phụ thuộc vào cách bố trí của bảng mục tiêu đang sử dụng. Khi sử dụng STK600 hoặc bảng sử dụng AVR JTAG pinout, cổng kết nối AVR trên Atmel-ICE phải được sử dụng. Khi kết nối với bo mạch sử dụng ARM JTAG chân cắm, cổng kết nối SAM trên Atmel-ICE phải được sử dụng.

Sơ đồ chân cắm được đề xuất cho đầu nối Cortex Debug 10 chân được hiển thị trong Hình 4-4.

Kết nối với đầu cắm Cortex 10 chân 50 mil

Sử dụng cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu cắm Cortex 50 mil tiêu chuẩn.

Kết nối với đầu cắm Cortex-layout 10 chân 100 mil

Sử dụng bo mạch điều hợp (có trong một số bộ dụng cụ) để kết nối với chân cắm Cortex 100 mil.

Kết nối với đầu cắm SAM 20 chân 100 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu cắm SAM 20 chân 100 mil.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR hoặc SAM và bo mạch mục tiêu. Cần có sáu kết nối, như mô tả trong bảng bên dưới.

Bảng 4-4. Ánh xạ chân Atmel-ICE SWD

| Tên | AVR chân cổng | SAM chân cổng | Sự miêu tả |

| SWDC LK | 1 | 4 | Đồng hồ gỡ lỗi dây nối tiếp. |

| SWDIO | 5 | 2 | Đầu vào/Đầu ra dữ liệu gỡ lỗi dây nối tiếp. |

| SWO | 3 | 6 | Đầu ra dây nối tiếp (tùy chọn - không được triển khai trên tất cả các thiết bị). |

| nSRST | 6 | 10 | Cài lại. |

| VTG | 4 | 1 | Mục tiêu voltage tham khảo. |

| GND | 2, 10 | 3, 5, 9 | Đất. |

4.2.6 Những cân nhắc đặc biệt

XÓA ghim

Một số thiết bị SAM bao gồm một chân ERASE được khẳng định là thực hiện xóa chip hoàn toàn và mở khóa các thiết bị có bit bảo mật được đặt. Tính năng này được ghép nối với chính thiết bị cũng như bộ điều khiển flash và không phải là một phần của lõi ARM.

Pin ERASE KHÔNG phải là một phần của bất kỳ tiêu đề gỡ lỗi nào và do đó Atmel-ICE không thể khẳng định tín hiệu này để mở khóa thiết bị. Trong những trường hợp như vậy, người dùng nên thực hiện xóa thủ công trước khi bắt đầu phiên gỡ lỗi.

Giao diện vật lý JTAG giao diện

Đường RESET phải luôn được kết nối để Atmel-ICE có thể kích hoạt JTAG giao diện.

Giao diện SWD

Luôn phải kết nối đường RESET để Atmel-ICE có thể kích hoạt giao diện SWD.

4.3 Thiết bị AVR UC3 với JTAG/aDây

Tất cả các thiết bị AVR UC3 đều có JTAG giao diện để lập trình và gỡ lỗi. Ngoài ra, một số thiết bị AVR UC3 có giao diện aWire với chức năng giống hệt nhau khi sử dụng một dây duy nhất. Kiểm tra bảng dữ liệu thiết bị để biết các giao diện được hỗ trợ của thiết bị đó

4.3.1 Hệ thống gỡ lỗi trên chip Atmel AVR UC3

Hệ thống Atmel AVR UC3 OCD được thiết kế theo tiêu chuẩn Nexus 2.0 (IEEE-ISTO 5001™-2003), đây là tiêu chuẩn gỡ lỗi mở trên chip mạnh mẽ và linh hoạt cao dành cho vi điều khiển 32 bit. Nó hỗ trợ các tính năng sau:

- Giải pháp gỡ lỗi tuân thủ Nexus

- OCD hỗ trợ bất kỳ tốc độ CPU nào

- Sáu điểm dừng phần cứng của bộ đếm chương trình

- Hai điểm ngắt dữ liệu

- Điểm dừng có thể được cấu hình như điểm quan sát

- Điểm dừng phần cứng có thể được kết hợp để tạo ra điểm dừng trên phạm vi

- Số lượng điểm dừng chương trình người dùng không giới hạn (sử dụng BREAK)

- Theo dõi nhánh bộ đếm chương trình thời gian thực, theo dõi dữ liệu, theo dõi quy trình (chỉ được hỗ trợ bởi trình gỡ lỗi có cổng chụp theo dõi song song)

Để biết thêm thông tin về hệ thống AVR UC3 OCD, hãy tham khảo Sổ tay tham khảo kỹ thuật AVR32UC, nằm trên www.atmel.com/uc3.

4.3.2.JTAG Giao diện vật lý

Chữ JTAG giao diện bao gồm bộ điều khiển Cổng truy cập thử nghiệm (TAP) 4 dây tuân thủ theo IEEE® Tiêu chuẩn 1149.1. Tiêu chuẩn IEEE được phát triển để cung cấp một cách thức chuẩn công nghiệp để kiểm tra hiệu quả khả năng kết nối của bảng mạch (Quét ranh giới). Các thiết bị Atmel AVR và SAM đã mở rộng chức năng này để bao gồm hỗ trợ Lập trình và Gỡ lỗi trên chip đầy đủ.

Hình 4-5. JTAG Kiến thức cơ bản về giao diện

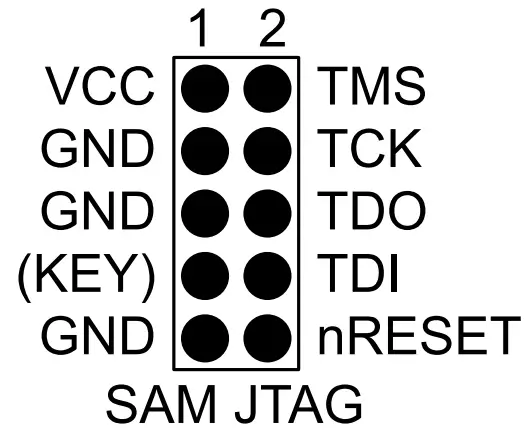

4.3.2.1 AVR JTAG Pinout

Khi thiết kế PCB ứng dụng, bao gồm Atmel AVR với JTAG giao diện, nên sử dụng chân cắm như trong hình bên dưới. Cả hai biến thể 100 mil và 50 mil của chân cắm này đều được hỗ trợ, tùy thuộc vào hệ thống cáp và bộ điều hợp đi kèm với bộ sản phẩm cụ thể.

Hình 4-6. AVR JTAG Pinout đầu trang

Bàn 4-5. AVR JTAG Mô tả Pin

| Tên | Ghim |

Sự miêu tả |

| TCK | 1 | Đồng hồ thử nghiệm (tín hiệu đồng hồ từ Atmel-ICE vào thiết bị mục tiêu). |

| TMS | 5 | Chọn chế độ kiểm tra (tín hiệu điều khiển từ Atmel-ICE vào thiết bị mục tiêu). |

| TDI | 9 | Dữ liệu thử nghiệm đầu vào (dữ liệu được truyền từ Atmel-ICE vào thiết bị mục tiêu). |

| TDO | 3 | Kiểm tra dữ liệu đầu ra (dữ liệu được truyền từ thiết bị mục tiêu vào Atmel-ICE). |

| nTRST | 8 | Kiểm tra lại (tùy chọn, chỉ có trên một số thiết bị AVR). Được sử dụng để thiết lập lại JTAG Bộ điều khiển TAP. |

| nSRST | 6 | Đặt lại (tùy chọn). Được sử dụng để đặt lại thiết bị mục tiêu. Nên kết nối chân này vì nó cho phép Atmel-ICE giữ thiết bị mục tiêu ở trạng thái đặt lại, điều này có thể cần thiết để gỡ lỗi trong một số trường hợp nhất định. |

| VTG | 4 | Mục tiêu voltage tham khảo. Atmel-ICE samples mục tiêu voltage trên chân này để cấp nguồn cho bộ chuyển đổi mức một cách chính xác. Atmel-ICE rút ít hơn 3mA từ chân này ở chế độ debugWIRE và ít hơn 1mA ở các chế độ khác. |

| GND | 2, 10 | Đất. Cả hai phải được kết nối để đảm bảo Atmel-ICE và thiết bị mục tiêu có cùng điểm tham chiếu đất. |

![]() Mẹo: Nhớ lắp tụ điện tách rời giữa chân 4 và GND.

Mẹo: Nhớ lắp tụ điện tách rời giữa chân 4 và GND.

4.3.2.2 JTAG Cúc Chuỗi

Chữ JTAG giao diện cho phép nhiều thiết bị được kết nối với một giao diện duy nhất trong cấu hình chuỗi nối tiếp. Các thiết bị mục tiêu phải được cấp nguồn bởi cùng một vol cung cấptage, chia sẻ một nút đất chung và phải được kết nối như minh họa trong hình bên dưới.

Hình 4-7. JTAG Chuỗi hoa cúc

Khi kết nối các thiết bị theo kiểu chuỗi, cần lưu ý những điểm sau:

- Tất cả các thiết bị phải chia sẻ một mặt đất chung, được kết nối với GND trên đầu dò Atmel-ICE

- Tất cả các thiết bị phải hoạt động trên cùng một vol mục tiêutage. VTG trên Atmel-ICE phải được kết nối với vol nàytage.

- TMS và TCK được kết nối song song; TDI và TDO được kết nối theo chuỗi nối tiếp.

- nSRST trên đầu dò Atmel-ICE phải được kết nối với RESET trên các thiết bị nếu bất kỳ thiết bị nào trong chuỗi vô hiệu hóa J của nóTAG cảng

- “Thiết bị trước” đề cập đến số lượng JTAG các thiết bị mà tín hiệu TDI phải đi qua trong chuỗi liên kết trước khi đến thiết bị mục tiêu. Tương tự như vậy, “thiết bị sau” là số lượng thiết bị mà tín hiệu phải đi qua sau thiết bị mục tiêu trước khi đến Atmel-ICE TDO

- “Các bit hướng dẫn “trước” và “sau” đề cập đến tổng số của tất cả JTAG độ dài thanh ghi lệnh của thiết bị, được kết nối trước và sau thiết bị mục tiêu trong chuỗi nối tiếp

- Tổng chiều dài IR (bit hướng dẫn trước + chiều dài IR của thiết bị mục tiêu Atmel + bit hướng dẫn sau) bị giới hạn ở mức tối đa là 256 bit. Số lượng thiết bị trong chuỗi bị giới hạn ở mức 15 trước và 15 sau.

Mẹo:

Daisy xích lại cũamptập tin: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Để kết nối với Atmel AVR XMEGA® thiết bị, các thiết lập chuỗi nối tiếp là:

- Thiết bị trước: 1

- Thiết bị sau: 1

- Các bit hướng dẫn trước: 4 (các thiết bị AVR 8 bit có 4 bit IR)

- Các bit hướng dẫn sau: 5 (các thiết bị AVR 32 bit có 5 bit IR)

Bảng 4-6. Độ dài IR của Atmel MCUS

| Loại thiết bị | Chiều dài IR |

| AVR 8-bit | 4 bit |

| AVR 32-bit | 5 bit |

| SAM | 4 bit |

4.3.3.Kết nối với JTAG Mục tiêu

Atmel-ICE được trang bị hai chân cắm J 50 mil 10 chânTAG đầu nối. Cả hai đầu nối đều được kết nối điện trực tiếp, nhưng tuân theo hai chân cắm khác nhau; AVR JTAG header và header ARM Cortex Debug. Đầu nối phải được chọn dựa trên chân cắm của bo mạch đích chứ không phải loại MCU đích – ví dụampthiết bị SAM được gắn trong ngăn xếp AVR STK600 phải sử dụng đầu cắm AVR.

Pinout được đề xuất cho AVR J 10 chânTAG Đầu nối được thể hiện ở Hình 4-6.

Sơ đồ chân cắm được đề xuất cho đầu nối ARM Cortex Debug 10 chân được hiển thị trong Hình 4-2.

Kết nối trực tiếp với đầu cắm 10 chân 50 mil tiêu chuẩn

Sử dụng cáp dẹt 50-mil 10 chân (có trong một số bộ sản phẩm) để kết nối trực tiếp với bo mạch hỗ trợ loại chân cắm này. Sử dụng cổng kết nối AVR trên Atmel-ICE cho các chân cắm có chân cắm AVR và cổng kết nối SAM cho các chân cắm tuân thủ chân cắm chân cắm ARM Cortex Debug.

Sơ đồ chân cắm cho cả hai cổng kết nối 10 chân được hiển thị bên dưới.

Kết nối với đầu cắm 10 chân 100 mil tiêu chuẩn

Sử dụng bộ chuyển đổi chuẩn 50 mil sang 100 mil để kết nối với đầu cắm 100 mil. Có thể sử dụng bảng chuyển đổi (có trong một số bộ dụng cụ) cho mục đích này hoặc thay thế bằng JTAGBộ điều hợp ICE3 có thể được sử dụng cho mục tiêu AVR.

![]() Quan trọng:

Quan trọng:

Chữ JTAGKhông thể sử dụng bộ chuyển đổi ICE3 100-mil với cổng kết nối SAM vì chân 2 và 10 (AVR GND) trên bộ chuyển đổi được kết nối.

Kết nối với đầu nối 100 mil tùy chỉnh

Nếu bo mạch mục tiêu của bạn không có đầu nối J 10 chân tương thíchTAG tiêu đề ở mức 50 hoặc 100 mil, bạn có thể ánh xạ tới một chân cắm tùy chỉnh bằng cáp “mini-squid” 10 chân (có trong một số bộ dụng cụ), cho phép truy cập vào mười ổ cắm 100 mil riêng lẻ.

Kết nối với đầu cắm 20 chân 100 mil

Sử dụng bảng chuyển đổi (có trong một số bộ dụng cụ) để kết nối với mục tiêu có đầu cắm 20 chân 100 mil.

Bảng 4-7. Atmel-ICE JTAG Mô tả Pin

|

Tên |

Chân cổng AVR | Chân cổng SAM |

Sự miêu tả |

| TCK | 1 | 4 | Đồng hồ thử nghiệm (tín hiệu đồng hồ từ Atmel-ICE vào thiết bị mục tiêu). |

| TMS | 5 | 2 | Chọn chế độ kiểm tra (tín hiệu điều khiển từ Atmel-ICE vào thiết bị mục tiêu). |

| TDI | 9 | 8 | Dữ liệu thử nghiệm đầu vào (dữ liệu được truyền từ Atmel-ICE vào thiết bị mục tiêu). |

| TDO | 3 | 6 | Kiểm tra dữ liệu đầu ra (dữ liệu được truyền từ thiết bị mục tiêu vào Atmel-ICE). |

| nTRST | 8 | – | Kiểm tra lại (tùy chọn, chỉ có trên một số thiết bị AVR). Được sử dụng để thiết lập lại JTAG Bộ điều khiển TAP. |

| nSRST | 6 | 10 | Đặt lại (tùy chọn). Được sử dụng để đặt lại thiết bị mục tiêu. Nên kết nối chân này vì nó cho phép Atmel-ICE giữ thiết bị mục tiêu ở trạng thái đặt lại, điều này có thể cần thiết để gỡ lỗi trong một số trường hợp nhất định. |

| VTG | 4 | 1 | Mục tiêu voltage tham khảo. Atmel-ICE samples mục tiêu voltage trên chân này để cấp nguồn cho bộ chuyển đổi mức một cách chính xác. Atmel-ICE rút ít hơn 3mA từ chân này ở chế độ debugWIRE và ít hơn 1mA ở các chế độ khác. |

| GND | 2, 10 | 3, 5, 9 | Đất. Tất cả phải được kết nối để đảm bảo Atmel-ICE và thiết bị mục tiêu có cùng điểm tham chiếu đất. |

4.3.4 Giao diện vật lý aWire

Giao diện aWire sử dụng dây RESET của thiết bị AVR để cho phép lập trình và gỡ lỗi các chức năng. Một chuỗi kích hoạt đặc biệt được truyền đi bởi Atmel-ICE, vô hiệu hóa chức năng RESET mặc định của chân. Khi thiết kế PCB ứng dụng, bao gồm Atmel AVR với giao diện aWire, nên sử dụng chân cắm như thể hiện trong Hình 4-8. Cả hai biến thể 100-mil và 50-mil của chân cắm này đều được hỗ trợ, tùy thuộc vào hệ thống cáp và bộ điều hợp đi kèm với bộ sản phẩm cụ thể.

Hình 4-8. Sơ đồ chân tiêu đề aWire

![]() Mẹo:

Mẹo:

Vì aWire là giao diện bán song công nên nên sử dụng điện trở kéo lên trên đường RESET theo thứ tự 47kΩ để tránh phát hiện bit bắt đầu sai khi thay đổi hướng.

Giao diện aWire có thể được sử dụng như một giao diện lập trình và gỡ lỗi. Tất cả các tính năng của hệ thống OCD đều có sẵn thông qua J 10 chânTAG Giao diện cũng có thể được truy cập bằng aWire.

4.3.5 Kết nối với mục tiêu aWire

Giao diện aWire chỉ yêu cầu một đường dữ liệu ngoài VCC và GND. Trên mục tiêu dòng này là dòng nRESET, mặc dù trình gỡ lỗi sử dụng JTAG Đường TDO đóng vai trò là đường dữ liệu.

Sơ đồ chân cắm được khuyến nghị cho đầu nối aWire 6 chân được hiển thị trong Hình 4-8.

Kết nối với đầu cắm aWire 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối aWire 100 mil tiêu chuẩn.

Kết nối với đầu cắm aWire 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ sản phẩm) để kết nối với đầu nối aWire 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có ba kết nối, như mô tả trong bảng bên dưới.

Bảng 4-8. Ánh xạ chân Atmel-ICE aWire

| Chân cổng Atmel-ICE AVR | Ghim mục tiêu | Mini-mực pin |

aPinout dây |

| Chân 1 (TCK) | 1 | ||

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | DỮ LIỆU | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 | ||

| Chân 6 (nSRST) | 6 | ||

| Pin 7 (Không kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | 9 | ||

| Chân 10 (GND) | 0 |

4.3.6. Những cân nhắc đặc biệt

JTAG giao diện

Trên một số thiết bị Atmel AVR UC3, JTAG cổng không được bật theo mặc định. Khi sử dụng các thiết bị này, điều cần thiết là phải kết nối đường RESET để Atmel-ICE có thể bật JTAG giao diện.

Giao diện aWire

Tốc độ truyền dữ liệu của aWire phụ thuộc vào tần số của đồng hồ hệ thống, vì dữ liệu phải được đồng bộ giữa hai miền này. Atmel-ICE sẽ tự động phát hiện rằng đồng hồ hệ thống đã bị hạ thấp và hiệu chuẩn lại tốc độ truyền dữ liệu của nó cho phù hợp. Hiệu chuẩn tự động chỉ hoạt động ở tần số đồng hồ hệ thống là 8kHz. Việc chuyển sang đồng hồ hệ thống thấp hơn trong phiên gỡ lỗi có thể khiến mất liên lạc với mục tiêu.

Nếu cần, tốc độ truyền aWire có thể bị hạn chế bằng cách thiết lập tham số đồng hồ aWire. Phát hiện tự động vẫn hoạt động, nhưng giá trị trần sẽ được áp dụng cho kết quả.

Bất kỳ tụ điện ổn định nào được kết nối với chân RESET đều phải được ngắt kết nối khi sử dụng aWire vì nó sẽ ảnh hưởng đến hoạt động chính xác của giao diện. Nên sử dụng điện áp kéo lên bên ngoài yếu (10kΩ trở lên) trên đường dây này.

Tắt chế độ ngủ

Một số thiết bị AVR UC3 có bộ điều chỉnh bên trong có thể sử dụng ở chế độ cung cấp 3.3V với các đường I/O được điều chỉnh 1.8V. Điều này có nghĩa là bộ điều chỉnh bên trong cấp nguồn cho cả lõi và hầu hết các I/O. Chỉ có trình gỡ lỗi Atmel AVR ONE! hỗ trợ gỡ lỗi trong khi sử dụng chế độ ngủ khi bộ điều chỉnh này bị tắt.

4.3.7. Sử dụng EVTI / EVTO

Các chân EVTI và EVTO không thể truy cập được trên Atmel-ICE. Tuy nhiên, chúng vẫn có thể được sử dụng kết hợp với các thiết bị bên ngoài khác.

EVTI có thể được sử dụng cho các mục đích sau:

- Mục tiêu có thể bị buộc dừng thực thi để phản hồi sự kiện bên ngoài. Nếu các bit Event In Control (EIC) trong thanh ghi DC được ghi vào 0b01, quá trình chuyển đổi từ cao xuống thấp trên chân EVTI sẽ tạo ra điều kiện điểm dừng. EVTI phải duy trì ở mức thấp trong một chu kỳ xung nhịp CPU để đảm bảo rằng điểm dừng là Bit External Breakpoint (EXB) trong DS được đặt khi điều này xảy ra.

- Tạo tin nhắn đồng bộ hóa theo dõi. Không được Atmel-ICE sử dụng.

EVTO có thể được sử dụng cho các mục đích sau:

- Chỉ ra rằng CPU đã vào chế độ gỡ lỗi. Đặt bit EOS trong DC thành 0b01 khiến chân EVTO bị kéo xuống mức thấp trong một chu kỳ xung nhịp CPU khi thiết bị mục tiêu vào chế độ gỡ lỗi. Tín hiệu này có thể được sử dụng làm nguồn kích hoạt cho máy hiện sóng ngoài.

- Chỉ ra rằng CPU đã đạt đến điểm dừng hoặc điểm quan sát. Bằng cách đặt bit EOC trong Thanh ghi điều khiển điểm dừng/điểm quan sát tương ứng, trạng thái điểm dừng hoặc điểm quan sát được chỉ ra trên chân EVTO. Các bit EOS trong DC phải được đặt thành 0xb10 để bật tính năng này. Sau đó, chân EVTO có thể được kết nối với máy hiện sóng ngoài để kiểm tra điểm quan sát

- Tạo tín hiệu thời gian theo dõi. Không được Atmel-ICE sử dụng.

4.4 Thiết bị tinyAVR, megaAVR và XMEGA

Thiết bị AVR có nhiều giao diện lập trình và gỡ lỗi khác nhau. Kiểm tra bảng dữ liệu thiết bị để biết các giao diện được hỗ trợ của thiết bị đó.

- Một số tinyAVR® thiết bị có TPI TPI chỉ có thể được sử dụng để lập trình thiết bị và các thiết bị này không có khả năng gỡ lỗi trên chip.

- Một số thiết bị tinyAVR và một số thiết bị megaAVR có giao diện debugWIRE, kết nối với hệ thống gỡ lỗi trên chip được gọi là tinyOCD. Tất cả các thiết bị có debugWIRE cũng có giao diện SPI cho hệ thống

- Một số thiết bị megaAVR có JTAG giao diện để lập trình và gỡ lỗi, với hệ thống gỡ lỗi trên chip còn được gọi là Tất cả các thiết bị có JTAG cũng có giao diện SPI như một giao diện thay thế cho lập trình trong hệ thống.

- Tất cả các thiết bị AVR XMEGA đều có giao diện PDI để lập trình và một số thiết bị AVR XMEGA cũng có JTAG giao diện có chức năng giống hệt nhau.

- Các thiết bị tinyAVR mới có giao diện UPDI, được sử dụng để lập trình và gỡ lỗi

Bảng 4-9. Tóm tắt giao diện lập trình và gỡ lỗi

|

|

CẬP NHẬT | TPI | SPI | gỡ lỗiWIR E | JTAG | PDI | aDây |

Tây Nam |

| tinyAVR | Thiết bị mới | Một số thiết bị | Một số thiết bị | Một số thiết bị | ||||

| megaAV R | Tất cả các thiết bị | Một số thiết bị | Một số thiết bị | |||||

| AVR XMEGA | Một số thiết bị | Tất cả các thiết bị | ||||||

| AVR-UC | Tất cả các thiết bị | Một số thiết bị | ||||||

| SAM | Một số thiết bị | Tất cả các thiết bị |

4.4.1.JTAG Giao diện vật lý

Chữ JTAG giao diện bao gồm bộ điều khiển Cổng truy cập thử nghiệm (TAP) 4 dây tuân thủ theo IEEE® Tiêu chuẩn 1149.1. Tiêu chuẩn IEEE được phát triển để cung cấp một cách thức chuẩn công nghiệp để kiểm tra hiệu quả khả năng kết nối của bảng mạch (Quét ranh giới). Các thiết bị Atmel AVR và SAM đã mở rộng chức năng này để bao gồm hỗ trợ Lập trình và Gỡ lỗi trên chip đầy đủ.

Hình 4-9. JTAG Kiến thức cơ bản về giao diện 4.4.2. Kết nối với JTAG Mục tiêu

4.4.2. Kết nối với JTAG Mục tiêu

Atmel-ICE được trang bị hai chân cắm J 50 mil 10 chânTAG đầu nối. Cả hai đầu nối đều được kết nối điện trực tiếp, nhưng tuân theo hai chân cắm khác nhau; AVR JTAG header và header ARM Cortex Debug. Đầu nối phải được chọn dựa trên chân cắm của bo mạch đích chứ không phải loại MCU đích – ví dụampthiết bị SAM được gắn trong ngăn xếp AVR STK600 phải sử dụng đầu cắm AVR.

Pinout được đề xuất cho AVR J 10 chânTAG Đầu nối được thể hiện ở Hình 4-6.

Sơ đồ chân cắm được đề xuất cho đầu nối ARM Cortex Debug 10 chân được hiển thị trong Hình 4-2.

Kết nối trực tiếp với đầu cắm 10 chân 50 mil tiêu chuẩn

Sử dụng cáp dẹt 50-mil 10 chân (có trong một số bộ sản phẩm) để kết nối trực tiếp với bo mạch hỗ trợ loại chân cắm này. Sử dụng cổng kết nối AVR trên Atmel-ICE cho các chân cắm có chân cắm AVR và cổng kết nối SAM cho các chân cắm tuân thủ chân cắm chân cắm ARM Cortex Debug.

Sơ đồ chân cắm cho cả hai cổng kết nối 10 chân được hiển thị bên dưới.

Kết nối với đầu cắm 10 chân 100 mil tiêu chuẩn

Sử dụng bộ chuyển đổi chuẩn 50 mil sang 100 mil để kết nối với đầu cắm 100 mil. Có thể sử dụng bảng chuyển đổi (có trong một số bộ dụng cụ) cho mục đích này hoặc thay thế bằng JTAGBộ điều hợp ICE3 có thể được sử dụng cho mục tiêu AVR.

![]() Quan trọng:

Quan trọng:

Chữ JTAGKhông thể sử dụng bộ chuyển đổi ICE3 100-mil với cổng kết nối SAM vì chân 2 và 10 (AVR GND) trên bộ chuyển đổi được kết nối.

Kết nối với đầu nối 100 mil tùy chỉnh

Nếu bo mạch mục tiêu của bạn không có đầu nối J 10 chân tương thíchTAG tiêu đề ở mức 50 hoặc 100 mil, bạn có thể ánh xạ tới một chân cắm tùy chỉnh bằng cáp “mini-squid” 10 chân (có trong một số bộ dụng cụ), cho phép truy cập vào mười ổ cắm 100 mil riêng lẻ.

Kết nối với đầu cắm 20 chân 100 mil

Sử dụng bảng chuyển đổi (có trong một số bộ dụng cụ) để kết nối với mục tiêu có đầu cắm 20 chân 100 mil.

Bảng 4-10. Atmel-ICE JTAG Mô tả Pin

| Tên | AVR chân cổng | SAM chân cổng | Sự miêu tả |

| TCK | 1 | 4 | Đồng hồ thử nghiệm (tín hiệu đồng hồ từ Atmel-ICE vào thiết bị mục tiêu). |

| TMS | 5 | 2 | Chọn chế độ kiểm tra (tín hiệu điều khiển từ Atmel-ICE vào thiết bị mục tiêu). |

| TDI | 9 | 8 | Dữ liệu thử nghiệm đầu vào (dữ liệu được truyền từ Atmel-ICE vào thiết bị mục tiêu). |

| TDO | 3 | 6 | Kiểm tra dữ liệu đầu ra (dữ liệu được truyền từ thiết bị mục tiêu vào Atmel-ICE). |

| nTRST | 8 | – | Kiểm tra lại (tùy chọn, chỉ có trên một số thiết bị AVR). Được sử dụng để thiết lập lại JTAG Bộ điều khiển TAP. |

| nSRST | 6 | 10 | Đặt lại (tùy chọn). Được sử dụng để đặt lại thiết bị mục tiêu. Nên kết nối chân này vì nó cho phép Atmel-ICE giữ thiết bị mục tiêu ở trạng thái đặt lại, điều này có thể cần thiết để gỡ lỗi trong một số trường hợp nhất định. |

| VTG | 4 | 1 | Mục tiêu voltage tham khảo. Atmel-ICE samples mục tiêu voltage trên chân này để cấp nguồn cho bộ chuyển đổi mức một cách chính xác. Atmel-ICE rút ít hơn 3mA từ chân này ở chế độ debugWIRE và ít hơn 1mA ở các chế độ khác. |

| GND | 2, 10 | 3, 5, 9 | Đất. Tất cả phải được kết nối để đảm bảo Atmel-ICE và thiết bị mục tiêu có cùng điểm tham chiếu đất. |

4.4.3. Giao diện vật lý SPI

Lập trình trong hệ thống sử dụng SPI (Giao diện ngoại vi nối tiếp) bên trong của Atmel AVR mục tiêu để tải mã vào bộ nhớ flash và EEPROM. Đây không phải là giao diện gỡ lỗi. Khi thiết kế PCB ứng dụng, bao gồm AVR có giao diện SPI, nên sử dụng sơ đồ chân như trong hình bên dưới.

Hình 4-10. Sơ đồ chân cắm đầu cắm SPI 4.4.4. Kết nối với mục tiêu SPI

4.4.4. Kết nối với mục tiêu SPI

Sơ đồ chân cắm được khuyến nghị cho đầu nối SPI 6 chân được hiển thị trong Hình 4-10.

Kết nối với đầu cắm SPI 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối SPI 100 mil tiêu chuẩn.

Kết nối với đầu cắm SPI 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu cắm SPI 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có sáu kết nối, như mô tả trong bảng bên dưới.

![]() Quan trọng:

Quan trọng:

Giao diện SPI bị vô hiệu hóa hiệu quả khi cầu chì kích hoạt debugWIRE (DWEN) được lập trình, ngay cả khi cầu chì SPIEN cũng được lập trình. Để kích hoạt lại giao diện SPI, lệnh 'vô hiệu hóa debugWIRE' phải được đưa ra trong khi đang trong phiên gỡ lỗi debugWIRE. Việc vô hiệu hóa debugWIRE theo cách này yêu cầu cầu chì SPIEN đã được lập trình. Nếu Atmel Studio không vô hiệu hóa debugWIRE, thì có thể là do cầu chì SPIEN KHÔNG được lập trình. Nếu đúng như vậy, thì cần phải sử dụng mộttagGiao diện lập trình e để lập trình cầu chì SPIEN.

![]() Thông tin:

Thông tin:

Giao diện SPI thường được gọi là “ISP”, vì đây là giao diện Lập trình Trong Hệ thống đầu tiên trên các sản phẩm Atmel AVR. Các giao diện khác hiện có sẵn cho Lập trình Trong Hệ thống.

Bảng 4-11. Ánh xạ chân SPI Atmel-ICE

| Chân cổng Atmel-ICE AVR | Ghim mục tiêu | Mini-mực pin |

Chân cắm SPI |

| Chân 1 (TCK) | SCK | 1 | 3 |

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | MISO | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 | ||

| Chân 6 (nSRST) | /CÀI LẠI | 6 | 5 |

| Pin 7 (không được kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | DAWDLE | 9 | 4 |

| Chân 10 (GND) | 0 |

4.4.5.DỰ ÁN

Giao diện lập trình và gỡ lỗi (PDI) là giao diện độc quyền của Atmel để lập trình bên ngoài và gỡ lỗi trên chip của thiết bị. PDI vật lý là giao diện 2 chân cung cấp giao tiếp đồng bộ bán song công hai chiều với thiết bị mục tiêu.

Khi thiết kế PCB ứng dụng, bao gồm Atmel AVR với giao diện PDI, nên sử dụng chân cắm được hiển thị trong hình bên dưới. Một trong các bộ chuyển đổi 6 chân được cung cấp cùng với bộ Atmel-ICE sau đó có thể được sử dụng để kết nối đầu dò Atmel-ICE với PCB ứng dụng.

Hình 4-11. Chân cắm tiêu đề PDI 4.4.6.Kết nối với mục tiêu PDI

4.4.6.Kết nối với mục tiêu PDI

Sơ đồ chân cắm được khuyến nghị cho đầu nối PDI 6 chân được hiển thị trong Hình 4-11.

Kết nối với đầu cắm PDI 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối PDI 100 mil tiêu chuẩn.

Kết nối với đầu cắm PDI 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu cắm PDI 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có bốn kết nối, như mô tả trong bảng bên dưới.

![]() Quan trọng:

Quan trọng:

Pinout yêu cầu khác với JTAGICE mkII JTAG đầu dò, trong đó PDI_DATA được kết nối với chân 9. Atmel-ICE tương thích với chân cắm được sử dụng bởi Atmel-ICE, JTAGICE3, AVR ONE!, và AVR Dragon™ các sản phẩm.

Bảng 4-12. Ánh xạ chân Atmel-ICE PDI

|

Chân cổng Atmel-ICE AVR |

Ghim mục tiêu | Mini-mực pin |

Sơ đồ chân cắm PDI của Atmel STK600 |

| Chân 1 (TCK) | 1 | ||

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | DỮ LIỆU PDI | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 | ||

| Chân 6 (nSRST) | PDI_CLK | 6 | 5 |

| Pin 7 (không được kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | 9 | ||

| Chân 10 (GND) | 0 |

4.4.7. Giao diện vật lý UPDI

Unified Program and Debug Interface (UPDI) là giao diện độc quyền của Atmel để lập trình bên ngoài và gỡ lỗi trên chip của thiết bị. Đây là giao diện kế thừa của giao diện vật lý 2 dây PDI, có trên tất cả các thiết bị AVR XMEGA. UPDI là giao diện một dây cung cấp giao tiếp không đồng bộ bán song công hai chiều với thiết bị mục tiêu cho mục đích lập trình và gỡ lỗi.

Khi thiết kế PCB ứng dụng, bao gồm Atmel AVR với giao diện UPDI, nên sử dụng sơ đồ chân cắm được hiển thị bên dưới. Một trong những bộ chuyển đổi 6 chân được cung cấp cùng với bộ Atmel-ICE sau đó có thể được sử dụng để kết nối đầu dò Atmel-ICE với PCB ứng dụng.

Hình 4-12. Chân cắm tiêu đề UPDI 4.4.7.1 UPDI và /RESET

4.4.7.1 UPDI và /RESET

Giao diện một dây UPDI có thể là chân chuyên dụng hoặc chân dùng chung, tùy thuộc vào thiết bị AVR mục tiêu. Tham khảo bảng dữ liệu thiết bị để biết thêm thông tin.

Khi giao diện UPDI nằm trên một chân chia sẻ, chân đó có thể được cấu hình là UPDI, /RESET hoặc GPIO bằng cách đặt cầu chì RSTPINCFG[1:0].

Cầu chì RSTPINCFG[1:0] có các cấu hình sau, như được mô tả trong bảng dữ liệu. Các hàm ý thực tế của từng lựa chọn được đưa ra ở đây.

Bảng 4-13. Cấu hình cầu chì RSTPINCFG[1:0]

| RSTPINCFG[1:0] | Cấu hình |

Cách sử dụng |

| 00 | GPIO | Pin I/O mục đích chung. Để truy cập UPDI, xung 12V phải được áp dụng cho pin này. Không có nguồn đặt lại bên ngoài nào khả dụng. |

| 01 | CẬP NHẬT | Pin lập trình và gỡ lỗi chuyên dụng. Không có nguồn reset bên ngoài nào khả dụng. |

| 10 | Cài lại | Thiết lập lại tín hiệu đầu vào. Để truy cập UPDI, xung 12V phải được áp dụng cho chân này. |

| 11 | Kín đáo | NA |

Ghi chú: Các thiết bị AVR cũ hơn có giao diện lập trình được gọi là “High-Voltage Lập trình” (cả hai biến thể nối tiếp và song song đều tồn tại.) Nhìn chung, giao diện này yêu cầu phải cấp 12V cho chân /RESET trong suốt thời gian của phiên lập trình. Giao diện UPDI là một giao diện hoàn toàn khác. Chân UPDI chủ yếu là chân lập trình và gỡ lỗi, có thể được hợp nhất để có chức năng thay thế (/RESET hoặc GPIO). Nếu chức năng thay thế được chọn thì cần có xung 12V trên chân đó để kích hoạt lại chức năng UPDI.

Ghi chú: Nếu một thiết kế yêu cầu chia sẻ tín hiệu UPDI do hạn chế chân cắm, các bước phải được thực hiện để đảm bảo rằng thiết bị có thể được lập trình. Để đảm bảo rằng tín hiệu UPDI có thể hoạt động chính xác, cũng như để tránh làm hỏng các thành phần bên ngoài từ xung 12V, nên ngắt kết nối bất kỳ thành phần nào trên chân cắm này khi cố gắng gỡ lỗi hoặc lập trình thiết bị. Điều này có thể được thực hiện bằng cách sử dụng điện trở 0Ω, được gắn theo mặc định và được tháo ra hoặc thay thế bằng một đầu cắm chân cắm trong khi gỡ lỗi. Cấu hình này có nghĩa là lập trình phải được thực hiện trước khi gắn thiết bị.

![]() Quan trọng: Atmel-ICE không hỗ trợ 12V trên đường UPDI. Nói cách khác, nếu chân UPDI đã được cấu hình là GPIO hoặc RESET thì Atmel-ICE sẽ không thể bật giao diện UPDI.

Quan trọng: Atmel-ICE không hỗ trợ 12V trên đường UPDI. Nói cách khác, nếu chân UPDI đã được cấu hình là GPIO hoặc RESET thì Atmel-ICE sẽ không thể bật giao diện UPDI.

4.4.8.Kết nối với mục tiêu UPDI

Sơ đồ chân cắm được khuyến nghị cho đầu nối UPDI 6 chân được hiển thị trong Hình 4-12.

Kết nối với đầu cắm UPDI 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối UPDI 100 mil tiêu chuẩn.

Kết nối với đầu cắm UPDI 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu cắm UPDI 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có ba kết nối, như mô tả trong bảng bên dưới.

Bảng 4-14. Ánh xạ chân Atmel-ICE UPDI

| Chân cổng Atmel-ICE AVR | Ghim mục tiêu | Mini-mực pin |

Sơ đồ chân Atmel STK600 UPDI |

| Chân 1 (TCK) | 1 | ||

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | DỮ LIỆU CẬP NHẬT | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 | ||

| Chân 6 (nSRST) | [/RESET cảm giác] | 6 | 5 |

| Pin 7 (Không kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | 9 | ||

| Chân 10 (GND) | 0 |

4.4.9 Giao diện vật lý TPI

TPI là giao diện chỉ dành cho lập trình đối với một số thiết bị AVR ATtiny. Đây không phải là giao diện gỡ lỗi và các thiết bị này không có khả năng OCD. Khi thiết kế PCB ứng dụng bao gồm AVR có giao diện TPI, nên sử dụng sơ đồ chân được hiển thị trong hình bên dưới.

Hình 4-13. Chân cắm đầu cắm TPI 4.4.10.Kết nối với mục tiêu TPI

4.4.10.Kết nối với mục tiêu TPI

Sơ đồ chân cắm được khuyến nghị cho đầu nối TPI 6 chân được hiển thị trong Hình 4-13.

Kết nối với đầu cắm TPI 6 chân 100 mil

Sử dụng đầu nối 6 chân 100 mil trên cáp dẹt (có trong một số bộ sản phẩm) để kết nối với đầu nối TPI 100 mil tiêu chuẩn.

Kết nối với đầu cắm TPI 6 chân 50 mil

Sử dụng bo mạch chuyển đổi (có trong một số bộ dụng cụ) để kết nối với đầu nối TPI 50 mil tiêu chuẩn.

Kết nối với đầu nối 100 mil tùy chỉnh

Cáp mini-squid 10 chân phải được sử dụng để kết nối giữa cổng kết nối Atmel-ICE AVR và bo mạch mục tiêu. Cần có sáu kết nối, như mô tả trong bảng bên dưới.

Bảng 4-15. Ánh xạ chân TPI Atmel-ICE

| Chân cổng Atmel-ICE AVR | Ghim mục tiêu | Mini-mực pin |

Chân cắm TPI |

| Chân 1 (TCK) | CÁI ĐỒNG HỒ | 1 | 3 |

| Chân 2 (GND) | GND | 2 | 6 |

| Chân 3 (TDO) | DỮ LIỆU | 3 | 1 |

| Chân 4 (VTG) | VTG | 4 | 2 |

| Chân 5 (TMS) | 5 | ||

| Chân 6 (nSRST) | /CÀI LẠI | 6 | 5 |

| Pin 7 (không được kết nối) | 7 | ||

| Chân 8 (nTRST) | 8 | ||

| Chân 9 (TDI) | 9 | ||

| Chân 10 (GND) | 0 |

4.4.11. Gỡ lỗi nâng cao (AVR JTAG /thiết bị debugWIRE)

Thiết bị ngoại vi I/O

Hầu hết các thiết bị ngoại vi I/O sẽ tiếp tục chạy ngay cả khi chương trình thực thi bị dừng lại bởi điểm dừng. Ví dụample: Nếu đạt đến điểm dừng trong quá trình truyền UART, quá trình truyền sẽ hoàn tất và các bit tương ứng được đặt. Cờ TXC (truyền hoàn tất) sẽ được đặt và khả dụng ở bước tiếp theo của mã mặc dù thông thường nó sẽ xảy ra sau đó trong một thiết bị thực tế.

Tất cả các mô-đun I/O sẽ tiếp tục chạy ở chế độ dừng với hai ngoại lệ sau:

- Bộ đếm/Bộ hẹn giờ (có thể cấu hình bằng phần mềm front-end)

- Bộ đếm thời gian giám sát (luôn dừng lại để ngăn chặn việc thiết lập lại trong quá trình gỡ lỗi)

Truy cập I/O bước đơn

Vì I/O tiếp tục chạy ở chế độ dừng nên cần cẩn thận để tránh một số vấn đề về thời gian. Ví dụample, mã:

Khi chạy mã này bình thường, thanh ghi TEMP sẽ không đọc lại 0xAA vì dữ liệu vẫn chưa được chốt vật lý vào chân cắm vào thời điểm nó được sampđược dẫn dắt bởi thao tác IN. Một lệnh NOP phải được đặt giữa lệnh OUT và lệnh IN để đảm bảo giá trị chính xác có trong thanh ghi PIN.

Tuy nhiên, khi thực hiện từng bước chức năng này thông qua OCD, mã này sẽ luôn đưa ra 0xAA trong thanh ghi PIN vì I/O vẫn chạy ở tốc độ tối đa ngay cả khi lõi dừng trong quá trình thực hiện từng bước.

Bước đơn và thời gian

Một số thanh ghi nhất định cần được đọc hoặc ghi trong một số chu kỳ nhất định sau khi bật tín hiệu điều khiển. Vì đồng hồ I/O và các thiết bị ngoại vi tiếp tục chạy ở tốc độ tối đa ở chế độ dừng, nên việc thực hiện từng bước qua mã như vậy sẽ không đáp ứng được các yêu cầu về thời gian. Giữa hai bước đơn lẻ, đồng hồ I/O có thể đã chạy hàng triệu chu kỳ. Để đọc hoặc ghi thành công các thanh ghi với các yêu cầu về thời gian như vậy, toàn bộ chuỗi đọc hoặc ghi phải được thực hiện như một hoạt động nguyên tử chạy thiết bị ở tốc độ tối đa. Điều này có thể được thực hiện bằng cách sử dụng macro hoặc lệnh gọi hàm để thực thi mã hoặc sử dụng hàm chạy đến con trỏ trong môi trường gỡ lỗi

Truy cập vào các thanh ghi 16 bit

Thiết bị ngoại vi Atmel AVR thường chứa một số thanh ghi 16 bit có thể truy cập qua bus dữ liệu 8 bit (ví dụ: TCNTn của bộ đếm thời gian 16 bit). Thanh ghi 16 bit phải được truy cập theo byte bằng hai thao tác đọc hoặc ghi. Việc ngắt giữa chừng khi truy cập 16 bit hoặc thực hiện một bước duy nhất trong tình huống này có thể dẫn đến các giá trị sai.

Quyền truy cập thanh ghi I/O bị hạn chế

Một số thanh ghi không thể đọc được mà không ảnh hưởng đến nội dung của chúng. Các thanh ghi như vậy bao gồm các thanh ghi chứa cờ được xóa khi đọc hoặc các thanh ghi dữ liệu đệm (ví dụ: UDR). Giao diện phần mềm sẽ ngăn không cho đọc các thanh ghi này khi ở chế độ dừng để bảo toàn bản chất không xâm lấn theo ý định của việc gỡ lỗi OCD. Ngoài ra, một số thanh ghi không thể được ghi một cách an toàn mà không xảy ra tác dụng phụ – các thanh ghi này chỉ đọc. Ví dụamplê:

- Thanh ghi cờ, trong đó cờ được xóa bằng cách ghi '1' vào bất kỳ Thanh ghi này chỉ đọc.

- Các thanh ghi UDR và SPDR không thể được đọc mà không ảnh hưởng đến trạng thái của mô-đun. Các thanh ghi này không

4.4.12. Những cân nhắc đặc biệt về megaAVR

Điểm dừng phần mềm

Vì nó chứa phiên bản đầu của mô-đun OCD nên ATmega128[A] không hỗ trợ việc sử dụng lệnh BREAK cho điểm dừng phần mềm.

JTAG cái đồng hồ

Tần số xung nhịp mục tiêu phải được chỉ định chính xác trong giao diện phần mềm trước khi bắt đầu phiên gỡ lỗi. Vì lý do đồng bộ hóa, JTAG Tín hiệu TCK phải nhỏ hơn một phần tư tần số xung nhịp mục tiêu để gỡ lỗi đáng tin cậy. Khi lập trình thông qua JTAG giao diện, tần số TCK bị giới hạn bởi tần số định mức tối đa của thiết bị mục tiêu chứ không phải tần số xung nhịp thực tế đang được sử dụng.

Khi sử dụng bộ dao động RC bên trong, hãy lưu ý rằng tần số có thể thay đổi tùy theo thiết bị và bị ảnh hưởng bởi nhiệt độ và VCC thay đổi. Hãy thận trọng khi chỉ định tần số xung nhịp mục tiêu.

JTAGCầu chì EN và OCDEN

Chữ JTAG giao diện được kích hoạt bằng cách sử dụng JTAGEN fuse, được lập trình theo mặc định. Điều này cho phép truy cập vào JTAG giao diện lập trình. Thông qua cơ chế này, cầu chì OCDEN có thể được lập trình (mặc định OCDEN không được lập trình). Điều này cho phép truy cập vào OCD để tạo điều kiện gỡ lỗi thiết bị. Giao diện phần mềm sẽ luôn đảm bảo rằng cầu chì OCDEN không được lập trình khi kết thúc phiên, do đó hạn chế mức tiêu thụ điện năng không cần thiết của mô-đun OCD. Nếu JTAGCầu chì EN bị vô tình tắt, chỉ có thể bật lại bằng SPI hoặc High Voltagphương pháp lập trình e.

Nếu JTAGCầu chì EN được lập trình, JTAG giao diện vẫn có thể bị vô hiệu hóa trong chương trình cơ sở bằng cách thiết lập bit JTD. Điều này sẽ khiến mã không thể gỡ lỗi và không nên thực hiện khi cố gắng thực hiện phiên gỡ lỗi. Nếu mã như vậy đã được thực thi trên thiết bị Atmel AVR khi bắt đầu phiên gỡ lỗi, Atmel-ICE sẽ khẳng định đường RESET trong khi kết nối. Nếu đường này được nối đúng cách, nó sẽ buộc thiết bị AVR mục tiêu phải đặt lại, do đó cho phép JTAG sự liên quan.

Nếu JTAG giao diện được kích hoạt, JTAG chân không thể được sử dụng cho các chức năng chân thay thế. Chúng sẽ vẫn dành riêng cho JTAG ghim cho đến khi JTAG giao diện bị vô hiệu hóa bằng cách thiết lập bit JTD từ mã chương trình hoặc bằng cách xóa JTAGEN fuse thông qua giao diện lập trình.

![]() Mẹo:

Mẹo:

Hãy chắc chắn kiểm tra hộp kiểm “sử dụng thiết lập lại bên ngoài” trong cả hộp thoại lập trình và hộp thoại tùy chọn gỡ lỗi để cho phép Atmel-ICE xác nhận dòng RESET và bật lại J.TAG giao diện trên các thiết bị đang chạy mã vô hiệu hóa JTAG giao diện bằng cách thiết lập bit JTD.

Sự kiện IDR/OCDR

IDR (In-out Data Register) còn được gọi là OCDR (On Chip Debug Register) và được trình gỡ lỗi sử dụng rộng rãi để đọc và ghi thông tin vào MCU khi ở chế độ dừng trong phiên gỡ lỗi. Khi chương trình ứng dụng ở chế độ chạy ghi một byte dữ liệu vào thanh ghi OCDR của thiết bị AVR đang được gỡ lỗi, Atmel-ICE sẽ đọc giá trị này và hiển thị trong cửa sổ thông báo của phần mềm giao diện người dùng. Thanh ghi OCDR được thăm dò sau mỗi 50ms, vì vậy việc ghi vào thanh ghi ở tần suất cao hơn sẽ KHÔNG mang lại kết quả đáng tin cậy. Khi thiết bị AVR mất nguồn trong khi đang được gỡ lỗi, các sự kiện OCDR không mong muốn có thể được báo cáo. Điều này xảy ra vì Atmel-ICE vẫn có thể thăm dò thiết bị dưới dạng vol mục tiêutage giảm xuống dưới mức hoạt động tối thiểu của AVRtage.

4.4.13. Những cân nhắc đặc biệt về AVR XMEGA

OCD và đồng hồ

Khi MCU vào chế độ dừng, đồng hồ OCD được sử dụng làm đồng hồ MCU. Đồng hồ OCD là JTAG TCK nếu JTAG giao diện đang được sử dụng hoặc PDI_CLK nếu giao diện PDI đang được sử dụng.

Các mô-đun I/O ở chế độ dừng

Ngược lại với các thiết bị Atmel megaAVR trước đó, trong XMEGA, các mô-đun I/O bị dừng ở chế độ dừng. Điều này có nghĩa là việc truyền USART sẽ bị gián đoạn, bộ hẹn giờ (và PWM) sẽ bị dừng.

Điểm dừng phần cứng

Có bốn bộ so sánh điểm dừng phần cứng – hai bộ so sánh địa chỉ và hai bộ so sánh giá trị. Chúng có một số hạn chế nhất định:

- Tất cả các điểm dừng phải cùng loại (chương trình hoặc dữ liệu)

- Tất cả các điểm dừng dữ liệu phải nằm trong cùng một vùng bộ nhớ (I/O, SRAM hoặc XRAM)

- Chỉ có thể có một điểm dừng nếu phạm vi địa chỉ được sử dụng

Sau đây là những kết hợp khác nhau có thể được thiết lập:

- Hai điểm dừng dữ liệu hoặc địa chỉ chương trình đơn

- Một điểm dừng phạm vi địa chỉ dữ liệu hoặc chương trình

- Hai điểm dừng địa chỉ dữ liệu đơn với so sánh giá trị đơn

- Một điểm dừng dữ liệu với phạm vi địa chỉ, phạm vi giá trị hoặc cả hai

Atmel Studio sẽ cho bạn biết nếu không thể đặt điểm dừng và lý do. Điểm dừng dữ liệu được ưu tiên hơn điểm dừng chương trình nếu có điểm dừng phần mềm.

Thiết lập lại bên ngoài và PDI vật lý