Mikrokontroler Atmel ATmega2564 8bit AVR

Cechy

- Obsługa sieci poprzez sprzętowe filtrowanie wielu adresów PAN

- Zaawansowane wspomaganie sprzętowe przy zmniejszonym zużyciu energii

- Wysokowydajny, energooszczędny mikrokontroler AVR® 8-bit

- Zaawansowana architektura RISC

- 135 Potężne instrukcje - większość wykonywania pojedynczego cyklu zegara

- 32×8 rejestrów roboczych ogólnego przeznaczenia / mnożnik 2-cykliczny na chipie

- Przepustowość do 16 MIPS przy 16 MHz i 1.8 V – praca w pełni statyczna

- Nieulotne pamięci programów i danych

- 256K/128K/64K bajtów pamięci Flash programowalnej w systemie

- Wytrzymałość: 10 000 cykli zapisu/kasowania w temp. 125°C (25 000 cykli w temp. 85°C)

- 8K/4K/2K bajtów EEPROM

- Wytrzymałość: 20 000 cykli zapisu/kasowania w temp. 125°C (100 000 cykli w temp. 25°C)

- 32K/16K/8K bajtów wewnętrznej pamięci SRAM

- JTAG (Zgodny ze standardem IEEE 1149.1) Interfejs

- Możliwości skanowania granic według JTAG Standard

- Obszerne wsparcie debugowania na układzie scalonym

- Programowanie pamięci Flash EEPROM, bezpieczników i bitów blokujących za pomocą JTAG interfejs

- Funkcje peryferyjne

- Wiele kanałów Timera/Licznika i PWM

- Licznik czasu rzeczywistego z oddzielnym oscylatorem

- 10-bitowy przetwornik analogowo-cyfrowy 330 ks/s; komparator analogowy; wbudowany czujnik temperatury

- Interfejs szeregowy Master/Slave SPI

- Dwa programowalne szeregowe USART

- Interfejs szeregowy 2-żyłowy zorientowany bajtowo

- Zaawansowany program obsługi przerwań i tryby oszczędzania energii

- Watchdog Timer z oddzielnym oscylatorem na chipie

- Resetowanie po włączeniu zasilania i detektor spadku napięcia przy niskim natężeniu

- W pełni zintegrowany transceiver małej mocy dla pasma ISM 2.4 GHz

- Wysoka moc Ampobsługa lifier poprzez tłumienie bocznego płatu widma TX

- Obsługiwane prędkości transmisji danych: 250 kb/s i 500 kb/s, 1 Mb/s, 2 Mb/s

- -100 dBm czułość RX; moc wyjściowa TX do 3.5 dBm

- Sprzętowo wspomagany MAC (automatyczne potwierdzanie, automatyczne ponawianie próby)

- 32-bitowy licznik symboli IEEE 802.15.4

- Wykrywanie SFD, rozprzestrzenianie; usuwanie rozprzestrzeniania; ramkowanie; obliczanie CRC-16

- Różnorodność anten i sterowanie TX/RX / Bufor ramki TX/RX 128 bajtów

- Syntezator PLL z odstępem międzykanałowym 5 MHz i 500 kHz dla pasma ISM 2.4 GHz

- Bezpieczeństwo sprzętowe (AES, prawdziwy generator losowy)

- Zintegrowane oscylatory kwarcowe (32.768 kHz i 16 MHz, wymagany zewnętrzny kwarc)

- I/O i pakiet

- 33 programowalne linie we/wy

- 48-pad QFN (RoHS/całkowicie zielony)

- Zakres temperatur: -40°C do 125°C Przemysłowy

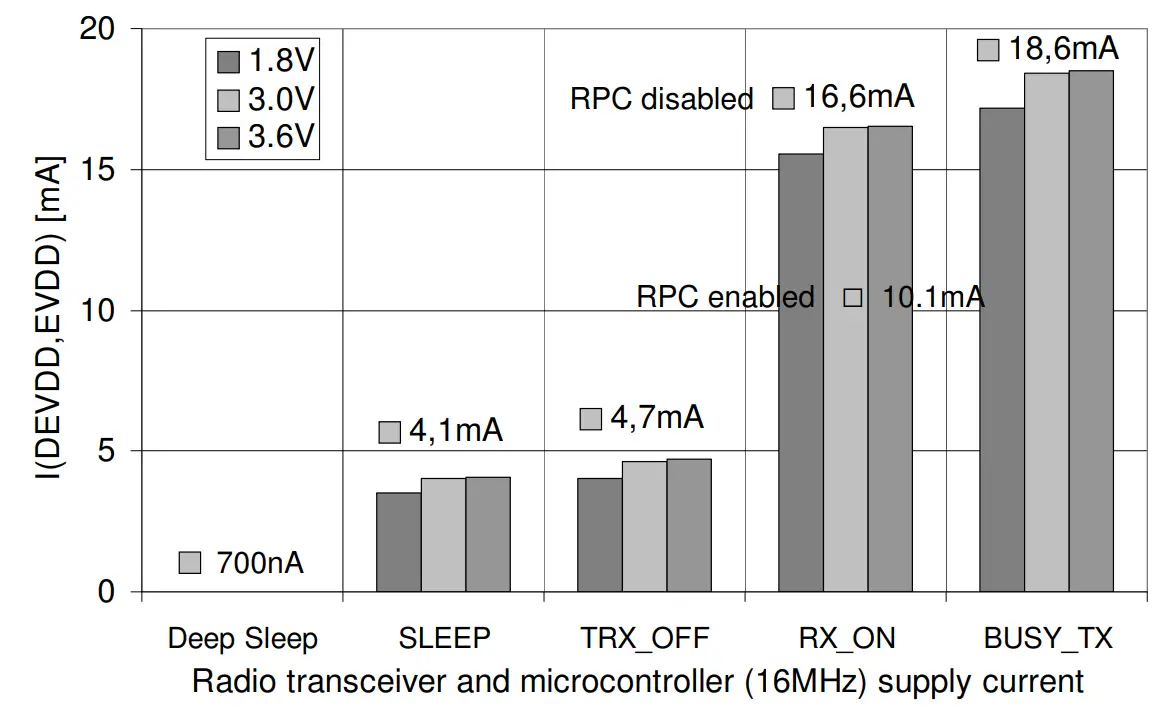

- Bardzo niskie zużycie energii (1.8 do 3.6 V) dla AVR i Rx/Tx: 10.1 mA/18.6 mA

- Tryb aktywny procesora (16 MHz): 4.1 mA

- Nadajnik-odbiornik 2.4 GHz: RX_ON 6.0 mA / TX 14.5 mA (maksymalna moc wyjściowa TX)

- Tryb głębokiego uśpienia: <700nA przy 25°C

- Stopień prędkości: 0 – 16 MHz przy zakresie 1.8 – 3.6 V ze zintegrowanym regulatorem głośnościtage regulatorzy

Aplikacje

- ZigBee®/IEEE 802.15.4-2011/2006/2003™ – urządzenie o pełnej i ograniczonej funkcjonalności

- Uniwersalny transceiver pasma ISM 2.4 GHz z mikrokontrolerem

- RF4CE, SP100, WirelessHART™, aplikacje ISM i IPv6 / 6LoWPAN

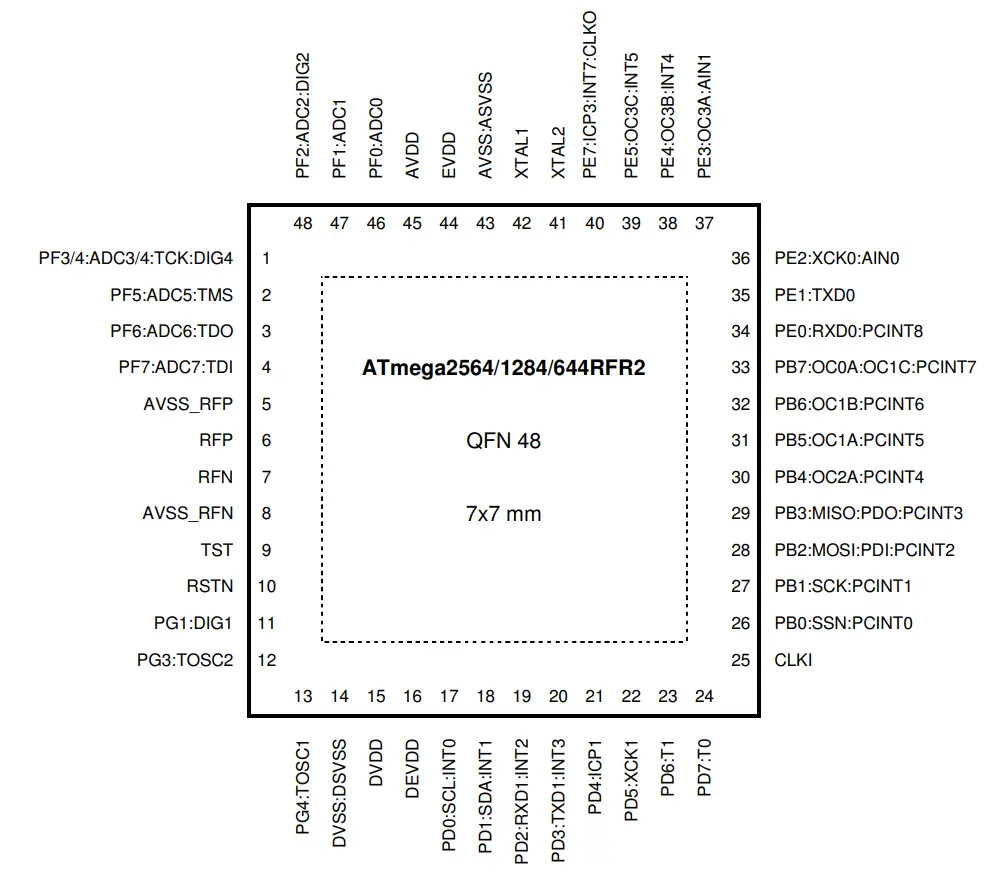

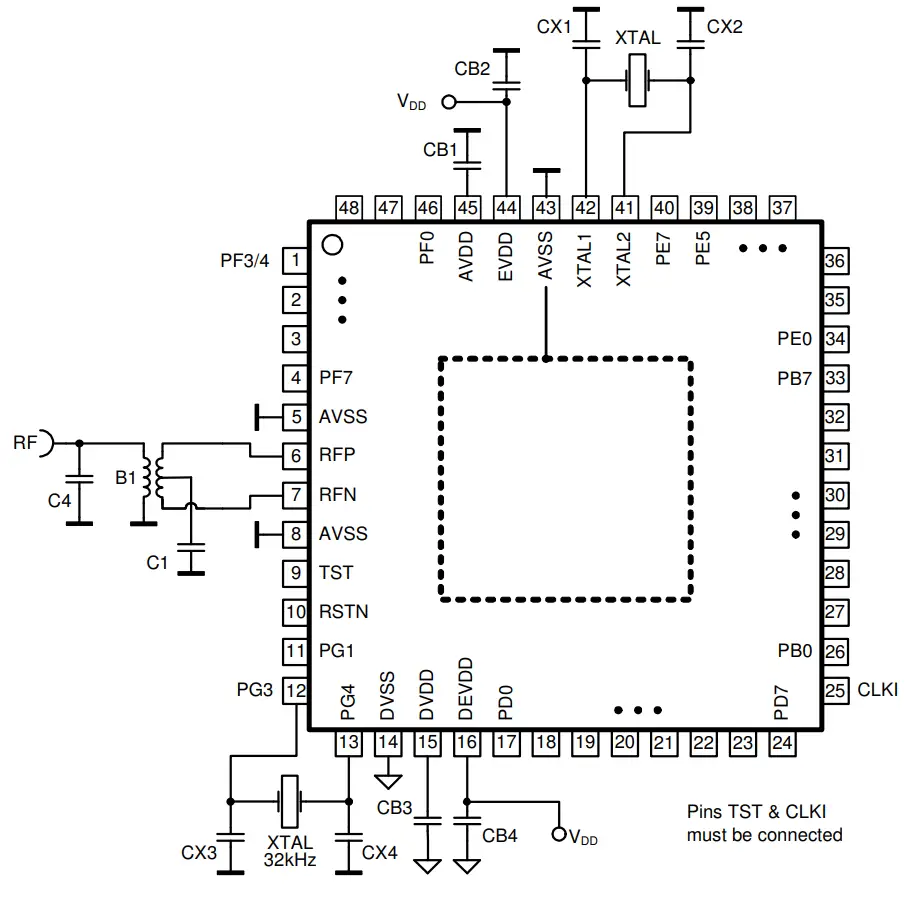

Konfiguracje pinów

Rysunek 1-1. Wyprowadzenia ATmega2564/1284/644RFR2

Notatka:Duży środkowy pad pod obudową QFN/MLF jest wykonany z metalu i wewnętrznie połączony z AVSS. Powinien być przylutowany lub przyklejony do płytki, aby zapewnić dobrą stabilność mechaniczną. Jeśli środkowy pad pozostanie niepołączony, obudowa może się poluzować od płytki. Nie zaleca się używania odsłoniętego paddle jako zamiennika zwykłych pinów AVSS.

Zastrzeżenie

Typowe wartości zawarte w tej karcie danych są oparte na wynikach symulacji i charakteryzacji innych mikrokontrolerów AVR i transceiverów radiowych wyprodukowanych w podobnej technologii procesowej. Wartości minimalne i maksymalne będą dostępne po scharakteryzowaniu urządzenia.

Nadview

ATmega2564/1284/644RFR2 to energooszczędny 8-bitowy mikrokontroler CMOS oparty na ulepszonej architekturze RISC AVR, połączony z transceiverem o dużej szybkości transmisji danych dla pasma ISM 2.4 GHz.

Wykonując zaawansowane instrukcje w jednym cyklu zegara, urządzenie osiąga przepustowość zbliżającą się do 1 MIPS na MHz, co pozwala projektantowi systemu optymalizować zużycie energii w zależności od szybkości przetwarzania.

Nadajnik-odbiornik radiowy zapewnia dużą prędkość transmisji danych od 250 kb/s do 2 Mb/s, obsługę ramek, doskonałą czułość odbiornika i wysoką moc wyjściową transmisji, co pozwala na niezwykle niezawodną komunikację bezprzewodową.

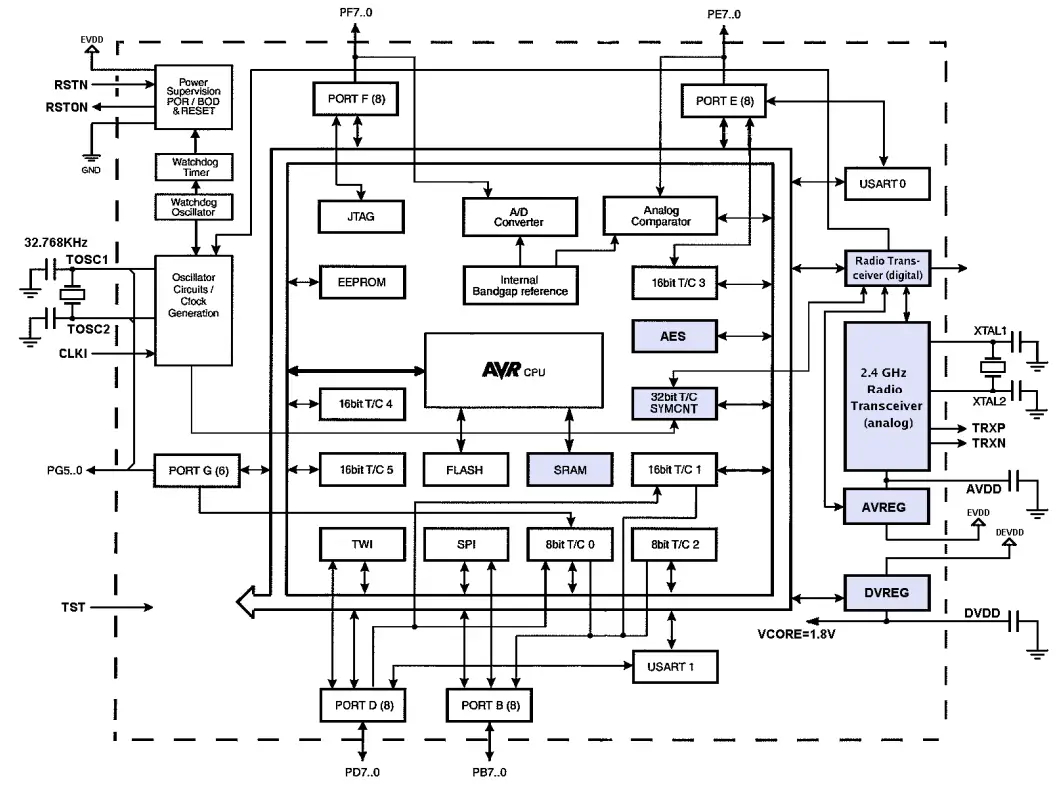

Schemat blokowy

Rysunek 3-1 Schemat blokowy

Rdzeń AVR łączy bogaty zestaw instrukcji z 32 rejestrami roboczymi ogólnego przeznaczenia. Wszystkie 32 rejestry są bezpośrednio połączone z jednostką arytmetyczną (ALU). Dostęp do dwóch niezależnych rejestrów można uzyskać za pomocą jednej instrukcji wykonywanej w jednym cyklu zegara. Powstała architektura jest bardzo wydajna pod względem kodu, a jednocześnie osiąga przepustowość do dziesięciu razy szybszą niż konwencjonalne mikrokontrolery CISC. System obejmuje wewnętrzny wolumintage regulacja i zaawansowane zarządzanie energią. Wyróżnia się małym prądem upływu, co pozwala na dłuższy czas pracy z baterii.

Nadajnik-odbiornik radiowy to w pełni zintegrowane rozwiązanie ZigBee wykorzystujące minimalną liczbę zewnętrznych komponentów. Łączy doskonałą wydajność RF z niskim kosztem, niewielkim rozmiarem i niskim zużyciem prądu. Nadajnik-odbiornik radiowy obejmuje syntezator frakcyjny N stabilizowany kryształem, nadajnik i odbiornik oraz pełne przetwarzanie Direct Sequence Spread Spectrum Signal (DSSS) z rozpraszaniem i derozpraszaniem. Urządzenie jest w pełni zgodne ze standardami IEEE802.15.4-2011/2006/2003 i ZigBee. Układ ATmega2564/1284/644RFR2 zapewnia następujące funkcje: 256 KB/128 KB/64 KB pamięci Flash ISP z możliwością odczytu podczas zapisu, 8 KB/4 KB/2 KB pamięci EEPROM, 32 KB/16 KB/8 KB pamięci SRAM, do 35 linii I/O ogólnego przeznaczenia, 32 rejestry robocze ogólnego przeznaczenia, licznik czasu rzeczywistego (RTC), 6 elastycznych liczników z trybami porównywania i PWM, 32-bitowy licznik/licznik, 2 USART, zorientowany bajtowo 2-żyłowy interfejs szeregowy, 8-kanałowy, 10-bitowy przetwornik analogowo-cyfrowy (ADC) z opcjonalnym wejściem różnicowymtage z programowalnym wzmocnieniem, programowalnym układem Watchdog Timer z wewnętrznym oscylatorem, portem szeregowym SPI, zgodny ze standardem IEEE 1149.1 JTAG interfejs testowy, używany również do dostępu do systemu debugowania na układzie scalonym i programowania oraz 6 programowo wybieranych trybów oszczędzania energii.

Tryb bezczynności zatrzymuje procesor, pozwalając jednocześnie na dalsze działanie pamięci SRAM, timerów/liczników, portu SPI i systemu przerwań. Tryb Power-down zapisuje zawartość rejestru, ale zamraża oscylator, wyłączając wszystkie inne funkcje układu do następnego przerwania lub resetu sprzętowego. W trybie oszczędzania energii asynchroniczny timer nadal działa, umożliwiając użytkownikowi utrzymanie bazy timera, podczas gdy reszta urządzenia jest w stanie uśpienia. Tryb redukcji szumów ADC zatrzymuje procesor i wszystkie moduły I/O z wyjątkiem asynchronicznego timera i ADC, aby zminimalizować szum przełączania podczas konwersji ADC. W trybie gotowości oscylator RC działa, podczas gdy reszta urządzenia jest w stanie uśpienia. Umożliwia to bardzo szybki rozruch w połączeniu z niskim zużyciem energii. W trybie rozszerzonego czuwania zarówno główny oscylator RC, jak i asynchroniczny timer nadal działają.

Typowy prąd zasilania mikrokontrolera z zegarem CPU ustawionym na 16MHz i transceiverem radiowym dla najważniejszych stanów pokazano na rysunku 3-2 poniżej.

Rysunek 3-2 Prąd zasilania transceivera radiowego i mikrokontrolera (16MHz)

Moc wyjściowa transmisji jest ustawiona na maksimum. Jeśli transceiver radiowy jest w trybie SLEEP, prąd jest rozpraszany tylko przez mikrokontroler AVR.

W trybie Deep Sleep wszystkie główne bloki cyfrowe bez wymagań dotyczących retencji danych są odłączane od zasilania głównego, zapewniając bardzo mały prąd upływu. Timer Watchdog, licznik symboli MAC i oscylator 32.768 kHz można skonfigurować tak, aby nadal działały.

Urządzenie jest produkowane w oparciu o technologię pamięci nieulotnej o dużej gęstości firmy Atmel.

On-chip ISP Flash umożliwia przeprogramowanie pamięci programu w systemie za pomocą interfejsu szeregowego SPI, za pomocą konwencjonalnego programatora pamięci nieulotnej lub za pomocą programu rozruchowego on-chip działającego na rdzeniu AVR. Program rozruchowy może używać dowolnego interfejsu do pobierania programu aplikacji w pamięci Flash aplikacji.

Oprogramowanie w sekcji Flash rozruchowej będzie nadal działać, podczas gdy sekcja Flash aplikacji będzie aktualizowana, zapewniając prawdziwą operację Read-While-Write. Łącząc 8-bitowy procesor RISC z In-System Self-Programmable Flash na monolitycznym układzie scalonym, Atmel ATmega2564/1284/644RFR2 jest wydajnym mikrokontrolerem, który zapewnia wysoce elastyczne i ekonomiczne rozwiązanie dla wielu wbudowanych aplikacji sterujących.

Mikrokontroler ATmega2564/1284/644RFR2 AVR jest obsługiwany przez pełen zestaw narzędzi do tworzenia programów i systemów, w tym: kompilator C, makroasemblery, debuggery/symulatory programów, emulatory wewnątrzukładowe i zestawy ewaluacyjne.

Opisy pinów

EVDD

Zewnętrzne zasilanie analogowe wolttage.

DEVDD

Zewnętrzny cyfrowy zasilacz wolumentage.

AVDD

Regulowany zasilacz analogowytage (generowane wewnętrznie).

DVDD

Regulowana cyfrowa dostawa wolumenutage (generowane wewnętrznie).

DVSS

Cyfrowa ziemia.

AVSS

Masa analogowa.

Port B (PB7…PB0)

Port B to 8-bitowy dwukierunkowy port I/O z wewnętrznymi rezystorami podciągającymi (wybieranymi dla każdego bitu). Bufory wyjściowe portu B mają symetryczne charakterystyki napędowe z możliwością zarówno wysokiego odpływu, jak i źródła. Jako wejścia, piny portu B, które są zewnętrznie podciągnięte do niskiego poziomu, będą źródłem prądu, jeśli rezystory podciągające zostaną aktywowane. Pinami portu B są trójstanowe, gdy warunek resetu staje się aktywny, nawet jeśli zegar nie działa.

Port B udostępnia również funkcje różnych funkcji specjalnych układów ATmega2564/1284/644RFR2.

Port D (PD7…PD0)

Port D to 8-bitowy dwukierunkowy port I/O z wewnętrznymi rezystorami podciągającymi (wybieranymi dla każdego bitu). Bufory wyjściowe portu D mają symetryczne charakterystyki napędowe z możliwością zarówno wysokiego odpływu, jak i źródła. Jako wejścia, piny portu D, które są zewnętrznie podciągnięte do niskiego poziomu, będą źródłem prądu, jeśli rezystory podciągające zostaną aktywowane. Pin Port D jest trójstanowy, gdy warunek resetu staje się aktywny, nawet jeśli zegar nie działa.

Port D udostępnia również funkcje różnych funkcji specjalnych układów ATmega2564/1284/644RFR2.

Port E (PE7,PE5…PE0)

Wewnętrznie Port E jest 8-bitowym dwukierunkowym portem I/O z wewnętrznymi rezystorami podciągającymi (wybieranymi dla każdego bitu). Bufory wyjściowe Port E mają symetryczne charakterystyki napędowe z możliwością zarówno wysokiego odpływu, jak i źródła. Jako wejścia, piny Port E, które są zewnętrznie podciągnięte do niskiego poziomu, będą źródłem prądu, jeśli rezystory podciągające zostaną aktywowane. Pin Port E jest trójstanowy, gdy warunek resetu staje się aktywny, nawet jeśli zegar nie działa.

Ze względu na małą liczbę pinów obudowy QFN48 port E6 nie jest podłączony do pinu. Port E zapewnia również funkcje różnych specjalnych funkcji ATmega2564/1284/644RFR2.

Port F (PF7..PF5,PF4/3,PF2…PF0)

Wewnętrznie Port F jest 8-bitowym dwukierunkowym portem I/O z wewnętrznymi rezystorami podciągającymi (wybieranymi dla każdego bitu). Bufory wyjściowe Port F mają symetryczne charakterystyki napędowe z możliwością zarówno wysokiego odpływu, jak i źródła. Jako wejścia, piny Port F, które są zewnętrznie podciągnięte do niskiego poziomu, będą źródłem prądu, jeśli rezystory podciągające zostaną aktywowane. Pin Port F jest trójstanowy, gdy warunek resetu staje się aktywny, nawet jeśli zegar nie działa.

Ze względu na małą liczbę pinów obudowy QFN48 porty F3 i F4 są podłączone do tego samego pinu. Konfigurację I/O należy wykonać ostrożnie, aby uniknąć nadmiernego rozpraszania mocy.

Port F udostępnia również funkcje różnych funkcji specjalnych układów ATmega2564/1284/644RFR2.

Port G (PG4, PG3, PG1)

Wewnętrznie Port G jest 6-bitowym dwukierunkowym portem I/O z wewnętrznymi rezystorami podciągającymi (wybieranymi dla każdego bitu). Bufory wyjściowe Port G mają symetryczne charakterystyki sterowania z wysoką zdolnością zarówno do odbioru, jak i odbioru. Jednak siła sterowania PG3 i PG4 jest zmniejszona w porównaniu z innymi pinami portu. Objętość wyjściowatagspadek napięcia (VOH, VOL) jest wyższy, a prąd upływu mniejszy. Jako wejścia, piny Port G, które są zewnętrznie podciągnięte do niskiego poziomu, będą źródłem prądu, jeśli rezystory podciągające zostaną aktywowane. Pin Port G jest trójstanowy, gdy warunek resetu stanie się aktywny, nawet jeśli zegar nie działa.

Ze względu na małą liczbę pinów w obudowie QFN48, porty G0, G2 i G5 nie są podłączone do żadnego pinu.

Port G udostępnia również funkcje różnych funkcji specjalnych układów ATmega2564/1284/644RFR2.

AVSS_RFP

AVSS_RFP to dedykowany pin uziemiający dla dwukierunkowego, różnicowego portu wejścia/wyjścia RF.

AVSS_RFN

AVSS_RFN to dedykowany pin uziemiający dla dwukierunkowego, różnicowego portu wejścia/wyjścia RF.

Zapytanie ofertowe

RFP to dodatni zacisk dwukierunkowego, różnicowego portu wejścia/wyjścia RF.

RFN

RFN to zacisk ujemny dwukierunkowego, różnicowego portu wejścia/wyjścia RF.

RSTN

Wejście resetu. Niski poziom na tym pinie przez okres dłuższy niż minimalna długość impulsu wygeneruje reset, nawet jeśli zegar nie działa. Krótsze impulsy nie gwarantują wygenerowania resetu.

XTAL1

Wejście do odwracającego oscylatora kwarcowego 16MHz amplifier. Ogólnie rzecz biorąc, kryształ pomiędzy XTAL1 i XTAL2 zapewnia zegar referencyjny 16MHz radiowego transceivera.

XTAL2

Wyjście inwertującego oscylatora kwarcowego 16MHz ampliyfikator.

TST

Programowanie i tryb testowy włącza pin. Jeśli pin TST nie jest używany, ustaw go na niski.

KLIK

Wejście do systemu zegara. Jeśli wybrane, dostarcza zegar operacyjny mikrokontrolera.

Nieużywane piny

Pływające piny mogą powodować rozpraszanie mocy w wejściach cyfrowychtage. Powinny być podłączone do odpowiedniego źródła. W normalnych trybach pracy wewnętrzne rezystory podciągające mogą być włączone (w Reset wszystkie GPIO są skonfigurowane jako wejście, a rezystory podciągające nadal nie są włączone).

Dwukierunkowe piny I/O nie powinny być podłączane bezpośrednio do uziemienia ani źródła zasilania.

Cyfrowe piny wejściowe TST i CLKI muszą być podłączone. Jeśli nieużywany pin TST można podłączyć do AVSS, a CLKI należy podłączyć do DVSS.

Piny wyjściowe są sterowane przez urządzenie i nie są unoszone. Piny zasilania i odpowiednie piny uziemienia są połączone ze sobą wewnętrznie.

XTAL1 i XTAL2 nigdy nie będą zmuszane do dostarczania objętościtagi w tym samym czasie.

Zgodność i ograniczenia funkcji pakietu QFN-48

RZECZ

Odniesienie voltagWyjście przetwornika analogowo-cyfrowego nie jest podłączone do żadnego pinu w układzie ATmega2564/1284/644RFR2.

Port E6

Port E6 nie jest podłączony do pinu w ATmega2564/1284/644RFR2. Alternatywny pin pełni funkcję wejścia zegara dla timera 3, a przerwanie zewnętrzne 6 nie jest dostępne.

Porty F3 i F4

Porty F3 i F4 są podłączone do tego samego pinu w ATmega2564/1284/644RFR2. Konfigurację wyjścia należy wykonać ostrożnie, aby uniknąć nadmiernego zużycia prądu.

Alternatywna funkcja pinu portu F4 jest używana przez JTAG interfejs. Jeśli JTAG używany jest interfejs, port F3 musi być skonfigurowany jako wejście, a wyjście funkcji alternatywnego pinu DIG4 (wskaźnik RX/TX) musi być wyłączone. W przeciwnym razie JTAG interfejs nie będzie działał. SPIEN Fuse powinien być zaprogramowany tak, aby móc wymazać program, który przypadkowo steruje portem F3.

Dostępnych jest tylko 7 niesymetrycznych kanałów wejściowych dla przetwornika ADC.

Port G0

Port G0 nie jest podłączony do pinu w ATmega2564/1284/644RFR2. Alternatywna funkcja pinu DIG3 (odwrócony wskaźnik RX/TX) nie jest dostępna. Jeśli JTAG Interfejs nie jest używany, a wyjście z alternatywną funkcją pinu DIG4 portu F3 może być nadal używane jako wskaźnik RX/TX.

Port G2

Port G2 nie jest podłączony do pinu w ATmega2564/1284/644RFR2. Alternatywna funkcja pinu AMR (asynchroniczne automatyczne odczytywanie licznika wejściowego do timera 2) nie jest dostępna.

Port G5

Port G5 nie jest podłączony do pinu w ATmega2564/1284/644RFR2. Alternatywna funkcja pinu OC0B (kanał porównania wyjścia 8-bitowego timera 0) jest niedostępna.

RSTON

Wyjście resetu RSTON sygnalizujące stan resetu wewnętrznego nie jest podłączone do pinu w układzie ATmega2564/1284/644RFR2.

Podsumowanie konfiguracji

W zależności od wymagań aplikacji zmienna wielkość pamięci pozwala na optymalizację poboru prądu i prądu upływu.

Tabela 3-1 Konfiguracja pamięci

| Urządzenie | Błysk | EEPROM | Pamięć RAM |

| ATmega2564RFR2 | 256 KB | 8 KB | 32 KB |

| ATmega1284RFR2 | 128 KB | 4 KB | 16 KB |

| ATmega644RFR2 | 64 KB | 2 KB | 8 KB |

Konfiguracja obudowy i powiązanych pinów jest taka sama dla wszystkich urządzeń, zapewniając pełną funkcjonalność aplikacji.

Tabela 3-2 Konfiguracja systemu

| Urządzenie | Pakiet | GPIO | Szeregowy IF | Kanał ADC |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

Urządzenia są zoptymalizowane pod kątem aplikacji opartych na ZigBee i specyfikacji IEEE 802.15.4. Mając stos aplikacji, warstwę sieciową, interfejs czujnika i doskonałą kontrolę mocy połączone w jednym układzie scalonym, możliwe jest wiele lat działania.

Tabela 3-3 Aplikacja Profile

| Urządzenie | Aplikacja |

| ATmega2564RFR2 | Duży koordynator sieci / router dla IEEE 802.15.4 / ZigBee Pro |

| ATmega1284RFR2 | Koordynator sieciowy / router dla IEEE 802.15.4 |

| ATmega644RFR2 | Urządzenie węzła końcowego / procesor sieciowy |

Obwody aplikacyjne

Podstawowy schemat aplikacji

Podstawowy schemat aplikacji ATmega2564/1284/644RFR2 ze złączem RF z pojedynczym końcem pokazano na poniższym rysunku 4-1, a powiązany wykaz materiałów w tabeli 4-1 na stronie 10. 50Ω wejście RF z pojedynczym końcem jest przekształcane na 100Ω różnicową impedancję portu RF za pomocą Balun B1. Kondensatory C1 i C2 zapewniają sprzężenie AC wejścia RF z portem RF, kondensator C4 poprawia dopasowanie.

Rysunek 4-1. Podstawowy schemat aplikacji (obudowa 48-pinowa)

Kondensatory obejściowe zasilania (CB2, CB4) są podłączone do zewnętrznego analogowego pinu zasilania (EVDD, pin 44) i zewnętrznego cyfrowego pinu zasilania (DEVDD, pin 16). Kondensator C1 zapewnia wymagane sprzężenie AC RFN/RFP.

Pływające piny mogą powodować nadmierne rozpraszanie mocy (np. podczas włączania zasilania). Powinny być podłączone do odpowiedniego źródła. GPIO nie powinno być podłączone bezpośrednio do uziemienia lub zasilania.

Cyfrowe piny wejściowe TST i CLKI muszą być podłączone. Jeśli pin TST nigdy nie będzie używany, można go podłączyć do AVSS, podczas gdy nieużywany pin CLKI można podłączyć do DVSS (patrz rozdział „Nieużywane piny”).

Kondensatory CB1 i CB3 są kondensatorami obejściowymi dla zintegrowanego układu analogowego i cyfrowego.tagRegulatory zapewniają stabilną pracę i poprawiają odporność na zakłócenia.

Kondensatory należy umieścić jak najbliżej pinów i charakteryzować się niską rezystancją i niską indukcyjnością połączenia z masą, aby uzyskać najlepszą wydajność.

Kryształ (XTAL), dwa kondensatory obciążeniowe (CX1, CX2) i wewnętrzne obwody podłączone do pinów XTAL1 i XTAL2 tworzą oscylator kwarcowy 16 MHz dla transceivera 2.4 GHz. Aby osiągnąć najlepszą dokładność i stabilność częstotliwości odniesienia, należy unikać dużych pojemności pasożytniczych. Linie kryształu powinny być prowadzone tak krótko, jak to możliwe i nie w pobliżu sygnałów cyfrowych I/O. Jest to szczególnie wymagane w trybach High Data Rate.

Kryształ 32.768 kHz podłączony do wewnętrznego oscylatora kwarcowego o niskim poborze mocy (poniżej 1 µA) zapewnia stabilne odniesienie czasowe dla wszystkich trybów niskiego poboru mocy, w tym 32-bitowego licznika symboli IEEE 802.15.4 („licznik symboli MAC”) i aplikacji zegara czasu rzeczywistego wykorzystujących asynchroniczny timer T/C2 („Timer/Counter2 z PWM i pracą asynchroniczną”).

Całkowita pojemność bocznikowa, wliczając CX3, CX4, nie powinna przekraczać 15 pF na obu pinach.

Bardzo niski prąd zasilający oscylator wymaga starannego rozplanowania płytki PCB i unikania wszelkich ścieżek upływu.

Przesłuchy i promieniowanie z przełączania sygnałów cyfrowych do pinów kryształu lub pinów RF mogą pogorszyć wydajność systemu. Zaleca się zaprogramowanie minimalnych ustawień siły napędu dla sygnału wyjściowego cyfrowego (patrz „DPDS0 – Port Driver Strength Register 0”).

Tabela 4-1. Wykaz materiałów (BoM)

| Desygnator | Opis | Wartość | Producent | Numer części | Komentarz |

| B1 | balun SMD

Balun/filtr SMD |

2.4 GHz | Technologia Wuerth Johanson | 748421245

2450FB15L0001 |

Filtr w zestawie |

| CB1 CB3 | LDO VREG

kondensator obejściowy |

1 mF (minimum 100 nF) | AVX

Murata |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10% 16 V |

| CB2 CB4 | Kondensator obejściowy zasilacza | 1 mF (minimum 100 nF) | |||

| CX1, CX2 | Kondensator obciążeniowy kwarcowy 16MHz | 12 pF | AVX

Murata |

06035A120JA GRP1886C1H120JA01 | ZĄB (0603) 5% 50 V |

| CX3, CX4 | Kondensator obciążeniowy kwarcowy 32.768 kHz | 12… 25 pF | |||

| C1, C2 | Kondensator sprzęgający RF | 22 pF | Epcos Epcos AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50 V (0402 lub 0603) |

| C4 (opcjonalnie) | Dopasowanie RF | 0.47 pF | Janusz | ||

| XTAL | Kryształ | CX-4025 16 MHz

SX-4025 16 MHz |

ACAL Taitjen Siward | XWBBPL-F-1 A207-011 | |

| XTAL32kHz | Kryształ | Rs=100 kOhm |

Historia rewizji

Należy pamiętać, że numery stron odsyłających w tej sekcji odnoszą się do tego dokumentu. Odnosząca się rewizja w tej sekcji odnosi się do rewizji dokumentu.

Wersja 42073BS-MCU Wireless-09/14

- Treść niezmieniona – utworzono ponownie na potrzeby połączonej wersji z arkuszem danych.

Wersja 8393AS-MCU Wireless-02/13

- Pierwsze wydanie.

© 2014 Atmel Corporation. Wszelkie prawa zastrzeżone. / Rev.: 42073BS-MCU Wireless-09/14 Atmel®, logo Atmel i ich kombinacje, Enabling Unlimited Possibilities® i inne są zarejestrowanymi znakami towarowymi lub znakami towarowymi Atmel Corporation lub jej spółek zależnych. Inne terminy i nazwy produktów mogą być znakami towarowymi innych osób.

Zastrzeżenie: Informacje zawarte w tym dokumencie są udostępniane w związku z produktami Atmel. Niniejszy dokument lub sprzedaż produktów Atmel nie udziela żadnej licencji, wyraźnej lub dorozumianej, na mocy estoppelu lub w inny sposób, na jakiekolwiek prawa własności intelektualnej. Z WYJĄTKIEM USTALEŃ WARUNKÓW SPRZEDAŻY ATMEL ZNAJDUJĄCYCH SIĘ NA STRONIE ATMEL WEBWITRYNA, ATMEL NIE PONOSI ŻADNEJ ODPOWIEDZIALNOŚCI I ZRZEKA SIĘ WSZELKICH WYRAŹNYCH, DOROZUMIANYCH LUB USTAWOWYCH GWARANCJI DOTYCZĄCYCH JEJ PRODUKTÓW, W TYM MIĘDZY INNYMI DOROZUMIANEJ GWARANCJI PRZYDATNOŚCI HANDLOWEJ, PRZYDATNOŚCI DO OKREŚLONEGO CELU. W ŻADNYM WYPADKU ATMEL NIE PONOSI ODPOWIEDZIALNOŚCI ZA ŻADNE SZKODY BEZPOŚREDNIE, POŚREDNIE, WTÓRNE, KARNE, SZCZEGÓLNE LUB PRZYPADKOWE (W TYM MIĘDZY OGRANICZENIAMI SZKODY ZA STRATY I ZYSKI, PRZERWY W DZIAŁALNOŚCI LUB UTRATĘ INFORMACJI) WYNIKAJĄCE Z WYKORZYSTANIA LUB NIEMOŻNOŚCI UŻYTKOWANIA NINIEJSZY DOKUMENT, NAWET JEŚLI ATMEL ZOSTAŁ POINFORMOWANY O MOŻLIWOŚCI WYSTĄPIENIA TAKICH SZKÓD. Atmel nie składa żadnych oświadczeń ani gwarancji w odniesieniu do dokładności lub kompletności treści tego dokumentu i zastrzega sobie prawo do wprowadzania zmian w specyfikacjach i opisach produktów w dowolnym czasie bez powiadomienia. Atmel nie zobowiązuje się do aktualizacji informacji zawartych w niniejszym dokumencie. O ile wyraźnie nie określono inaczej, produkty Atmel nie nadają się i nie powinny być używane w zastosowaniach motoryzacyjnych. Produkty Atmel nie są przeznaczone, autoryzowane ani objęte gwarancją do użytku jako komponenty w aplikacjach mających na celu podtrzymywanie lub podtrzymywanie życia.

Elektronika Mouser

Autoryzowany dystrybutor

Kliknij, aby View Informacje o cenach, zapasach, dostawach i cyklu życia:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

Obsługa klienta

Korporacja Atmel

1600 Technologia Drive

San Jose, Kalifornia 95110

USA

Telefon: (+1)408-441-0311

Faks: (+1)408-487-2600

www.atmel.com

Dokumenty / Zasoby

|

Mikrokontroler Atmel ATmega2564 8bit AVR [plik PDF] Instrukcja obsługi ATmega2564RFR2, ATmega1284RFR2, ATmega644RFR2, ATmega2564 8-bitowy mikrokontroler AVR, ATmega2564, 8-bitowy mikrokontroler AVR, mikrokontroler AVR, mikrokontroler |