Microcontrolador Atmel ATmega2564 AVR de 8 bits

Característiques

- Suport a la xarxa mitjançant el filtratge d'adreces PAN múltiple assistit per maquinari

- Consum d'energia reduït assistit per maquinari avançat

- Microcontrolador AVR® de 8 bits d'alt rendiment i baixa potència

- Arquitectura RISC avançada

- 135 Instruccions potents: la majoria d'execucions de cicle de rellotge individual

- Registres de treball d'ús general 32×8 / Multiplicador de 2 cicles en xip

- Rendiment de fins a 16 MIPS a 16 MHz i 1.8 V: funcionament totalment estàtic

- Memòries de dades i programes no volàtils

- 256K/128K/64K bytes de flaix autoprogramable al sistema

- Resistència: 10 cicles d'escriptura/esborrat a 000 °C (125 cicles a 25 °C)

- EEPROM de 8K/4K/2K bytes

- Resistència: 20 cicles d'escriptura/esborrat a 000 °C (125 cicles a 100 °C)

- SRAM interna de 32K/16K/8K bytes

- JTAG (Compatible amb IEEE std. 1149.1) Interfície

- Capacitats d'escaneig de límits segons JTAG Estàndard

- Suport ampli de depuració en xip

- Programació de Flash EEPROM, Fusibles i Bits de bloqueig a través de JTAG interfície

- Característiques perifèriques

- Múltiples canals de temporitzador/comptador i PWM

- Comptador en temps real amb oscil·lador separat

- Convertidor A/D de 10 bits i 330 ks/s; Comparador analògic; Sensor de temperatura en xip

- Interfície sèrie SPI mestre/esclau

- Dos USART sèries programables

- Interfície sèrie de 2 fils orientada a bytes

- Manejador avançat d'interrupcions i modes d'estalvi d'energia

- Temporitzador Watchdog amb oscil·lador separat en xip

- Reinicialització d'encesa i detector de baixa corrent

- Transceptor de baixa potència totalment integrat per a la banda ISM de 2.4 GHz

- Alta potència Ampsuport de lificació mitjançant la supressió del lòbul lateral de l'espectre TX

- Taxes de dades admeses: 250 kb/s i 500 kb/s, 1 Mb/s, 2 Mb/s

- -100 dBm de sensibilitat RX; Potència de sortida TX de fins a 3.5 dBm

- MAC assistit per maquinari (reconeixement automàtic, reintent automàtic)

- Comptador de símbols IEEE 32 de 802.15.4 bits

- SFD-detecció, propagació; Desextensió; Enquadrament ; CRC-16 Càlcul

- Diversitat d'antena i control TX/RX / TX/RX 128 Byte Frame Buffer

- Sintetitzador PLL amb espai de canal de 5 MHz i 500 kHz per a la banda ISM de 2.4 GHz

- Seguretat de maquinari (AES, True Random Generator)

- Oscil·ladors de cristall integrats (32.768 kHz i 16 MHz, es necessita un cristall extern)

- E/S i paquet

- 33 línies d'E/S programables

- QFN de 48 coixinets (RoHS/totalment verd)

- Interval de temperatura: -40 °C a 125 °C Industrial

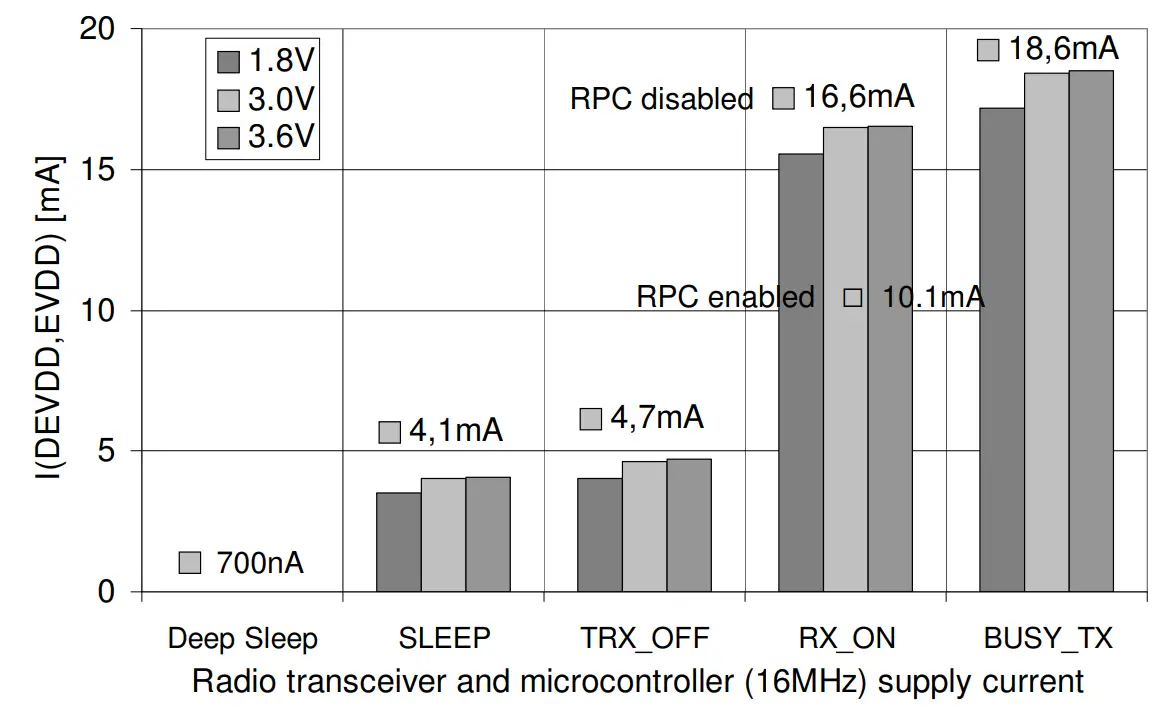

- Consum d'energia ultra baix (1.8 a 3.6 V) per a AVR i Rx/Tx: 10.1 mA/18.6 mA

- Mode actiu de la CPU (16 MHz): 4.1 mA

- Transceptor de 2.4 GHz: RX_ON 6.0 mA / TX 14.5 mA (potència de sortida màxima de TX)

- Mode de repòs profund: <700nA @ 25 °C

- Grau de velocitat: 0 – 16 MHz @ 1.8 – 3.6 V rang amb vol integrattage reguladors

Aplicacions

- ZigBee®/ IEEE 802.15.4-2011/2006/2003™: dispositiu amb funcions completes i reduïdes

- Transceptor de banda ISM de 2.4 GHz d'ús general amb microcontrolador

- Aplicacions RF4CE, SP100, WirelessHART™, ISM i IPv6/6LoWPAN

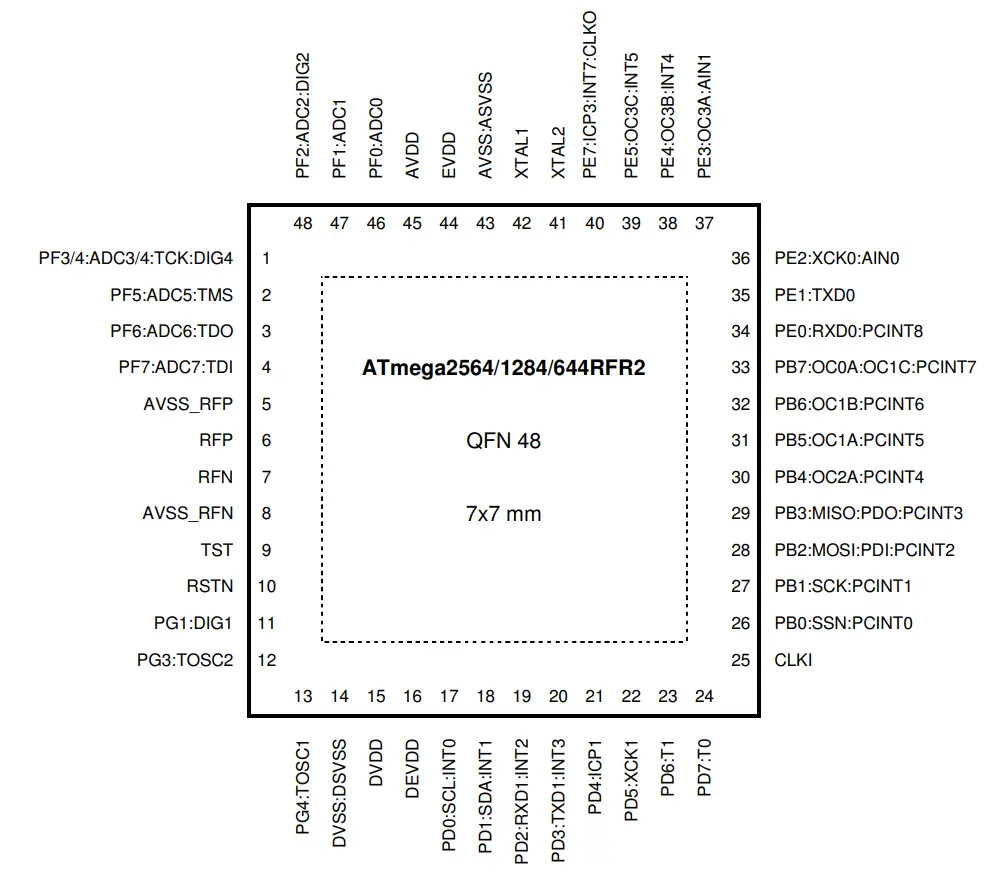

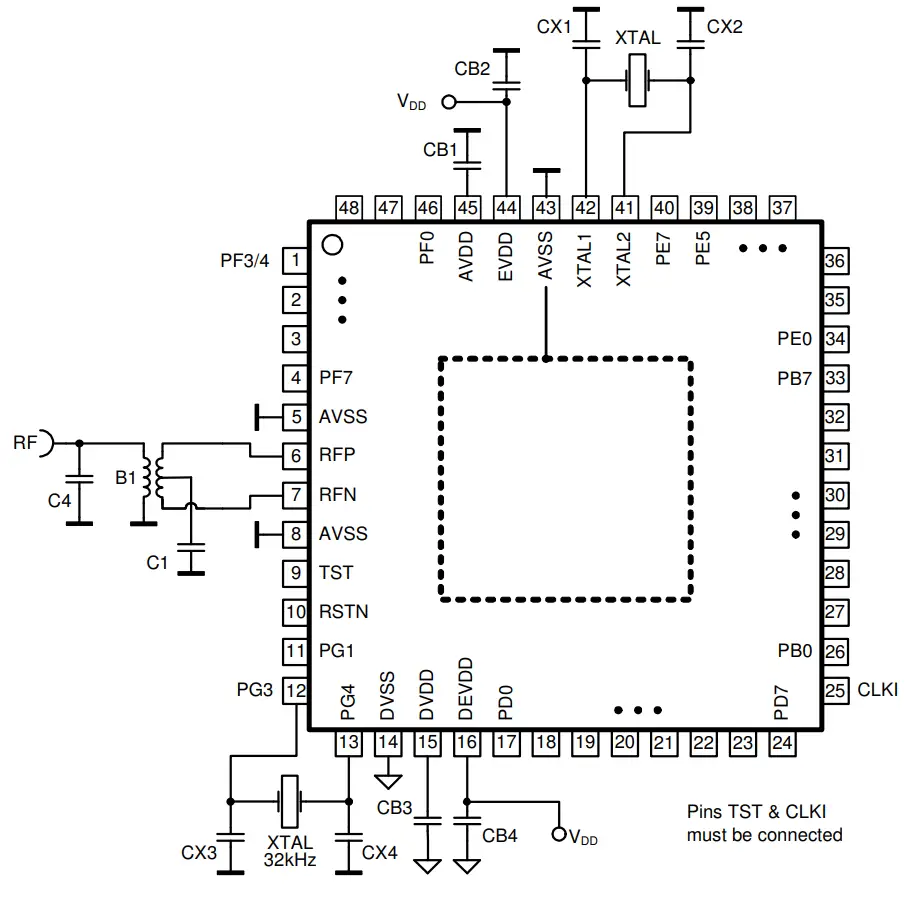

Configuracions de pins

Figura 1-1. Pinout ATmega2564/1284/644RFR2

Nota: El gran coixinet central que hi ha sota el paquet QFN/MLF està fet de metall i està connectat internament a AVSS. S'ha de soldar o enganxar al tauler per garantir una bona estabilitat mecànica. Si el coixinet central es deixa sense connectar, el paquet es pot afluixar del tauler. No es recomana utilitzar la paleta exposada com a reemplaçament de les agulles AVSS habituals.

Exempció de responsabilitat

Els valors típics continguts en aquest full de dades es basen en resultats de simulació i caracterització d'altres microcontroladors AVR i transceptors de ràdio fabricats amb una tecnologia de procés similar. Els valors mínims i màxims estaran disponibles després de caracteritzar el dispositiu.

Acabatview

L'ATmega2564/1284/644RFR2 és un microcontrolador CMOS de 8 bits de baixa potència basat en l'arquitectura RISC millorada AVR combinada amb un transceptor d'alta velocitat de dades per a la banda ISM de 2.4 GHz.

En executar instruccions potents en un sol cicle de rellotge, el dispositiu aconsegueix rendiments propers a 1 MIPS per MHz, cosa que permet al dissenyador del sistema optimitzar el consum d'energia en comparació amb la velocitat de processament.

El transceptor de ràdio proporciona altes velocitats de dades des de 250 kb/s fins a 2 Mb/s, maneig de trames, una sensibilitat excepcional del receptor i una gran potència de sortida de transmissió que permeten una comunicació sense fils molt robusta.

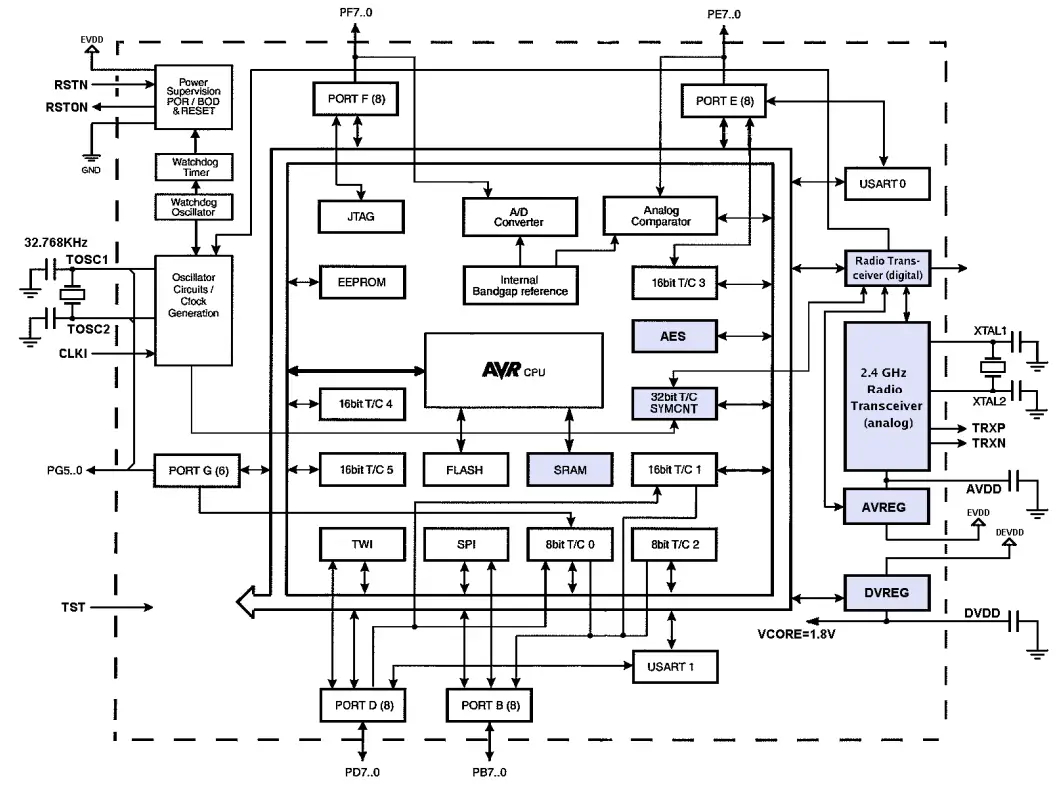

Diagrama de blocs

Figura 3-1 Diagrama de blocs

El nucli AVR combina un ric conjunt d'instruccions amb 32 registres de treball d'ús general. Els 32 registres estan connectats directament a la Unitat Lògica Aritmètica (ALU). Es pot accedir a dos registres independents amb una sola instrucció executada en un cicle de rellotge. L'arquitectura resultant és molt eficient en codi, alhora que aconsegueix un rendiment fins a deu vegades més ràpid que els microcontroladors CISC convencionals. El sistema inclou el vol interntage regulació i una gestió avançada de l'energia. Es distingeix pel petit corrent de fuga que permet un temps de funcionament prolongat des de la bateria.

El transceptor de ràdio és una solució ZigBee totalment integrada que utilitza un nombre mínim de components externs. Combina un excel·lent rendiment de RF amb baix cost, mida petita i baix consum de corrent. El transceptor de ràdio inclou un sintetitzador de N fraccional estabilitzat amb cristalls, un transmissor i un receptor, i un processament complet del senyal d'espectre propagat de seqüència directa (DSSS) amb difusió i desexpansió. El dispositiu és totalment compatible amb els estàndards IEEE802.15.4-2011/2006/2003 i ZigBee. L'ATmega2564/1284/644RFR2 ofereix les següents característiques: 256K/128K/64K bytes de flaix programable al sistema (ISP) amb capacitats de lectura mentre escriptura, 8K/4K/2K bytes EEPROM, 32K/16K/8K bytes SRAM, fins a 35 línies d'E/S de propòsit general, 32 registres de treball d'ús general, comptador en temps real (RTC), 6 temporitzadors/comptadors flexibles amb modes de comparació i PWM, un temporitzador/comptador de 32 bits, 2 USART, un byte de 2 fils orientat Interfície sèrie, un convertidor analògic a digital (ADC) de 8 canals i 10 bits amb una entrada diferencial opcional.tagi amb guany programable, temporitzador programable Watchdog amb oscil·lador intern, un port sèrie SPI, IEEE std. 1149.1 compatible JTAG interfície de prova, també s'utilitza per accedir al sistema de depuració on-chip i programació i 6 modes d'estalvi d'energia seleccionables per programari.

El mode inactiu atura la CPU mentre permet que la SRAM, el temporitzador/comptadors, el port SPI i el sistema d'interrupció continuïn funcionant. El mode d'apagada desa el contingut del registre, però congela l'oscil·lador, desactivant totes les altres funcions del xip fins a la següent interrupció o restabliment del maquinari. En el mode d'estalvi d'energia, el temporitzador asíncron continua funcionant, cosa que permet a l'usuari mantenir una base de temporitzador mentre la resta del dispositiu està dormint. El mode de reducció de soroll ADC atura la CPU i tots els mòduls d'E/S excepte el temporitzador asíncron i l'ADC, per minimitzar el soroll de commutació durant les conversions ADC. En mode d'espera, l'oscil·lador RC s'està executant mentre la resta del dispositiu està dormint. Això permet una arrencada molt ràpida combinada amb un baix consum d'energia. En el mode d'espera ampliat, tant l'oscil·lador RC principal com el temporitzador asíncron continuen funcionant.

El corrent de subministrament típic del microcontrolador amb el rellotge de la CPU ajustat a 16 MHz i el transceptor de ràdio per als estats més importants es mostra a la figura 3-2 següent.

Figura 3-2 Corrent d'alimentació del transceptor de ràdio i del microcontrolador (16 MHz).

La potència de sortida de transmissió s'estableix al màxim. Si el transceptor de ràdio està en mode SLEEP, el corrent només es dissipa pel microcontrolador AVR.

En el mode de repòs profund, tots els blocs digitals principals sense requisits de retenció de dades es desconnecten del subministrament principal proporcionant un corrent de fuga molt petit. El temporitzador de vigilant, el comptador de símbols MAC i l'oscil·lador de 32.768 kHz es poden configurar per continuar funcionant.

El dispositiu es fabrica amb la tecnologia de memòria no volàtil d'alta densitat d'Atmel.

El Flash ISP On-Chip permet que la memòria del programa es reprograma al sistema mitjançant una interfície sèrie SPI, un programador de memòria no volàtil convencional o un programa d'arrencada en xip que s'executa al nucli AVR. El programa d'arrencada pot utilitzar qualsevol interfície per descarregar el programa d'aplicació a la memòria Flash de l'aplicació.

El programari de la secció Flash d'arrencada continuarà executant-se mentre s'actualitza la secció Flash de l'aplicació, proporcionant una operació real de lectura mentre escriptura. En combinar una CPU RISC de 8 bits amb un flaix autoprogramable al sistema en un xip monolític, l'Atmel ATmega2564/1284/644RFR2 és un potent microcontrolador que proporciona una solució altament flexible i rendible per a moltes aplicacions de control incrustades.

L'ATmega2564/1284/644RFR2 AVR és compatible amb un conjunt complet d'eines de desenvolupament de programes i sistemes que inclouen: compilador C, assembladors de macros, depuradors/simuladors de programes, emuladors en circuit i kits d'avaluació.

Descripcions de pins

EVDD

Alimentació analògica externa voltage.

DEVDD

Subministrament digital extern voltage.

AVDD

Subministrament analògic regulat voltage (generat internament).

DVDD

Subministrament digital regulat voltage (generat internament).

DVSS

Terra digital.

AVSS

Terra analògica.

Port B (PB7…PB0)

El port B és un port d'E/S bidireccional de 8 bits amb resistències d'extracció internes (seleccionades per a cada bit). Els buffers de sortida del port B tenen característiques d'unitat simètriques amb una gran capacitat d'aigüe i font. Com a entrades, els pins del port B que s'estimen a baix externament generaran corrent si s'activen les resistències d'extracció. Els pins del port B s'estableixen en tres estats quan s'activa una condició de restabliment, fins i tot si el rellotge no està funcionant.

El port B també ofereix funcions de diverses característiques especials de l'ATmega2564/1284/644RFR2.

Port D (PD7…PD0)

El port D és un port d'E/S bidireccional de 8 bits amb resistències d'extracció internes (seleccionades per a cada bit). Els buffers de sortida del port D tenen característiques d'unitat simètriques amb una gran capacitat d'aigüe i font. Com a entrades, els pins del port D que s'estimen a baix externament generaran corrent si s'activen les resistències d'extracció. Els pins del port D s'estableixen en tres estats quan s'activa una condició de restabliment, fins i tot si el rellotge no funciona.

El port D també proporciona funcions de diverses característiques especials de l'ATmega2564/1284/644RFR2.

Port E (PE7,PE5...PE0)

Internament, el port E és un port d'E/S bidireccional de 8 bits amb resistències d'extracció internes (seleccionades per a cada bit). Els buffers de sortida del Port E tenen característiques d'unitat simètriques amb una gran capacitat d'enfonsament i font. Com a entrades, els pins del port E que s'estimen a baix externament generaran corrent si s'activen les resistències pull-up. Els pins del port E es mostren en tres estats quan s'activa una condició de restabliment, fins i tot si el rellotge no està funcionant.

A causa del baix nombre de pins del paquet QFN48, el port E6 no està connectat a un pin. El port E també ofereix funcions de diverses característiques especials de l'ATmega2564/1284/644RFR2.

Port F (PF7..PF5,PF4/3,PF2…PF0)

Internament, el port F és un port d'E/S bidireccional de 8 bits amb resistències d'extracció internes (seleccionades per a cada bit). Els buffers de sortida del port F tenen característiques d'unitat simètriques amb una gran capacitat d'enfonsament i font. Com a entrades, els pins del port F que s'estimen a baix externament generaran corrent si s'activen les resistències d'extracció. Els pins del port F es mostren en tres estats quan s'activa una condició de restabliment, fins i tot si el rellotge no està funcionant.

A causa del baix nombre de pins del paquet QFN48, els ports F3 i F4 estan connectats al mateix pin. La configuració d'E/S s'ha de fer amb cura per evitar una dissipació excessiva de potència.

El port F també ofereix funcions de diverses característiques especials de l'ATmega2564/1284/644RFR2.

Port G (PG4,PG3,PG1)

Internament, el port G és un port d'E/S bidireccional de 6 bits amb resistències d'extracció internes (seleccionades per a cada bit). Els buffers de sortida del Port G tenen característiques d'unitat simètriques amb una gran capacitat d'aigüe i font. Tanmateix, la força del controlador de PG3 i PG4 es redueix en comparació amb els altres pins de port. La sortida voltagLa caiguda (VOH, VOL) és més alta mentre que el corrent de fuga és menor. Com a entrades, els pins del port G que s'estimen a baix externament generaran corrent si s'activen les resistències d'extracció. Els pins del port G s'estableixen en tres estats quan s'activa una condició de restabliment, fins i tot si el rellotge no està funcionant.

A causa del baix nombre de pins del port del paquet QFN48 G0, G2 i G5 no estan connectats a un pin.

El port G també ofereix funcions de diverses característiques especials de l'ATmega2564/1284/644RFR2.

AVSS_RFP

AVSS_RFP és un pin de terra dedicat per al port d'E/S de RF bidireccional i diferencial.

AVSS_RFN

AVSS_RFN és un pin de terra dedicat per al port d'E/S de RF bidireccional i diferencial.

RFP

RFP és el terminal positiu del port d'E/S de RF bidireccional i diferencial.

RFN

RFN és el terminal negatiu del port d'E/S de RF bidireccional i diferencial.

RSTN

Restableix l'entrada. Un nivell baix en aquest pin durant més temps que la durada mínima del pols generarà un restabliment, fins i tot si el rellotge no està funcionant. No es garanteix que els polsos més curts generin un reinici.

XTAL1

Entrada a l'oscil·lador de cristall inversor de 16 MHz amplificador. En general, un cristall entre XTAL1 i XTAL2 proporciona el rellotge de referència de 16MHz del transceptor de ràdio.

XTAL2

Sortida de l'oscil·lador de cristall inversor de 16 MHz ampmés viu.

TST

El mode de programació i prova habiliten el pin. Si no s'utilitza el pin TST, tireu-lo cap a baix.

CLKI

Entrada al sistema de rellotge. Si se selecciona, proporciona el rellotge de funcionament del microcontrolador.

Pins no utilitzats

Els pins flotants poden provocar una dissipació de potència a l'entrada digital stage. Han d'estar connectats a una font adequada. En els modes de funcionament normal, es poden habilitar les resistències d'extracció internes (a Reiniciar tots els GPIO es configuren com a entrada i les resistències d'extracció encara no estan habilitades).

Els pins d'E/S bidireccionals no s'han de connectar directament a terra o font d'alimentació.

Cal connectar els pins d'entrada digital TST i CLKI. Si no s'utilitza el pin TST es pot connectar a AVSS mentre que CLKI s'hauria de connectar a DVSS.

Els pins de sortida són impulsats pel dispositiu i no suren. Els pins de la font d'alimentació respectives pins d'alimentació de terra estan connectats entre si internament.

XTAL1 i XTAL2 mai no es veuran obligats a subministrar voltage al mateix temps.

Compatibilitat i limitacions de funcions del paquet QFN-48

AREF

El vol de referènciatagLa sortida del convertidor A/D no està connectada a un pin de l'ATmega2564/1284/644RFR2.

Port E6

El port E6 no està connectat a un pin de l'ATmega2564/1284/644RFR2. Les funcions de pin alternatiu com a entrada de rellotge al temporitzador 3 i la interrupció externa 6 no estan disponibles.

Port F3 i F4

El port F3 i F4 estan connectats al mateix pin a l'ATmega2564/1284/644RFR2. La configuració de sortida s'ha de fer amb cura per evitar un consum excessiu de corrent.

La funció de pin alternatiu del port F4 és utilitzada pel JTAG interfície. Si el JTAG s'utilitza la interfície, el port F3 s'ha de configurar com a entrada i la sortida de la funció de pin alternatiu DIG4 (indicador RX/TX) s'ha de desactivar. En cas contrari, el JTAG la interfície no funcionarà. El fusible SPIEN s'ha de programar per poder esborrar un programa que condueixi accidentalment el port F3.

Només hi ha 7 canals d'entrada d'un sol extrem a l'ADC disponibles.

Port G0

El port G0 no està connectat a un pin de l'ATmega2564/1284/644RFR2. La funció de pin alternatiu DIG3 (indicador RX/TX invertit) no està disponible. Si el JTAG no s'utilitza la interfície, la sortida de la funció de pin alternatiu DIG4 del port F3 encara es pot utilitzar com a indicador RX/TX.

Port G2

El port G2 no està connectat a un pin de l'ATmega2564/1284/644RFR2. La funció de pin alternatiu AMR (entrada de lectura de comptador automàtica asíncrona al temporitzador 2) no està disponible.

Port G5

El port G5 no està connectat a un pin de l'ATmega2564/1284/644RFR2. La funció de pin alternatiu OC0B (canal de comparació de sortida del temporitzador de 8 bits 0) no està disponible.

RSTON

La sortida de restabliment RSTON que indica l'estat de restabliment intern no està connectada a un pin de l'ATmega2564/1284/644RFR2.

Resum de configuració

Segons els requisits de l'aplicació, una mida de memòria variable permet optimitzar el consum de corrent i el corrent de fuga.

Taula 3-1 Configuració de la memòria

| Dispositiu | Flash | EEPROM | SRAM |

| ATmega2564RFR2 | 256 KB | 8 KB | 32 KB |

| ATmega1284RFR2 | 128 KB | 4 KB | 16 KB |

| ATmega644RFR2 | 64 KB | 2 KB | 8 KB |

El paquet i la configuració del pin associada són els mateixos per a tots els dispositius que proporcionen una funcionalitat completa a l'aplicació.

Taula 3-2 Configuració del sistema

| Dispositiu | paquet | GPIO | Serial IF | Canal ADC |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

Els dispositius estan optimitzats per a aplicacions basades en l'especificació ZigBee i IEEE 802.15.4. Tenir una pila d'aplicacions, una capa de xarxa, una interfície de sensor i un control de potència excel·lent combinat en un sol xip hauria de ser possible durant molts anys de funcionament.

Taula 3-3 Aplicació Profile

| Dispositiu | Aplicació |

| ATmega2564RFR2 | Coordinador de xarxa gran / encaminador per a IEEE 802.15.4 / ZigBee Pro |

| ATmega1284RFR2 | Coordinador de xarxa/encaminador per a IEEE 802.15.4 |

| ATmega644RFR2 | Dispositiu del node final / processador de xarxa |

Circuits d'aplicació

Esquema bàsic de l'aplicació

A la figura 2564-1284 següent es mostra un esquema bàsic d'aplicació de l'ATmega644/2/4RFR1 amb un connector de RF d'un sol extrem i la llista de materials associada a la Taula 4-1 a la pàgina 10. L'entrada de RF d'un sol extrem de 50Ω es transforma. a la impedància diferencial del port de RF de 100Ω mitjançant Balun B1. Els condensadors C1 i C2 proporcionen l'acoblament de CA de l'entrada de RF al port de RF, el condensador C4 millora la concordança.

Figura 4-1. Esquema bàsic de l'aplicació (paquet de 48 pins)

Els condensadors de derivació de la font d'alimentació (CB2, CB4) estan connectats al pin d'alimentació analògic extern (EVDD, pin 44) i al pin de subministrament digital extern (DEVDD, pin 16). El condensador C1 proporciona l'acoblament de CA requerit de RFN/RFP.

Els pins flotants poden provocar una dissipació excessiva de potència (per exemple, durant l'encesa). Han d'estar connectats a una font adequada. GPIO no s'ha de connectar directament a terra o font d'alimentació.

Cal connectar els pins d'entrada digital TST i CLKI. Si mai no s'utilitzarà el pin TST, es pot connectar a AVSS mentre que un pin CLKI no utilitzat es podria connectar a DVSS (vegeu el capítol "Pins no utilitzats").

Els condensadors CB1 i CB3 són condensadors de bypass per al vol analògic i digital integrattage reguladors per garantir un funcionament estable i millorar la immunitat al soroll.

Els condensadors s'han de col·locar el més a prop possible dels pins i han de tenir una connexió a terra de baixa resistència i baixa inductància per aconseguir el millor rendiment.

El cristall (XTAL), els dos condensadors de càrrega (CX1, CX2) i els circuits interns connectats als pins XTAL1 i XTAL2 formen l'oscil·lador de cristall de 16 MHz per al transceptor de 2.4 GHz. Per aconseguir la millor precisió i estabilitat de la freqüència de referència, s'han d'evitar grans capacitats paràsites. Les línies de cristall s'han d'encaminar el més curt possible i no a prop dels senyals d'E/S digitals. Això és especialment necessari per als modes d'alta velocitat de dades.

El cristall de 32.768 kHz connectat a l'oscil·lador de cristall intern de baixa potència (sub 1 µA) proporciona una referència de temps estable per a tots els modes de baixa potència, inclòs el comptador de símbols IEEE 32 de 802.15.4 bits ("Comptador de símbols MAC") i l'aplicació de rellotge en temps real mitjançant l'aplicació asíncron. temporitzador T/C2 (“Temporitzador/Comptador2 amb PWM i funcionament asíncron”).

La capacitat total de derivació, inclosos CX3 i CX4, no ha de superar els 15 pF a tots dos pins.

El corrent de subministrament molt baix de l'oscil·lador requereix un disseny acurat de la PCB i s'ha d'evitar qualsevol ruta de fuga.

La diafonia i la radiació de la commutació de senyals digitals als pins de cristall o als pins de RF poden degradar el rendiment del sistema. Es recomana programar els paràmetres mínims de força de la unitat per al senyal de sortida digital (vegeu "DPDS0 - Port Driver Strength Register 0").

Taula 4-1. Llista de materials (BdM)

| Designador | Descripció | Valor | Fabricant | Número de part | Comenta |

| B1 | Balun SMD

Balun / filtre SMD |

2.4 GHz | Tecnologia Wuerth Johanson | 748421245

2450FB15L0001 |

Filtre inclòs |

| CB1 CB3 | LDO VREG

condensador de derivació |

1 mF (mínim 100 nF) | AVX

Murata |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10% 16V |

| CB2 CB4 | Condensador de derivació de la font d'alimentació | 1 mF (mínim 100 nF) | |||

| CX1, CX2 | Condensador de càrrega de cristall de 16 MHz | 12 pF | AVX

Murata |

06035A120JA GRP1886C1H120JA01 | COG (0603) 5% 50V |

| CX3, CX4 | Condensador de càrrega de cristall de 32.768 kHz | 12 … 25 pF | |||

| C1, C2 | Condensador d'acoblament RF | 22 pF | Epcos Epcos AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 o 0603) |

| C4 (opcional) | Coincidència de RF | 0.47 pF | Johnstech | ||

| XTAL | Cristall | CX-4025 16 MHz

SX-4025 16 MHz |

ACAL Taitjen Siward | XWBBPL-F-1 A207-011 | |

| XTAL 32 kHz | Cristall | Rs = 100 kOhm |

Historial de revisions

Tingueu en compte que els números de pàgina de referència d'aquesta secció fan referència a aquest document. La revisió de referència d'aquesta secció es refereix a la revisió del document.

Rev. 42073BS-MCU Wireless-09/14

- Contingut sense canvis: recreat per al llançament combinat amb el full de dades.

Rev. 8393AS-MCU Wireless-02/13

- Alliberament inicial.

© 2014 Atmel Corporation. Tots els drets reservats. / Rev.: 42073BS-MCU Wireless-09/14 Atmel®, el logotip d'Atmel i les seves combinacions, Enabling Unlimited Possibilities® i altres són marques registrades o marques comercials d'Atmel Corporation o de les seves filials. Altres termes i noms de productes poden ser marques comercials d'altres.

Exempció de responsabilitat: la informació d'aquest document es proporciona en relació amb els productes Atmel. No s'atorga cap llicència, expressa o implícita, per preclusió o d'una altra manera, a cap dret de propietat intel·lectual en aquest document o en relació amb la venda de productes Atmel. EXCEPTE EL QUE ESTABLECTE ALS TERMES I CONDICIONS DE VENDA D'ATMEL UBICATS A L'ATMEL WEBLLOC, ATMEL NO ASSUMIR RESPONSABILITAT I RENUNCIA A QUALSEVOL GARANTIA EXPRESSA, IMPLÍCITA O LEGAL RELACIONADA AMB ELS SEUS PRODUCTES, INCLOSA, PERÒ NO LIMITADA A, LA GARANTIA IMPLÍCITA DE COMERCIABILITAT, IDONEIDAD PER A UN FINS NO PARTICULAR, INFRACCIÓ. EN CAP CAS, ATMEL SERÀ RESPONSABLE DE CAP DANYS DIRECTS, INDIRECTS, CONSEQUENTLS, PUNITIUS, ESPECIALS O INCIDENTALS (INCLOSOS, SENSE LIMITACIÓ, DANYS PER PÈRDUES I BENEFICIS, INTERRUPCIÓ DE NEGOCI O PÈRDUA D'INFORMACIÓ) DERIVATS DE LA POSIBILITAT D'ÚS PER A L'ÚS. AQUEST DOCUMENT, TOT I QUE ATMEL S'HA AVISAT DE LA POSSIBILITAT D'AQUESTS DANYS. Atmel no fa representacions ni garanteix pel que fa a l'exactitud o la integritat del contingut d'aquest document i es reserva el dret de fer canvis a les especificacions i descripcions dels productes en qualsevol moment sense previ avís. Atmel no es compromet a actualitzar la informació aquí continguda. Llevat que s'especifiqui el contrari, els productes Atmel no són adequats ni s'han d'utilitzar en aplicacions d'automoció. Els productes Atmel no estan pensats, autoritzats o garantits per utilitzar-los com a components en aplicacions destinades a donar suport o mantenir la vida.

Mouser Electronics

Distribuïdor autoritzat

Feu clic a View Informació sobre preus, inventari, lliurament i cicle de vida:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

Atenció al client

Corporació Atmel

1600 Technology Drive

San Jose, CA 95110

EUA

Tel: (+1)408-441-0311

Fax: (+1)408-487-2600

www.atmel.com

Documents/Recursos

|

Microcontrolador Atmel ATmega2564 AVR de 8 bits [pdfManual del propietari ATmega2564RFR2, ATmega1284RFR2, ATmega644RFR2, ATmega2564 Microcontrolador AVR de 8 bits, ATmega2564, Microcontrolador AVR de 8 bits, Microcontrolador AVR, Microcontrolador |