Atmel ATmega2564 8 位元 AVR 微控制器

特徵

- 硬體輔助多 PAN 位址過濾的網路支持

- 先進的硬體輔助降低功耗

- 高效能、低功耗 AVR® 8 位元微控制器

- 先進的 RISC 架構

- 135 條強大指令 – 大多數單時鐘週期執行

- 32×8 通用工作暫存器/片上 2 週期乘法器

- 16 MHz 和 16V 下吞吐量高達 1.8 MIPS – 全靜態操作

- 非揮發性程序和資料存儲器

- 256K/128K/64K 位元組系統內自編程快閃記憶體

- 耐久性:10°C 時 000'125 次寫入/擦除週期(25°C 時 000'85 次週期)

- 8K/4K/2K 位元組 EEPROM

- 耐久性:20°C 時 000'125 次寫入/擦除週期(100°C 時 000'25 次週期)

- 32K/16K/8K 位元組內部 SRAM

- JTAG (符合 IEEE 標準 1149.1)接口

- 根據 J 的邊界掃描功能TAG 標準

- 廣泛的片上調試支持

- 透過 J 對快閃記憶體 EEPROM、熔絲和鎖定位進行編程TAG 介面

- 周邊特性

- 多個定時器/計數器和 PWM 通道

- 具有獨立振盪器的即時計數器

- 10 位元、330 ks/s A/D 轉換器;模擬比較器;片上溫度感測器

- 主/從 SPI 串行接口

- 兩個可編程串行 USART

- 面向位元組的 2 線串行接口

- 進階中斷處理程序和省電模式

- 具有獨立片上振盪器的看門狗定時器

- 上電重置和低電流欠壓檢測器

- 適用於 2.4 GHz ISM 頻段的完全整合低功耗收發器

- 高功率 Amplifier 支援 TX 頻譜旁瓣抑制

- 支援的數據速率:250 kb/s 和 500 kb/s、1 Mb/s、2 Mb/s

- -100 dBm 接收靈敏度;發射輸出功率高達 3.5 dBm

- 硬體輔助 MAC(自動確認、自動重試)

- 32 位元 IEEE 802.15.4 符號計數器

- SFD-檢測、傳播;去傳播;取景; CRC-16 計算

- 天線分集和 TX/RX 控制/TX/RX 128 位元組幀緩衝器

- PLL 合成器,具有 5 MHz 和 500 kHz 通道間隔,適用於 2.4 GHz ISM 頻段

- 硬體安全(AES、真正的隨機產生器)

- 整合晶體振盪器(32.768 kHz 和 16 MHz,需要外部晶體)

- I/O 和封裝

- 33 條可編程 I/O 線

- 48 焊盤 QFN(RoHS/全綠)

- 溫度範圍:-40°C 至 125°C 工業級

- AVR 和 Rx/Tx 超低功耗(1.8 至 3.6V):10.1mA/18.6 mA

- CPU 活動模式 (16MHz):4.1 mA

- 2.4GHz 收發器:RX_ON 6.0 mA / TX 14.5 mA(最大 TX 輸出功率)

- 深度睡眠模式:<700nA @ 25°C

- 速度等級:0 – 16 MHz @ 1.8 – 3.6V 範圍,搭配整合音量tag監管者

應用領域

- ZigBee®/ IEEE 802.15.4-2011/2006/2003™ – 全功能與精簡功能設備

- 具有微控制器的通用 2.4GHz ISM 頻段收發器

- RF4CE、SP100、WirelessHART™、ISM 應用和 IPv6 / 6LoWPAN

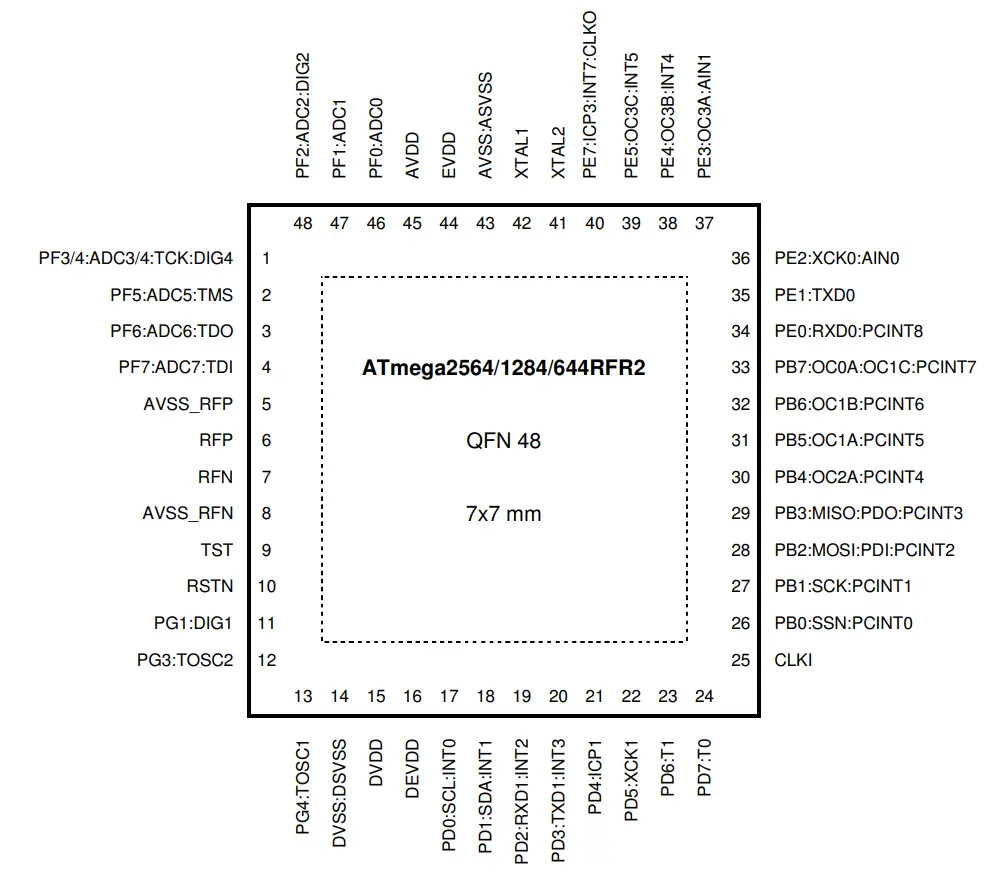

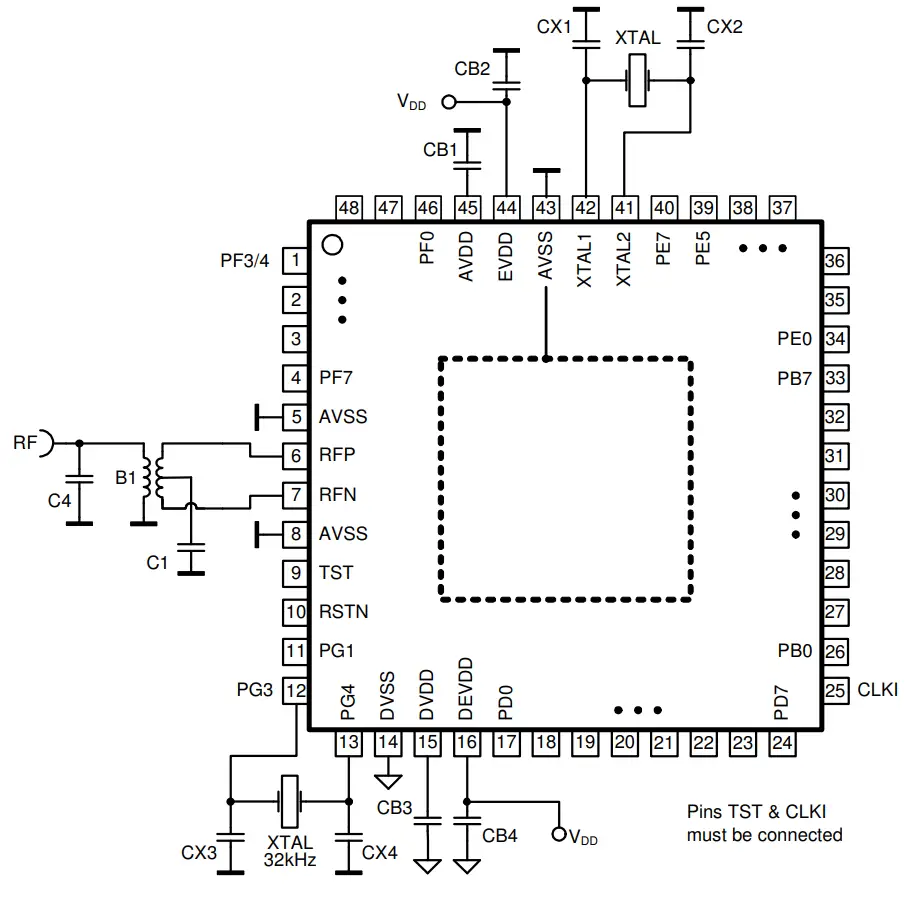

引腳配置

圖 1-1。 ATmega2564/1284/644RFR2 腳位分配

筆記:QFN/MLF 封裝下方的大中心焊盤由金屬製成,內部連接到 AVSS。應將其焊接或粘合到板上,以確保良好的機械穩定性。如果中心焊盤未連接,封裝可能會從板上鬆動。不建議使用裸露焊盤取代常規 AVSS 引腳。

免責聲明

本資料表中所包含的典型值是基於採用類似製程技術製造的其他 AVR 微控制器和無線電收發器的模擬和特性結果。裝置特徵化後即可獲得最小值和最大值。

超過view

ATmega2564/1284/644RFR2 是一款低功耗 CMOS 8 位元微控制器,基於 AVR 增強型 RISC 架構,並結合了適用於 2.4 GHz ISM 頻段的高資料速率收發器。

透過在單一時脈週期內執行強大的指令,該裝置可實現接近 1 MIPS/MHz 的吞吐量,從而使系統設計人員能夠優化功耗與處理速度。

該無線電收發器提供 250 kb/s 至 2 Mb/s 的高數據速率、幀處理、出色的接收器靈敏度和高發射輸出功率,從而實現非常強大的無線通訊。

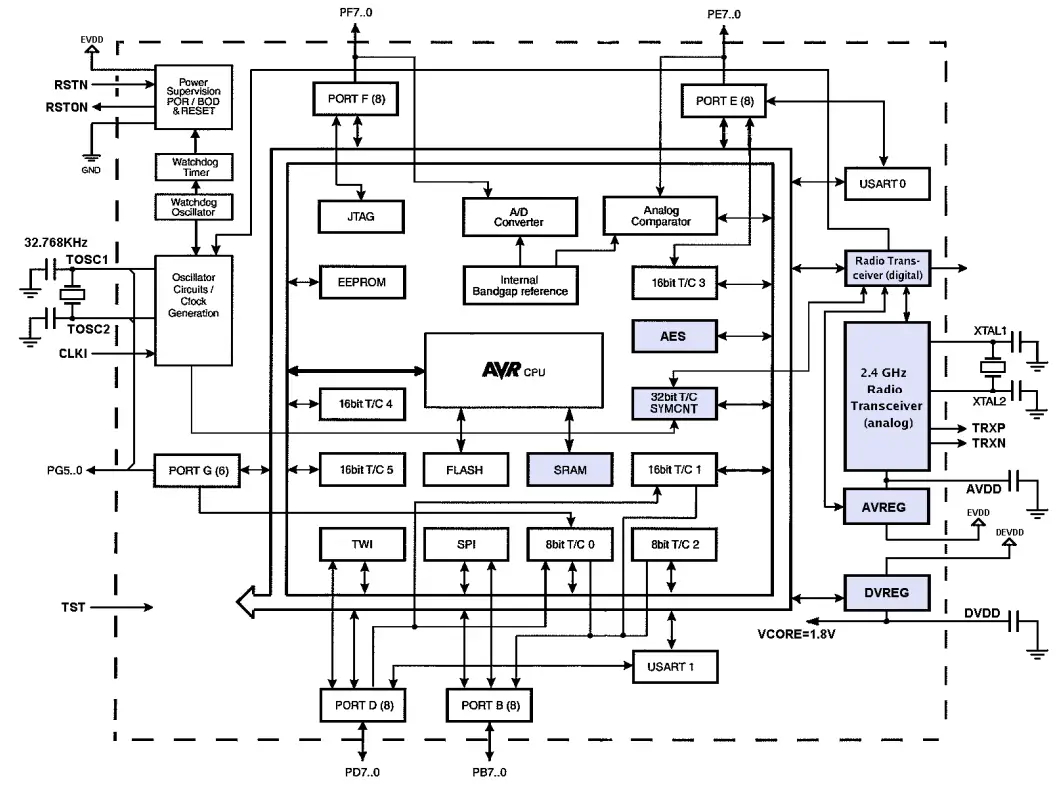

框圖

圖 3-1 框圖

AVR 核心結合了豐富的指令集和 32 個通用工作暫存器。所有 32 個暫存器都直接連接到算術邏輯單元 (ALU)。一個時脈週期內執行的一條指令可以存取兩個獨立的暫存器。由此產生的架構非常高效,同時吞吐量比傳統 CISC 微控制器快十倍。該系統包括內部卷tage 調節和先進的電源管理。其特點是漏電流小,可延長電池的工作時間。

此無線電收發器是一個完全整合的 ZigBee 解決方案,使用最少數量的外部組件。它將卓越的射頻性能與低成本、小尺寸和低電流消耗結合在一起。此無線電收發器包括晶體穩定分數 N 合成器、發射器和接收器,以及具有擴頻和解擴功能的完整直接序列擴頻訊號 (DSSS) 處理。本設備完全相容於IEEE802.15.4-2011/2006/2003和ZigBee標準。 ATmega2564/1284/644RFR2 提供以下功能:具有邊寫邊讀功能的 256K/128K/64K 位元組系統內可編程 (ISP) 快閃記憶體、8K/4K/2K 位元組 EEPROM、32K/16K/8K 位元組 SRAM、多達35 條通用I/O 線、32 個通用工作暫存器、即時計數器(RTC)、6 個具有比較模式和PWM 的靈活定時器/計數器、一個32 位元定時器/計數器、2 個USART、一個面向位元組的2 線串列接口,一個 8 通道、10 位元類比數位轉換器 (ADC),具有可選的差分輸入tage 具有可程式增益、具有內部振盪器的可程式看門狗定時器、SPI 序列埠、IEEE 標準。符合 1149.1 標準TAG 測試接口,也用於存取片上調試系統和編程以及 6 種軟體可選的省電模式。

空閒模式停止 CPU,同時允許 SRAM、定時器/計數器、SPI 連接埠和中斷系統繼續運作。掉電模式保存暫存器內容,但凍結振盪器,停用所有其他晶片功能,直到下一次中斷或硬體重設。在省電模式下,非同步定時器繼續運行,讓使用者在裝置的其餘部分休眠時維持定時器基數。 ADC 降噪模式會停止 CPU 和非同步定時器和 ADC 之外的所有 I/O 模組,以最大程度地減少 ADC 轉換期間的開關雜訊。在待機模式下,RC 振盪器正在運行,而裝置的其餘部分則處於休眠狀態。這樣可以實現非常快速的啟動和低功耗。在擴展待機模式下,主 RC 振盪器和非同步定時器繼續運作。

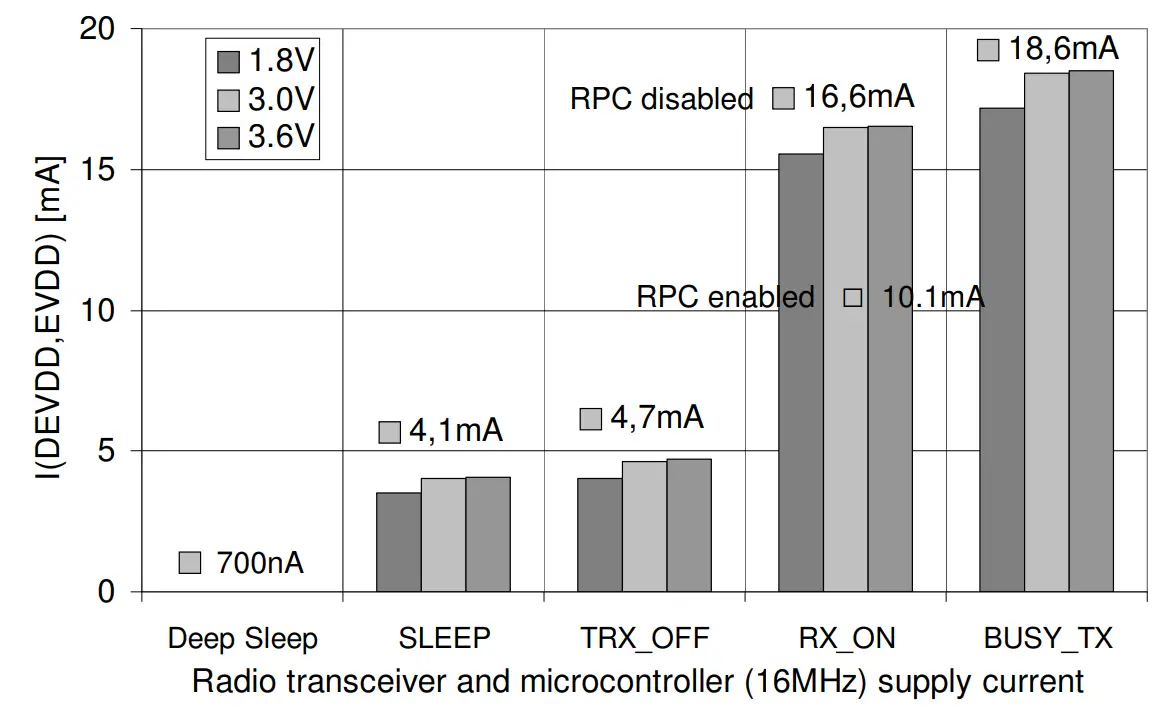

CPU 時脈設定為 16MHz 的微控制器和最重要狀態的無線電收發器的典型電源電流如下圖 3-2 所示。

圖 3-2 無線電收發器和微控制器 (16MHz) 電源電流

發射輸出功率設定為最大。如果無線電收發器處於睡眠模式,則電流僅由 AVR 微控制器消耗。

在深度睡眠模式下,所有沒有資料保留要求的主要數位模組都與主電源斷開,從而提供非常小的洩漏電流。看門狗定時器、MAC 符號計數器和 32.768kHz 振盪器可以設定為繼續運作。

此裝置採用 Atmel 的高密度非揮發性記憶體技術製造。

片上 ISP 快閃記憶體允許透過 SPI 串列介面、透過傳統的非揮發性記憶體程式設計器或透過在 AVR 核心上執行的片上引導程式對程式記憶體進行系統內重新編程。引導程式可以使用任何介面將應用程式下載到應用程式Flash記憶體中。

當應用程式快閃記憶體部分更新時,引導快閃記憶體部分中的軟體將繼續運行,從而提供真正的邊讀邊寫操作。 Atmel ATmega8/2564/1284RFR644 將2 位元RISC CPU 與單晶片上的系統內自編程快閃記憶體結合,成為一款功能強大的微控制器,可為許多嵌入式控制應用提供高度靈活且經濟高效的解決方案。

ATmega2564/1284/644RFR2 AVR 由全套程式和系統開發工具支持,包括:C 編譯器、巨集彙編器、程式偵錯器/模擬器、線上模擬器和評估套件。

引腳說明

外延電壓

外部類比電源電壓tage.

德維德

外部數位電源電壓tage.

電源電壓

調節類比電源電壓tage(內部生成)。

影碟

穩壓數位供電量tage(內部生成)。

DVSS

數字地面。

AVSS

模擬接地。

埠 B (PB7…PB0)

端口 B 是一個 8 位元雙向 I/O 端口,具有內部上拉電阻(為每位選擇)。連接埠 B 輸出緩衝器具有對稱驅動特性,具有高灌電流和拉電流能力。作為輸入,如果上拉電阻被激活,則外部拉低的連接埠 B 引腳將提供電流。當重設條件變為活動狀態時,即使時脈未運行,連接埠 B 接腳也會處於三態。

埠B也提供ATmega2564/1284/644RFR2的各種特殊功能的功能。

連接埠 D (PD7…PD0)

端口 D 是一個 8 位元雙向 I/O 端口,具有內部上拉電阻(為每位選擇)。連接埠 D 輸出緩衝器具有對稱驅動特性,具有高灌電流和拉電流能力。作為輸入,如果上拉電阻被激活,被外部拉低的連接埠 D 引腳將提供電流。當重設條件變為活動狀態時,即使時脈未運行,連接埠 D 接腳也會處於三態。

連接埠D也提供ATmega2564/1284/644RFR2的各種特殊功能的功能。

連接埠 E(PE7、PE5…PE0)

內部端口 E 是一個 8 位元雙向 I/O 端口,具有內部上拉電阻(為每位選擇)。連接埠 E 輸出緩衝器具有對稱驅動特性,具有高灌電流和拉電流能力。作為輸入,如果上拉電阻被激活,被外部拉低的連接埠 E 引腳將提供電流。當重設條件變為活動狀態時,即使時脈未運行,連接埠 E 接腳也會處於三態。

由於 QFN48 封裝的引腳數較少,因此連接埠 E6 未連接到引腳。 E連接埠也提供ATmega2564/1284/644RFR2的各種特殊功能的功能。

Port F (PF7..PF5,PF4/3,PF2…PF0)

內部端口F是一個8位元雙向I/O端口,具有內部上拉電阻(為每一位選擇)。 F 連接埠輸出緩衝器具有對稱驅動特性,具有高灌電流和拉電流能力。作為輸入,如果上拉電阻被激活,被外部拉低的連接埠 F 引腳將提供電流。當重設條件變為活動狀態時,即使時脈未運行,連接埠 F 接腳也會處於三態。

由於 QFN48 封裝的引腳數較少,因此連接埠 F3 和 F4 連接到同一引腳。 I/O 配置應謹慎進行,以避免功耗過高。

連接埠F也提供ATmega2564/1284/644RFR2的各種特殊功能的功能。

G 口(PG4、PG3、PG1)

內部端口G是一個6位元雙向I/O端口,具有內部上拉電阻(為每一位選擇)。連接埠 G 輸出緩衝器具有對稱驅動特性,具有高灌電流和拉電流能力。然而,與其他連接埠引腳相比,PG3 和 PG4 的驅動強度有所降低。輸出量tage drop (VOH, VOL) 較高,而漏電流較小。作為輸入,如果上拉電阻被激活,被外部拉低的連接埠 G 引腳將提供電流。當重設條件變為活動狀態時,即使時脈未運行,連接埠 G 接腳也會處於三態。

由於 QFN48 封裝的引腳數較少,連接埠 G0、G2 和 G5 沒有連接到引腳。

連接埠G也提供ATmega2564/1284/644RFR2的各種特殊功能的功能。

AVSS_RFP

AVSS_RFP 是雙向差分 RF I/O 連接埠的專用接地引腳。

AVSS_RFN

AVSS_RFN 是雙向差分 RF I/O 連接埠的專用接地引腳。

徵求建議書

RFP 是雙向差分 RF I/O 連接埠的正極端子。

射頻網路

RFN 是雙向差分 RF I/O 連接埠的負極端子。

RSTN

重置輸入。即使時脈未運行,此引腳上的低電平持續時間超過最小脈衝長度也會產生重設。較短的脈衝不能保證產生重設。

晶振1

反相 16MHz 晶體振盪器的輸入 amp淨化器。一般來說,XTAL1 和 XTAL2 之間的晶體提供無線電收發器的 16MHz 參考時脈。

晶振2

反相16MHz晶體振盪器的輸出 amp擴音器。

尖沙咀

編程和測試模式使能引腳。如果未使用引腳 TST,則將其拉至低電位。

時脈訊號

輸入到時脈系統。如果選擇,它提供微控制器的操作時鐘。

未使用的引腳

浮動引腳可能會導致數位輸入中的功耗tage.它們應該連接到適當的來源。在正常操作模式下,可以啟用內部上拉電阻(在重設中,所有 GPIO 均配置為輸入,且上拉電阻仍未啟用)。

雙向 I/O 接腳不得直接接地或電源。

數位輸入引腳 TST 和 CLKI 必須連接。如果未使用接腳 TST 可連接至 AVSS,而 CLKI 應連接至 DVSS。

輸出引腳由裝置驅動且不浮動。電源引腳和接地引腳在內部連接在一起。

XTAL1 和 XTAL2 不得被迫提供電壓tage 同時。

QFN-48 封裝的相容性和功能限制

阿瑞夫

參考體積tagA/D 轉換器的輸出未連接到 ATmega2564/1284/644RFR2 中的接腳。

E6端口

連接埠 E6 未連接到 ATmega2564/1284/644RFR2 中的接腳。備用引腳用作定時器 3 的時鐘輸入,且外部中斷 6 不可用。

端口 F3 和 F4

連接埠 F3 和 F4 連接到 ATmega2564/1284/644RFR2 中的相同接腳。應仔細進行輸出配置,以避免電流消耗過多。

連接埠 F4 的備用引腳功能由 J 使用TAG 介面.如果 JTAG 使用介面時,連接埠 F3 必須配置為輸入,並且必須停用備用引腳功能輸出 DIG4(RX/TX 指示器)。否則 JTAG 介面將無法工作。應對 SPIEN 熔絲進行編程,以便能夠擦除意外驅動連接埠 F3 的程式。

ADC 僅有 7 個可用的單端輸入通道。

G0端口

連接埠 G0 未連接到 ATmega2564/1284/644RFR2 中的接腳。備用引腳功能 DIG3(反向 RX/TX 指示器)無法使用。如果 JTAG 介面未使用時,F4 埠的 DIG3 復用接腳功能輸出仍可用作 RX/TX 指示燈。

G2端口

連接埠 G2 未連接到 ATmega2564/1284/644RFR2 中的接腳。備用引腳功能 AMR(定時器 2 的非同步自動抄表輸入)無法使用。

G5端口

連接埠 G5 未連接到 ATmega2564/1284/644RFR2 中的接腳。備用引腳功能 OC0B(8 位元定時器 0 的輸出比較通道)無法使用。

瑞斯頓

表示內部重設狀態的 RSTON 重設輸出未連接到 ATmega2564/1284/644RFR2 中的接腳。

配置總結

根據應用需求,可變記憶體大小可以優化電流消耗和洩漏電流。

表 3-1 記憶體配置

| 裝置 | 閃光 | EEPROM | 靜態隨機記憶體 |

| ATmega2564RFR2 | 256KB | 8KB | 32KB |

| ATmega1284RFR2 | 128KB | 4KB | 16KB |

| ATmega644RFR2 | 64KB | 2KB | 8KB |

對於為應用程式提供完整功能的所有裝置,封裝和相關引腳配置都是相同的。

表 3-2 系統配置

| 裝置 | 包裹 | 通用輸入輸出介面 | 序列中頻 | ADC通道 |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART、SPI、TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART、SPI、TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART、SPI、TWI | 7 |

這些裝置針對基於 ZigBee 和 IEEE 802.15.4 規範的應用進行了最佳化。將應用程式堆疊、網路層、感測器介面和出色的電源控制結合在一個晶片中,並運行多年應該是可能的。

表 3-3 應用專業版file

| 裝置 | 應用 |

| ATmega2564RFR2 | 適用於 IEEE 802.15.4 / ZigBee Pro 的大型網路協調器/路由器 |

| ATmega1284RFR2 | IEEE 802.15.4 網路協調器/路由器 |

| ATmega644RFR2 | 終端節點設備/網路處理器 |

應用電路

基本應用原理圖

單端射頻連接器的 ATmega2564/1284/644RFR2 的基本應用原理圖如下圖 4-1 所示,相關物料清單請參閱第 4 頁表 1-10。差分RF 連接埠阻抗。電容器 C50 和 C100 提供 RF 輸入到 RF 連接埠的交流耦合,電容器 C1 改善匹配。

圖 4-1。基本應用原理圖(48引腳封裝)

電源旁路電容器(CB2、CB4)連接到外部類比電源引腳(EVDD,引腳 44)和外部數位電源引腳(DEVDD,引腳 16)。電容器 C1 提供 RFN/RFP 所需的交流耦合。

浮動引腳可能會導致功耗過大(例如,在通電期間)。它們應該連接到適當的來源。 GPIO 不得直接接地或連接電源。

數位輸入引腳 TST 和 CLKI 必須連接。如果引腳 TST 永遠不會被使用,則可以將其連接到 AVSS,而未使用的引腳 CLKI 可以連接到 DVSS(請參閱「未使用的引腳」章節)。

電容 CB1 和 CB3 是整合類比和數位音量的旁路電容。tage調節器,以確保穩定運作並提高抗噪能力。

電容器應盡可能靠近引腳放置,並且應具有低電阻和低電感接地連接,以實現最佳性能。

晶體 (XTAL)、兩個負載電容器 (CX1、CX2) 以及連接到引腳 XTAL1 和 XTAL2 的內部電路構成了 16GHz 收發器的 2.4MHz 晶體振盪器。為了實現參考頻率的最佳精度和穩定性,必須避免大的寄生電容。晶體線的佈線應盡可能短,並且不要靠近數位 I/O 訊號。這對於高數據速率模式尤其需要。

連接到內部低功耗(低於32.768μA)晶體振盪器的1 kHz 晶體為所有低功耗模式提供穩定的時間參考,包括32 位元IEEE 802.15.4 符號計數器(「MAC 符號計數器」)和使用非同步的即時時鐘應用。

兩個引腳上的總並聯電容(包括 CX3、CX4)不應超過 15pF。

振盪器的電源電流非常低,因此需要仔細佈局 PCB,並且必須避免任何洩漏路徑。

將數位訊號切換到晶體引腳或 RF 引腳時產生的串擾和輻射會降低系統效能。建議對數位輸出訊號的最小驅動強度設定進行程式設計(請參閱「DPDS0 – 連接埠驅動強度暫存器 0」)。

表 4-1。物料清單 (BoM)

| 代號 | 描述 | 價值 | 製造商 | 零件編號 | 評論 |

| B1 | 貼片巴倫

貼片巴倫/濾波器 |

2.4GHz | 伍爾特約翰遜技術公司 | 748421245

2450FB15L0001 |

包括過濾器 |

| CB1 CB3 | 低壓差穩壓器

旁路電容 |

1 mF(最小 100nF) | AVX

村田 |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10%16V |

| CB2 CB4 | 電源旁路電容 | 1 mF(最小 100nF) | |||

| CX1、CX2 | 16MHz晶振負載電容 | 12皮法 | AVX

村田 |

06035A120JA GRP1886C1H120JA01 | 重心 (0603) 5%50V |

| CX3、CX4 | 32.768kHz晶振負載電容 | 12 … 25 皮法 | |||

| C1、C2 | 射頻耦合電容 | 22皮法 | Epcos 愛普科斯 AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 或 0603) |

| C4(可選) | 射頻匹配 | 0.47皮法 | 約翰泰克 | ||

| 晶振 | 水晶 | CX-4025 16兆赫

SX-4025 16 兆赫 |

ACAL 泰特延西沃德 | XWBBPL-F-1 A207-011 | |

| 晶體 32kHz | 水晶 | Rs=100 kOhm |

修訂歷史

請注意,本節中引用的頁碼指的是本文檔。本節所引用的修訂版均指文件修訂版。

修訂版 42073BS-MCU 無線-09/14

- 內容不變 - 重新建立以與資料表合併發布。

修訂版 8393AS-MCU 無線 - 02/13

- 初次發布。

© 2014 Atmel 公司。版權所有。 / Rev.: 42073BS-MCU Wireless-09/14 Atmel®、Atmel 標誌及其組合、Enabling Unlimited Possibilities® 以及其他是 Atmel Corporation 或其子公司的註冊商標或商標。其他術語和產品名稱可能是其他人的商標。

免責聲明:本文檔中的資訊與 Atmel 產品相關。本文檔或與 Atmel 產品銷售相關的任何智慧財產權均未以禁止反言或其他方式授予任何明示或暗示的許可。除非 ATMEL 上的 ATMEL 銷售條款與條件另有規定 WEBSITE, ATMEL 不承擔任何責任,並且不承擔與其產品有關的任何明示、默示或法定保證,包括但不限於對適銷性、特定用途適用性或不侵權的默示保證。 在任何情況下,ATMEL 均不對因使用或無法使用而引起的任何直接、間接、後果性、懲罰性、特殊或附帶損害(包括但不限於損失和利潤損害、業務中斷或信息丟失)負責本文件,即使 ATMEL 已被告知此類損害的可能性。 Atmel 對本文檔內容的準確性或完整性不作任何陳述或保證,並保留隨時更改規格和產品說明的權利,恕不另行通知。 Atmel 不承諾更新此處包含的信息。 除非另有明確規定,否則 Atmel 產品不適合也不應用於汽車應用。 Atmel 產品並非旨在、授權或保證用作旨在支持或維持生命的應用中的組件。

貿澤電子

授權經銷商

點擊進入 View 定價、庫存、交付和生命週期信息:

微晶片:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

客戶支援

愛特梅爾公司

1600技術驅動

聖荷西, CA 95110

美國

電話:(+1)408-441-0311

傳真:(+1)408-487-2600

www.atmel.com

文件/資源

|

Atmel ATmega2564 8 位元 AVR 微控制器 [pdf] 使用者手冊 ATmega2564RFR2、ATmega1284RFR2、ATmega644RFR2、ATmega2564 8位元AVR微控制器、ATmega2564、8位元AVR微控制器、AVR微控制器、微控制器 |