Microcontrolador Atmel ATmega2564 AVR de 8 bits

Características

- Soporte de rede mediante filtrado de enderezos PAN múltiple asistido por hardware

- Consumo de enerxía reducido asistido por hardware avanzado

- Microcontrolador AVR® de 8 bits de alto rendemento e baixa potencia

- Arquitectura RISC avanzada

- 135 instrucións potentes: a execución do ciclo de reloxo máis simple

- 32×8 rexistros de traballo de propósito xeral / multiplicador de 2 ciclos en chip

- Rendimento de ata 16 MIPS a 16 MHz e 1.8 V: operación totalmente estática

- Memoria de datos e programas non volátiles

- 256K/128K/64K bytes de flash autoprogramable no sistema

- Resistencia: 10 ciclos de escritura/borrado a 000 °C (125 ciclos a 25 °C)

- EEPROM de 8K/4K/2K bytes

- Resistencia: 20 ciclos de escritura/borrado a 000 °C (125 ciclos a 100 °C)

- SRAM interna de 32K/16K/8K bytes

- JTAG (Compatible con IEEE std. 1149.1) Interface

- Capacidades de exploración de límites segundo JTAG Estándar

- Amplo soporte de depuración no chip

- Programación de Flash EEPROM, Fusibles e Bits de bloqueo a través do JTAG interface

- Características periféricas

- Varias canles de temporizador/contador e PWM

- Contador en tempo real con oscilador separado

- Conversor A/D de 10 bits e 330 ks/s; Comparador analóxico; Sensor de temperatura no chip

- Interface serie SPI mestre/esclavo

- Dos USART serie programables

- Interface serie de 2 cables orientada a bytes

- Manexador de interrupcións avanzado e modos de aforro de enerxía

- Temporizador Watchdog con oscilador en chip separado

- Reinicio de encendido e detector de baixa intensidade

- Transceptor de baixa potencia totalmente integrado para banda ISM de 2.4 GHz

- Alta Potencia Ampsoporte de lifier mediante supresión de lóbulos laterales del espectro TX

- Taxas de datos admitidas: 250 kb/s e 500 kb/s, 1 Mb/s, 2 Mb/s

- -100 dBm Sensibilidade RX; Potencia de saída TX de ata 3.5 dBm

- MAC asistido por hardware (recoñecemento automático, reintento automático)

- Contador de símbolos IEEE 32 de 802.15.4 bits

- SFD-Detección, propagación; Despropagación; Encadramento ; CRC-16 Computación

- Diversidade de antenas e control TX/RX / TX/RX 128 Byte Frame Buffer

- Sintetizador PLL con espazamento de canles de 5 MHz e 500 kHz para a banda ISM de 2.4 GHz

- Seguridade de hardware (AES, True Random Generator)

- Osciladores de cristal integrados (32.768 kHz e 16 MHz, necesita cristal externo)

- E/S e paquete

- 33 liñas de E/S programables

- QFN de 48 almohadillas (RoHS/totalmente verde)

- Rango de temperatura: -40°C a 125°C Industrial

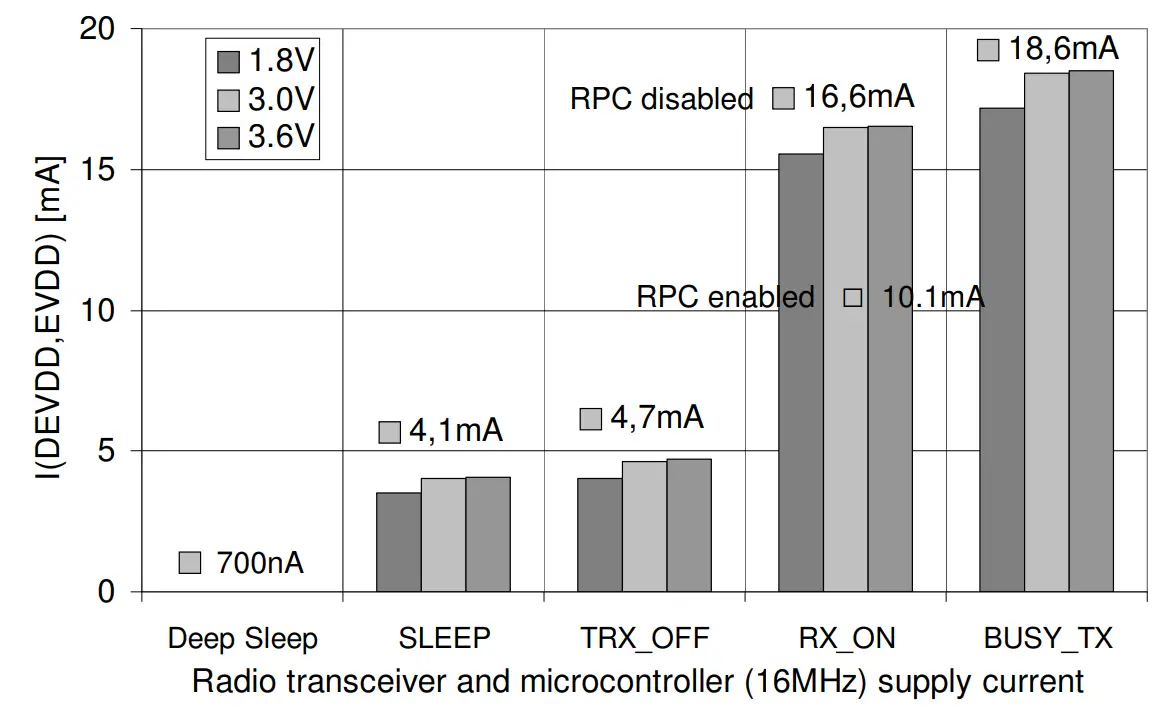

- Consumo de enerxía ultra baixo (1.8 a 3.6 V) para AVR e Rx/Tx: 10.1 mA/18.6 mA

- Modo activo da CPU (16 MHz): 4.1 mA

- Transceptor de 2.4 GHz: RX_ON 6.0 mA / TX 14.5 mA (potencia de saída máxima de TX)

- Modo de sono profundo: <700nA @ 25°C

- Grao de velocidade: 0 – 16 MHz @ rango de 1.8 – 3.6 V con vol. integradotage reguladores

Aplicacións

- ZigBee®/ IEEE 802.15.4-2011/2006/2003™ – Dispositivo de función completa e reducida

- Transceptor de banda ISM de 2.4 GHz de propósito xeral con microcontrolador

- Aplicacións RF4CE, SP100, WirelessHART™, ISM e IPv6/6LoWPAN

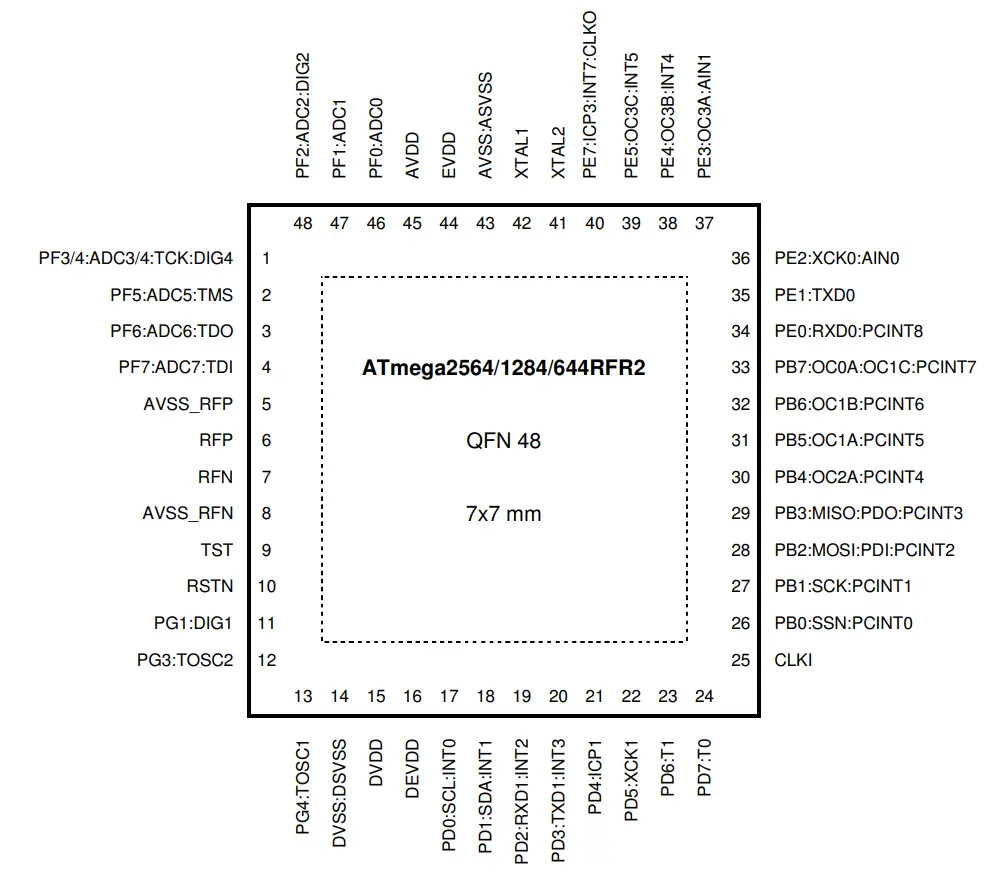

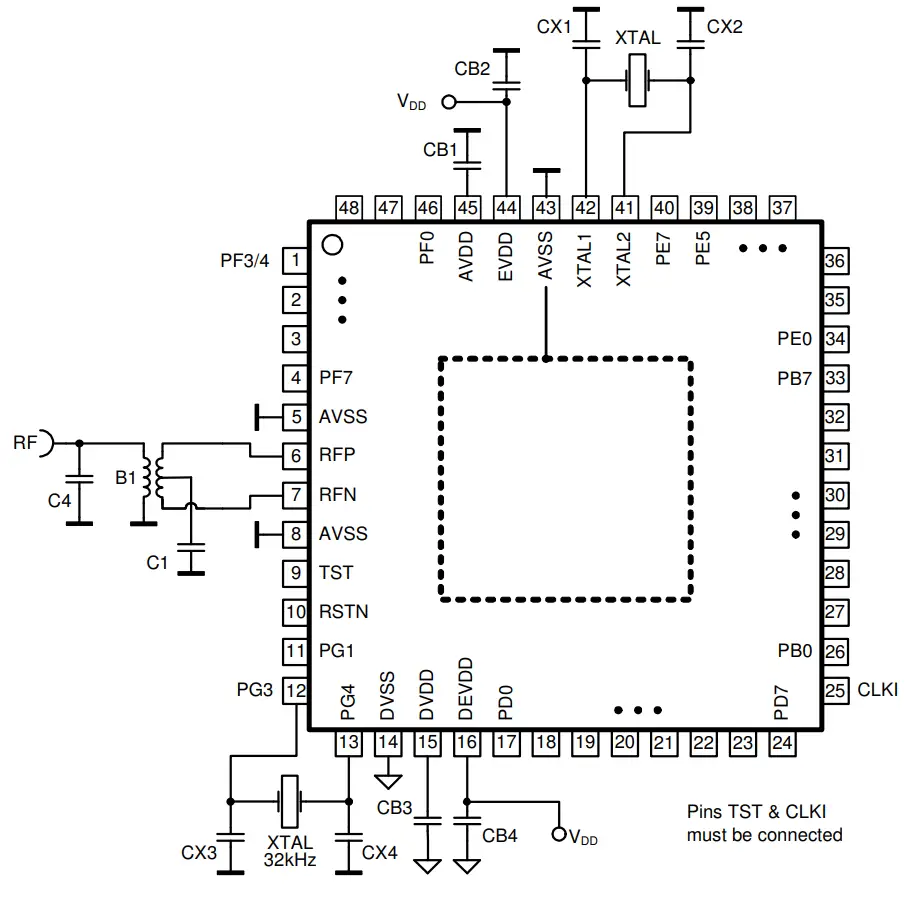

Configuracións de pin

Figura 1-1. Pinout ATmega2564/1284/644RFR2

Nota: A almofada central grande debaixo do paquete QFN/MLF está feita de metal e está conectada internamente a AVSS. Debe estar soldado ou pegado á placa para garantir unha boa estabilidade mecánica. Se a almofada central non se conecta, o paquete pode afrouxarse do taboleiro. Non se recomenda utilizar a paleta exposta como substitución dos pasadores AVSS habituais.

Exención de responsabilidade

Os valores típicos contidos nesta folla de datos baséanse nos resultados de simulación e caracterización doutros microcontroladores AVR e transceptores de radio fabricados cunha tecnoloxía de proceso similar. Os valores mínimos e máximos estarán dispoñibles despois de que se caracterice o dispositivo.

Acabadoview

O ATmega2564/1284/644RFR2 é un microcontrolador CMOS de 8 bits de baixa potencia baseado na arquitectura RISC mellorada AVR combinada cun transceptor de alta velocidade de datos para a banda ISM de 2.4 GHz.

Ao executar instrucións poderosas nun único ciclo de reloxo, o dispositivo alcanza rendementos que se aproximan a 1 MIPS por MHz, o que permite ao deseñador do sistema optimizar o consumo de enerxía fronte á velocidade de procesamento.

O transceptor de radio ofrece altas velocidades de datos desde 250 kb/s ata 2 Mb/s, manexo de cadros, excelente sensibilidade do receptor e alta potencia de saída de transmisión que permiten unha comunicación sen fíos moi robusta.

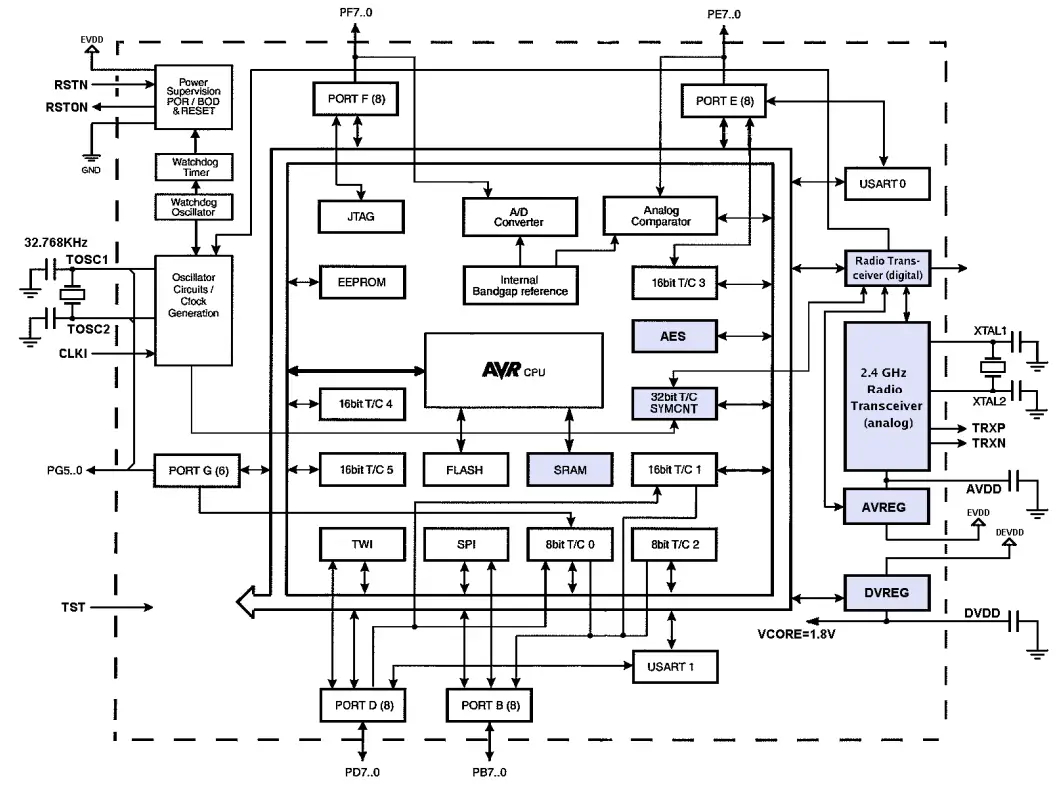

Diagrama de bloques

Figura 3-1 Diagrama de bloques

O núcleo AVR combina un rico conxunto de instrucións con 32 rexistros de traballo de propósito xeral. Os 32 rexistros están directamente conectados á Unidade Lóxica Aritmética (ALU). Pódese acceder a dous rexistros independentes cunha única instrución executada nun ciclo de reloxo. A arquitectura resultante é moi eficiente en código ao mesmo tempo que logra un rendemento ata dez veces máis rápido que os microcontroladores CISC convencionais. O sistema inclúe voltage regulación e unha xestión de enerxía avanzada. Distinguido pola pequena corrente de fuga permite un tempo de funcionamento prolongado desde a batería.

O transceptor de radio é unha solución ZigBee totalmente integrada que utiliza un número mínimo de compoñentes externos. Combina un excelente rendemento de RF con baixo custo, pequeno tamaño e baixo consumo de corrente. O transceptor de radio inclúe un sintetizador, transmisor e receptor de N fraccionario estabilizado con cristal, e procesamento completo de sinal de espectro espallado de secuencia directa (DSSS) con propagación e desprendimento. O dispositivo é totalmente compatible cos estándares IEEE802.15.4-2011/2006/2003 e ZigBee. O ATmega2564/1284/644RFR2 ofrece as seguintes funcións: 256K/128K/64K bytes de flash programable no sistema (ISP) con capacidade de lectura mentres escritura, 8K/4K/2K bytes EEPROM, 32K/16K/8K bytes SRAM, ata 35 liñas de E/S de propósito xeral, 32 rexistros de traballo de propósito xeral, contador en tempo real (RTC), 6 temporizadores/contadores flexibles con modos de comparación e PWM, un temporizador/contador de 32 bits, 2 USART, un byte de 2 cables orientado Interfaz serie, un conversor analóxico a dixital (ADC) de 8 canles e 10 bits cunha entrada diferencial opcional.tage con ganancia programable, temporizador Watchdog programable con oscilador interno, un porto serie SPI, estándar IEEE. 1149.1 conforme JTAG interface de proba, tamén se usa para acceder ao sistema de depuración e programación On-chip e 6 modos de aforro de enerxía seleccionables por software.

O modo inactivo detén a CPU mentres permite que a SRAM, o temporizador/contadores, o porto SPI e o sistema de interrupción sigan funcionando. O modo de apagado garda o contido do rexistro pero conxela o oscilador, desactivando todas as outras funcións do chip ata a seguinte interrupción ou reinicio do hardware. No modo de aforro de enerxía, o temporizador asíncrono continúa a funcionar, o que permite ao usuario manter unha base de temporizador mentres o resto do dispositivo está durmindo. O modo de redución de ruído ADC detén a CPU e todos os módulos de E/S excepto o temporizador asíncrono e o ADC, para minimizar o ruído de conmutación durante as conversións de ADC. No modo de espera, o oscilador RC está funcionando mentres o resto do dispositivo está durmindo. Isto permite un arranque moi rápido combinado cun baixo consumo de enerxía. No modo de espera ampliada, tanto o oscilador RC principal como o temporizador asíncrono continúan funcionando.

A corrente de subministración típica do microcontrolador co reloxo da CPU configurado en 16 MHz e o transceptor de radio para os estados máis importantes móstrase na Figura 3-2 a continuación.

Figura 3-2 Corriente de alimentación do transceptor de radio e do microcontrolador (16 MHz).

A potencia de saída de transmisión está definida como máximo. Se o transceptor de radio está en modo SLEEP, a corrente é disipada só polo microcontrolador AVR.

No modo Deep Sleep, todos os bloques dixitais principais sen requisitos de retención de datos están desconectados da subministración principal proporcionando unha corrente de fuga moi pequena. O temporizador Watchdog, o contador de símbolos MAC e o oscilador de 32.768 kHz pódense configurar para que sigan funcionando.

O dispositivo está fabricado mediante a tecnoloxía de memoria non volátil de alta densidade de Atmel.

O Flash ISP no chip permite que a memoria do programa se reprograma no sistema mediante unha interface serie SPI, mediante un programador de memoria non volátil convencional ou mediante un programa de arranque no chip que se executa no núcleo AVR. O programa de inicio pode usar calquera interface para descargar o programa da aplicación na memoria Flash da aplicación.

O software da sección Flash de arranque seguirá executándose mentres se actualice a sección Flash da aplicación, proporcionando unha verdadeira operación de lectura mentres escribe. Ao combinar unha CPU RISC de 8 bits con Flash autoprogramable no sistema nun chip monolítico, o Atmel ATmega2564/1284/644RFR2 é un poderoso microcontrolador que ofrece unha solución altamente flexible e rendible para moitas aplicacións de control integradas.

O ATmega2564/1284/644RFR2 AVR é compatible cun conxunto completo de ferramentas de desenvolvemento de programas e sistemas, incluíndo: compilador C, ensambladores de macros, depuradores/simuladores de programas, emuladores en circuíto e kits de avaliación.

Descricións de Pin

EVDD

Alimentación analóxica externa voltage.

DEVDD

Alimentación dixital externa voltage.

AVDD

Alimentación analóxica regulada voltage (xerado internamente).

DVDD

Subministro dixital regulado voltage (xerado internamente).

DVSS

Terra dixital.

AVSS

Terra analóxica.

Porto B (PB7…PB0)

O porto B é un porto de E/S bidireccional de 8 bits con resistencias pull-up internas (seleccionadas para cada bit). Os búfers de saída do porto B teñen características de unidade simétricas con capacidade de fonte e sumidoiro elevadas. Como entradas, os pinos do porto B que son baixados externamente xerarán corrente se se activan as resistencias de extracción. Os pinos do porto B están en tres estados cando se activa unha condición de reinicio, aínda que o reloxo non estea a funcionar.

O porto B tamén ofrece funcións de varias características especiais do ATmega2564/1284/644RFR2.

Porto D (PD7…PD0)

O porto D é un porto de E/S bidireccional de 8 bits con resistencias pull-up internas (seleccionadas para cada bit). Os búfers de saída do porto D teñen características de unidade simétricas con capacidade de fonte e sumidoiro elevadas. Como entradas, os pinos do porto D que son baixos externamente xerarán corrente se se activan as resistencias de extracción. Os pinos do porto D están en tres estados cando se activa unha condición de reinicio, aínda que o reloxo non estea a funcionar.

O porto D tamén ofrece funcións de varias características especiais do ATmega2564/1284/644RFR2.

Porto E (PE7,PE5...PE0)

Internamente o porto E é un porto de E/S bidireccional de 8 bits con resistencias pull-up internas (seleccionadas para cada bit). Os búfers de saída do porto E teñen características de unidade simétricas con capacidade de fonte e sumidoiro elevadas. Como entradas, os pinos do porto E que son baixados externamente xerarán corrente se se activan as resistencias de extracción. Os pinos do porto E están en tres estados cando se activa unha condición de reinicio, aínda que o reloxo non estea a funcionar.

Debido ao baixo número de pins do paquete QFN48, o porto E6 non está conectado a un pin. O porto E tamén ofrece funcións de varias características especiais do ATmega2564/1284/644RFR2.

Port F (PF7..PF5,PF4/3,PF2…PF0)

Internamente o porto F é un porto de E/S bidireccional de 8 bits con resistencias pull-up internas (seleccionadas para cada bit). Os búfers de saída do porto F teñen características de unidade simétricas con capacidade de fonte e sumidoiro elevadas. Como entradas, os pinos do porto F que son baixos externamente xerarán corrente se se activan as resistencias de extracción. Os pinos do porto F están en tres estados cando se activa unha condición de reinicio, aínda que o reloxo non estea a funcionar.

Debido ao baixo número de pins do paquete QFN48, os portos F3 e F4 están conectados ao mesmo pin. A configuración de E/S debe realizarse con coidado para evitar unha disipación de enerxía excesiva.

O porto F tamén ofrece funcións de varias características especiais do ATmega2564/1284/644RFR2.

Porto G (PG4,PG3,PG1)

Internamente o porto G é un porto de E/S bidireccional de 6 bits con resistencias pull-up internas (seleccionadas para cada bit). Os búfers de saída do porto G teñen características de unidade simétricas con capacidade de fonte e sumidoiro elevadas. Non obstante, a forza do controlador de PG3 e PG4 redúcese en comparación cos outros pinos de porto. A saída voltagA caída de e (VOH, VOL) é maior mentres que a corrente de fuga é menor. Como entradas, os pinos do porto G que son baixos externamente xerarán corrente se se activan as resistencias de extracción. Os pinos do porto G están en tres estados cando se activa unha condición de reinicio, aínda que o reloxo non estea a funcionar.

Debido ao baixo número de pins do porto do paquete QFN48 G0, G2 e G5 non están conectados a un pin.

O porto G tamén ofrece funcións de varias características especiais do ATmega2564/1284/644RFR2.

AVSS_RFP

AVSS_RFP é un pin de terra dedicado para o porto de E/S de RF bidireccional e diferencial.

AVSS_RFN

AVSS_RFN é un pin de terra dedicado para o porto de E/S de RF bidireccional e diferencial.

RFP

RFP é o terminal positivo para o porto de E/S de RF bidireccional e diferencial.

RFN

RFN é o terminal negativo para o porto de E/S de RF bidireccional e diferencial.

RSTN

Restablecer entrada. Un nivel baixo neste pin durante máis tempo que a lonxitude de pulso mínima xerará un reinicio, aínda que o reloxo non estea funcionando. Non se garante que os pulsos máis curtos xeren un reinicio.

XTAL 1

Entrada ao oscilador de cristal inversor de 16 MHz amplificador. En xeral, un cristal entre XTAL1 e XTAL2 proporciona o reloxo de referencia de 16 MHz do transceptor de radio.

XTAL 2

Saída do oscilador de cristal inversor de 16 MHz ampmáis vivo.

TST

O modo de programación e proba activa o pin. Se non se usa o pin TST, tírao abaixo.

CLKI

Entrada ao sistema de reloxo. Se se selecciona, proporciona o reloxo de funcionamento do microcontrolador.

Pins sen usar

Os pinos flotantes poden provocar a disipación de enerxía na entrada dixital stage. Deben estar conectados a unha fonte adecuada. Nos modos de funcionamento normal pódense activar as resistencias de extracción internas (en Restablecer todos os GPIO están configurados como entrada e as resistencias de extracción aínda non están habilitadas).

Os pines de E/S bidireccionais non deben conectarse directamente á terra nin á fonte de alimentación.

Os pines de entrada dixital TST e CLKI deben estar conectados. Se non se usa o pin TST pódese conectar a AVSS mentres que CLKI debe conectarse a DVSS.

Os pinos de saída son impulsados polo dispositivo e non flotan. Os pinos da fonte de alimentación respectivos pinos da fonte de terra están conectados entre si internamente.

XTAL1 e XTAL2 nunca serán obrigados a subministrar voltage ao mesmo tempo.

Compatibilidade e limitacións das características do paquete QFN-48

AREF

A referencia voltagA saída do conversor A/D non está conectada a un pin no ATmega2564/1284/644RFR2.

Porto E6

O porto E6 non está conectado a un pin no ATmega2564/1284/644RFR2. As funcións de pin alternativo como entrada de reloxo ao temporizador 3 e a interrupción externa 6 non están dispoñibles.

Portos F3 e F4

O porto F3 e F4 están conectados ao mesmo pin no ATmega2564/1284/644RFR2. A configuración da saída debe facerse con coidado para evitar un consumo excesivo de corrente.

A función de pin alternativo do porto F4 é usada polo JTAG interface. Se o JTAG utilízase a interface, o porto F3 debe estar configurado como entrada e a saída da función de pin alternativo DIG4 (indicador RX/TX) debe estar desactivada. En caso contrario, JTAG a interface non funcionará. O fusible SPIEN debe ser programado para poder borrar un programa que conduza accidentalmente o porto F3.

Só hai 7 canles de entrada de extremo único para o ADC dispoñibles.

Porto G0

O porto G0 non está conectado a un pin no ATmega2564/1284/644RFR2. A función de pin alternativo DIG3 (indicador RX/TX invertido) non está dispoñible. Se o JTAG a interface non se usa a saída da función de pin alternativo DIG4 do porto F3 aínda se pode usar como indicador RX/TX.

Porto G2

O porto G2 non está conectado a un pin no ATmega2564/1284/644RFR2. A función de pin alternativo AMR (entrada de lectura automática de contadores asíncrona ao temporizador 2) non está dispoñible.

Porto G5

O porto G5 non está conectado a un pin no ATmega2564/1284/644RFR2. A función de pin alternativo OC0B (canle de comparación de saída do temporizador de 8 bits 0) non está dispoñible.

RSTON

A saída de reinicio RSTON que sinala o estado de reinicio interno non está conectada a un pin no ATmega2564/1284/644RFR2.

Resumo da configuración

Segundo os requisitos da aplicación, un tamaño de memoria variable permite optimizar o consumo de corrente e a corrente de fuga.

Táboa 3-1 Configuración da memoria

| Dispositivo | Flash | EEPROM | SRAM |

| ATmega2564RFR2 | 256KB | 8KB | 32KB |

| ATmega1284RFR2 | 128KB | 4KB | 16KB |

| ATmega644RFR2 | 64KB | 2KB | 8KB |

O paquete e a configuración do pin asociado son os mesmos para todos os dispositivos que proporcionan unha funcionalidade completa á aplicación.

Táboa 3-2 Configuración do sistema

| Dispositivo | Paquete | GPIO | Serie IF | Canle ADC |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

Os dispositivos están optimizados para aplicacións baseadas na especificación ZigBee e IEEE 802.15.4. Ter unha pila de aplicacións, unha capa de rede, unha interface de sensor e un excelente control de enerxía combinados nun só chip deberían ser posibles durante moitos anos.

Táboa 3-3 Aplicación Profile

| Dispositivo | Aplicación |

| ATmega2564RFR2 | Coordinador de redes grandes/enrutador para IEEE 802.15.4/ZigBee Pro |

| ATmega1284RFR2 | Coordinador de rede/enrutador para IEEE 802.15.4 |

| ATmega644RFR2 | Dispositivo de nodo final/procesador de rede |

Circuítos de aplicación

Esquema básico da aplicación

Na Figura 2564-1284 a continuación móstrase un esquema de aplicación básico do ATmega644/2/4RFR1 cun conector de RF dun único extremo e a lista de materiais asociada na Táboa 4-1 da páxina 10. A entrada de RF dun único extremo de 50Ω transfórmase. á impedancia diferencial do porto de RF de 100Ω usando Balun B1. Os capacitores C1 e C2 proporcionan o acoplamento de CA da entrada de RF ao porto de RF, o capacitor C4 mellora a correspondencia.

Figura 4-1. Esquema básico da aplicación (paquete de 48 pines)

Os capacitores de derivación da fonte de alimentación (CB2, CB4) están conectados ao pin da fonte analóxica externa (EVDD, pin 44) e ao pin da fonte dixital externa (DEVDD, pin 16). O capacitor C1 proporciona o acoplamento AC necesario de RFN/RFP.

Os pinos flotantes poden provocar unha disipación excesiva de enerxía (por exemplo, durante o acendido). Deben estar conectados a unha fonte adecuada. GPIO non debe conectarse directamente á terra nin á fonte de alimentación.

Os pines de entrada dixital TST e CLKI deben estar conectados. Se nunca se usará o pin TST, pódese conectar a AVSS mentres que un pin CLKI non utilizado podería conectarse a DVSS (consulte o capítulo "Pinas non utilizadas").

Os capacitores CB1 e CB3 son capacitores de derivación para o vol analóxico e dixital integradostage reguladores para garantir un funcionamento estable e mellorar a inmunidade ao ruído.

Os capacitores deben colocarse o máis preto posible dos pinos e deben ter unha conexión a terra de baixa resistencia e baixa inductancia para conseguir o mellor rendemento.

O cristal (XTAL), os dous capacitores de carga (CX1, CX2) e os circuítos internos conectados aos pinos XTAL1 e XTAL2 forman o oscilador de cristal de 16 MHz para o transceptor de 2.4 GHz. Para conseguir a mellor precisión e estabilidade da frecuencia de referencia, hai que evitar grandes capacidades parasitarias. As liñas de cristal deben ser encamiñadas o máis curtas posible e non nas proximidades dos sinais de E/S dixitais. Isto é especialmente necesario para os modos de alta velocidade de datos.

O cristal de 32.768 kHz conectado ao oscilador de cristal interno de baixa potencia (sub 1 µA) proporciona unha referencia de tempo estable para todos os modos de baixa potencia, incluíndo o contador de símbolos IEEE 32 de 802.15.4 bits ("Contador de símbolos MAC") e a aplicación de reloxo en tempo real mediante a aplicación asíncrona. temporizador T/C2 (“Timer/Counter2 with PWM and Asynchronous Operation”).

A capacidade de derivación total, incluíndo CX3, CX4, non debe exceder os 15 pF en ambos os pinos.

A baixa corrente de subministración do oscilador require un deseño coidadoso da PCB e debe evitarse calquera vía de fuga.

A diafonía e a radiación derivadas da conmutación de sinais dixitais aos pinos de cristal ou ós pinos de RF poden degradar o rendemento do sistema. Recoméndase a programación de configuracións de forza mínima da unidade para o sinal de saída dixital (consulte "DPDS0 - Rexistro de forza do controlador de porto 0").

Táboa 4-1. Lista de materiais (BoM)

| Designador | Descrición | Valor | Fabricante | Número de peza | Comenta |

| B1 | Balun SMD

Balun/filtro SMD |

2.4 GHz | Tecnoloxía Wuerth Johanson | 748421245

2450FB15L0001 |

Filtro incluído |

| CB1 CB3 | LDO VREG

condensador de derivación |

1 mF (mínimo 100 nF) | AVX

Murata |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10 % 16 V |

| CB2 CB4 | Condensador de derivación da fonte de alimentación | 1 mF (mínimo 100 nF) | |||

| CX1, CX2 | Condensador de carga de cristal de 16 MHz | 12 pF | AVX

Murata |

06035A120JA GRP1886C1H120JA01 | COG (0603) 5 % 50 V |

| CX3, CX4 | Condensador de carga de cristal de 32.768 kHz | 12 … 25 pF | |||

| C1, C2 | Condensador de acoplamento RF | 22 pF | Epcos Epcos AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 ou 0603) |

| C4 (opcional) | Correspondencia de RF | 0.47 pF | Johnstech | ||

| XTAL | Cristal | CX-4025 16 MHz

SX-4025 16 MHz |

ACAL Taitjen Siward | XWBBPL-F-1 A207-011 | |

| XTAL 32 kHz | Cristal | Rs = 100 kOhm |

Historial de revisións

Teña en conta que os números de páxinas de referencia nesta sección refírense a este documento. A revisión de referencia nesta sección refírense á revisión do documento.

Rev. 42073BS-MCU Wireless-09/14

- Contido sen cambios: recreouse para a versión combinada coa folla de datos.

Rev. 8393AS-MCU Wireless-02/13

- Lanzamento inicial.

© 2014 Atmel Corporation. Todos os dereitos reservados. / Rev.: 42073BS-MCU Wireless-09/14 Atmel®, o logotipo de Atmel e as súas combinacións, Enabling Unlimited Possibilities® e outros son marcas rexistradas ou marcas comerciais de Atmel Corporation ou das súas subsidiarias. Outros termos e nomes de produtos poden ser marcas comerciais doutros.

Exención de responsabilidade: a información deste documento ofrécese en relación cos produtos Atmel. Este documento ou en relación coa venda de produtos Atmel non concede ningunha licenza, expresa ou implícita, por exclusión ou doutra forma, a ningún dereito de propiedade intelectual. EXCEPTO O ESTABLECIDO NOS TERMOS E CONDICIÓNS DE VENDA DE ATMEL UBICADOS NO ATMEL WEBSITIO, ATMEL NON ASUME NINGUNHA RESPONSABILIDADE E RENUNCIA A NINGÚN GARANTÍA EXPRESA, IMPLÍCITA OU ESTATUTORIA RELATIVA AOS SEUS PRODUTOS INCLUÍENDO, PERO NON LIMITADO A, A GARANTÍA IMPLÍCITA DE COMERCIABILIDADE, ADECUACIÓN PARA UN FIN PARTICULAR, INFRACCIÓN. EN NINGÚN CASO ATMEL SERÁ RESPONSABLE DE NINGÚN DANOS DIRECTOS, INDIRECTOS, CONSECUENTES, PUNITIVOS, ESPECIAIS OU INCIDENTAIS (INCLUÍDOS, SEN LIMITACIÓNS, DANOS POR PERDAS E BENEFICIOS, INTERRUPCIÓN DA NEGOCIO OU PERDA DE INFORMACIÓN) DERIVADOS DO USO PARA O USO. ESTE DOCUMENTO, AÍNDA QUE ATMEL FOI AVISO DA POSIBILIDADE DE ESTOS DANOS. Atmel non fai ningunha representación ou garantía con respecto á exactitude ou integridade do contido deste documento e resérvase o dereito de facer cambios nas especificacións e nas descricións dos produtos en calquera momento sen previo aviso. Atmel non se compromete a actualizar a información aquí contida. A non ser que se indique expresamente o contrario, os produtos Atmel non son axeitados para aplicacións automotrices e non se deben utilizar en aplicacións de automoción. Os produtos Atmel non están destinados, autorizados ou garantidos para o seu uso como compoñentes en aplicacións destinadas a soportar ou manter a vida útil.

Mouser Electronics

Distribuidor autorizado

Fai clic para View Información sobre prezos, inventario, entrega e ciclo de vida:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

Atención ao cliente

Corporación Atmel

1600 Tecnoloxía Drive

San José, CA 95110

EUA

Teléfono: (+1)408-441-0311

Fax: (+1)408-487-2600

www.atmel.com

Documentos/Recursos

|

Microcontrolador Atmel ATmega2564 AVR de 8 bits [pdfManual do propietario ATmega2564RFR2, ATmega1284RFR2, ATmega644RFR2, ATmega2564 Microcontrolador AVR de 8 bits, ATmega2564, Microcontrolador AVR de 8 bits, Microcontrolador AVR, Microcontrolador |