Atmel ATmega2564 8bit AVR Mikroregilo

Karakterizaĵoj

- Reta subteno per aparataro helpita Multoblaj PAN-Adresfiltrigado

- Altnivela Aparataro helpis Reduktan Elektron-Konsumon

- Alta Efikeco, Malalta Potenco AVR® 8-Bita Mikroregilo

- Altnivela RISC-Arkitekturo

- 135 Potencaj Instruoj - Plej Unuopa Horloĝa Ciklo-Ekzekuto

- 32×8 Ĝenerala Celo Laboraj Registroj / Sur-blato 2-cikla Multipliktilo

- Ĝis 16 MIPS-Trafluo ĉe 16 MHz kaj 1.8V - Plene Statika Operacio

- Ne-volatila Programo kaj Datumemoroj

- 256K/128K/64K Bajtoj de En-Sistema Mem-Programebla Flash

- Eltenivo: 10'000 Skribu/Forigi ciklojn @ 125 °C (25'000 ciklojn @ 85 °C)

- 8K/4K/2K Bajtoj EEPROM

- Eltenivo: 20'000 Skribu/Forigi ciklojn @ 125 °C (100'000 ciklojn @ 25 °C)

- 32K/16K/8K Bytes Interna SRAM

- JTAG (IEEE std. 1149.1 konforma) Interfaco

- Lim-skanaj Kapabloj Laŭ la JTAG Normo

- Vasta Sur-blato Sencimiga Subteno

- Programado de Flash EEPROM, Fuzeoj kaj Lock Bits tra la JTAG interfaco

- Ekstercentraj Ecoj

- Multoblaj Timer/Counter & PWM-kanaloj

- Realtempa Nombrilo kun Aparta Oscilatoro

- 10-bita, 330 ks/s A/D-Konvertilo; Analoga Komparilo; Sur-blato Temperatura Sensilo

- Majstro/Sklavo SPI Seria Interfaco

- Du Programeblaj Seriaj USART

- Byte Oriented 2-drata Seria Interfaco

- Altnivela Interrompa Pritraktilo kaj Potenca Ŝparreĝimoj

- Gardhundo-Temigilo kun Aparta Sur-blata Oscilatoro

- Ekfunkciiga Restarigi kaj Malalta Nuna Bruna-Eksterdetektilo

- Plene integra Malalta Potenca Dissendilo por 2.4 GHz ISM-Bando

- Alta Potenco AmpLiifiersubteno per TX-spektra flankloba subpremado

- Subtenataj Datumoj: 250 kb/s kaj 500 kb/s, 1 Mb/s, 2 Mb/s

- -100 dBm RX-Sentemo; TX Eliga Potenco ĝis 3.5 dBm

- Aparataro Helpita MAC (Aŭtomata agnosko, Aŭtomata reprovo)

- 32 Bitoj IEEE 802.15.4 Simbolo Nombrilo

- SFD-Detekto, Disvastigo; De-Disvastigo; Enkadrigo ; CRC-16 Komputado

- Antena Diverseco kaj TX/RX-kontrolo / TX/RX 128 Byte Frame Buffer

- PLL-sintezilo kun 5 MHz kaj 500 kHz kanalinterspaco por 2.4 GHz ISM-grupo

- Sekureco de aparataro (AES, Vera Hazarda Generatoro)

- Integritaj Kristalaj Oscilatoroj (32.768 kHz & 16 MHz, ekstera kristalo bezonata)

- I/O kaj Pako

- 33 Programeblaj I/O-Linioj

- 48-kuseneto QFN (RoHS/Tute Verda)

- Temperaturintervalo: -40 °C ĝis 125 °C Industria

- Ultra Malalta Potenca konsumo (1.8 ĝis 3.6 V) por AVR & Rx/Tx: 10.1 mA/18.6 mA

- CPU Aktiva Reĝimo (16MHz): 4.1 mA

- 2.4GHz Dissendilo: RX_ON 6.0 mA / TX 14.5 mA (maksimuma TX elira potenco)

- Profunda Dorma Reĝimo: <700nA @ 25 °C

- Rapida Grado: 0 – 16 MHz @ 1.8 – 3.6V gamo kun integra voltage reguligistoj

Aplikoj

- ZigBee®/ IEEE 802.15.4-2011/2006/2003™ - Plena kaj Reduktita Funkcia Aparato

- Ĝenerala Celo 2.4GHz ISM Band Transceiver kun Mikroregilo

- RF4CE, SP100, WirelessHART™, ISM-Aplikoj kaj IPv6/6LoWPAN

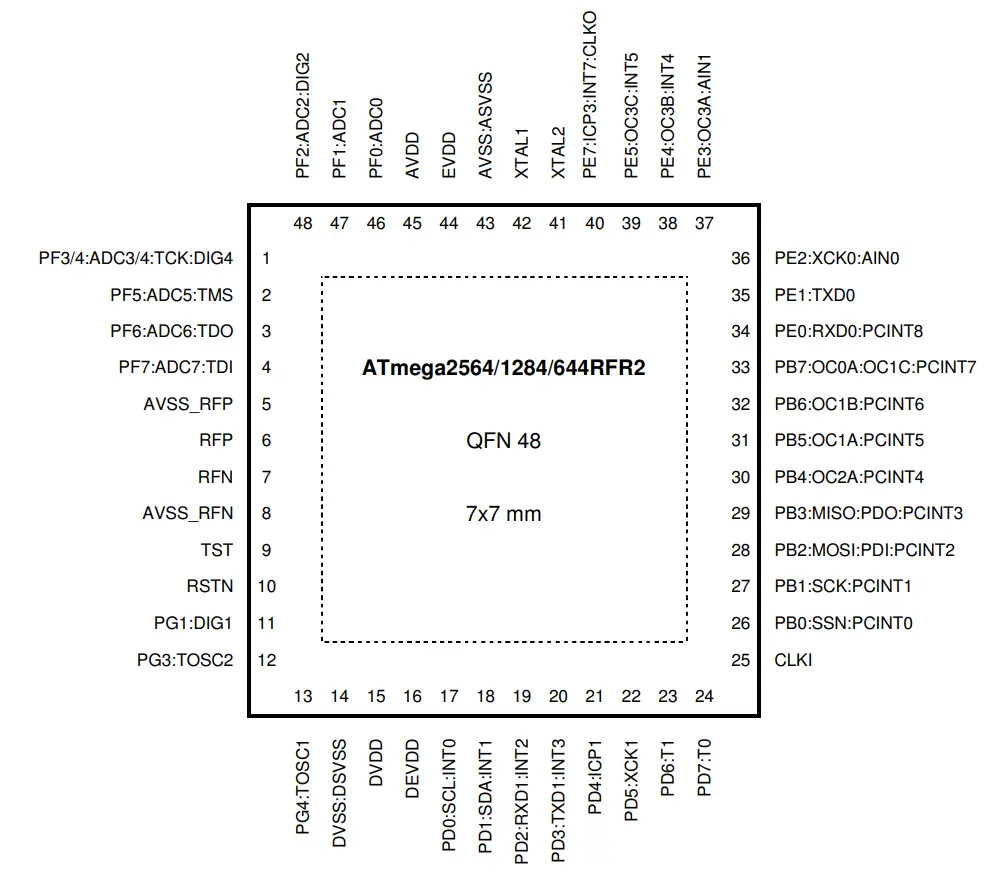

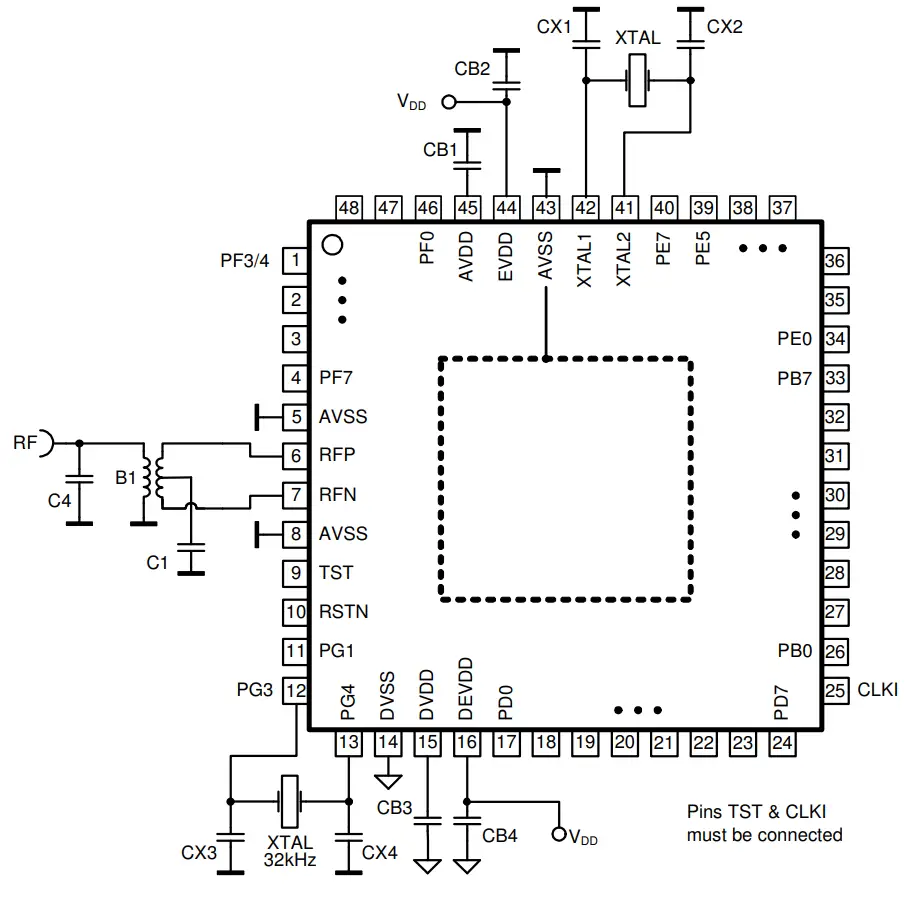

Pinglo-Agordoj

Figuro 1-1. Pinout ATmega2564/1284/644RFR2

Notu: La granda centra kuseneto sub la QFN/MLF-pakaĵo estas farita el metalo kaj interne konektita al AVSS. Ĝi devus esti lutita aŭ gluita al la tabulo por certigi bonan mekanikan stabilecon. Se la centra kuseneto estas lasita nekonektita, la pakaĵo povus malfiksi de la tabulo. Ne rekomendas uzi la elmontritan padelon kiel anstataŭaĵon de la regulaj AVSS-pingloj.

Malgarantio

Tipaj valoroj enhavitaj en ĉi tiu datenfolio estas bazitaj sur simulado kaj karakterizadrezultoj de aliaj AVR-mikroregiloj kaj radiosendiloj produktitaj en simila procezteknologio. Minimumaj kaj Maksimumaj valoroj estos disponeblaj post kiam la aparato estas karakterizita.

Finiteview

La ATmega2564/1284/644RFR2 estas malalt-potenca CMOS 8-bita mikroregilo bazita sur la AVR-plifortigita RISC-arkitekturo kombinita kun alta datenfrekvenca transceptoro por la 2.4 GHz ISM-grupo.

Efektivigante potencajn instrukciojn en ununura horloĝa ciklo, la aparato atingas trairojn proksimiĝantajn al 1 MIPS per MHz permesante al la sistemdizajnisto optimumigi elektrokonsumon kontraŭ pretigrapideco.

La radioaparato disponigas altajn datumrapidecojn de 250 kb/s ĝis 2 Mb/s, kadro-traktadon, elstaran ricevilo-sentemon kaj altan elsenda eligpotencon ebligante tre fortikan sendratan komunikadon.

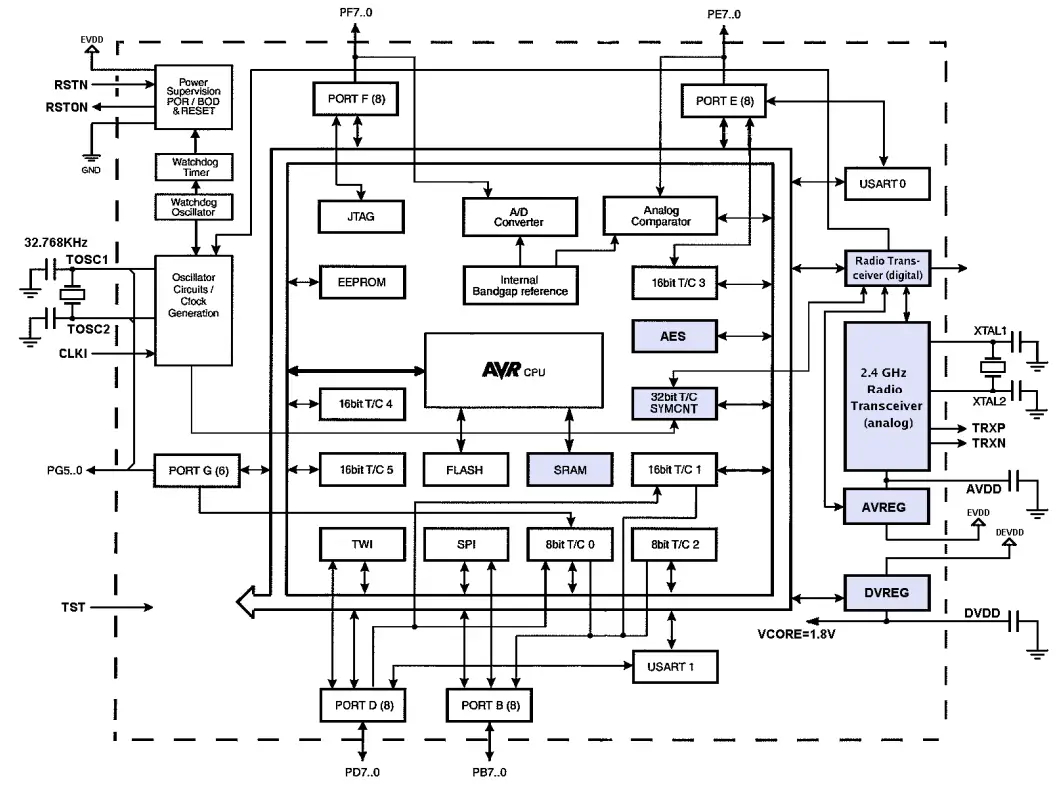

Bloka Diagramo

Figuro 3-1 Blokdiagramo

La AVR-kerno kombinas riĉan instrukciaĵon kun 32 ĝeneraluzeblaj laborregistroj. Ĉiuj 32 registroj estas rekte ligitaj al la Aritmetika Logika Unuo (ALU). Du sendependaj registroj povas esti aliritaj kun unu ununura instrukcio efektivigita en unu horloĝciklo. La rezulta arkitekturo estas tre koda efika dum atingado de trairoj ĝis dekoble pli rapide ol konvenciaj CISC-mikroregiloj. La sistemo inkluzivas internan voltage reguligo kaj altnivela administrado de potenco. Distingite per la malgranda elflua kurento ĝi permesas plilongigitan operaciotempon de baterio.

La radioaparato estas plene integra ZigBee-solvo uzanta minimuman nombron da eksteraj komponantoj. Ĝi kombinas bonegan RF-agadon kun malalta kosto, malgranda grandeco kaj malalta nuna konsumo. La radiotransceptoro inkluzivas kristalan stabiligitan frakcie-N-sintezilon, dissendilon kaj ricevilon, kaj plenan Direct Sequence Spread Spectrum Signal (DSSS) prilaboradon kun disvastigo kaj sendisvastigo. La aparato estas plene kongrua kun IEEE802.15.4-2011/2006/2003 kaj ZigBee-normoj. La ATmega2564/1284/644RFR2 provizas la jenajn funkciojn: 256K/128K/64K Bajtoj de En-Sistema Programebla (ISP) Ekbrilo kun legado-dum-skriba kapabloj, 8K/4K/2K Bajtoj EEPROM, 32K/16K/8K Bajtoj SRAM, ĝis 35 ĝeneraluzeblaj I/O-linioj, 32 ĝeneraluzeblaj laborregistroj, Real Time Counter (RTC), 6 flekseblaj Timer/Counters kun komparreĝimoj kaj PWM, 32-bit Timer/Counter, 2 USART, bajto orientita 2-drato Seria Interfaco, 8 kanalo, 10 bitoj analoga al cifereca transformilo (ADC) kun laŭvola diferenciala enigaĵo stage kun programebla gajno, programebla Watchdog Timer kun Interna Oscilatoro, SPI seria haveno, IEEE std. 1149.1 konforma JTAG testa interfaco, ankaŭ uzata por aliri la On-blata Sencimiga sistemo kaj programado kaj 6 programaro elekteblaj energiŝparreĝimoj.

La Neaktiva reĝimo maldaŭrigas la CPU permesante al la SRAM, Timer/Counters, SPI-haveno kaj interrompa sistemo daŭre funkcii. La Power-down-reĝimo ŝparas la registroenhavon sed frostigas la Oscilatoron, malfunkciigante ĉiujn aliajn pecetfunkciojn ĝis la venonta interrompo aŭ aparataro rekomencigita. En Power-ŝpara reĝimo, la nesinkrona tempigilo daŭre funkcias, permesante al la uzanto konservi tempigilon dum la resto de la aparato dormas. La ADC Noise Reduction-reĝimo maldaŭrigas la CPU kaj ĉiujn I/O-modulojn krom nesinkrona tempigilo kaj ADC, por minimumigi ŝanĝan bruon dum ADC-konvertoj. En Standby-reĝimo, la RC-oscilatoro funkcias dum la resto de la aparato dormas. Ĉi tio permesas tre rapidan ekfunkciigon kombinitan kun malalta energikonsumo. En Etendita Standby-reĝimo, kaj la ĉefa RC-oscilatoro kaj la nesinkrona tempigilo daŭre funkcias.

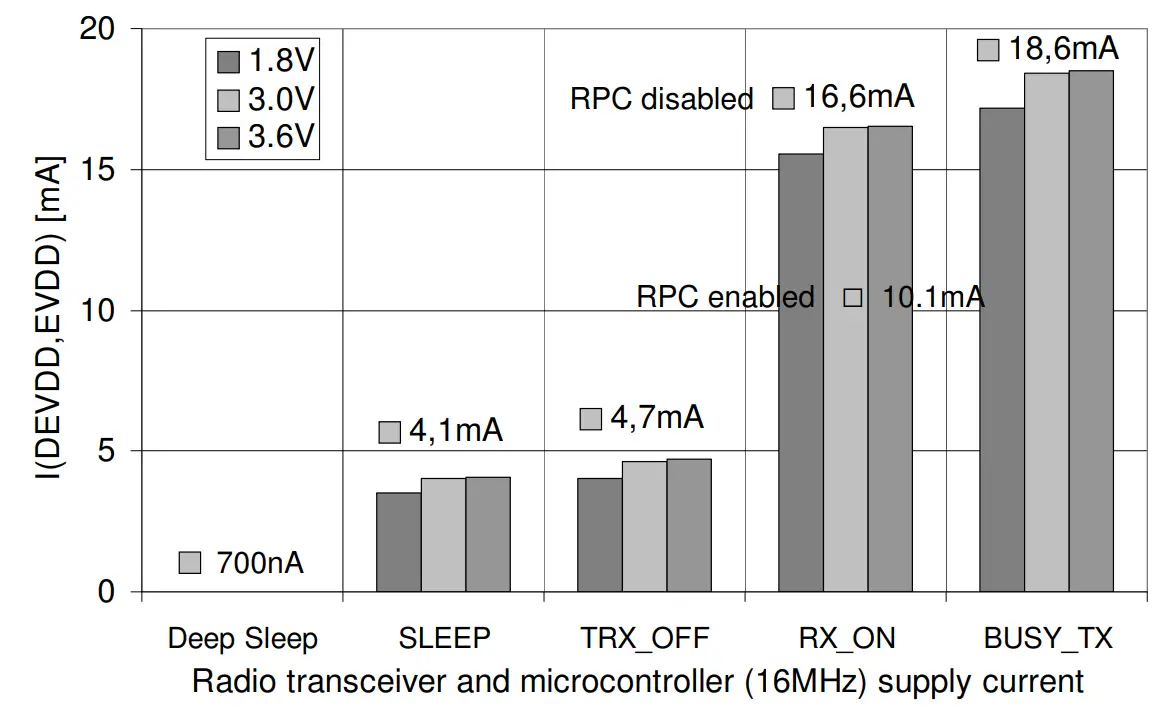

Tipa provizofluo de la mikroregilo kun CPU-horloĝo fiksita al 16MHz kaj la radiotransceptoro por la plej gravaj ŝtatoj estas montrita en la Figuro 3-2 malsupre.

Figuro 3-2 Radiodissendilo kaj mikroregilo (16MHz) provizofluo

La elsenda eliga potenco estas agordita al maksimumo. Se la radiodissendilo estas en SLEEP-reĝimo la fluo estas disipita per la AVR-mikroregilo nur.

En Deep Sleep-reĝimo ĉiuj ĉefaj ciferecaj blokoj kun neniuj datumtenadpostuloj estas malkonektitaj de ĉefa provizo provizante tre malgrandan elfluan fluon. Gardhundo-tempigilo, MAC-simbolo-nombrilo kaj 32.768kHz-oscilatoro povas esti agorditaj por daŭre funkcii.

La aparato estas fabrikita per la alt-denseca nevolatila memorteknologio de Atmel.

La Sur-blata ISP-Fulmo permesas al la programmemoro esti reprogramita en-sistemo tra SPI-seria interfaco, fare de konvencia nevolatila memorprogramisto, aŭ per sur-blata lanĉa programo funkcianta sur la AVR-kerno. La lanĉa programo povas uzi ajnan interfacon por elŝuti la aplikaĵon en la aplikaĵo Flash-memoro.

Programaro en la ekŝarga Flash-sekcio daŭros funkcii dum la aplikaĵa Flash-sekcio estas ĝisdatigita, provizante veran operacion Legado-Dum-Skribo. Kombinante 8-bitan RISC-CPU kun En-Sistema Mem-Programebla Flash sur monolita blato, la Atmel ATmega2564/1284/644RFR2 estas potenca mikroregilo kiu disponigas tre flekseblan kaj kostefika solvon al multaj enigitaj kontrol-aplikoj.

La ATmega2564/1284/644RFR2 AVR estas subtenata kun plena aro de programaj kaj sistemaj evoluiloj inkluzive de: C-kompilo, makro-asemblontoj, program-sencimigilo/simuliloj, encirkvitaj emuliloj kaj taksadkompletoj.

Pinaj Priskriboj

EVDD

Ekstera analoga provizo voltage.

DEVDD

Ekstera cifereca provizo voltage.

AVDD

Reguligita analoga provizo voltage (interne generita).

DVDD

Reguligita cifereca provizo voltage (interne generita).

DVSS

Cifereca grundo.

AVSS

Analoga grundo.

Haveno B (PB7...PB0)

Haveno B estas 8-bita dudirekta I/O-haveno kun internaj tirrezistoj (elektitaj por ĉiu bito). La Port B-produktaĵbufroj havas simetriajn veturadkarakterizaĵojn kun kaj alta lavujo kaj fontkapableco. Kiel enigaĵoj, Port B-stiftoj kiuj estas ekstere tiritaj malalte fontos fluon se la tirrezistoj estas aktivigitaj. La Port B-stiftoj estas tri-deklaritaj kiam rekomencigita kondiĉo iĝas aktiva, eĉ se la horloĝo ne funkcias.

Port B ankaŭ disponigas funkciojn de diversaj specialaj trajtoj de la ATmega2564/1284/644RFR2.

Haveno D (PD7...PD0)

Haveno D estas 8-bita dudirekta I/O-haveno kun internaj tirrezistoj (elektitaj por ĉiu bito). La Port D-produktaĵbufroj havas simetriajn veturadkarakterizaĵojn kun kaj alta lavujo kaj fontkapableco. Kiel enigaĵoj, Port D-stiftoj kiuj estas ekstere tiritaj malalte fontos fluon se la tirrezistoj estas aktivigitaj. La Port D-stiftoj estas tri-deklaritaj kiam rekomencigita kondiĉo iĝas aktiva, eĉ se la horloĝo ne funkcias.

Port D ankaŭ disponigas funkciojn de diversaj specialaj ecoj de la ATmega2564/1284/644RFR2.

Haveno E (PE7,PE5...PE0)

Interna Haveno E estas 8-bita dudirekta I/O-haveno kun internaj tirrezistoj (elektitaj por ĉiu bito). La Port E-produktaĵbufroj havas simetriajn veturadkarakterizaĵojn kun kaj alta lavujo kaj fontkapableco. Kiel enigaĵoj, Port E-stiftoj kiuj estas ekstere tiritaj malalte fontos fluon se la tirrezistoj estas aktivigitaj. La Port E-stiftoj estas tri-deklaritaj kiam rekomencigita kondiĉo iĝas aktiva, eĉ se la horloĝo ne funkcias.

Pro la malalta pingla nombro de la QFN48-pakaĵhaveno E6 ne estas konektita al pinglo. Port E ankaŭ disponigas funkciojn de diversaj specialaj trajtoj de la ATmega2564/1284/644RFR2.

Port F (PF7..PF5,PF4/3,PF2…PF0)

Interna Haveno F estas 8-bita dudirekta I/O-haveno kun internaj tirrezistoj (elektitaj por ĉiu bito). La Port F-produktaĵbufroj havas simetriajn veturadkarakterizaĵojn kun kaj alta lavujo kaj fontkapableco. Kiel enigaĵoj, Port F-stiftoj kiuj estas ekstere tiritaj malalte fontos fluon se la tirrezistoj estas aktivigitaj. La Port F-stiftoj estas tri-deklaritaj kiam rekomencigita kondiĉo iĝas aktiva, eĉ se la horloĝo ne funkcias.

Pro la malalta pingla nombro de la QFN48-pakaĵhaveno F3 kaj F4 estas konektitaj al la sama pinglo. La I/O-agordo devas esti farita zorge por eviti troan povan disipadon.

Port F ankaŭ disponigas funkciojn de diversaj specialaj ecoj de la ATmega2564/1284/644RFR2.

Haveno G (PG4,PG3,PG1)

Interna Haveno G estas 6-bita dudirekta I/O-haveno kun internaj tirrezistoj (elektitaj por ĉiu bito). La Port G-produktaĵbufroj havas simetriajn veturadkarakterizaĵojn kun kaj alta lavujo kaj fontkapableco. Tamen la ŝoforforto de PG3 kaj PG4 estas reduktita kompare kun la aliaj havenstiftoj. La eligo voltage guto (VOH, VOL) estas pli alta dum la elflua fluo estas pli malgranda. Kiel enigaĵoj, Port G-stiftoj kiuj estas ekstere tiritaj malalte fontos fluon se la tirrezistoj estas aktivigitaj. La Port G-stiftoj estas tri-deklaritaj kiam rekomencigita kondiĉo iĝas aktiva, eĉ se la horloĝo ne funkcias.

Pro la malalta pingla nombro de la QFN48-pakaĵhaveno G0, G2 kaj G5 ne estas konektitaj al pinglo.

Port G ankaŭ disponigas funkciojn de diversaj specialaj ecoj de la ATmega2564/1284/644RFR2.

AVSS_RFP

AVSS_RFP estas diligenta terstifto por la dudirekta, diferenciga RF I/O-haveno.

AVSS_RFN

AVSS_RFN estas diligenta terstifto por la dudirekta, diferenciga RF I/O-haveno.

RFP

RFP estas la pozitiva terminalo por la dudirekta, diferenciga RF I/O-haveno.

RFN

RFN estas la negativa terminalo por la dudirekta, diferenciga RF I/O-haveno.

RSTN

Restarigi enigon. Malalta nivelo sur ĉi tiu pinglo por pli longa ol la minimuma pulslongo generos rekomencon, eĉ se la horloĝo ne funkcias. Pli mallongaj pulsoj ne garantias generi rekomencon.

XTAL1

Enigo al la inversa 16MHz kristala oscilatoro ampligilo. Ĝenerale kristalo inter XTAL1 kaj XTAL2 disponigas la 16MHz-referenchorloĝon de la radiosendilo.

XTAL2

Eligo de la inversa 16MHz-kristala oscilatoro amppli viva.

TST

Programado kaj testa reĝimo ebligas pinglon. Se pinglo TST ne estas uzata, tiri ĝin al malalta.

CLKI

Enigo al la horloĝa sistemo. Se elektita, ĝi disponigas la funkcian horloĝon de la mikroregilo.

Neuzataj Stiftoj

Flosantaj stiftoj povas kaŭzi potencodissipadon en la cifereca enigaĵo stage. Ili devus esti konektitaj al taŭga fonto. En normalaj operaciaj reĝimoj la internaj tirrezistoj povas esti ebligitaj (en Restarigi ĉiuj GPIO estas agorditaj kiel enigaĵo kaj la tirrezistiloj ankoraŭ ne estas ebligitaj).

Dudirektaj I/O-stiftoj ne devas esti konektitaj al grundo aŭ elektroprovizo rekte.

La ciferecaj enigstiftoj TST kaj CLKI devas esti konektitaj. Se neuzata pinglo TST povas esti konektita al AVSS dum CLKI devus esti konektita al DVSS.

Eliraj pingloj estas pelataj de la aparato kaj ne flosas. Elektraj stiftoj respektivaj teraj stiftoj estas kunligitaj interne.

XTAL1 kaj XTAL2 neniam devas esti devigitaj provizi voltage samtempe.

Kongrueco kaj Karakterizaj Limigoj de QFN-48-Pako

AREF

La referenca voltagLa eligo de la A/D-konvertilo ne estas konektita al pinglo en la ATmega2564/1284/644RFR2.

Haveno E6

La haveno E6 ne estas konektita al pinglo en la ATmega2564/1284/644RFR2. La alterna stifto funkcias kiel horloĝenigo al tempigilo 3 kaj ekstera interrompo 6 ne haveblas.

Haveno F3 kaj F4

La haveno F3 kaj F4 estas konektitaj al la sama pinglo en la ATmega2564/1284/644RFR2. La eliga agordo devas esti farita zorge por eviti troan kurentkonsumon.

La alterna stifta funkcio de haveno F4 estas uzita fare de la JTAG interfaco. Se la JTAG interfaco estas uzata, la haveno F3 devas esti agordita kiel enigo kaj la alterna pingla funkcio eligo DIG4 (RX/TX-indikilo) devas esti malŝaltita. Alie la JTAG interfaco ne funkcios. La SPIEN Fuze devus esti programita por povi forviŝi programon kiu hazarde veturas havenon F3.

Estas nur 7 unu-finitaj enigkanaloj al la ADC haveblaj.

Haveno G0

La haveno G0 ne estas konektita al pinglo en la ATmega2564/1284/644RFR2. La alterna pingla funkcio DIG3 (inversa RX/TX-indikilo) ne disponeblas. Se la JTAG interfaco ne estas uzata la DIG4 alterna pingla funkcio eligo de haveno F3 ankoraŭ povas esti uzata kiel RX/TX-indikilo.

Haveno G2

La haveno G2 ne estas konektita al pinglo en la ATmega2564/1284/644RFR2. La alterna pingla funkcio AMR (sensinkrona aŭtomatigita mezurila legado enigo al tempigilo 2) ne estas disponebla.

Haveno G5

La haveno G5 ne estas konektita al pinglo en la ATmega2564/1284/644RFR2. La alterna pinglofunkcio OC0B (eliga kompara kanalo de 8-Bita tempigilo 0) ne haveblas.

RSTON

La rekomencigita eligo de RSTON signalanta la internan rekomencigitan staton ne estas konektita al pinglo en la ATmega2564/1284/644RFR2.

Resumo de agordo

Laŭ la aplikaj postuloj ŝanĝiĝema memorgrandeco permesas optimumigi nunan konsumon kaj elfluan kurenton.

Tabelo 3-1 Memora Agordo

| Aparato | Ekbrilo | EEPROM | SRAM |

| ATmega2564RFR2 | 256KB | 8KB | 32KB |

| ATmega1284RFR2 | 128KB | 4KB | 16KB |

| ATmega644RFR2 | 64KB | 2KB | 8KB |

Pako kaj rilata pingla agordo estas la samaj por ĉiuj aparatoj provizantaj plenan funkciecon al la aplikaĵo.

Tablo 3-2 Sistema Agordo

| Aparato | Pako | GPIO | Seria IF | ADC-kanalo |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

La aparatoj estas optimumigitaj por aplikoj bazitaj sur la ZigBee kaj la specifo IEEE 802.15.4. Havi aplikaĵan stakon, retan tavolon, sensilinterfacon kaj bonegan potencan kontrolon kombinitan en ununura blato multajn jarojn da operacio devus esti ebla.

Tabelo 3-3 Apliko Profile

| Aparato | Apliko |

| ATmega2564RFR2 | Granda Reta Kunordiganto / Enkursigilo por IEEE 802.15.4 / ZigBee Pro |

| ATmega1284RFR2 | Reta Kunordiganto/Enkursigilo por IEEE 802.15.4 |

| ATmega644RFR2 | Finnoda aparato/reta procesoro |

Aplikaj Cirkvitoj

Baza Aplika Skemo

Baza aplika skemo de la ATmega2564/1284/644RFR2 kun unu-finita RF-konektilo estas montrita en Figuro 4-1 malsupre kaj la rilata Materiala Fakturo en Tabelo 4-1 sur paĝo 10. La 50Ω-unu-fina RF-enigo estas transformita. al la 100Ω diferenciala RF-havenimpedanco uzante Balun B1. La kondensiloj C1 kaj C2 provizas AC-kupladon de la RF-enigo al la RF-haveno, kondensilo C4 plibonigas kongruadon.

Figuro 4-1. Baza Aplika skemo (48-stifta pako)

La elektroprovizaj preterpasaj kondensiloj (CB2, CB4) estas konektitaj al la ekstera analoga liverstifto (EVDD, pinglo 44) kaj ekstera cifereca liverstifto (DEVDD, pinglo 16). La kondensilo C1 disponigas la postulatan AC-kupladon de RFN/RFP.

Flosantaj pingloj povas kaŭzi troan povan disipadon (ekz. dum ŝaltado). Ili devus esti konektitaj al taŭga fonto. GPIO ne devas esti konektita al grundo aŭ elektroprovizo rekte.

La ciferecaj enigstiftoj TST kaj CLKI devas esti konektitaj. Se pinglo TST neniam estos uzata, ĝi povas esti konektita al AVSS dum neuzata pinglo CLKI povus esti konektita al DVSS (vidu ĉapitron "Neuzataj Stiftoj").

Kondensiloj CB1 kaj CB3 estas pretervojaj kondensiloj por la integra analoga kaj cifereca voltage reguligistoj por certigi stabilan funkciadon kaj plibonigi bruan imunecon.

Kondensiloj devas esti metitaj kiel eble plej proksime al la pingloj kaj devus havi malaltan reziston kaj malaltan induktan konekton al grundo por atingi la plej bonan rendimenton.

La kristalo (XTAL), la du ŝarĝkondensiloj (CX1, CX2), kaj la interna cirkulado ligita al pingloj XTAL1 kaj XTAL2 formas la 16MHz-kristalan oscilatoron por la 2.4GHz-ricevilo. Por atingi la plej bonan precizecon kaj stabilecon de la referenca frekvenco, grandaj parazitaj kapacitoj devas esti evititaj. Kristallinioj devus esti direktitaj kiel eble plej mallongaj kaj ne proksime de ciferecaj I/O-signaloj. Ĉi tio estas precipe postulata por la Alta Datuma Rapida Reĝimo.

La 32.768 kHz-kristalo konektita al la interna malalta potenco (sub 1µA) kristala oscilatoro disponigas stabilan tempreferencon por ĉiuj malaltaj potencaj reĝimoj inkluzive de 32 Bitoj IEEE 802.15.4 Symbol Counter ("MAC Symbol Counter") kaj realtempa horloĝa aplikaĵo uzante la nesinkronan. tempigilo T/C2 ("Temigilo/Counter2 kun PWM kaj Nesinkrona Operacio").

Totala ŝuntkapacitanco inkluzive de CX3, CX4 ne devus superi 15pF trans ambaŭ pingloj.

La tre malalta provizofluo de la oscilatoro postulas zorgan aranĝon de la PCB kaj ajna elflua vojo devas esti evitita.

Interkruciĝo kaj radiado de ŝanĝado de ciferecaj signaloj al la kristalaj pingloj aŭ la RF-pingloj povas degradi la sisteman rendimenton. La programado de minimumaj veturfortaj agordoj por la cifereca eligsignalo estas rekomendita (vidu "DPDS0 - Port Driver Strength Register 0").

Tabelo 4-1. Fakturo de Materialoj (BoM)

| Nomumanto | Priskribo | Valoro | Fabrikisto | Parta Nombro | Komento |

| B1 | SMD balun

SMD balun / filtrilo |

2.4 GHz | Wuerth Johanson Teknologio | 748421245

2450FB15L0001 |

Filtrilo inkluzivita |

| CB1 CB3 | LDO VREG

bypass kondensilo |

1 mF (minimumo 100nF) | AVX

Murata |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10% 16V |

| CB2 CB4 | Elektroprovizo bypass kondensilo | 1 mF (minimumo 100nF) | |||

| Ĉ1, Ĉ2 | 16MHz kristala ŝarĝa kondensilo | 12 pF | AVX

Murata |

06035A120JA GRP1886C1H120JA01 | COG (0603) 5% 50V |

| Ĉ3, Ĉ4 | 32.768kHz kristala ŝarĝokondensilo | 12 … 25 pF | |||

| C1, C2 | RF-kunliga kondensilo | 22 pF | Epcos Epcos AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 aŭ 0603) |

| C4 (laŭvola) | RF-kongruo | 0.47 pF | Johnstech | ||

| XTAL | Kristalo | Ĉ-4025 16 MHz

SX-4025 16 MHz |

ACAL Taitjen Siward | XWBBPL-F-1 A207-011 | |

| XTAL 32kHz | Kristalo | Rs=100 kOhm |

Historio de Revizio

Bonvolu noti, ke la referencaj paĝnumeroj en ĉi tiu sekcio rilatas al ĉi tiu dokumento. La referenca revizio en ĉi tiu sekcio rilatas al la dokumenta revizio.

Rev. 42073BS-MCU Sendrata-09/14

- Enhavo neŝanĝita - rekreita por kombinita eldono kun la datenfolio.

Rev 8393AS-MCU Sendrata-02/13

- Komenca eldono.

© 2014 Atmel Corporation. Ĉiuj rajtoj rezervitaj. / Rev.: 42073BS-MCU Wireless-09/14 Atmel® , Atmel-emblemo kaj kombinaĵoj de tio, Enabling Unlimited Possibilities® , kaj aliaj estas registritaj varmarkoj aŭ varmarkoj de Atmel Corporation aŭ ĝiaj filioj. Aliaj terminoj kaj produktnomoj povas esti varmarkoj de aliaj.

Malgarantio: La informoj en ĉi tiu dokumento estas provizita lige kun Atmel-produktoj. Neniu licenco, esprima aŭ implicita, per malpermeso aŭ alie, al ajna intelekta proprieta rajto estas donita de ĉi tiu dokumento aŭ lige kun la vendo de Atmel-produktoj. KROM KIEL INSTALITA EN LA ATMEL-KONDIĈOJ DE VENDO LOKITA SUR LA ATMEL. WEBRETEJO, ATMEL ASUPONAS NENIAN RESPONBON KAJ RILAS AJN AJN ESPPRIMAN, IMPLICITAN AŬ LEJAN GARANTION RELATANTI AL ĜIAJ PRODUTOJ INKLUDE, SED NE LIMIGISTE AL, LA IMPLITA GARANTIO PRI KOMERKABLECO, TAŬGECO POR APARTA CELO, INFRULO. NENIEK ATMEL RESPONDAS PRI IUJ REKTA, NEKREKTA, KONSEKVA, PUNITIVA, SPECIALA AŬ EKZENDAJ damaĝoj (INKLUDE, SEN LIMIGO, damaĝoj por perdo kaj profitoj, komercaj interrompoj aŭ perdo de informoj) EKZISTANTA PRO LA UZADO DE UZO. ĈI ĈI DOKUMENTO, Eĉ SE ATMEL ESTIS INFORMITA PRI LA POSIBLO DE TIAJ DANMAĜOJ. Atmel faras neniujn reprezentojn aŭ garantiojn rilate la precizecon aŭ kompletecon de la enhavo de ĉi tiu dokumento kaj rezervas la rajton fari ŝanĝojn al specifoj kaj produktaj priskriboj en ajna momento sen avizo. Atmel ne faras ajnan devontigon ĝisdatigi la informojn enhavitajn ĉi tie. Krom se specife provizite alie, Atmel-produktoj ne taŭgas por kaj ne devas esti uzataj en aŭtomobilaj aplikoj. Atmel-produktoj ne estas destinitaj, rajtigitaj aŭ garantiitaj por uzo kiel komponantoj en aplikoj intencitaj por subteni aŭ subteni vivon.

Mouser Elektroniko

Rajtigita Distribuisto

Klaku al View Informoj pri Prezoj, Stokregistro, Livero kaj Vivciklo:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

Klienta Subteno

Atmel Corporation

1600 Teknologia Veturado

San Jose, CA 95110

Usono

Tel: (+1)408-441-0311

Faksi: (+1)408-487-2600

www.atmel.com

Dokumentoj/Rimedoj

|

Atmel ATmega2564 8bit AVR Mikroregilo [pdf] Manlibro de la posedanto ATmega2564RFR2, ATmega1284RFR2, ATmega644RFR2, ATmega2564 8bit AVR Mikroregilo, ATmega2564, 8bit AVR Mikroregilo, AVR Mikroregilo, Mikroregilo |