Microcontrolador Atmel ATmega2564 8 bits AVR

Características

- Suporte de rede por filtragem de múltiplos endereços PAN assistida por hardware

- Consumo de energia reduzido assistido por hardware avançado

- Microcontrolador AVR® de 8 bits de alto desempenho e baixo consumo de energia

- Arquitetura RISC Avançada

- 135 Instruções poderosas - Maior execução de ciclo de clock único

- Registros de trabalho de uso geral 32 × 8 / multiplicador de 2 ciclos no chip

- Taxa de transferência de até 16 MIPS a 16 MHz e 1.8 V – operação totalmente estática

- Programa não volátil e memórias de dados

- 256K/128K/64K Bytes de Flash Autoprogramável no Sistema

- Resistência: 10 ciclos de gravação/apagamento a 000°C (125 ciclos a 25°C)

- EEPROM de 8K/4K/2K bytes

- Resistência: 20 ciclos de gravação/apagamento a 000°C (125 ciclos a 100°C)

- SRAM interna de 32K/16K/8K bytes

- JTAG (Compatível com padrão IEEE 1149.1) Interface

- Capacidades de varredura de limite de acordo com o JTAG Padrão

- Amplo suporte de depuração no chip

- Programação de Flash EEPROM, Fusíveis e Lock Bits através do JTAG interface

- Recursos Periféricos

- Vários canais de temporizador/contador e PWM

- Contador em tempo real com oscilador separado

- Conversor A/D de 10 bits, 330 ks/s; Comparador Analógico; Sensor de temperatura no chip

- Interface Serial SPI Mestre/Escravo

- Dois USART seriais programáveis

- Interface serial de 2 fios orientada a bytes

- Manipulador de interrupção avançado e modos de economia de energia

- Watchdog Timer com oscilador separado no chip

- Redefinição de inicialização e detector de queda de corrente baixa

- Transceptor de baixa potência totalmente integrado para banda ISM de 2.4 GHz

- Alta potência Ampsuporte lifier por supressão de lóbulo lateral do espectro TX

- Taxas de dados suportadas: 250 kb/s e 500 kb/s, 1 Mb/s, 2 Mb/s

- Sensibilidade RX de -100dBm; Potência de saída TX de até 3.5 dBm

- MAC assistido por hardware (reconhecimento automático, nova tentativa automática)

- Contador de símbolos IEEE 32 de 802.15.4 bits

- Detecção SFD, Espalhamento; Des-propagação; Enquadramento; Computação CRC-16

- Diversidade de antena e controle TX/RX / TX/RX 128 Byte Frame Buffer

- Sintetizador PLL com espaçamento de canal de 5 MHz e 500 kHz para banda ISM de 2.4 GHz

- Segurança de hardware (AES, True Random Generator)

- Osciladores de cristal integrados (32.768 kHz e 16 MHz, cristal externo necessário)

- E/S e pacote

- 33 linhas de E/S programáveis

- QFN de 48 pads (RoHS/totalmente verde)

- Faixa de temperatura: -40°C a 125°C Industrial

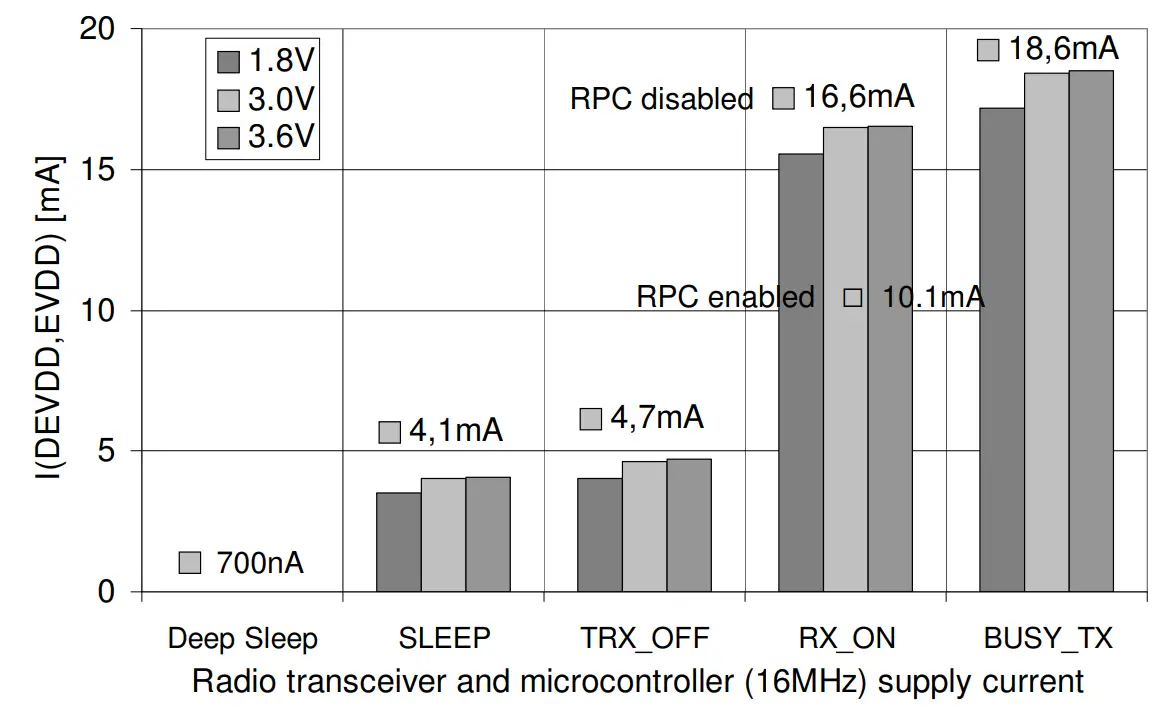

- Consumo de energia ultrabaixo (1.8 a 3.6 V) para AVR e Rx/Tx: 10.1 mA/18.6 mA

- Modo ativo da CPU (16 MHz): 4.1 mA

- Transceptor de 2.4 GHz: RX_ON 6.0 mA / TX 14.5 mA (potência máxima de saída TX)

- Modo de suspensão profunda: <700nA @ 25°C

- Grau de velocidade: 0 – 16 MHz @ faixa de 1.8 – 3.6 V com vol integradotage reguladores

Aplicações

- ZigBee®/IEEE 802.15.4-2011/2006/2003™ – Dispositivo de função completa e reduzida

- Transceptor de banda ISM de uso geral de 2.4 GHz com microcontrolador

- RF4CE, SP100, WirelessHART™, aplicações ISM e IPv6/6LoWPAN

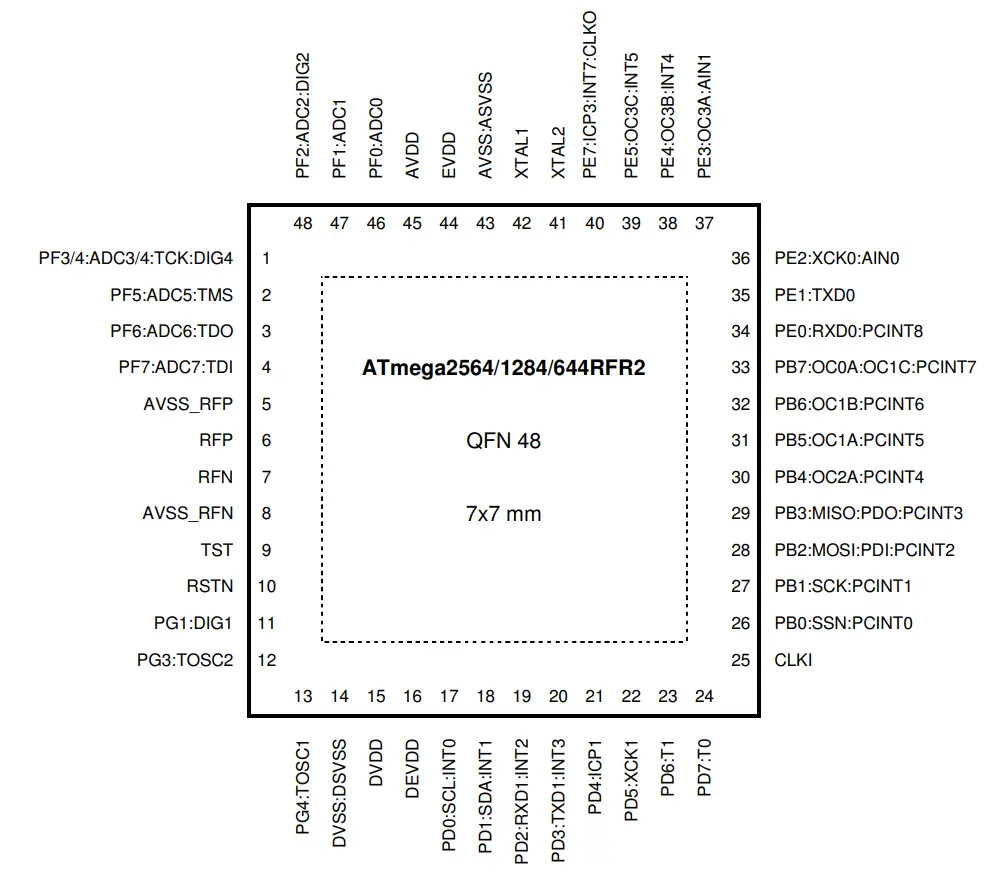

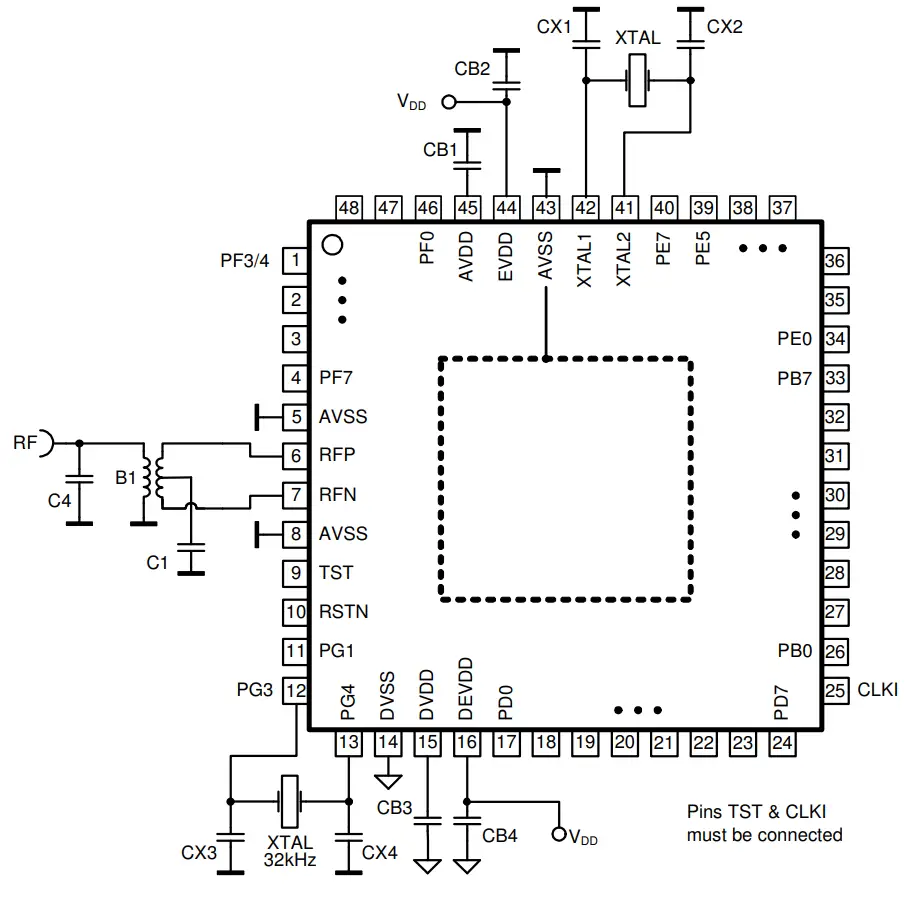

Configurações de pinos

Figura 1-1. Pinagem ATmega2564/1284/644RFR2

Observação: A grande almofada central abaixo do pacote QFN/MLF é feita de metal e conectada internamente ao AVSS. Deve ser soldado ou colado à placa para garantir uma boa estabilidade mecânica. Se a almofada central não estiver conectada, a embalagem poderá se soltar da placa. Não é recomendado usar a pá exposta como substituição dos pinos AVSS regulares.

Isenção de responsabilidade

Os valores típicos contidos nesta folha de dados são baseados em resultados de simulação e caracterização de outros microcontroladores AVR e transceptores de rádio fabricados em uma tecnologia de processo semelhante. Os valores Mínimo e Máximo estarão disponíveis após a caracterização do dispositivo.

Sobreview

O ATmega2564/1284/644RFR2 é um microcontrolador CMOS de 8 bits de baixa potência baseado na arquitetura RISC aprimorada AVR combinada com um transceptor de alta taxa de dados para a banda ISM de 2.4 GHz.

Ao executar instruções poderosas em um único ciclo de clock, o dispositivo atinge taxas de transferência próximas de 1 MIPS por MHz, permitindo ao projetista do sistema otimizar o consumo de energia em relação à velocidade de processamento.

O transceptor de rádio fornece altas taxas de dados de 250 kb/s até 2 Mb/s, manipulação de quadros, excelente sensibilidade do receptor e alta potência de saída de transmissão, permitindo uma comunicação sem fio muito robusta.

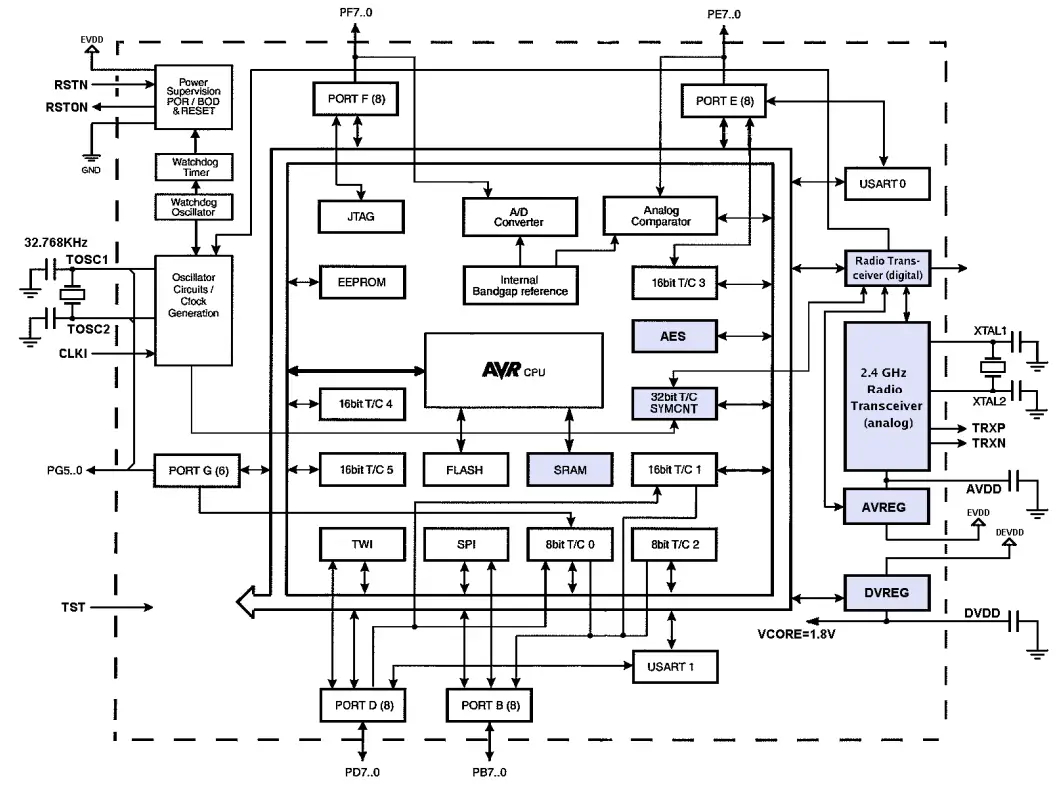

Diagrama de bloco

Figura 3-1 Diagrama de blocos

O núcleo do AVR combina um rico conjunto de instruções com 32 registros de trabalho de uso geral. Todos os 32 registros estão diretamente conectados à Unidade Lógica Aritmética (ALU). Dois registradores independentes podem ser acessados com uma única instrução executada em um ciclo de clock. A arquitetura resultante é muito eficiente em termos de código, ao mesmo tempo em que atinge rendimentos até dez vezes mais rápidos do que os microcontroladores CISC convencionais. O sistema inclui volume internotage regulação e gerenciamento avançado de energia. Distinguido pela pequena corrente de fuga permite um tempo de operação prolongado da bateria.

O transceptor de rádio é uma solução ZigBee totalmente integrada que utiliza um número mínimo de componentes externos. Combina excelente desempenho de RF com baixo custo, tamanho pequeno e baixo consumo de corrente. O transceptor de rádio inclui um sintetizador, transmissor e receptor de N fracionário estabilizado por cristal e processamento completo de sinal de espectro de propagação de sequência direta (DSSS) com espalhamento e desprendimento. O dispositivo é totalmente compatível com os padrões IEEE802.15.4-2011/2006/2003 e ZigBee. O ATmega2564/1284/644RFR2 fornece os seguintes recursos: 256K/128K/64K Bytes de Flash Programável no Sistema (ISP) com recursos de leitura durante gravação, EEPROM de 8K/4K/2K Bytes, SRAM de 32K/16K/8K Bytes, até 35 linhas de E/S de uso geral, 32 registros de trabalho de uso geral, contador em tempo real (RTC), 6 temporizadores/contadores flexíveis com modos de comparação e PWM, um temporizador/contador de 32 bits, 2 USART, um 2 fios orientado a bytes Interface serial, um conversor analógico para digital (ADC) de 8 canais e 10 bits com uma entrada diferencial opcionaltage com ganho programável, Watchdog Timer programável com oscilador interno, porta serial SPI, padrão IEEE. Compatível com 1149.1JTAG interface de teste, também usada para acessar o sistema On-chip Debug e programação e 6 modos de economia de energia selecionáveis por software.

O modo Idle interrompe a CPU enquanto permite que SRAM, temporizadores/contadores, porta SPI e sistema de interrupção continuem funcionando. O modo Power-down salva o conteúdo do registro, mas congela o oscilador, desativando todas as outras funções do chip até a próxima interrupção ou reinicialização do hardware. No modo de economia de energia, o temporizador assíncrono continua a funcionar, permitindo ao usuário manter uma base de temporizador enquanto o restante do dispositivo está em suspensão. O modo de redução de ruído ADC interrompe a CPU e todos os módulos de E/S, exceto o temporizador assíncrono e o ADC, para minimizar o ruído de comutação durante as conversões ADC. No modo Standby, o oscilador RC está funcionando enquanto o restante do dispositivo está em hibernação. Isto permite um arranque muito rápido combinado com baixo consumo de energia. No modo Extended Standby, tanto o oscilador RC principal quanto o temporizador assíncrono continuam a funcionar.

A corrente de alimentação típica do microcontrolador com clock da CPU ajustado para 16MHz e o transceptor de rádio para os estados mais importantes é mostrada na Figura 3-2 abaixo.

Figura 3-2 Transceptor de rádio e microcontrolador (16MHz) fornecem corrente

A potência de saída de transmissão está definida para o máximo. Se o transceptor de rádio estiver no modo SLEEP, a corrente será dissipada apenas pelo microcontrolador AVR.

No modo Deep Sleep, todos os principais blocos digitais sem requisitos de retenção de dados são desconectados da fonte principal, proporcionando uma corrente de fuga muito pequena. O temporizador Watchdog, o contador de símbolos MAC e o oscilador de 32.768kHz podem ser configurados para continuar funcionando.

O dispositivo é fabricado com tecnologia de memória não volátil de alta densidade da Atmel.

O ISP Flash no chip permite que a memória do programa seja reprogramada no sistema através de uma interface serial SPI, por um programador de memória não volátil convencional ou por um programa de inicialização no chip executado no núcleo AVR. O programa de inicialização pode usar qualquer interface para baixar o programa aplicativo na memória Flash do aplicativo.

O software na seção Flash de inicialização continuará em execução enquanto a seção Flash do aplicativo for atualizada, proporcionando uma verdadeira operação de leitura durante gravação. Ao combinar uma CPU RISC de 8 bits com Flash autoprogramável no sistema em um chip monolítico, o Atmel ATmega2564/1284/644RFR2 é um microcontrolador poderoso que fornece uma solução altamente flexível e econômica para muitas aplicações de controle embarcadas.

O AVR ATmega2564/1284/644RFR2 é compatível com um conjunto completo de ferramentas de desenvolvimento de programas e sistemas, incluindo: compilador C, montadores de macro, depuradores/simuladores de programas, emuladores de circuito e kits de avaliação.

Descrições dos Pinos

EVDD

Alimentação analógica externa voltage.

DEVDD

Fornecimento digital externo voltage.

AVDD

Alimentação analógica regulada voltage (gerado internamente).

DVD

Fornecimento digital regulamentado voltage (gerado internamente).

DVSS

Terreno digital.

AVSS

Terra analógica.

Porta B (PB7…PB0)

A porta B é uma porta de E/S bidirecional de 8 bits com resistores pull-up internos (selecionados para cada bit). Os buffers de saída da Porta B têm características de acionamento simétricas com alta capacidade de dissipação e origem. Como entradas, os pinos da porta B que são puxados externamente para baixo fornecerão corrente se os resistores pull-up forem ativados. Os pinos da porta B são tri-estabelecidos quando uma condição de reinicialização se torna ativa, mesmo se o relógio não estiver funcionando.

A porta B também fornece funções de vários recursos especiais do ATmega2564/1284/644RFR2.

Porta D (PD7…PD0)

A porta D é uma porta de E/S bidirecional de 8 bits com resistores pull-up internos (selecionados para cada bit). Os buffers de saída da Porta D têm características de acionamento simétricas com alta capacidade de dissipação e origem. Como entradas, os pinos da porta D que são puxados externamente para baixo fornecerão corrente se os resistores pull-up forem ativados. Os pinos da Porta D são tri-estabelecidos quando uma condição de reinicialização se torna ativa, mesmo se o relógio não estiver funcionando.

A porta D também fornece funções de vários recursos especiais do ATmega2564/1284/644RFR2.

Porta E (PE7,PE5…PE0)

Internamente, a Porta E é uma porta de E/S bidirecional de 8 bits com resistores pull-up internos (selecionados para cada bit). Os buffers de saída da Porta E possuem características de drive simétricas com alta capacidade de dissipador e fonte. Como entradas, os pinos da Porta E que são puxados externamente para baixo fornecerão corrente se os resistores pull-up estiverem ativados. Os pinos da Porta E recebem três estados quando uma condição de reinicialização se torna ativa, mesmo se o relógio não estiver funcionando.

Devido à baixa contagem de pinos do pacote QFN48, a porta E6 não está conectada a um pino. A porta E também fornece funções de vários recursos especiais do ATmega2564/1284/644RFR2.

Port F (PF7..PF5,PF4/3,PF2…PF0)

Internamente, a Porta F é uma porta de E/S bidirecional de 8 bits com resistores pull-up internos (selecionados para cada bit). Os buffers de saída da Porta F possuem características de unidade simétricas com alta capacidade de dissipador e fonte. Como entradas, os pinos da Porta F que são puxados externamente para baixo fornecerão corrente se os resistores pull-up estiverem ativados. Os pinos da Porta F recebem três estados quando uma condição de reinicialização se torna ativa, mesmo se o relógio não estiver funcionando.

Devido à baixa contagem de pinos do pacote QFN48, as portas F3 e F4 estão conectadas ao mesmo pino. A configuração de E/S deve ser feita com cuidado para evitar dissipação excessiva de energia.

A porta F também fornece funções de vários recursos especiais do ATmega2564/1284/644RFR2.

Porta G (PG4,PG3,PG1)

Internamente, a Porta G é uma porta de E/S bidirecional de 6 bits com resistores pull-up internos (selecionados para cada bit). Os buffers de saída da Porta G possuem características de drive simétricas com alta capacidade de dissipador e fonte. No entanto, a potência do driver PG3 e PG4 é reduzida em comparação com os outros pinos da porta. O volume de saídatagA queda (VOH, VOL) é maior enquanto a corrente de fuga é menor. Como entradas, os pinos da Porta G que são puxados externamente para baixo fornecerão corrente se os resistores pull-up estiverem ativados. Os pinos da Porta G recebem três estados quando uma condição de reinicialização se torna ativa, mesmo se o relógio não estiver funcionando.

Devido à baixa contagem de pinos do pacote QFN48, as portas G0, G2 e G5 não estão conectadas a um pino.

A porta G também fornece funções de vários recursos especiais do ATmega2564/1284/644RFR2.

AVSS_RFP

AVSS_RFP é um pino de aterramento dedicado para a porta de E/S de RF diferencial bidirecional.

AVSS_RFN

AVSS_RFN é um pino de aterramento dedicado para a porta de E/S de RF diferencial bidirecional.

Solicitação de proposta

RFP é o terminal positivo para a porta de E/S de RF diferencial bidirecional.

RFN

RFN é o terminal negativo para a porta de E/S de RF diferencial bidirecional.

RSTN

Redefinir entrada. Um nível baixo neste pino por mais tempo que o comprimento mínimo do pulso gerará um reset, mesmo se o relógio não estiver funcionando. Não é garantido que pulsos mais curtos gerem uma reinicialização.

XTAL1

Entrada para o oscilador de cristal inversor de 16 MHz amplificador. Em geral, um cristal entre XTAL1 e XTAL2 fornece o clock de referência de 16MHz do transceptor de rádio.

XTAL2

Saída do oscilador de cristal inversor de 16 MHz ampmais vivo.

TST

Pino de habilitação do modo de programação e teste. Se o pino TST não for usado, puxe-o para baixo.

CLKI

Entrada para o sistema de relógio. Se selecionado, fornece o relógio operacional do microcontrolador.

Pinos não utilizados

Pinos flutuantes podem causar dissipação de energia nas entradas digitaistage. Eles devem estar conectados a uma fonte apropriada. Nos modos normais de operação os resistores pull-up internos podem ser habilitados (em Reset todos os GPIO estão configurados como entrada e os resistores pull-up ainda não estão habilitados).

Os pinos de E/S bidirecionais não devem ser conectados diretamente ao terra ou à fonte de alimentação.

Os pinos de entrada digital TST e CLKI devem estar conectados. Se o pino não utilizado, o TST pode ser conectado ao AVSS, enquanto o CLKI deve ser conectado ao DVSS.

Os pinos de saída são acionados pelo dispositivo e não flutuam. Os pinos da fonte de alimentação e os respectivos pinos da fonte de aterramento são conectados entre si internamente.

XTAL1 e XTAL2 nunca serão forçados a fornecer voltage ao mesmo tempo.

Compatibilidade e limitações de recursos do pacote QFN-48

AREF

O vol de referênciatagA saída do conversor A/D não está conectada a um pino no ATmega2564/1284/644RFR2.

Porta E6

A porta E6 não está conectada a um pino no ATmega2564/1284/644RFR2. As funções do pino alternativo como entrada de relógio para o temporizador 3 e interrupção externa 6 não estão disponíveis.

Porta F3 e F4

As portas F3 e F4 estão conectadas ao mesmo pino no ATmega2564/1284/644RFR2. A configuração da saída deve ser feita com cuidado para evitar consumo excessivo de corrente.

A função de pino alternativo da porta F4 é usada pelo JTAG interface. Se o JTAG Se for utilizada a interface, a porta F3 deve ser configurada como entrada e a saída de função do pino alternativo DIG4 (indicador RX/TX) deve ser desabilitada. Caso contrário, o JTAG interface não funcionará. O fusível SPIEN deve ser programado para poder apagar um programa que acidentalmente acionou a porta F3.

Existem apenas 7 canais de entrada single-ended para o ADC disponíveis.

Porta G0

A porta G0 não está conectada a um pino no ATmega2564/1284/644RFR2. A função de pino alternativo DIG3 (indicador RX/TX invertido) não está disponível. Se o JTAG A interface não é usada, a saída da função de pino alternativo DIG4 da porta F3 ainda pode ser usada como indicador RX/TX.

Porta G2

A porta G2 não está conectada a um pino no ATmega2564/1284/644RFR2. A função de pino alternativo AMR (entrada de leitura automatizada assíncrona do medidor para o temporizador 2) não está disponível.

Porta G5

A porta G5 não está conectada a um pino no ATmega2564/1284/644RFR2. A função de pino alternativo OC0B (canal de comparação de saída do temporizador 8 de 0 bits) não está disponível.

RSTON

A saída de reset RSTON que sinaliza o estado de reset interno não está conectada a um pino no ATmega2564/1284/644RFR2.

Resumo da configuração

De acordo com os requisitos da aplicação, um tamanho de memória variável permite otimizar o consumo de corrente e a corrente de fuga.

Tabela 3-1 Configuração de memória

| Dispositivo | Clarão | EEPROM | SRAM |

| ATmega2564RFR2 | 256 KB | 8 KB | 32 KB |

| ATmega1284RFR2 | 128 KB | 4 KB | 16 KB |

| ATmega644RFR2 | 64 KB | 2 KB | 8 KB |

A configuração do pacote e dos pinos associados é a mesma para todos os dispositivos, fornecendo funcionalidade completa ao aplicativo.

Tabela 3-2 Configuração do Sistema

| Dispositivo | Pacote | GPIO | Serial SE | Canal ADC |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

Os dispositivos são otimizados para aplicações baseadas nas especificações ZigBee e IEEE 802.15.4. Ter pilha de aplicativos, camada de rede, interface de sensor e um excelente controle de energia combinados em um único chip deve ser possível por muitos anos de operação.

Tabela 3-3 Aplicativo Profile

| Dispositivo | Aplicativo |

| ATmega2564RFR2 | Coordenador/roteador de rede grande para IEEE 802.15.4/ZigBee Pro |

| ATmega1284RFR2 | Coordenador de Rede / Roteador para IEEE 802.15.4 |

| ATmega644RFR2 | Dispositivo de nó final/processador de rede |

Circuitos de Aplicação

Esquema Básico de Aplicação

Um esquema básico de aplicação do ATmega2564/1284/644RFR2 com um conector RF de terminação única é mostrado na Figura 4-1 abaixo e a lista de materiais associada na Tabela 4-1 na página 10. A entrada RF de terminação única de 50Ω é transformada à impedância diferencial da porta RF de 100Ω usando Balun B1. Os capacitores C1 e C2 fornecem acoplamento CA da entrada RF à porta RF, o capacitor C4 melhora a correspondência.

Figura 4-1. Esquema básico da aplicação (pacote de 48 pinos)

Os capacitores de bypass da fonte de alimentação (CB2, CB4) são conectados ao pino de alimentação analógica externa (EVDD, pino 44) e ao pino de alimentação digital externa (DEVDD, pino 16). O capacitor C1 fornece o acoplamento CA necessário de RFN/RFP.

Pinos flutuantes podem causar dissipação excessiva de energia (por exemplo, durante a inicialização). Eles devem estar conectados a uma fonte apropriada. GPIO não deve ser conectado diretamente ao terra ou à fonte de alimentação.

Os pinos de entrada digital TST e CLKI devem estar conectados. Se o pino TST nunca for usado, ele poderá ser conectado ao AVSS, enquanto um pino CLKI não utilizado poderá ser conectado ao DVSS (consulte o capítulo “Pinos não utilizados”).

Os capacitores CB1 e CB3 são capacitores de bypass para o vol analógico e digital integrado.tage reguladores para garantir uma operação estável e melhorar a imunidade ao ruído.

Os capacitores devem ser colocados o mais próximo possível dos pinos e devem ter uma conexão de terra de baixa resistência e baixa indutância para obter o melhor desempenho.

O cristal (XTAL), os dois capacitores de carga (CX1, CX2) e o circuito interno conectado aos pinos XTAL1 e XTAL2 formam o oscilador de cristal de 16 MHz para o transceptor de 2.4 GHz. Para obter a melhor precisão e estabilidade da frequência de referência, grandes capacitâncias parasitas devem ser evitadas. As linhas de cristal devem ser roteadas o mais curtas possível e não próximas de sinais de E/S digitais. Isto é especialmente necessário para os modos de alta taxa de dados.

O cristal de 32.768 kHz conectado ao oscilador de cristal interno de baixa potência (sub 1µA) fornece uma referência de tempo estável para todos os modos de baixa potência, incluindo contador de símbolos IEEE 32 de 802.15.4 bits (“Contador de símbolos MAC”) e aplicação de relógio em tempo real usando o assíncrono. temporizador T/C2 (“Temporizador/Contador2 com PWM e Operação Assíncrona”).

A capacitância total do shunt, incluindo CX3, CX4, não deve exceder 15pF em ambos os pinos.

A corrente de alimentação muito baixa do oscilador requer um layout cuidadoso da PCB e qualquer caminho de vazamento deve ser evitado.

Crosstalk e radiação da comutação de sinais digitais para os pinos de cristal ou pinos de RF podem degradar o desempenho do sistema. Recomenda-se a programação de configurações mínimas de intensidade do drive para o sinal de saída digital (ver “DPDS0 – Port Driver Strength Register 0”).

Tabela 4-1. Lista de materiais (BoM)

| Designador | Descrição | Valor | Fabricante | Número da peça | Comentário |

| B1 | Balão SMD

Balun/filtro SMD |

2.4 GHz | Tecnologia Wuerth Johanson | 748421245

2450FB15L0001 |

Filtro incluído |

| CB1 CB3 | LDO VREG

capacitor de desvio |

1 mF (mínimo de 100 nF) | AVX

Murata |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10% 16 V |

| CB2 CB4 | Capacitor de bypass da fonte de alimentação | 1 mF (mínimo de 100 nF) | |||

| CX1, CX2 | Capacitor de carga de cristal de 16 MHz | 12 pF | AVX

Murata |

06035A120JA GRP1886C1H120JA01 | COG (0603) 5% 50 V |

| CX3, CX4 | Capacitor de carga de cristal de 32.768 kHz | 12…25pF | |||

| C1, C2 | Capacitor de acoplamento RF | 22 pF | Epcos Epcos AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 ou 0603) |

| C4 (opcional) | Correspondência de RF | 0.47 pF | Johnstech | ||

| XTAL | Cristal | CX-4025 16MHz

SX-4025 16MHz |

ACAL Taitjen Siward | XWBBPL-F-1 A207-011 | |

| XTAL 32kHz | Cristal | Rs = 100 kOhm |

Histórico de revisão

Observe que os números de página de referência nesta seção referem-se a este documento. A revisão de referência nesta seção refere-se à revisão do documento.

Rev. 42073BS-MCU Sem Fio-09/14

- Conteúdo inalterado – recriado para lançamento combinado com a folha de dados.

Rev. 8393AS-MCU Sem Fio-02/13

- Lançamento inicial.

© 2014 Atmel Corporation. Todos os direitos reservados. / Rev.: 42073BS-MCU Wireless-09/14 Atmel®, logotipo Atmel e combinações dos mesmos, Enabling Unlimited Possibilities® e outros são marcas registradas ou marcas comerciais da Atmel Corporation ou de suas subsidiárias. Outros termos e nomes de produtos podem ser marcas comerciais de terceiros.

Isenção de responsabilidade: As informações neste documento são fornecidas em relação aos produtos Atmel. Nenhuma licença, expressa ou implícita, por preclusão ou de outra forma, a qualquer direito de propriedade intelectual é concedida por este documento ou em conexão com a venda de produtos Atmel. EXCETO CONFORME ESTABELECIDO NOS TERMOS E CONDIÇÕES DE VENDA ATMEL LOCALIZADOS NO ATMEL WEBSITE, A ATMEL NÃO ASSUME NENHUMA RESPONSABILIDADE E RENUNCIA A QUALQUER GARANTIA EXPRESSA, IMPLÍCITA OU LEGAL RELACIONADA A SEUS PRODUTOS, INCLUINDO, SEM LIMITAÇÃO, A GARANTIA IMPLÍCITA DE COMERCIABILIDADE, ADEQUAÇÃO A UM DETERMINADO FIM OU NÃO VIOLAÇÃO. EM NENHUM CASO A ATMEL SERÁ RESPONSÁVEL POR QUAISQUER DANOS DIRETOS, INDIRETOS, CONSEQUENTES, PUNITIVOS, ESPECIAIS OU INCIDENTAIS (INCLUINDO, SEM LIMITAÇÃO, DANOS POR PERDAS E LUCROS, INTERRUPÇÃO DE NEGÓCIOS OU PERDA DE INFORMAÇÕES) DECORRENTES DO USO OU INCAPACIDADE DE USO ESTE DOCUMENTO, MESMO QUE A ATMEL TENHA SIDO AVISADA DA POSSIBILIDADE DE TAIS DANOS. A Atmel não faz representações ou garantias com relação à precisão ou integridade do conteúdo deste documento e reserva-se o direito de fazer alterações nas especificações e descrições de produtos a qualquer momento sem aviso prévio. A Atmel não se compromete a atualizar as informações aqui contidas. Salvo disposição em contrário, os produtos Atmel não são adequados e não devem ser usados em aplicações automotivas. Os produtos da Atmel não são destinados, autorizados ou garantidos para uso como componentes em aplicações destinadas a dar suporte ou sustentar a vida.

Mouser Eletrônicos

Distribuidor autorizado

Clique para View Informações sobre preços, estoque, entrega e ciclo de vida:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

Suporte ao cliente

Corporação Atmel

1600 Tecnologia Drive

São José, CA 95110

EUA

Telefone: (+1)408-441-0311

Fax: (+1)408-487-2600

www.atmel.com

Documentos / Recursos

|

Microcontrolador Atmel ATmega2564 8 bits AVR [pdf] Manual do Proprietário ATmega2564RFR2, ATmega1284RFR2, ATmega644RFR2, ATmega2564 Microcontrolador AVR de 8 bits, ATmega2564, Microcontrolador AVR de 8 bits, Microcontrolador AVR, Microcontrolador |